# Low-loss compact multilayer silicon nitride platform for 3D photonic integrated circuits

Kuanping Shang, Shibnath Pathak, Binbin Guan, Guangyao Liu, and S. J. B. Yoo'

Department of Electrical and Computer Engineering, University of California, Davis, 95616, USA \*sbyoo@ucdavis.edu

**Abstract:** We design, fabricate, and demonstrate a silicon nitride (Si<sub>3</sub>N<sub>4</sub>) multilayer platform optimized for low-loss and compact multilayer photonic integrated circuits. The designed platform, with 200 nm thick waveguide core and 700 nm interlayer gap, is compatible for active thermal tuning and applicable to realizing compact photonic devices such as arrayed waveguide gratings (AWGs). We achieve ultra-low loss vertical couplers with 0.01 dB coupling loss, multilayer crossing loss of 0.167 dB at 90° crossing angle, 50  $\mu$ m bending radius,  $100\times2~\mu\text{m}^2$  footprint, lateral misalignment tolerance up to 400 nm, and less than -52 dB interlayer crosstalk at 1550 nm wavelength. Based on the designed platform, we demonstrate a  $27\times32\times2$  multilayer star coupler.

©2015 Optical Society of America

OCIS codes: (230.0230) Optical devices; (230.4170) Multilayers; (230.7370) Waveguides.

#### References and links

- T. L. Koch and U. Koren, "Semiconductor photonic integrated circuits," IEEE J. Quantum Electron. 27(3), 641–653 (1991).

- J. F. Bauters, M. J. R. Heck, D. D. John, J. S. Barton, C. M. Bruinink, A. Leinse, R. G. Heideman, D. J. Blumenthal, and J. E. Bowers, "Planar waveguides with less than 0.1 dB/m propagation loss fabricated with wafer bonding," Opt. Express 19(24), 24090–24101 (2011).

- D. D. John, M. J. R. Heck, J. F. Bauters, R. Moreira, J. S. Barton, J. E. Bowers, and D. J. Blumenthal, "Multilayer platform for ultra-low-loss waveguide applications," IEEE Photonics Technol. Lett. 24(11), 876–878 (2012).

- J. Feng and R. Akimoto, "Vertically coupled silicon nitride microdisk resonant filters," IEEE Photonics Technol. Lett. 26(23), 2391–2394 (2014).

- M. Sodagar, R. Pourabolghasem, A. A. Eftekhar, and A. Adibi, "High-efficiency and wideband interlayer grating couplers in multilayer Si/SiO2/SiN platform for 3D integration of optical functionalities," Opt. Express 22(14), 16767–16777 (2014).

- X. Zheng, J. E. Cunningham, I. Shubin, J. Simons, M. Asghari, D. Feng, H. Lei, D. Zheng, H. Liang, C. C. Kung, J. Luff, T. Sze, D. Cohen, and A. V. Krishnamoorthy, "Optical proximity communication using reflective mirrors," Opt. Express 16(19), 15052–15058 (2008).

- R. Moreira, J. Barton, M. Belt, T. Huffman, and D. Blumenthal, "Optical interconnect for 3D Integration of ultra-low loss planar lightwave circuits," in *Advanced Photonics* 2013, OSA Technical Digest (online) (OSA, 2013), IT2A.4.

- 8. D. Dai, Z. Wang, J. F. Bauters, M. C. Tien, M. J. R. Heck, D. J. Blumenthal, and J. E. Bowers, "Low-loss Si3N4 arrayed-waveguide grating (de)multiplexer using nano-core optical waveguides," Opt. Express 19(15), 14130–14136 (2011).

- A. Arbabi and L. L. Goddard, "Measurements of the refractive indices and thermo-optic coefficients of Si3N4 and SiOx using microring resonances," Opt. Lett. 38(19), 3878–3881 (2013).

- 10. K. Shang, S. Pathak, G. Liu, and S. J. B. Yoo, "Ultra-low loss vertical optical couplers for 3D photonic integrated circuits," in *Optical Fiber Communication Conference*, (OSA, 2015), paper Th1F.6.

- 11. K. Shang, S. Pathak, B. Guan, G. Liu, C. Qin, R. P. Scott, and S. J. B. Yoo, "Si3N4 multilayer platform for photonic integrated circuits," in *The Conference on Lasers and Electro-Optics* (OSA, 2015), STu2F.6.

#### 1. Introduction

Recent developments in photonic integrated circuits (PICs) [1] are attracting strong interest due to their advances of building scalable, high-throughput, and low-cost on-chip optical communication system. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) based PICs are becoming an outstanding

solution because of relatively low optical propagation losses [2]. The multilayer structure is promising for future low-loss, small-footprint, and high-density PICs.

Achieving low interlayer vertical coupling loss and waveguide crossing loss is essential for realizing practical  $\mathrm{Si_3N_4}$  multilayer PICs. The interlayer couplers in multilayer platform utilized various methods including directional couplers [3, 4], grating couplers [5], reflector mirrors [6], and inverse tapers couplers [7]. However, typical reported values for vertical coupling losses are ~1 dB for grating coupled [5, 6] configurations, or reasonably low 0.2 dB [7] for inverse taper couplers with waveguides accompanying large bending radius of 9 mm [8]. On the other hand, typical reported values for multilayer crossing losses are 0.4-0.6 dB [7], or reasonably low crossing loss of 0.254 dB when using a relatively wide waveguide width of 15  $\mu$ m [3]. Hence, the trade-off between vertical coupling and multilayer crossing loss for various interlayer distances is an important consideration in designing the waveguide for each layer. For devices with fewer multilayer crossings, shorter interlayer gap helps improve interlayer coupling but introduces large excess losses at crossing. For devices with many crossings, a larger interlayer gap increases coupling losses but reduces total insertion loss. Therefore, optimization of multilayer platform design for low total losses should be based on requirements for specific applications.

In this paper, we report a  $Si_3N_4/SiO_2$  multilayer platform design with core thickness of 200 nm and an interlayer gap of 700 nm optimized for compact multilayer photonic integrated circuits involving devices such as arrayed waveguide gratings (AWGs) with smaller than a 3  $\times$  1 mm² die. Based on this design, no measurable excess bending loss is reported with 50  $\mu$ m bending radius. We achieve 0.01 dB coupling loss from proposed vertical coupler with a 100  $\times$  2  $\mu$ m² footprint and 0.167 dB multilayer crossing losses at 90° crossing angle. Further, we demonstrate a 27  $\times$  32  $\times$  2 multilayer star coupler, which is useful for future 3-D photonic integrated devices.

## 2. Waveguide design

To design a practical platform of  $Si_3N_4/SiO_2$ , there are several factors that should be considered, such as device footprint, loss budget, and functional compatibility. For this paper, we aim to optimize a platform for compact and low loss AWGs within  $2.2 \times 0.7$  mm<sup>2</sup>. Therefore, the bending radius needs to be reasonably small.

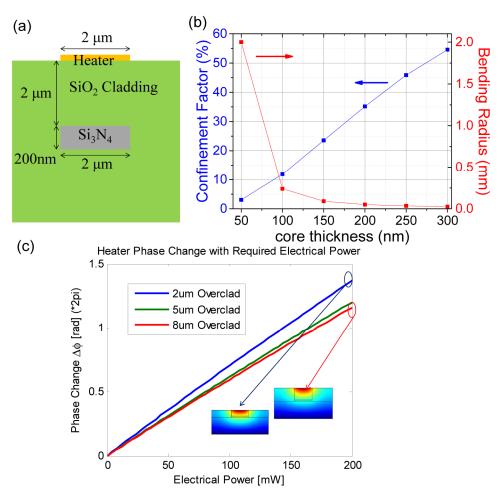

Figure 1(a) illustrates the cross section of proposed waveguide, where  $Si_3N_4$  is the waveguide core and  $SiO_2$  is the cladding. In Fig. 1(b), the blue curve shows simulated confinement factors with varying waveguide core thicknesses and the red curve shows corresponding bending radii. As the waveguide core thickness reduces below 100 nm, the mode is less confined in waveguide core, and the minimum bending radius required for < 0.1 dB loss/90° bending increases rapidly, leading to large device footprint. However, thick (>400 nm) silicon nitride waveguide cores increase the possibility of stress-induced cracks. Therefore, this paper investigates 200 nm  $Si_3N_4$  core thickness that yields 50  $\mu$ m bending radius.

Another consideration for the selection of waveguide core thickness is the requirement for thermal tuning for devices such as AWGs. Thermo-Optical Coefficient (TOC) of  $Si_3N_4$  is approximately 2.5 times that of  $SiO_2$  [9]. Waveguides with small confinement factors will have a smaller fraction of optical mode confined in  $Si_3N_4$  and require a larger heater power to achieve the same amount of phase shift. Furthermore, thinner optical cores also require thicker overcladding, which makes the heater less effective in heating the waveguide core. For these reasons, thinner silicon nitride waveguide cores require higher electrical power to achieve a given amount of optical phase shift. Figure 1(c) shows simulation plots of the optical phase change vs. electrical power of the heater of 1000  $\mu$ m length and 2  $\mu$ m width shown for three different overcladding thicknesses (2  $\mu$ m, 5  $\mu$ m, 8  $\mu$ m). The insets show simulated heat distribution for the silicon nitride waveguide with core dimensions 2  $\mu$ m  $\times$  200 nm

Fig. 1. (a) Cross section of proposed waveguide design; (b) simulated confinement factor (blue) and bending radius (red) with varied  $\mathrm{Si}_3\mathrm{N}_4$  single mode waveguide core thickness; at each bending radius, the simulated bending loss is less than 0.3 dB per 90°; (c) simulated phase change with required electrical power for overcladding thickness of 2  $\mu$ m (blue), 5  $\mu$ m (green), and 8  $\mu$ m (red).

### 3. Simulation and optimization of Si<sub>3</sub>N<sub>4</sub> platform

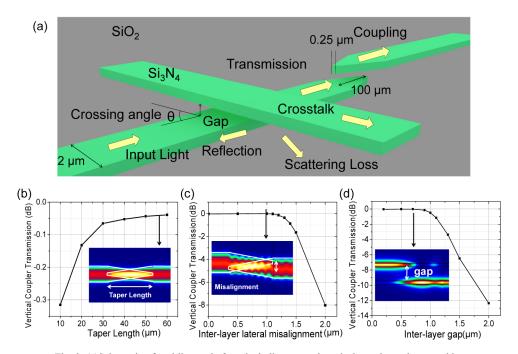

Multilayer platform PICs occupies a smaller footprint compared to a single layer PICs of equivalent functionality. As Fig. 2(a) illustrates, it is important to achieve low loss vertical couplers that interconnect between the layers while keeping the crosstalk and scattering loss minimal at the crossings.

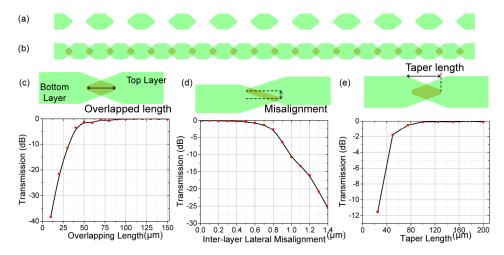

Figures 2(b)-2(d) simulate vertical coupling transmission with varying taper lengths, interlayer misalignments, and interlayer gaps, respectively. In Fig. 2(b), the interlayer gap is 200 nm, and the vertical transmission decreases when taper lengths are less than 30  $\mu$ m. In Fig. 2(c), the taper length and the interlayer gap are 100  $\mu$ m and 200 nm, respectively. In this case, lateral misalignments up to 1.2  $\mu$ m still supports strong vertical coupling, and this design is applied to a process requiring strong fabrication tolerance. Figure 2(d) illustrates that the vertical transmission starts to decrease when the interlayer gap increases above 800 nm for the taper length of 100  $\mu$ m.

Fig. 2. (a)Schematic of multilayer platform including tapered vertical coupler and waveguides crossing; (b-d)vertical coupling simulation of devices with varying (b) taper length,(c) lateral misalignment, and (d) inter-layer gap [10].

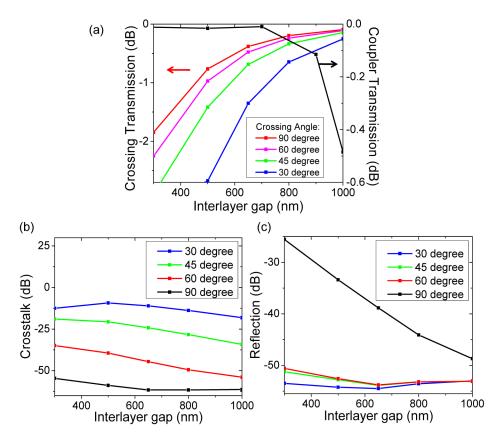

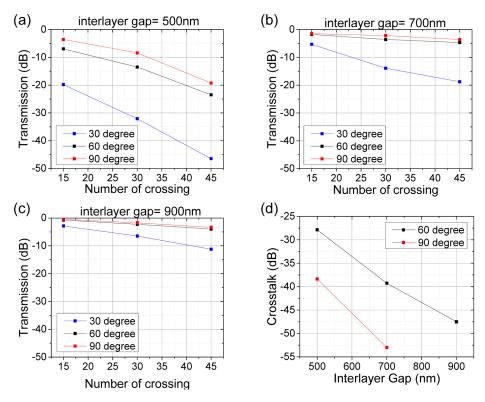

As indicated in Fig. 2(a), light incident into a cross gets transmitted, reflected, scattered, or becomes crosstalk to other layers. As simulated in Fig. 3(a), there is a trade-off between interlayer coupling transmission and crossing transmission as gap distance varies. The larger gap helps to reduce crossing loss while smaller gap improves vertical transmission. The value of gap optimized for ultra-low vertical coupling loss is 700 nm, where crossing loss is reasonably low. Another trade-off is between interlayer crosstalk and reflection by varying the crossing angle. Large crossing angle keeps low crosstalk while small crossing angle prevents reflection. Overall, platform optimization of the interlayer gap is to achieve low total insertion loss, based on the relative quantity between vertical coupler and multilayer crossing; while optimization of crossing angle is to meet devices application.

Fig. 3. (a) Left axis: FDTD simulation of multilayer waveguides crossing intra-layer transmission with varied interlayer gap at crossing angles of  $90^{\circ}$  (red),  $60^{\circ}$  (purple),  $45^{\circ}$  (green), and  $30^{\circ}$  (blue); right axis: zoomed-in vertical coupler transmission plot. (b-c) FDTD simulation of multilayer (b) crosstalk and (c) reflection with varied interlayer gap at crossing angles of  $90^{\circ}$  (red),  $60^{\circ}$  (purple),  $45^{\circ}$  (green), and  $30^{\circ}$  (blue) [11].

## 4. Device fabrication

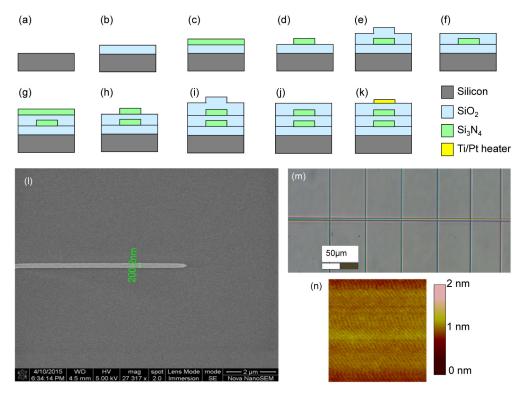

We fabricated the devices using ASML<sup>TM</sup> PAS 5500 300 deep-UV lithography stepper technology on 6-inch Silicon wafers. Figures 4(a)-4(k) show the principle steps of the fabrication process, starting with the growth of Low-Temperature Oxide (LTO) by Low-Pressure Chemical Vapor Deposition (LPCVD), serving as a lower cladding layer. We use stoichiometric Si<sub>3</sub>N<sub>4</sub> by LPCVD at 800 °C as waveguide layer and Inductively Coupled Plasma (ICP) Etching to define waveguides on both layers. Interlayer cladding is LTO planarized by Chemical Mechanical Polishing (CMP). The overcladding layer is planarized LTO, and the heater metal is 20 nm titanium and 200 nm platinum deposited by electron-beam evaporation.

Figures 4(1) and 4(m) are device photos of inverse taper tips and multilayer crossings. Figure 4(n) is the surface roughness measurement of planarized LTO by Atomic Force Microscopy (AFM). The RMS roughness is 1 nm.

Fig. 4. Fabrication flow charts of (a) initial cleaning of a 6 inch silicon wafer; (b) LTO deposition; (c)  $Si_3N_4$  bottom layer deposition; (d)  $Si_3N_4$  bottom layer lithography and etching; (e)inter-layer LTO cladding deposition; (f) CMP; (g)  $Si_3N_4$  top layer deposition; (h)  $Si_3N_4$  top layer lithography and etching; (i) LTO overcladding deposition; (j) CMP; (k) Ti/Pt heater lift-off. (l) photo of fabricated  $Si_3N_4$  tip; (m) photo of fabricated multilayer waveguides crossing at  $90^\circ$ ; (n) AFM measurement of  $SiO_2$  surface after CMP.

## 5. Characterization of vertical coupler and multilayer crossing

We characterize the fabricated devices by using single mode lensed fibers as input and output. The insertion loss of the straight waveguide is 3.2 dB including the facet coupling losses and the propagation loss in the straight waveguide. The coupling loss between lensed fiber and the waveguide is 1.5 dB per facet. The measured straight waveguide propagation loss is  $0.3 \pm 0.1$  dB/cm.

Fig. 5. (a) Single layer Si<sub>3</sub>N<sub>4</sub>top view schematic for 10 sections of inverse taper and positive taper; (b) Double-layer Si<sub>3</sub>N<sub>4</sub>top view schematic for 20 stages of overlaid vertical couplers; (ce) measured vertical coupling transmission of in-series 20 couplers with varying (c) overlapping length, (d) interlayer lateral misalignment, and (e)taper length.

Figure 5(a) shows the schematic of lower layer waveguide core, where ten sections of inverse tapers and positive tapers are in series. Figure 5(b) shows the schematic of the Si<sub>3</sub>N<sub>4</sub> lower layer core and the upper layer core overlaid on its top with a 700 nm gap to achieve light transmission by 20 stages of inter-layer coupling. The measured transmission is less than -60 dB and -3.4 dB for devices with single layer only (no vertical couplers) and with double layer, respectively, indicating strong coupling between layers. The plots in Figs. 5(c)-5(e) show the measured vertical transmission values (normalized to the waveguide transmission of the same length) of vertical couplers with varying overlapping length, interlayer lateral misalignment, and taper length. The measured excess loss of the 20 stages of cascaded vertical couplers was 0.2 dB (normalized to the waveguide transmission of the same length), indicating that the intrinsic loss of each vertical coupling is on the average 0.01 dB per coupling for the vertical coupler with taper length of 100 µm and overlapping length of 100 μm. Interlayer misalignment tolerance of the ASML stepper is less than 60 nm. The overlapping length is indicating the misalignment in propagating direction, where the tolerance is 15 µm for inverse taper with a length of 100 µm. The lateral misalignment tolerance of 400 nm is reasonable regarding taper tip width of 250 nm.

Figures 6(a)-6(c) illustrate measured transmission values for a waveguide crossing with a number of cascaded waveguides at another layer crossing at angles of 30°, 60°, and 90° with interlayer gap of 500 nm, 700 nm, and 900 nm, respectively. For a 700 nm interlayer gap, the measured crossing transmission is - 0.167 dB at crossing angle of 90°. The corresponding crosstalk is -52 dB, as shown in Fig. 6(d).

Fig. 6. Measured multilayer crossing transmission with interlayer gap of (a) 500 nm, (b) 700 nm, and (c) 900nm at crossing angle of 30° (blue), 60° (black), and 90° (red); (d) measured interlayer crosstalk with varied interlayer gap at crossing angle of 60° (black) and 90° (red).

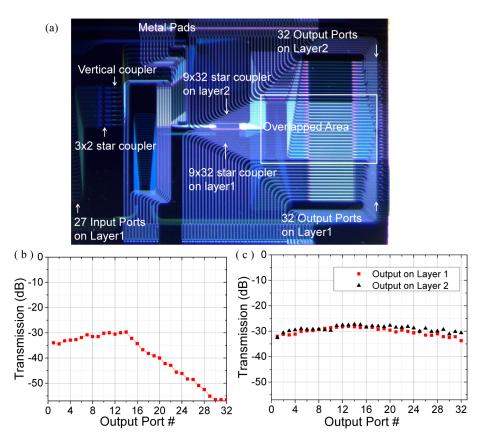

#### 6. Multilayer star couplers

Figure 7(a) shows an example of multilayer PICs composed of multiple connected couplers. On this PIC, there are 27 input ports that feed into nine  $3 \times 2$  couplers on layer 1 (lower layer). The two outputs from the  $3 \times 2$  couplers feed two different  $9 \times 32$  star couplers, one on layer 1, and the other on layer 2 via a vertical coupler. By utilizing multilayer platform, the footprint of this PIC is reduced from 80 mm<sup>2</sup> to 40 mm<sup>2</sup>. In Fig. 7(b), the output transmission increases by 2 dB per port from #15 to #32, resulting in >25 dB variation from multilayer crossing with 300 nm interlayer gap. Figure 7(c) shows the 32 × 2 multiple output transmission with 800 nm interlayer gap. The corresponding variation is about 5 dB across all outputs, mainly resulting from the star coupler design.

Fig. 7. (a) Device photo of fabricated multilayer starcoupler; (b) measured transmission of 32 output ports on layer1 with 300 nm interlayer gap, where from port #15 to #32, the number of multilayer crossings increases from 1 to 18; (c) measured transmission of 32 output ports on layer1 (red) and 32 output ports on layer2 (black) with 800 nm interlayer gap.

#### 7. Conclusion

We demonstrate a multilayer Si3N4 platform for compact 3D PIC with ultra-low interlayer coupling loss of 0.01 dB, low multilayer crossing loss of 0.167 dB at 90° crossing angle, compact bending radius of 50  $\mu$ m, small interlayer crosstalk of –52 dB, strong fabrication tolerance of lateral and tangential misalignment up to 400nm and 15  $\mu$ m. Our inverse taper vertical couplers also have a compact device footprint of 100  $\times$  2  $\mu$ m², which is small compared to other vertical coupling solutions [3, 5, 6] and other inverse taper designs [7].

## Acknowledgments

Devices were fabricated in Marvell Nanolab facility, University of California, Berkeley, and North California Nanotechnology Center, University of California, Davis.

This work was supported in part by DARPA DSO under the contracts HR0011-11-1-0005 and W911NF-12-1-0311, DARPA TTO under grant no. W31P4Q-13-1-006, and by National Science Foundation (NSF) under ECCS-1028729.