# Ternary Computing Testbed 3-Trit Computer Architecture

Jeff Connelly

Computer Engineering Department

August 29th, 2008

with contributions from Chirag Patel and Antonio Chavez

Advised by Professor Phillip Nico California Polytechnic State University of San Luis Obispo

# Table of Contents

| 1. Introduction                 |              | 1  |

|---------------------------------|--------------|----|

| 1.1. Method                     |              | 1  |

| 1.2. Plan                       |              | 2  |

| 1.3. Team and Individual Respo  | onsibilities | 2  |

| 1.3.1. Jeff Connelly            |              | 2  |

| 1.3.2. Antonio Chavez           |              | 2  |

| 1.3.3. Chirag Patel             |              | 3  |

| 2. Background Theory            |              | 3  |

| 2.1. Base 3                     |              | 3  |

| 2.1.1. Compared to Analog       |              | 3  |

| 2.1.2. Compared to Digital      |              | 4  |

| 2.1.3. Compared to Base e       |              | 5  |

| 2.1.4. Trits, Tribbles, and Try | vtes         | 7  |

| 2.1.5. Base 9 and 27            |              | 9  |

| 2.1.6. Text                     |              | 10 |

| 2.2. Logic and Arithmetic       |              | 10 |

| 3. Application Description      | 1            | 10 |

| 3.1. Christmas Lights Game      |              | 10 |

| 3.2. Guessing Game              |              | 11 |

| 4. Architecture Description     | n            | 11 |

| 4.1. Power Supply               |              | 12 |

| 4.2. Instruction Memory         |              | 13 |

| 4.2.1. Experimental Results     |              | 16 |

| 4.3. Program Counter                                | 16 |

|-----------------------------------------------------|----|

| 4.4. Clock Generator                                | 17 |

| 4.5. Processor                                      | 18 |

| 4.5.1. Registers                                    | 18 |

| 4.5.2. Input and Output                             | 19 |

| 4.5.3. 3-Trit Instruction Set                       | 20 |

| 4.5.4. LWI Instruction Example (also known as TCA0) | 21 |

| 4.5.5. CMP Instruction                              | 25 |

| 4.5.5.1. ALU                                        | 26 |

| 4.5.5.2. CMP Instruction Example                    | 29 |

| 4.5.6. BE Instruction                               | 31 |

| 4.5.6.1. BE Instruction Example                     | 32 |

| 4.5.7. Guessing Game Program                        | 33 |

| 5. Evaluation                                       | 38 |

| 6. Conclusion and Future Directions                 | 39 |

| 7. Works Cited                                      | 40 |

| A. Logic                                            | 43 |

| A.1. Unicode Symbols                                | 43 |

| A.2. Ternary Functions                              | 44 |

| A.3. Unary Functions                                | 44 |

| A.3.1. Constant Functions                           | 45 |

| A.3.2. One-to-one Functions                         | 45 |

| A.3.3. Many-to-one Functions                        | 46 |

| A.3.4. Symmetric Unary Functions                    | 49 |

| A.3.5. Basic Unary Functions                        | 50 |

| A.3.6 Unary Overbar Notation Explained | 50 |

|----------------------------------------|----|

| A.4. Dyadic Functions                  | 51 |

| A.4.1. Commutativity                   | 51 |

| A.4.2. Preference Functions            | 53 |

| A.4.3. Tritmasks                       | 55 |

| A.4.4. Named Functions                 | 55 |

| A.4.5. Completeness                    | 56 |

| A.5. Troolean Algebra Functions        | 57 |

| A.6. Unknown-State Logic               | 57 |

| A.6.1. NOT: Inversion                  | 58 |

| A.6.2. AND, XOR, OR, XNOR, NAND        | 59 |

| A.7. SQL-like NULL Logic               | 60 |

| A.8. Works Cited                       | 60 |

| B. Arithmetic                          | 64 |

| B.1. Balanced Arithmetic               | 64 |

| B.1.1. Negation: Inversion             | 65 |

| B.1.2. Sign                            | 66 |

| B.1.3. Even/Odd                        | 67 |

| B.1.4. Rounding                        | 67 |

| B.1.5. Addition: Half-adder            | 68 |

| B.1.6. Addition: Full-adder            | 71 |

| B.1.7. Subtraction                     | 79 |

| B.1.8. Multiplication                  | 79 |

| B.1.9. Division                        | 80 |

| B.2. Unbalanced Arithmetic             | 80 |

| B.2.1. Negation: 3's Complement        | 80 |

|----------------------------------------|----|

| B.2.2. Addition                        | 80 |

| B.2.3. Subtraction                     | 81 |

| B.3. Works Cited                       | 81 |

| C. Implementation Methods              | 85 |

| C.1. Existing Computers                | 85 |

| C.1.1. TERNAC                          | 85 |

| C.1.2. Trinary                         | 85 |

| C.1.3. Dytrax 1000                     | 85 |

| C.1.4. TRIPS Processor                 | 85 |

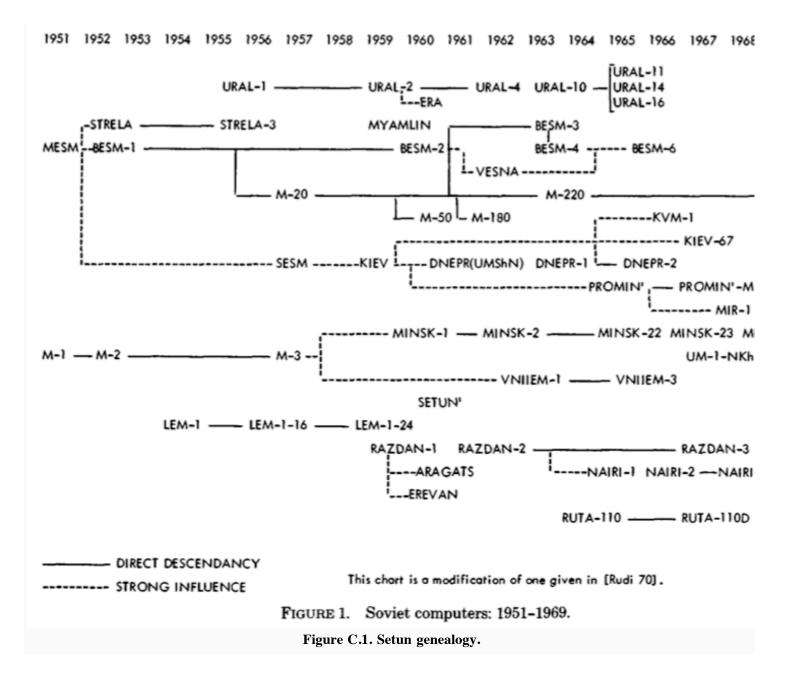

| C.1.5. Setun (Russian: Сетунь)         | 85 |

| C.1.6. Team R2D2's 64-tert SRAM        | 86 |

| C.2. Electrostatic Charge (Capacitors) | 86 |

| C.3. Magnetism                         | 87 |

| C.3.1. Electromagnetism                | 87 |

| C.3.2. Bipolar Relays                  | 88 |

| C.3.3. Core Memory                     | 89 |

| C.4. Gravity                           | 89 |

| C.5. Rapid Single Flux Quantum         | 90 |

| C.6. Cryogenic Storage Devices         | 90 |

| C.7. Light and Other Methods           | 90 |

| C.8. Electrical Methods                | 90 |

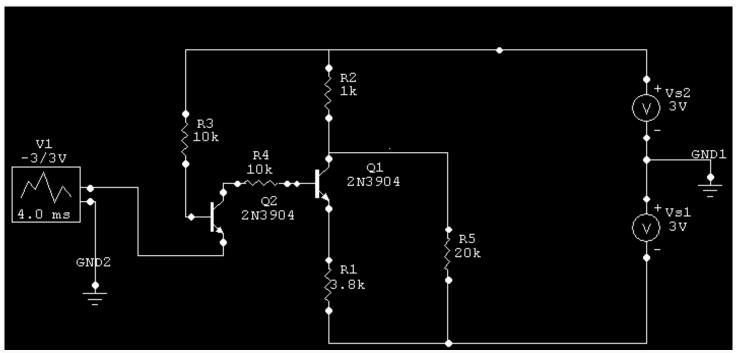

| C.8.1. BJT Model                       | 91 |

| C.8.2. CMOS Logic                      | 91 |

| C.9. Works Cited                       | 92 |

| O. Circuit Simulation                                                   | 97  |

|-------------------------------------------------------------------------|-----|

| D.1. LTspice Parts Library                                              | 97  |

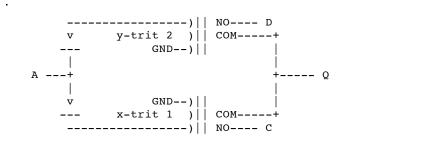

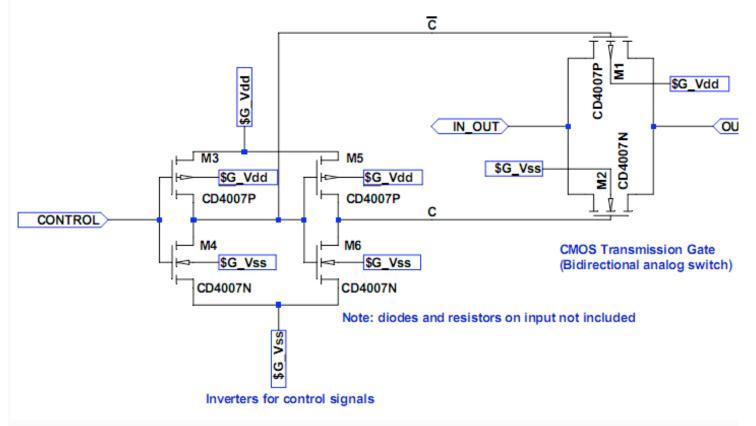

| D.2. Transmission Gate                                                  | 97  |

| D.3. Unary Logic Gates                                                  | 99  |

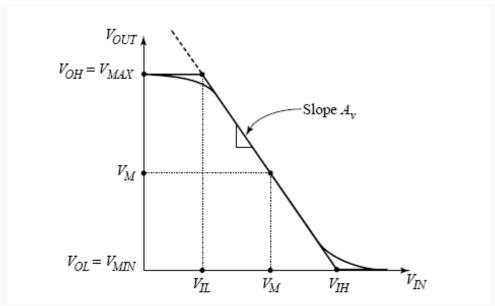

| D.3.1. VTC Curve Characteristics                                        | 99  |

| D.3.2. Inverters                                                        | 101 |

| D.3.3. Diode Gates                                                      | 104 |

| D.3.4. Cycling Gates                                                    | 108 |

| D.3.5. Shift Gates                                                      | 111 |

| D.4. Dyadic Logic Gates                                                 | 112 |

| D.4.1. TNAND                                                            | 112 |

| D.4.2. TNOR                                                             | 116 |

| D.4.3. TOR                                                              | 119 |

| D.4.4. TAND                                                             | 121 |

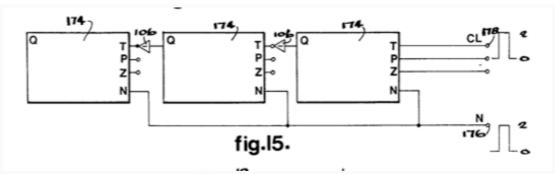

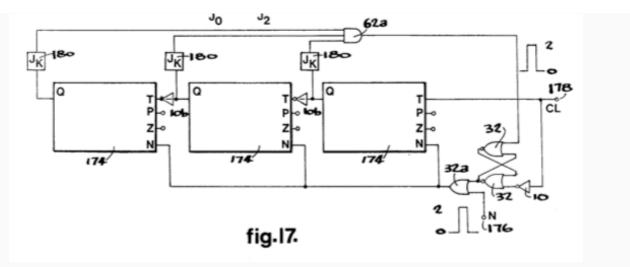

| D.5. Flip-flap-flops                                                    | 122 |

| D.5.1. PZN Tri-Latch                                                    | 123 |

| D.5.2. PZN Tri-Flop                                                     | 124 |

| D.5.3. T-Type Tri-Flop with PZN Inputs                                  | 125 |

| D.5.4. D Tri-Latch                                                      | 126 |

| D.5.5. D Tri-Flop                                                       | 127 |

| D.5.6. Rising-Edge Triggered Master-Slave D Tri-Flop: Mouftah's Version | 128 |

| D.5.7. Rising-Edge Triggered Master-Slave D Tri-Flop                    | 133 |

| D.6. Ring Oscillator                                                    | 137 |

| D.7. 1:3 Decoder                                                        | 138 |

| D.8. 3:1 Multiplexer                                                    | 141 |

| D.8.1. 3:1 Multiplexer Tested on Breadboard | 143 |

|---------------------------------------------|-----|

| D.8.2. 3:1 Multiplexer Tested on PCB        | 147 |

| D.9. Untested Circuits                      | 149 |

| D.9.1. Trinary to Binary Converter          | 149 |

| D.9.2. AND-OR-INVERT                        | 149 |

| D.9.3. Counters                             | 150 |

| D.9.4. Memory                               | 151 |

| D.9.5. Other                                | 153 |

| D.10. Works Cited                           | 155 |

| E. Circuit Construction                     | 161 |

| E.1. Layout                                 | 162 |

| E.2. Footprints                             | 162 |

| E.3. Chip Maps                              | 163 |

| E.4. Interconnects                          | 164 |

| E.4.1. TCA2                                 | 165 |

| E.4.2. TCA0                                 | 165 |

| E.5. Boards                                 | 167 |

| E.5.1. ROM Boards                           | 168 |

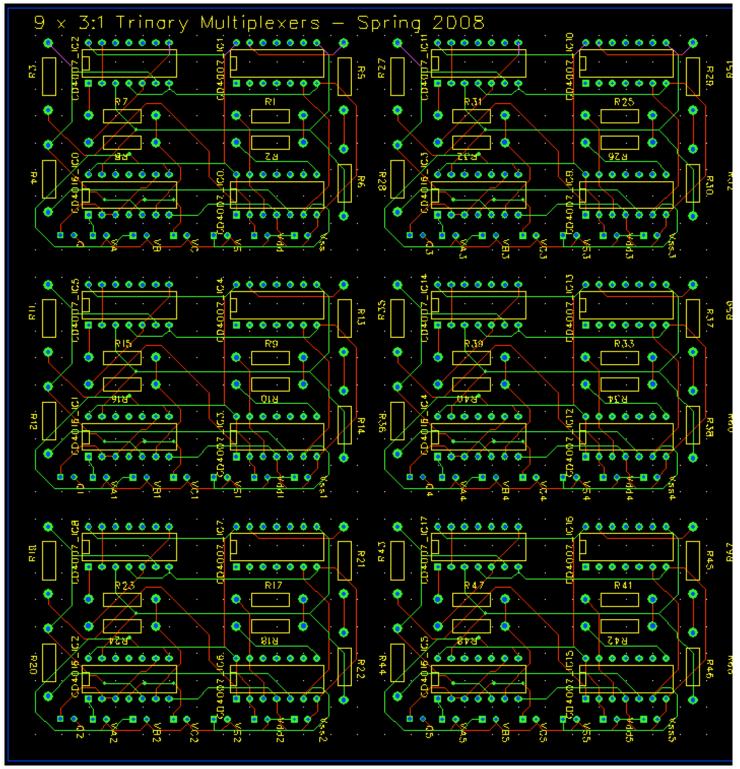

| E.5.2. Multiplexer Boards                   | 169 |

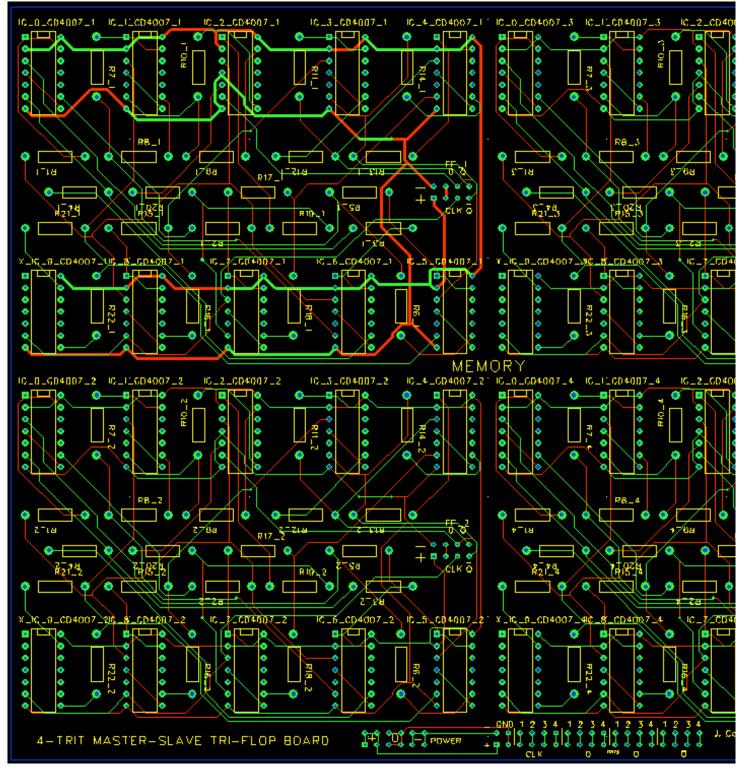

| E.5.3. Memory Board                         | 170 |

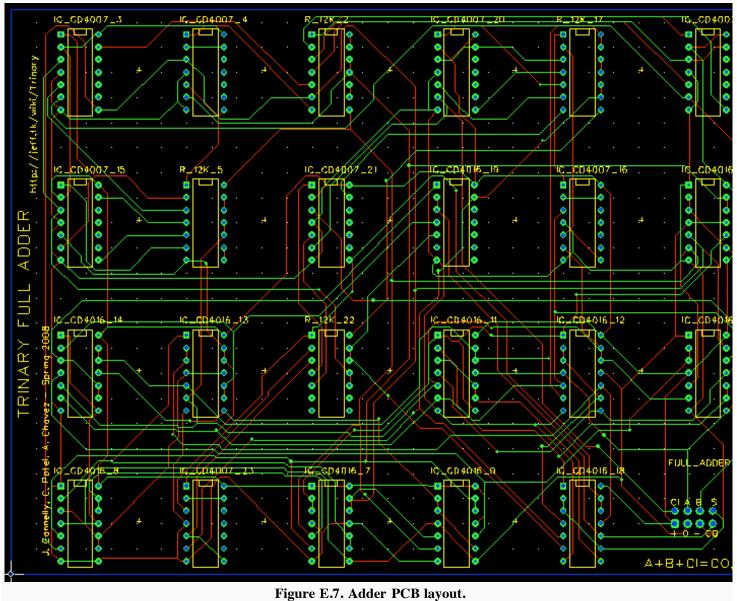

| E.5.4. Adder Board                          | 171 |

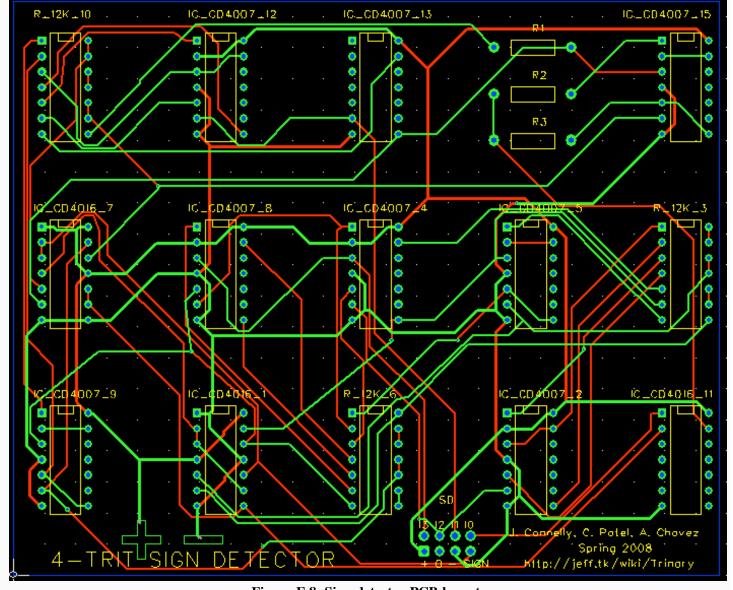

| E.5.5. Sign Board                           | 172 |

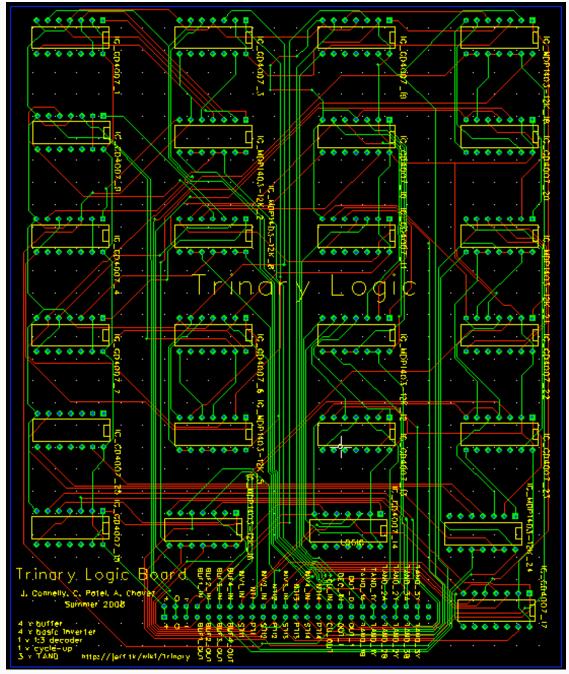

| E.5.6. Logic Board                          | 173 |

| E.6. Works Cited                            | 174 |

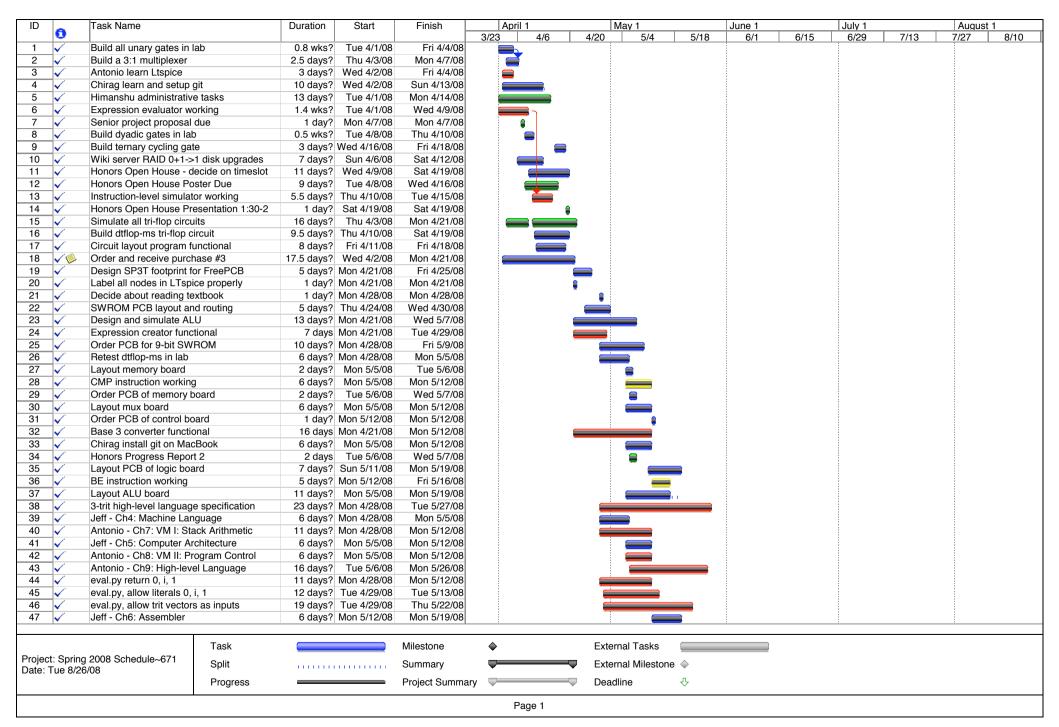

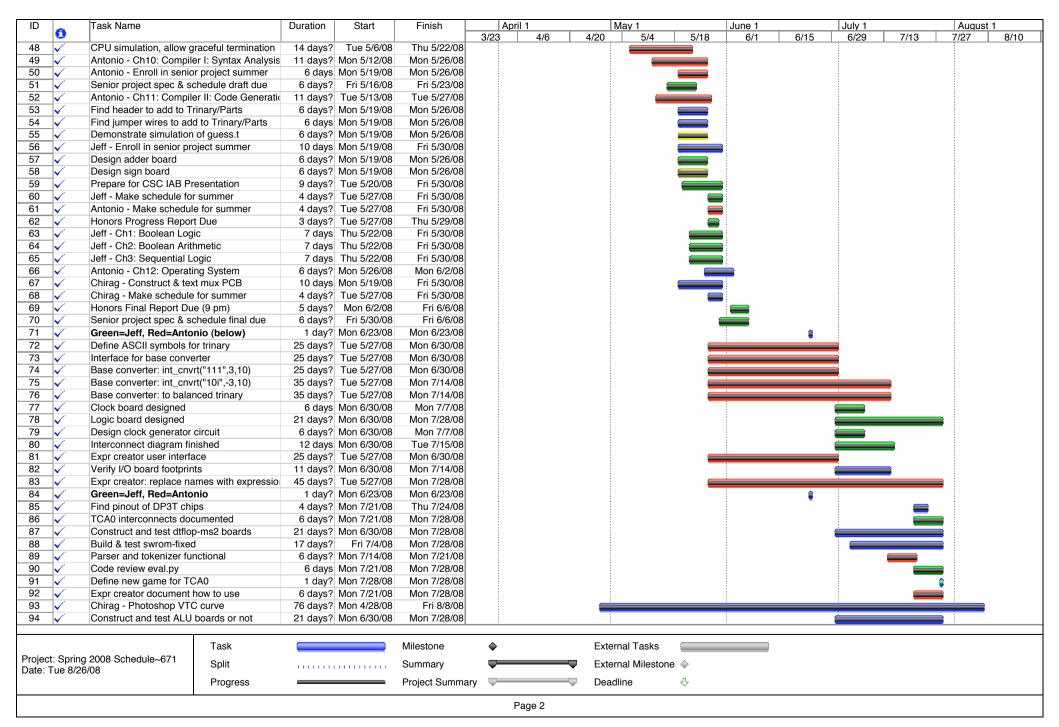

| F. Schedule                                 | 182 |

# 1. Introduction

As the computing industry advances, researchers are discovering new and innovative ways to increase computer processor performance, rather than strictly adhering to the traditional technique of increasing chip density. Some techniques, such as multi-core processors, build upon well-established binary circuit systems, while other technologies such as quantum computing require a radical rethinking of the foundations of computer science. Our team researched a middle-ground by building a functional computer based on base 3 or *trinary* (synonymous with *ternary*) logic. Trinary computers are digital as are binary computers, but are not as extreme departure from classical computing technologies as quantum computers. Trinary technology is relatively unexplored territory in the computer architecture field.

The trinary numbering system itself has numerous interesting properties that make building trinary-based digital circuits an attractive proposition from an efficiency perspective (2.1). Although trinary logic is significantly more complex than binary logic, the addition of the third logic state opens up exciting new possibilities (appendix **A**). Additionally, from trinary naturally follows "balanced trinary arithmetic", a numbering system using digits -1,0, and 1. Esteemed Computer Scientist Donald Knuth describes balanced trinary as "the prettiest number system of all" for its elegant arithmetic properties (appendix **B**).

Nonetheless, trinary computer systems are not a new idea. In as early as 1959, trinary computers have been built, simulated, or imagined (appendix C), to varying degrees of completeness and practicality. In this project, our team set out to design and build a complete trinary computer that is capable of running a simple game (section 3). I began designing logic gates at the transistor level, and then built upon the gates to design memory and control circuitry (appendix D). Layered further on top, I implemented and designed high-level architectural components (section 4) including an instruction memory/decoder, registers, a control unit, and an Arithmetic Logic Unit. In the end, the components culminate in a processor that can execute programmed instructions in a 3-trit assembly language (section 4.5.7). A compiler for the high-level programming language which compiles into the trinary assembly language is part of the Ternary Computing Testbed project, but out of the scope of this report. Although I also helped with the physical construction of the computer, this report focuses on my primary contribution to trinary computing: the implementation of a practical Ternary Computing Architecture. Our hope is to inspire a change in the foundation of the computer architecture industry which will lead to more efficient computer systems.

In the end, I achieved the goal of designing a complete trinary computer capable of running a simple numerical guessing game. The transistor-level architecture design successfully simulates in the LTspice circuit simulation program and behaves as expected.

# 1.1. Method

Our practices were inspired by Shimon Schocken's workshop on computer construction, often offered as a college course titled "From NAND to Tetris", taught along with a book written by the instructor<sup>[2]</sup>. Schocken's course is composed of several units, ascending from low-level logic gates and architecture to high-level application programming concepts. We followed a similar bottom-up approach, beginning with trinary logic, trinary arithmetic, sequential logic and computer architecture, up to writing a assembly-language game running

on a trinary computer.

## 1.2. Plan

We, the Ternary Computing Testbed team, met weekly with our advisor to discuss our progress and our plans. Each of us posted weekly status reports online<sup>[3]</sup> along with weekly individual status reports<sup>[4]</sup>.

In addition, we posted our research findings on a publicly-viewable wiki<sup>[5]</sup>.

This interdisciplinary senior project built on our Honors research project started in Winter 2008, applying what we have learned in our efforts to research existing research in trinary, in order to construct a functional trinary computer system.

# 1.3. Team and Individual Responsibilities

The Ternary Computing Testbed team is composed of Jeff Connelly, Antonio Chavez, and Chirag Patel. You are reading Jeff's report, which also includes documentation of Chirag's efforts since he is not doing a senior project. Antonio's report will be submitted as a separate senior project report, although references to it will be made in this report when appropriate.

## 1.3.1. Jeff Connelly

Jeff's tasks include designing and simulating the complete trinary architecture to be constructed by Chirag, writing software for the trinary computer, and helping Chirag construct and test circuits.

#### Deliverables:

- A wiki documenting our research and progress<sup>[5]</sup>

- Transistor-level SPICE simulation of complete 3-trit CPU architecture circuits and associated components, running a simple game (section **4.5.7**)

- An assembly-language implementation of a simple game to run on the trinary computer

#### 1.3.2. Antonio Chavez

Antonio's tasks include developing software to support construction of the trinary computer, instruction-level simulators of a simple and extended architecture, and a high-level language compiler for a custom trinary computer architecture.

#### Deliverables:

- Several utility tools<sup>[6]</sup> were developed to support our work:

- Arbitrary trinary expression evaluator

- Expression creator

- Radix converter

- Instruction-level CPU simulators<sup>[7]</sup>

- Simulator of 3-trit architecture that Chirag and Jeff build.

- Simulator of an expanded trinary architecture, designed by Antonio

- Compiler<sup>[8]</sup>

• Design a language and implement a compiler for a high-level language using trinary.

While Antonio is part of the team effort, he will submit a separate Senior Project report since his work significantly diverges from ours.

## 1.3.3. Chirag Patel

Chirag's tasks include physically building and testing trinary circuits for logic gates, storage elements, control units, and all other circuitry.

#### Deliverables:

• A physical trinary computer running a simple game

While this work is not Chirag's senior project, relevant portions of his progress will be covered in this report as we worked together extensively and our work is related in that Jeff's simulated architectures are being physically built in hardware by Chirag.

# 2. Background Theory

# 2.1. Base 3

Base 3 is any weighted numbering system that uses three digits. Familiarity with positional numbering systems [9], including binary and decimal, is assumed throughout this document.

Before delving into the technical details, a word on terminology is in order. Base 3 is traditionally known as *ternary*. In this report, I use the term *trinary* over *ternary* or *tertiary*, as a homage to Steve Grubb's Trinary.cc web site. Merriam-Webster defines ternary as "Composed of three or arranged in threes, having the base three." while trinary is defined as "Consisting of three parts of proceeding by threes; ternary.", and tertiary as "Third in place, order, degree, or rank". Although they are nearly synonyms, tertiary would be more appropriate if base 2 was called *secondary*. This naming ambiguity also arises in programming languages such as C and Perl which have a *ternary* or *trinary* operator, often spelled "?:". Although some in the community prefer the term *ternary*<sup>[10]</sup> Larry Wall, the creator of Perl, in Apocalypse 3<sup>[11]</sup> as well as in *Programming Perl*<sup>[12]</sup>, uses the term *trinary*. In this paper, I prefer *trinary* as well, although *ternary* will occasionally be used in contexts where it is common.

In the following sections, I will compare the benefits and disadvantages of trinary to several alternatives.

# 2.1.1. Compared to Analog

The earliest known computer is the *Antikythera mechanism*, an analog mechanical computer designed to calculate astronomical positions, found in Greece and dating to *circa* 100 BC<sup>[13]</sup>. In more recent times (*circa* 1943), the TDC Mark III electromechanical analog computer was used in U.S. submarines during World War II to aim torpedoes<sup>[14]</sup>:

Figure 1. TDC Mark III, 1943<sup>[14]</sup>

Electrically, operational amplifiers can be used in an analog computer to perform integration, differentiation, root extraction, multiplication/division, logarithm, and anti-log operations<sup>[15]</sup>. Although analog computers played an important historical role<sup>[16]</sup>, they have the significant disadvantage that noise can unpredictably affect the results of a computation<sup>[17]</sup>. Following the development of digital computers, analog computing quickly fell out of mainstream usage<sup>[14]</sup>. Although trinary computers are not immune to noise, they are significantly more resistant than analog computers because discrete voltage levels are used. Any voltage within a quantifiable range is accepted as signifying a given logic state (section **D.3.1**).

# 2.1.2. Compared to Digital

A digital computers is defined as storing data in terms of discrete states and having execution proceed in

discrete steps from one state to the next<sup>[18]</sup>. Early digital computers used ten voltages, that is, base 10 or *decimal*. Atanasoff<sup>[19]</sup> came up with the idea in the 1930s of using two voltage levels, or *binary*:

Atanasoff was thinking about computers. There were already mechanical and analog computers. But Atanasoff thought there might be better methods of computing. He drove from dry Iowa to a bar over the Illinois line, drank three Scotch and waters, and had a *Eureka!* moment. "That's when he figured out he could do everything in base 2," Gustafson says. Base 2 is digital. It's 1s and 0s. Previous computers worked in base 10. "He jotted on a cocktail napkin all the basic principles of modern computing."

In 1938, Claude E. Shannon published his master's thesis describing how the *true* and *false* notions of George Boole's (1847—1854) *Boolean Algebra* could be mapped to the two logic levels of a binary digital computer<sup>[20]</sup>. The rest, as they say, is history. Digital binary computers are the most prevalent computing technology available today, by far.

Digital computers have the advantage of computational accuracy over analog computers. The two discrete voltage levels allow for some variation due to noise or other environmental factors, without changing the outcome of a calculation. Barring a significant disturbance (such as *cosmic ray* interference<sup>[21]</sup>), digital computers perform accurate calculations. Like base 10 and 2, base 3 is digital and therefore benefits from the properties of having discrete voltage levels.

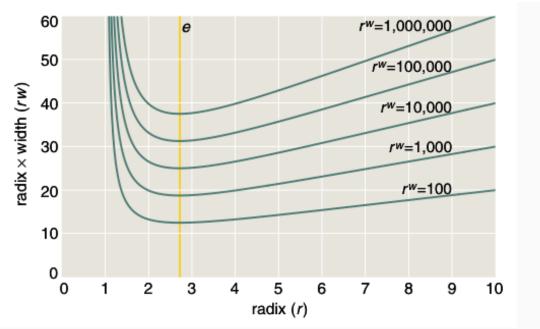

## **2.1.3.** Compared to Base e

Given a set of assumptions outlined in [22], base e is the most efficient base for representing arbitrary numbers. If one measures cost as the radix (base, or r) times the number of digits ("width", or w), on the grounds that greater widths require proportionally more circuitry, and higher radices require proportionally more complex circuitry. That is, a 16-digit number will require twice the amount of circuitry as a 8-digit number; additionally, the assumption is that base 4 (for example) requires twice as complex circuitry as base 2, and base 3 requires 3/2 or 1.5 times as complex circuitry as base 2, for an abstract definition of complexity. These assumptions are revisited in section 5.

3 is the closest integer to e (2.718...)—closer than 2—therefore, the reasoning is that base 3 is more efficient than base 2 when used to build digital systems.

The following figure from [22] shows how base e occupies the local minimum of a graph plotting cost (as previously defined), for numbers of several magnitudes:

Figure 2. "Most economical radix for a numbering system is (about 2.718) when economy is measured as the product of the radix and the width, or number of digits, needed to express a given range of values. Here both the radix and the width are treated as continuous variables." [22]

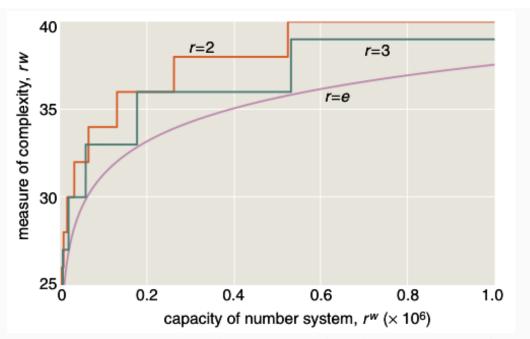

Additionally, base 3 is the most efficient integer base. As shown below, the cost of 3 closely follows that of base e, whereas base 2 is significantly more costly in many instances:

Figure 3. "[The] most economical integer radix is almost always 3, the integer closest to e. If the capacity of a numbering system is  $r^w$ , and the cost of a representation is rw, then r=3 is the best integer radix for all but a finite set of capacities. Specifically, ternary is inferior to binary only for 8,487 values of rw; ternary is superior for infinitely many values." [22]

A. Srivastava and K. Venkatapathy<sup>[23]</sup> have found that multi-valued logic allows for significantly increased performance, largely because of the reduced number of interconnects. Srivastava also came to the same conclusions as in *Third Base*—base 3 is more efficient than base 2—assuming that cost is measured as radix times width. The relevant portion of the paper is quoted in full below:

The performance of two levels (binary logic) is limited due to interconnect which occupies large area on a VLSI chip. In a VLSI circuit, approximately 70 percent of the area is devoted to interconnection, 20 percent to insulation, and 10 percent to devices<sup>[24]</sup>. One can achieve a more cost effective way of utilizing interconnections by using a larger set of signals over the same area in multiple-valued logic (MVL) circuits. This also solves the problem of pinout (the limit to the amount of data that can enter and exit a chip). Commercially multiple-valued logic circuits have made an appearance with the four-valued read-only memory (ROM) which Intel used in the control store of its 8087 numeric coprocessor<sup>[24]</sup>. Hitachi has introduced into the market a 16-valued mass memory with a high storage capacity. Kameyama et al.<sup>[25]</sup> reported a 32 x 32 bit signed digit (SD) multiplier implementation using MVL circuits realized in current-mode CMOS technology. The chip area and power dissipation of MVL multiplier implementation reduced to half that of the fastest conventional binary realization of the same multiplier.

The main draw back in multiple valued logic circuits is that their design techniques are more complex than the binary logic circuits<sup>[26]</sup>. The implementation of MVL circuits have ranged through integrated injection logic, emitter coupled logic, CMOS and n-MOS technologies and charge-coupled devices. In this work, the design of ternary-valued logic circuits have been explored over other ternary-valued logic due to the following reasoning. In a numerical system, the number N is given by  $N = R^d$  where R < i is the radix and d is the necessary number of digits up to the next highest integer value where necessary. If the cost or complexity C in any system is assumed to be proportional to  $R \times D^{[27]}$ , then  $C = k(R \times d) = k[R(\ln N/\ln R)]$  where k is some constant. Differentiating with respect to R will show that for a minimum cost C, R should be equal to e(2.718). Since in practice R must be an integer, this suggests that R = 3(ternary) would be more economical than R = 2(binary)<sup>[28]</sup>

Srivastava and Venkatapathy were not the only ones to come to these conclusions. Dhande and Ingole<sup>[29]</sup> have also found that base 3 is the most efficient radix for switching circuits, because of the following reasons:<sup>[30]</sup>

- Base 3 reduce the interconnections required to implement logic functions.

- Base 3 therefore reduces chip area.

- Base 3 allows more information to be transmitted over a given set of lines.

- Base 3 has a lower memory requirement for a given data length.

- Serial operations can be carried out at a higher speed [31][32]

The advantages of base 3 have been confirmed in digital memories, communications components, and the field of digital signal processing<sup>[33]</sup>. Our research extends the concept of base 3 to the field of computer architecture.

# 2.1.4 Trits, Tribbles, and Trytes

Before we delve too deeply into trinary computing systems, additional terminology definitions are in order. In the binary world, bits, nibbles, and bytes are household names<sup>[34]</sup>. As for trinary, the analogous names for base 3 have not been standardized.

Analogous to bits, *trits* are base 3 digits. The term *tert* is also occasionally used, but it will not be used in this paper.

The *TriINTERCAL programming language* defines unsigned 10-trit (0 to 59048) and 20-trit words. The ranges of the 10- and 20-trit numbers are remarkably close to their 16- and 32-bit counterparts. 16 bits store as much as  $16*(\log(2)/\log(3)) \approx 10.0949$  trits, and 32 bits store as much as  $32*(\log(2)/\log(3)) \approx 20.1898$  trits. Following

the pattern, 64 bits are about 40.3795 trits. However, base 2 word sizes are almost always powers of 2. Therefore, I suggest using powers of base 3 for word sizes, grouping the trits as follows:

**Table 1. Trit Grouping Names**

|    |     | Digits, base 27 | Max.<br>(decimal, 3 <sup>trits</sup> - 1) | Name        | Description                         |

|----|-----|-----------------|-------------------------------------------|-------------|-------------------------------------|

| 1  | 1/3 | 1/27            | 2                                         | trit        | Relatively well-established.        |

| 2  | 1   | 2/3             | 8                                         | nit         | One base-9 digit.                   |

| 3  | 3/2 | 1               | 26                                        | tribble     | Half of a tryte, one base-27 digit. |

| 6  |     | 2               | 728                                       | tryte       | Analogous to a byte.                |

| 9  |     |                 | 19,682                                    | not defined | not defined                         |

| 27 |     |                 | 7,625,597,484,986                         | not defined | not defined                         |

There has been much informal discussion about trinary digit groupings on Slashdot<sup>[35]</sup>, rather than peer-reviewed journals, but I believe these make the most sense based on extrapolating the terminology used for binary (at least, one person<sup>[36]</sup> agreed). In the architecture I designed (section 4), the natural *word size* that all operations operate on is 3 trits, or one tribble.

In binary, the two states often correspond to 0 and 1, or *true* and *false*. As discussed in depth later in this document (appendix  $\bf A$  and  $\bf B$ ), the three states in trinary can be defined as the following:

**Table 2. Trinary Digits**

| Table 2. It mary Digits |                               |  |  |  |  |  |  |  |  |

|-------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| Set                     | Name / comments               |  |  |  |  |  |  |  |  |

| {0,1,2}                 | Unbalanced Trinary            |  |  |  |  |  |  |  |  |

| {0,1/2,1}               | Fractional Unbalanced Trinary |  |  |  |  |  |  |  |  |

| {-1,0,1}                | Balanced Trinary              |  |  |  |  |  |  |  |  |

| {F,?,T}                 | Unknown-State Logic           |  |  |  |  |  |  |  |  |

| $\{T,F,T\}$             | Trinary Coded Binary          |  |  |  |  |  |  |  |  |

The most common trinary digit mappings are  $\{0,1,2\}$  (unbalanced) or  $\{-1,0,1\}$  (balanced). Of these,  $\{-1,0,1\}$  can be defined as  $\{F,?,T\}$  where ? is unknown (simultaneously T and F)—this is hereby termed "Unknown-State Logic" (USL) and the logical properties of USL are covered in section **A.7**. The set  $\{0,1/2,1\}$  is mentioned by Merrill<sup>[37]</sup> but is not covered here, and it can be thought of as simply  $\{0,1,2\}$  (unbalanced) with half the logic level quantities. Lastly, the set  $\{T,F,T\}$  strictly maps trinary digits to binary, and it is expected to be useful for interfacing with binary systems<sup>[38]</sup>.

We chose to use balanced trinary when possible, because of its obvious mapping to electrical voltages: -1 negative, 0 neutral, 1 positive. It is useful to represent -1 as a single digit so it lines up properly in fixed-width text. There are several conventions that have been defined:

- Merrill<sup>[37]</sup> used T for -1. "T" is like 1 with a negative sign on top of it, but it unfortunately could be too easily mistaken for "True".

- Setun used i for  $-1^{[39]}$ . This is what will be used when no special formatting is possible. i is also used to represent the square-root of -1, so there is some pre-existing convention here.

- Knuth<sup>[1]</sup> uses 1 with an overline. This is the convention I have adapted in this document:  $\overline{1}$ . I developed

an extension for the wiki we used to automatically overbar the i symbols if they are enclosed within the  $\langle \text{trits} \rangle$  tag.

For details on how arithmetic operations can be performed on balanced trinary numbers, refer to section **B.1**.

## 2.1.5. Base 9 and 27

As in binary computing where one *octal* digit is 3 bits and one *hexadecimal* digit is 4 bits, in trinary computing it is useful to define conventional bases to compactly represent a sequence of trits.

If  $a^n = b$ , then one base b digit holds n base-a digits. Since  $3^2 = 9$ , one ninary (base 9) digit represents 2 trits. Groups of 2 trits can be converted directly to a ninary digit and vice versa as follows:

| Tern<br>N | able 3. nary and onary, oalanced | Table 4. Ternary and Nonary, Balanced |                                    |  |  |  |

|-----------|----------------------------------|---------------------------------------|------------------------------------|--|--|--|

| Base      | e 3 Base 9                       | Base                                  | 3 Base 9                           |  |  |  |

| 00        | 0                                | 11                                    | $\overline{4}$ , $\textcircled{4}$ |  |  |  |

| 01        | 1                                | 10                                    | $\overline{3}$ , $\overline{3}$    |  |  |  |

| 02        | 2                                | <del>1</del> 1                        | $\overline{2}$ , ②                 |  |  |  |

| 10        | 3                                | $0\overline{1}$                       | $\overline{1}$ , ①                 |  |  |  |

| 11        | 4                                | 00                                    | 0                                  |  |  |  |

| 12        | 5                                | 01                                    | 1                                  |  |  |  |

| 20        | 6                                | $1\overline{1}$                       | 2                                  |  |  |  |

| 21        | 7                                | 10                                    | 3                                  |  |  |  |

| 22        | 8                                | 11                                    | 4                                  |  |  |  |

For example, using the table above, one can determine that  $2021_3 = 67_9$ , or in a balanced numerical system:  $11 = 4\overline{2}_9$ . Unbalanced base 9 uses digits [0..8]. In the table above, an overbar is used over negative digits.

Setun<sup>[39]</sup> pioneered the use of upside-down 4,3,2,1 and right-side up 0,1,2,3,4 for balanced base-9, but the Unicode character standard does not define such symbols<sup>[40]</sup> so they cannot be easily represented on a modern computer system. Therefore, I chose single-character representations of the negative digits 1-4 to be the digits *circled*, shown above, starting from Unicode character U+2460.

Although one ninary digit represents two trits, greater compactness is desirable for writing longer sequences of trits. Since,  $3^3 = 27$ , in base 27 (which unfortunately lacks a catchy name), three trits represent one base-27 digit. *Unbalanced base 27* uses the characters [0..9] in addition to [A..S], excluding I and O to avoid confusion between 0 and 1, as follows:

Table 5. Unbalanced Ternary and 27-uary

|    |     |     |     |     | 11/0 001 |     |     |     | <u> </u> |     |     |     |     |     |

|----|-----|-----|-----|-----|----------|-----|-----|-----|----------|-----|-----|-----|-----|-----|

| 3  | 000 | 001 | 002 | 010 | 011      | 012 | 020 | 021 | 022      | 100 | 101 | 102 | 110 |     |

| 27 | 0   | 1   | 2   | 3   | 4        | 5   | 6   | 7   | 8        | 9   | A   | В   | C   |     |

| 3  | 111 | 112 | 120 | 121 | 122      | 200 | 201 | 202 | 210      | 211 | 212 | 220 | 221 | 222 |

| 27 | D   | E   | F   | G   | Н        | J   | K   | L   | M        | N   | P   | Q   | R   | S   |

In *balanced base-27*, digit values range from -13 to +13 and use symbols 0 through 9, A through D (table not shown). Negative digits are represented with overbars over the digits.

One base-27 digit is equivalent to exactly  $1.5 = 3/2 = \log 27(9)$  base-9 digits.

Any power-of-3 radix higher than 27 is impractical for human usage due to the large number of glyphs that would be required (81 for 3<sup>4</sup>), but base 27 is highly practical and useful for compact trit representation.

## 2.1.6. Text

For text on conventional 8-bit binary systems, 7-bit ASCII is a common choice. The 8<sup>th</sup> bit is variously used for additional characters in "extended ASCII" character sets, of which there are too many conflicting incompatible standards, or to indicate that a character code point greater than 7 bits is approaching (as with UTF-8, a Unicode encoding). With trinary, we are not limited by 8 bits, and 8 digits is rather small. It therefore makes sense to choose a character size big enough for Unicode characters, making Unicode the textual standard rather than ASCII. Unicode uses 21-bit code points up to 2,097,151 to define a repertoire of more than 100,000 standard characters. The Internet Request for Comments document #4042<sup>[41]</sup>, released on April 1st of 2005, defines Unicode Transformation Formats UTF-9 and UTF-18 that would be suitable for usage on an advanced trinary computer. All of the encodings are able to map the full set of characters using varying methods.

# 2.2. Logic and Arithmetic

There is much to be said about the logical and arithmetic aspects of a trinary-based computer system. Please refer to Appendix  $\bf A$  and  $\bf B$  for a detailed analysis.

# 3. Application Description

As described in the introduction, the end goal of this project is to build a trinary computer running a simple game. This section discusses the high-level aspects of simple gaming applications that were developed.

# 3.1. Christmas Lights Game

The most trivial "game" that could be developed using a limited computer architecture is what I call the *Christmas lights game*. Although this game does not involve competition, it can provide amusement to young children and therefore is classified as a game.

In this game, the user is treated to a series of several multi-color LEDs. The LEDs sequence through a series of colors, as the instructions advance. The user can change the programming to experiment with an endless variation of Christmas light sequences, limited only the creativity of the programmer.

While simplistic, this game illustrates the programmability of the computer architecture. It is intended for use

on a physical implementation of the Trinary Computer Architecture, also known as *TCA0* (section **4.5.4**), as part of Chirag's tasks. This game has been successfully simulated in a transistor-level design using the LTspice circuit simulator, as detailed in section **4.5.4**.

# 3.2. Guessing Game

A slightly more sophisticated game is the classic *number guessing game*. In this game, the player inputs a number, and is told whether he or she is too high, too low, or just right.

The peripherals required by this game are:

- A multi-color LED indicating the result of guessing

- A 3-trit array of switches to enter your guess

The high-level procedure of this game is as follows:

- Loop:

- On power up, the system stores a secret number in a register (the number to guess)

- Loop:

- Compare input register from switches to the register that has the correct number

- Check status trit

- Status trit  $\overline{1}$ , too low.

- Status trit 0, got it right. Break out of inner loop and re-initialize the secret value.

- Status trit 1, too high.

The programming details of this game are explained later in the architecture section, where the architecture that is able to run this game (known as TCA2) is introduced. The "status trit" is wired to a multi-color LED that gives feedback on the guess to the user.

This game demonstrates user input, register storage, branching, and arithmetic. In order to compare the user input to the secret number, the computer system has to subtract the two values and check whether the result is negative, zero, or positive, indicating that the guess was too low, correct, or too high. If the guess is incorrect, the program immediately loops back to the comparison. However, if the guess is incorrect, the program loops back to the very beginning of the program and re-loads the secret number. The secret number is a fixed part of the software, but can be changed by reprogramming the software on the fly; although because of this looping construct, changing the secret value will not take affect until after the user has correctly guessed the previous value. This was done in order to demonstrate conditional branching.

In summary, this game demonstrates programmability, arithmetic computations, input/output, and conditional branching.

This program was successfully demonstrated on a transistor-level LTspice circuit simulation, as detailed in section **4.5.7**.

# 4. Architecture Description

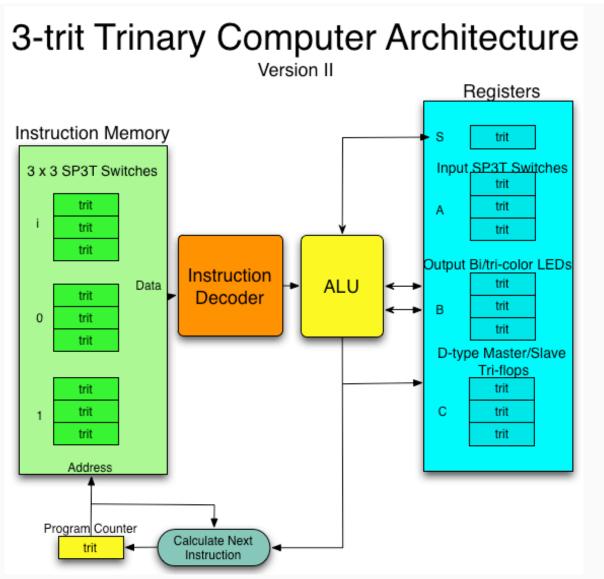

I designed several related Trinary Computer Architectures of varying complexity:

- **TCA2** is a complete 3-trit system, implementing compare, branch, and load instructions. It can successfully run a "guessing game program" in a transistor-level LTspice simulation as well as in a CPU instruction-level software simulation (see section **4.5.7**).

- TCA1 is an old prototype architecture obsoleted by TCA0 and TCA2.

- **TCA0** is a simplified proof-of-concept architecture, that has been simulated and is intended to be easily physically built in hardware. It only implements a load instruction. For overall architecture of TCA0, see section **4.5.4**.

Antonio Chavez designed a third, extended, architecture, TCA3, to be simulated only at the CPU instruction level (rather than the transistor-level), exploring higher-level trinary concepts. Antonio's architecture is covered in his own separate senior project paper and will not be discussed further.

# 4.1. Power Supply

All electrical computers require a source of electrical power to operate. Modern personal computers often have a power supply that outputs several voltages, but most of the current is drawn through a +5 V rail. The motherboard often steps down the voltage even further to power the processor, in order to reduce power consumption<sup>[42]</sup>. In either case, the processor power supply is one single voltage.

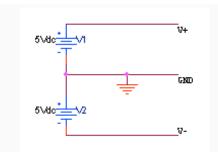

In our trinary computer, we used a dual-rail voltage supply of positive and negative voltages with equal magnitudes. Two supplies were connected back-to-back to provide +5 V, 0 V, and -5 V voltages, corresponding to logic 1, 0, and  $\overline{1}$ . For simulation purposes, I designed a component, known as tpower in the git repository, to provide this functionality:

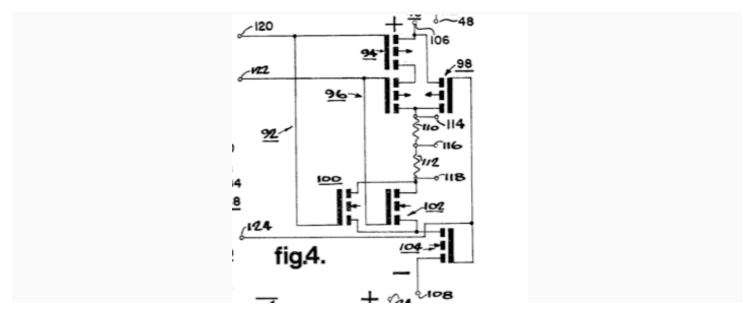

Figure 4. Trinary Power Supply

Alternatively, a suitable power supply can be constructed by supplying a single 10 V voltage, tying the negative side of the 10 V supply to the negative rail, and using a 1/2 voltage divider for ground. In our trinary computer, ground does have its uses, although it is not used as frequently as the positive and negative supply; nonetheless, we did not choose to implement the power supply this way for reasons of simplicity.

Within our circuitry, we used the node names \$g\_vdd and \$g\_vss to refer to the +5 V and -5 V rails, respectively. The "\$G\_" prefix informs the circuit simulation software we used (LTspice) that the nodes are "global", in that they traverse subcomponent hierarchies<sup>[43]</sup>. Doing this allows us to use the same power supplies for all electrical components, without having to wire power lines to each component within the simulation.

Logic levels are relative to ground for balanced trinary, but they can also be read relative to \$G\_Vss to convert to unbalanced trinary:

**Table 6. Relative Voltages**

| From | To  | Logic Level            |

|------|-----|------------------------|

| GND  | V-  | 1, balanced            |

| GND  | GND | 0, balanced            |

| GND  | V+  | 1, balanced            |

| V-   | V-  | 0, unbalanced          |

| V-   | GND | 1, unbalanced          |

| V-   | V+  | 2, unbalanced          |

| V+   | V-  | 2, inverted unbalanced |

| V+   | GND | 1, inverted unbalanced |

| V+   | V+  | 0, inverted unbalanced |

To convert balanced to unbalanced, 1 is added. The alternate system of converting between balanced and unbalanced, replacing  $\overline{1}$  with 2, as suggested in the TriINTERCAL manual<sup>[44]</sup>, was not used as it changes the meaning of the truth tables. For simplicity, we exclusively used balanced trinary within this computer architecture.

In the labs on campus, obtaining a steady +5 V and -5 V is easy using the Agilent DC power supply equipment, which was sufficient for our testing. However, to make the computer stand-alone, additional circuitry is needed to regulate the voltage from a battery or AC mains to the desired voltages.

We purchased<sup>[45]</sup> a handful of AA batteries intended to build the DC power supply, but due to time constraints we did not design a power circuit, instead preferring to use the available lab voltage supply equipment. However, a future task (beyond the scope of this senior project) could be to design, build, test, and integrate such a power supply with the rest of the computer system. I researched several ideas of how to best accomplish this:

- Use an LM317 adjustable voltage regulator chip with appropriate resistors to supply a 5 V output voltage with up to anywhere from about 37 V input or lower.

- Alternatively, use an LM7805 for a fixed 5 volt output, but without the flexibility to change the voltage later if we need to.

- Use a diode bridge rectifier on the input of the LM voltage regulator, to ensure that the polarity is correct.

- Connect the power from an AC wall outlet using almost any wall wart, using any connector.

- Power connectors are all different voltages, and some have a negative shield while some have a positive one. The regulator and diode bridge combination makes almost any old "wall wart" power supply acceptable. The power could also come from batteries.

- Alternatively, purchase 5 V wall wart power supplies and their appropriate connectors.

- An alternative power supply: 10 volts, with a voltage divider for 5 V to connect to ground. An All About Circuits posting [46][47] has some ideas using zener diodes to make a positive and negative voltage regulator.

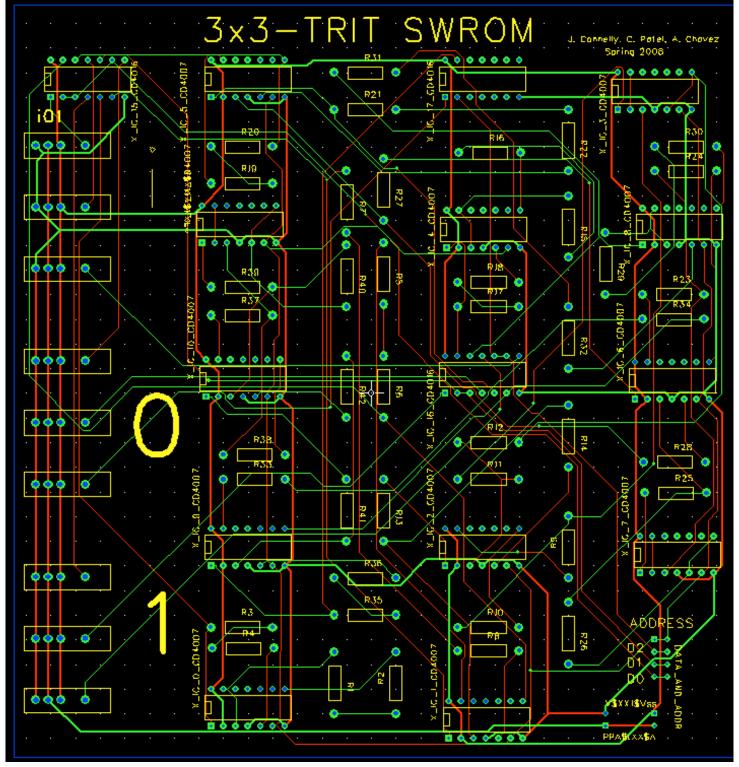

# 4.2. Instruction Memory

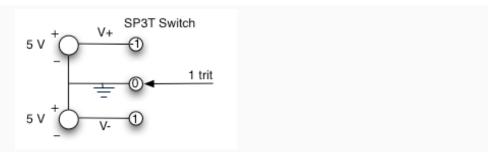

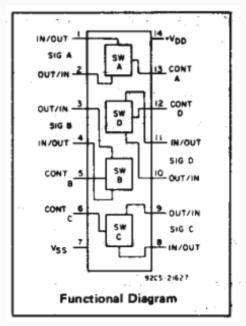

To simplify the design, the system has separate instruction and register memories. Instruction memory is ideally a bank of N triple-throw switches<sup>[48]</sup> for specific switches; I call this "SWROM" for switch-based

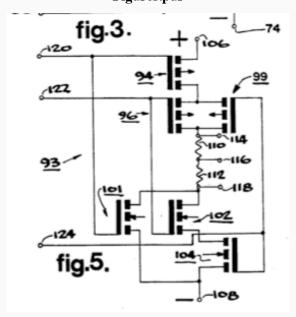

read-only-memory), with poles connected to 1, 0, and  $\overline{1}$ , labeled as such:

Figure 5. One Trit of Trinary Switch-ROM

The programmer can flip these switches to load a machine-language program into the computer. In the 3x3 SWROM, trits are grouped into 3-trit words, arranged horizontally, allowing 3 words to be programmed into the machine. However, due to time constraints in selecting a proper switch, our "switch ROM" instead is operated by plugging in wires into the appropriate holes of a breadboard.

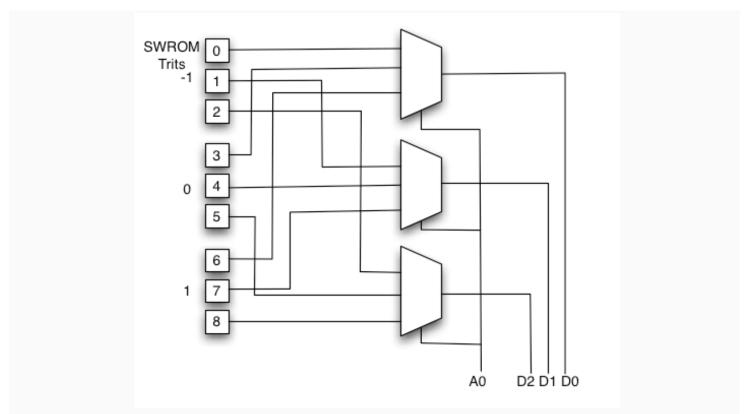

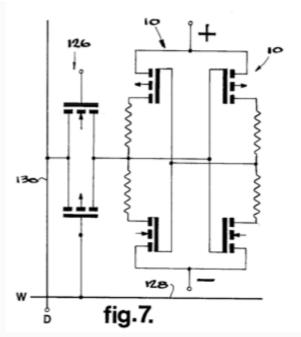

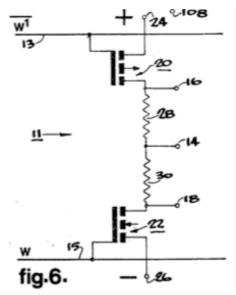

This memory with three addresses, addressing three trits each for a total of 9 trits, is constructed as follows:

Figure 6. 3x3 SWROM address decoder. The address (A0) determines which triplet of memory cells will be read onto the data lines D2, D1, and D0.

As an example, the following SWROM is loaded with a sequence of trits corresponding to an old version of the assembled guessing game program:

Figure 7. 3x3 SWROM loaded with guess.t trits.

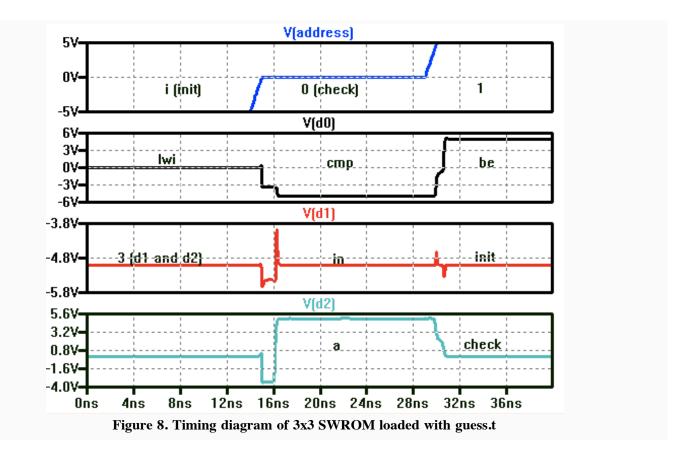

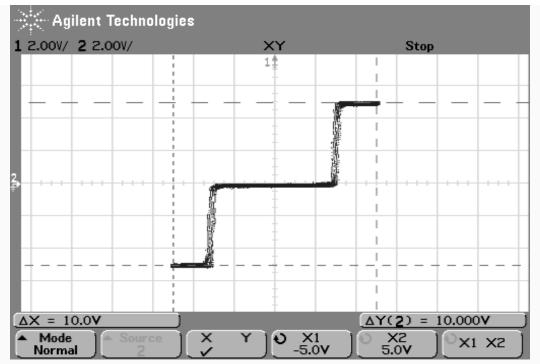

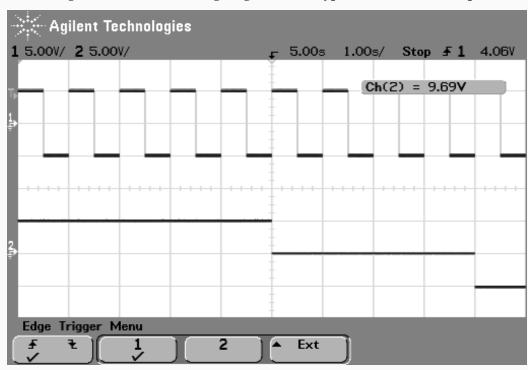

The SWROM behaves as expected during simulation when the address line is given several addresses to read from:

In the timing diagram above, the first address requested is  $\overline{1}$ , which outputs trits for the lwi -3 instruction, as shown. Address 0 outputs cmp in, a and address 1 outputs be init, check. "init" and "check" are labels that refer to addresses  $\overline{1}$  and 0, respectively. Note that since this timing diagram was made, PC has been made to start at 0, and the instructions and labels have shifted around appropriately.

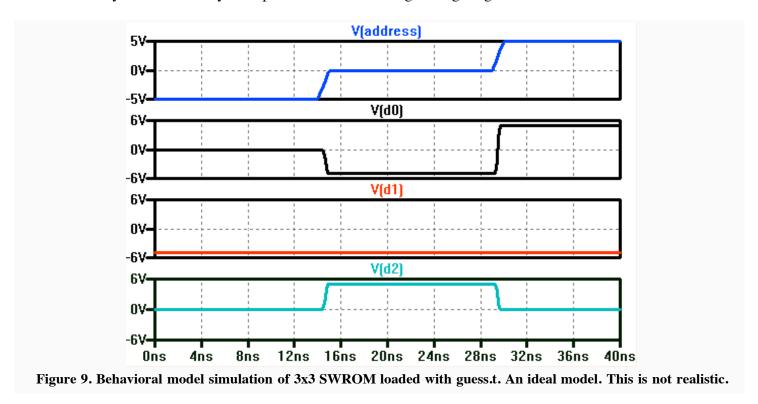

The completed SWROM can be simulated at the transistor level (as it is above), but it takes a few seconds to complete. For faster simulation, I developed swrom-fast. This component is a behavioral model that uses B-sources in LTspice, which describe the voltage mathematically rather than using electrical components. It simulates nearly instantaneously, and produces the following timing diagram:

swrom-fast can load arbitrary assembly programs, compiled into an .sp file with asm/asm.py.

# 4.2.1. Experimental Results

Although we designed and constructed a switch ROM printed circuit board, due to time constraints were not able to have a working board with triple-pole switches soldered on to it for easy reprogramming. As stated above, instead the computer can be programmed by manually plugging in wire corresponding to each data line into the appropriate holes of the breadboard:  $G_Vdd$ , ground, and  $G_Vs$  for 1, 0, and  $\overline{1}$ .

# 4.3. Program Counter

The *program counter*, or PC, is a 1-trit rising-edge triggered master-slave D-type tri-flop register (refer to section **D.5.6** for detailed information on this component) initialized to 0. The PC cycles through  $0, 1, \overline{1}$  using the cycle up gate. Note that PC does *not* start up at  $\overline{1}$  and sequence through  $\overline{1}, 0, 1$ , but rather  $0, 1, \overline{1}$ . Program execution starts at 0 instead of  $\overline{1}$  because registers start at 0 on power-up, and it would require additional

hardware to initialize it to  $\overline{1}$  (although asynchronous resets would be particularly useful to tie to a global RESET signal, such a feature is out of the scope of this project).

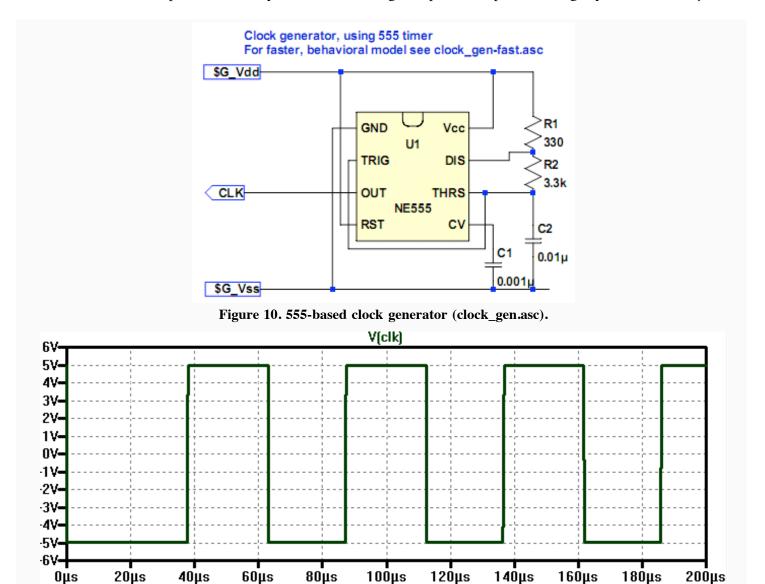

# 4.4. Clock Generator

TCA2 requires a two-phase clock, with signals named FETCH and EXECUTE, each the inverted version of each other.

The clock\_gen-fast component includes an LTspice PULSE voltage source with a fixed period and a 50% duty cycle for EXECUTE, and an inverter to generate FETCH. It is so named because it simulates quickly since the signals are generated by the simulator using mathematical expressions, rather than electrical models of physical components.

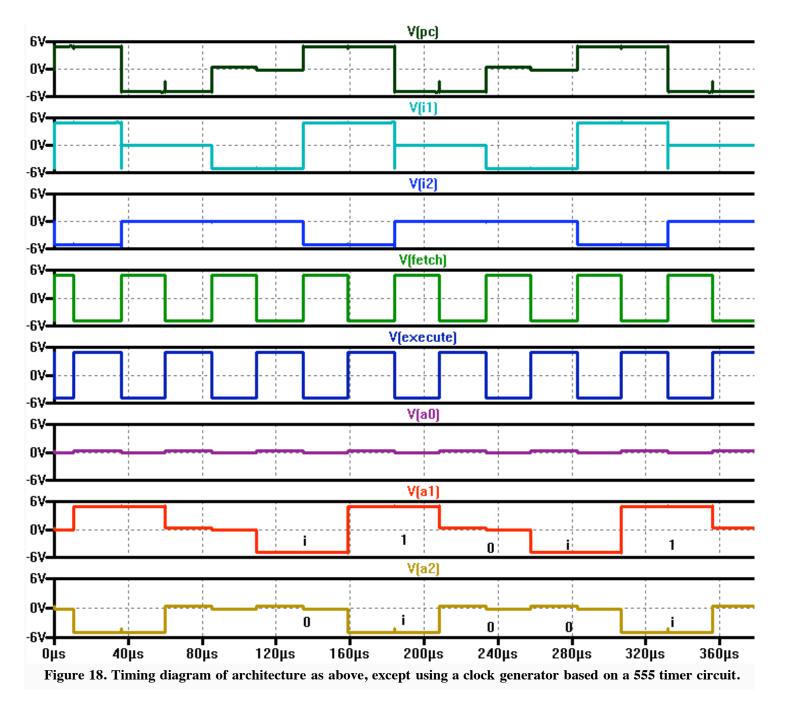

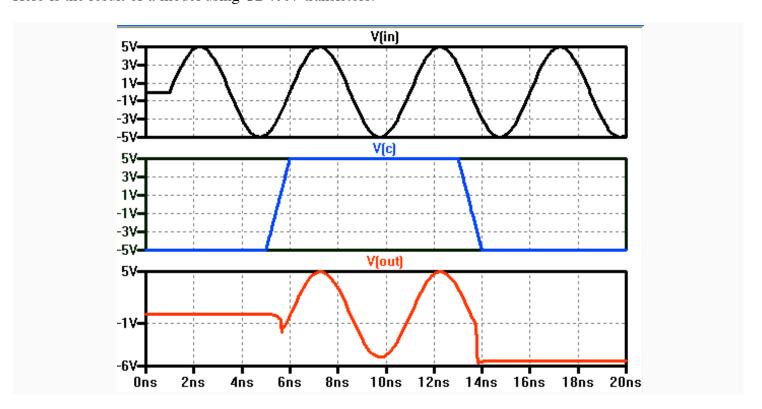

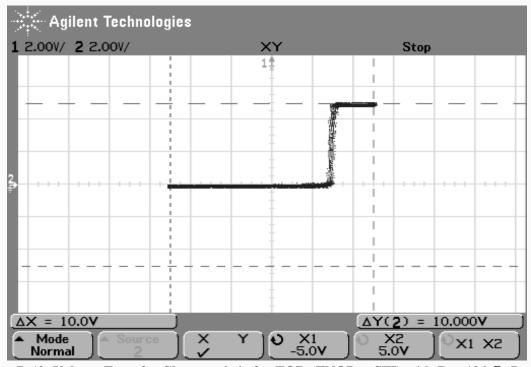

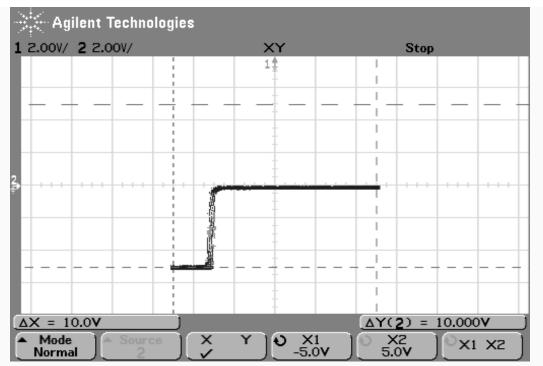

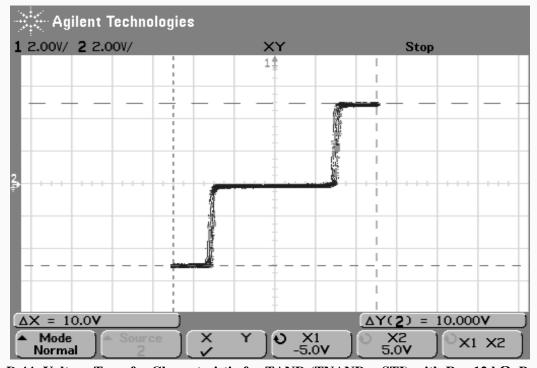

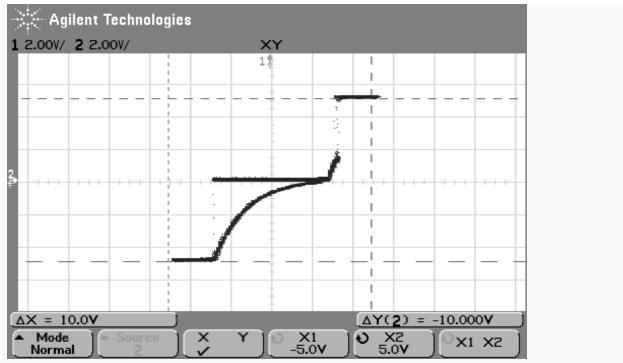

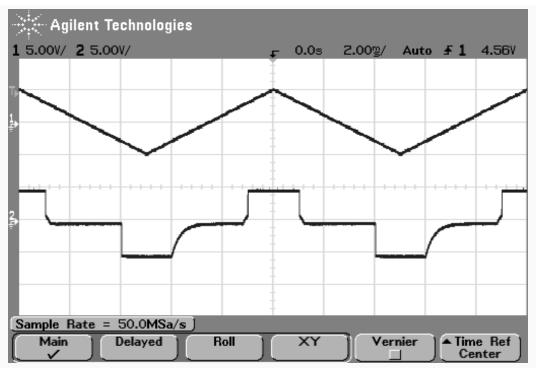

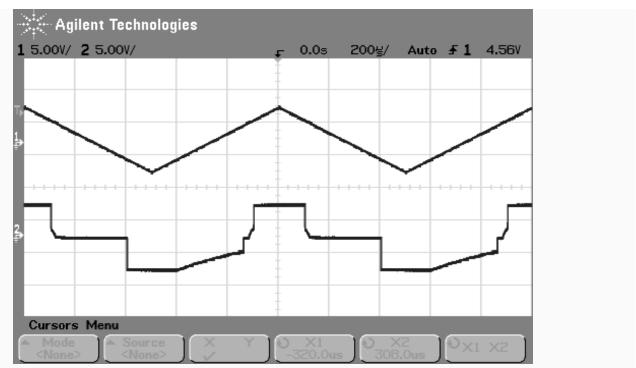

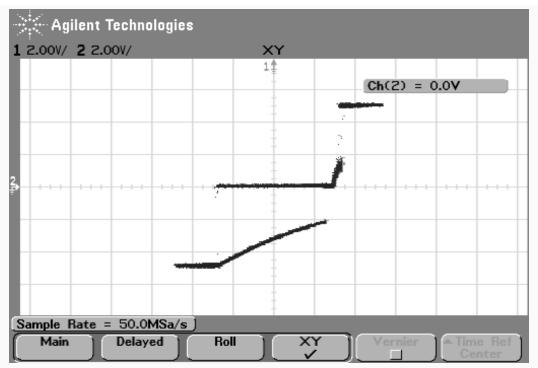

clock\_gen contains a circuit with the NE555 timer integrated circuit to generate a similar pulse to the faster behavioral model. The period and duty cycle do not exactly match clock\_gen-fast but it is close enough to allow for visually similar simulation results to clock\_gen-fast.asc. The output is a square wave from -6 V to +6 V. It does not stop intermediately at 0 V as one might expect. The period is slightly more than 10  $\mu$ s:

Tthe 555-timer is too complex to simulate within the full TCA2 architecture in a reasonable timeframe (we left it running for 48 hours and it did not progress past the initialize phase), so clock\_gen-fast was used in that architecture. Since TCA0 is a simpler architecture, clock\_gen is integrated to provide a more accurate simulation.

## 4.5. Processor

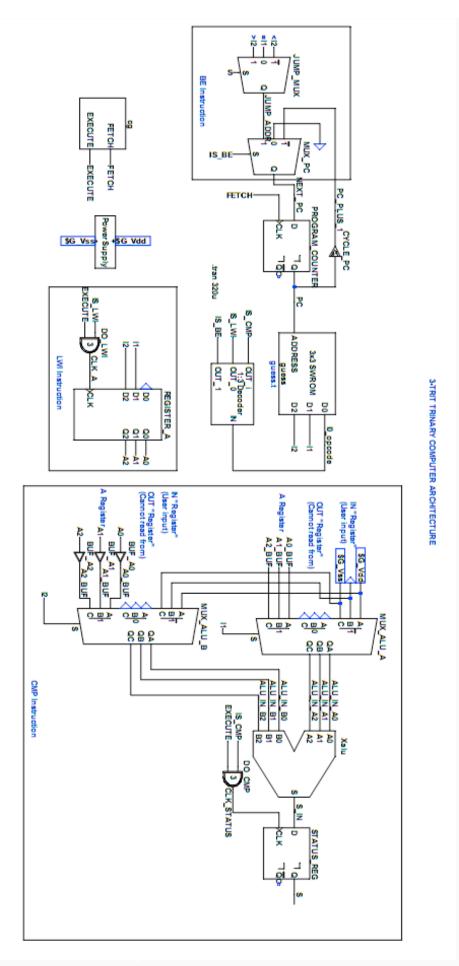

Figure 12. High-level block diagram of 3-trit trinary computer architecture 2, in color (TCA2). Older diagrams<sup>[49]</sup> are available.

The basic design is a trinary ROM configured by an array of switches, connected to an address decoder. The program counter initializes to 0 on startup and increments with each cycle. The PC is sent, as the address, to the memory bank, and output of the memory is fed to an instruction decoder that controls the proper signal outputs to execute the instruction.

# 4.5.1. Registers

TCA2 has a set of three registers, addressed by a single trit value:

- $\blacksquare$  1 input register IN, wired to 3 switches

- 0 output register OUT, wired to 3 LEDs

- 1 general-purpose accumulator register A, 3 trits, latches, also wired to LEDs

We decided on having three registers since three is the least number that can be represented using one trit. Additionally, the status trit, S, holds the numerical sign of the last operation. It is set by the CMP instruction and indirectly accessed by the BE branch instruction.

TCA0 only has the general-purpose register: the accumulator, known simply as "A".

## 4.5.2. Input and Output

We researched a myriad of LEDs and switches to use for I/O<sup>[50]</sup>. Triple-throw switches were originally planned for TCA2 input, but in TCA0 inputs can be manually wired to positive, ground, and negative by connecting the input wire to the appropriate pins on the breadboard.

For output, we purchased 2-, 3-, and 6-pin bi-color and tri-color LEDs for experimentation. During testing, an oscilloscope can be used to view the output, however, visual output is desirable. In a binary digital system, an active LED is often used to indicate a 1, while 0 is indicated by off. In a trinary digital system, either three colors (red, green, blue) can be used to indicate each of the three states, or two states (red-orange, green) can be represented by two colors and the third state (0) by off.

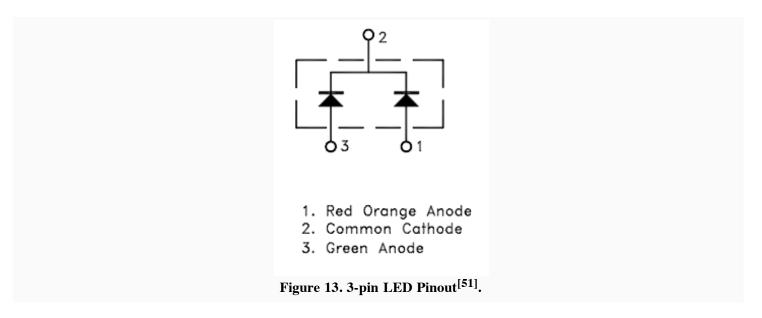

A 3-pin bi-color LED may appear to be the ideal solution, but the one we purchased had a common cathode and separate anodes, making additional circuitry necessary to translate a trinary voltage level to the LED output:

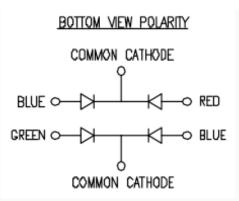

The 6-pin LED offers three colors and a promising pinout:

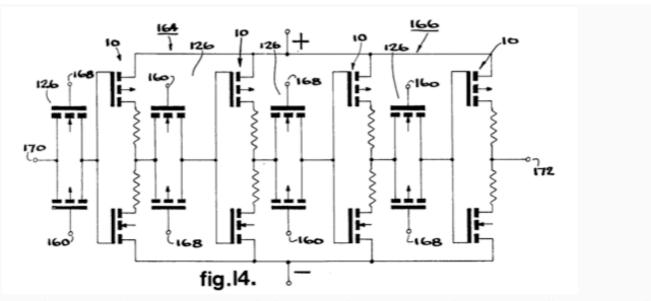

Figure 14. 6-pin RGB LED Pinout<sup>[52]</sup>.

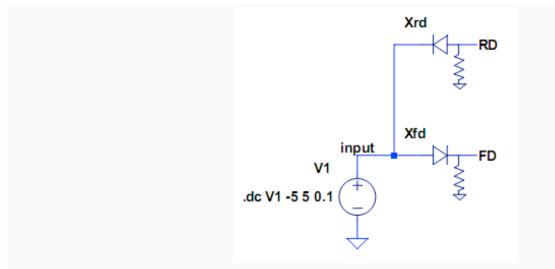

The bottom pair could be used as follows. Blue would be grounded, the common cathode would be left floating, and the green terminal would be used for input. A zero input would leave both LEDs off, a positive input would forward-bias the green LED turning it on, while a negative input would forward-bias the blue LED, turning it on. However, implementation is complicated by the maximum forward voltages required by the LEDs. Green has a maximum of 2.5 V, 2.1 V typical, while blue has a maximum of 4.2 V and 3.65 V typical. A 2:1 resistive voltage divider could be used to bring the nominal 5 V down to 2.5 V, but it is not known whether the blue LED will function at a low 2.5 V. Additional, complicated circuitry would also be needed to use all three colors in this expensive, 6-pin LED.

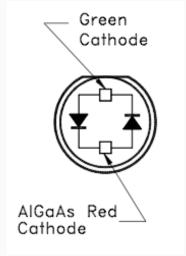

A third option is a humble 2-pin LED, which offers the perfect reverse-parallel configuration:

Figure 15. 2-pin LED Pinout<sup>[53]</sup>.

The red has a 40 mA absolute maximum forward current, while the green is 30 mA. Forward voltage for red is 1.8 V typical, 2.4 max, and green 2.1 V typical and 2.6 V max, at 20 mA forward current. Therefore a voltage of  $\pm 2.1 \text{ V}$  and a current of 20 mA will cause the LED to function as expected:

Table 7. Bicolor LED Output Colors

| Log | ic Input Color Output Green |

|-----|-----------------------------|

| 1   | Green                       |

| 0   | (off)                       |

| 1   | Red                         |

According to a current limiting resistor calculator<sup>[54]</sup>, for a 5 V supply and a 2.1 V drop across the LED along with a desired 20 mA current, the current limiting resistor should be 150  $\Omega$ .

In summary, to build an LED output circuit, one would connect the logic input signal to a 150  $\Omega$  resistor in series with the 2-pin bi-color LED. We built such a circuit and confirmed that it correctly lit the LED as each logic level input was applied.

#### 4.5.3. 3-Trit Instruction Set

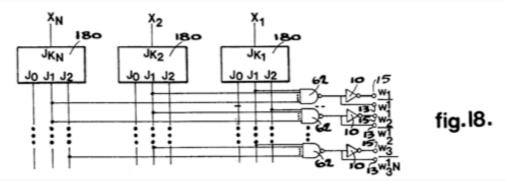

Although a *One Instruction Set Computer* (OISC) with a "subtract (balanced ternary) and branch if negative" (subneg) operation is Turing complete and could be used to implement any program<sup>[55]</sup>, for simplicity and ease of debugging we instead decided to implement three separate opcodes for each of the operations, as follows:

- $\blacksquare$  1xy cmp, compare register x with register y, store status trit in S

- 0xx lwi, load immediate value xx into register 1 (A, accumulator)

- 1xy be, branch to immediate address x if S = 0 (previous comparison indicated the two values were equal), otherwise branch to immediate address y

The motivation for using precisely the above instructions is that a trivial guessing game can be written as follows (this file is available in the git source code repository as asm/guess.t):

```

init: lwi -3 ; random number to guess

check: cmp in, a ; did they guess right?

be init, check ; re-initialize if correct, loop if not

```

Using the assembler in asm/asm.py, this program assembles to the tritstream asm/guess.3:

```

1010<del>1</del>0111

```

The tritstream dumps the contents of memory at addresses  $\overline{1}$ , 0, and 1. The program counter begins at 0, so the first instruction, 1wi -3, assembles to  $\overline{101}$  in the middle of this stream, at address 0, label init. The next instruction at address 1, label check, is cmp in, a which assembles to  $\overline{111}$ . The last instruction wraps PC around to  $\overline{1}$  and assembles be init, check to 101, at the beginning of the tritstream. Hence, this 3-trit instruction set allows for implementation of a guessing game as required.

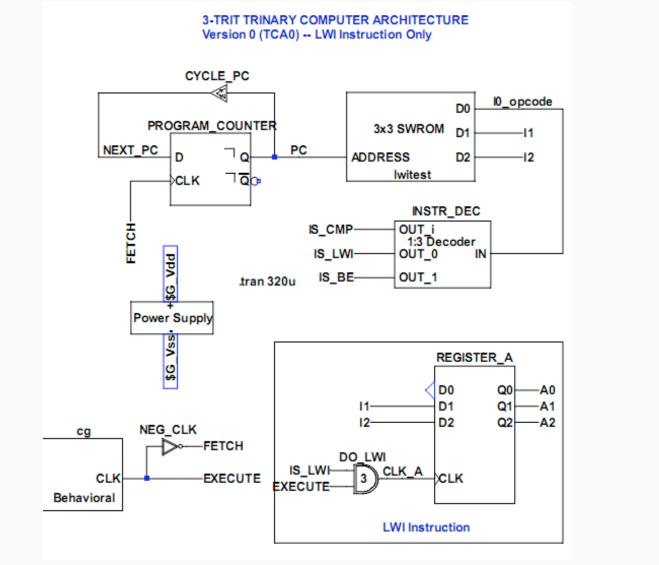

# 4.5.4. LWI Instruction Example (also known as TCA0)

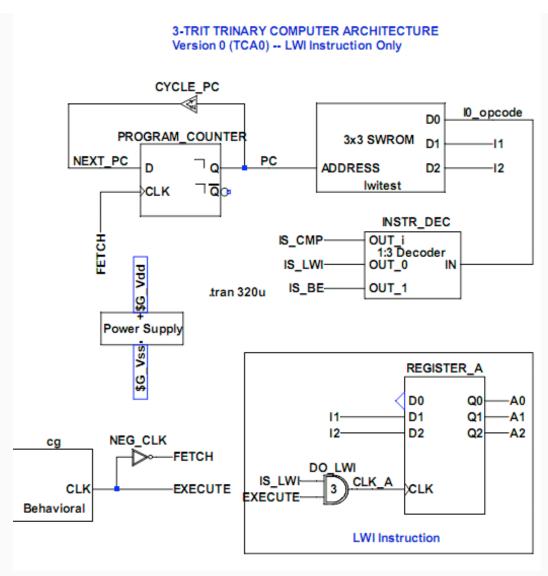

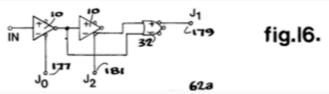

In implementing the architecture, I took the approach of building it incrementally, beginning with the load-word-immediate instruction. This instruction is the easiest to implement because it merely activates a clock signal on the A register, to load it with the last two trits of the instruction. Because it only supports this one instruction, this architecture is known as TCAO. A schematic of the architecture is as follows:

Figure 16. main\_lwitest.asc, an architecture that supports the LWI instruction.

Each of the components shown above have been designed ultimately from transistors, as described in detail in appendix E.

The computer operates as follows. The clock generator (section **4.4**) emits a regular series of pulses. In the beginning, the PC register (a rising-edge triggered master-slave tri-flop, see section **D.5.7**) starts at 0, which reads address 0 from the switch ROM. The SWROM is loaded with the following code assembled from the source fileasm/lwitest.t:

```

lwi -3

lwi -2

lwi 0

```

Therefore, address 0 causes the SWROM to output the signals for lwi -3 (of which the machine code is  $0\overline{11}$ ). Hence, the instruction signals are at the following logic levels:

Table 8. Logic Levels of TCA0 Instruction Signals Shortly After Power-On

| Signal    | Logic Level |

|-----------|-------------|

| I0_opcode | 0 0         |

| I1        | 1           |

| I2        | 1           |

The I0\_opcode feeds into the *instruction decoder*, a 3:1 decoder (section **D.8**) that translates the opcode into a set of control signals. In this case, I0\_opcode is 0, corresponding to the lwi instruction, so the control signals are set as follows:

Table 9. Logic Levels of TCA0 Control Signals Shortly After Power-On

| Signal  | Logic Level |  |  |  |

|---------|-------------|--|--|--|

| IS_CMP  | 1           |  |  |  |

| IS_LWI  | 1           |  |  |  |

| IS_BE   | 1           |  |  |  |

| EXECUTE | E 1         |  |  |  |

As shown above, the instruction decoder outputs  $\overline{1}$  for inactive signals, and 1 for active signals. Since the instruction is lwi, IS\_LWI is active. This signal feeds into the DO\_LWI TAND gate (section **D.4.4**), thus causing CLK\_A to be 1 since EXECUTE is also 1 (at power-up). Therefore, the REGISTER\_A register loads the values of I1 and I2,  $\overline{1}$  and  $\overline{1}$  respectively, into the A register. The *lwi* -3 instruction has completed, and -3 ( $\overline{11}$ ) has been loaded into the A register.

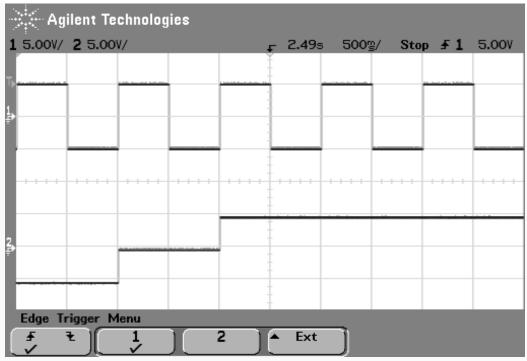

At the next clock cycle, FETCH is 1 and EXECUTE goes to 0. The rising edge of FETCH causes the program counter register to load the contents of NEXT\_PC. NEXT\_PC is the output of the program counter when connected to a *cycle up gate* (section **D.3.4**) that increments the 1-trit number. This causes PC to increment from 0 to 1, and the instruction at this address (lwi -2) is executed as EXECUTE goes to 1. In the next cycle, PC is incremented again and wraps around to  $\overline{1}$ , and the lwi 0 instruction executes. A timing diagram has the details:

00), from lwitest.t, running main\_lwitest.asc.

The last three plots show the contents of the accumulator ("A" register). Note that 1wi only specifies the lower two trits to load; the upper trit is hardwired to 0 in this example.

The above timing diagram uses a SPICE voltage pulse for the clock generator, but because TCA0 is much simpler than TCA2, it is possible to simulate using the clock generator built using the 555 IC. Execution begins at PC = 1 instead of 0, and the frequency is slightly different, but the operation of the instructions is the same:

This architecture, although limited, is sufficient to execute a "Christmas lights game", where the player determines the sequence of colors to emit. The output of the A register, as controlled by the lwi instruction, is wired to a series of multi-color LEDs. By changing the programming, the player can experiment with a variety of light sequences. While the game would be more exciting with a larger number of LEDs (ideally, enough to string up a medium-size Douglas-fir) than the A register can represent, this game demonstrates the programmability of the TCAO architecture.

## 4.5.5. CMP Instruction

The *compare* instruction sets the status bit based on the comparison of two registers, as follows:

In order to do so, an arithmetic *subtraction* operation must be performed. To do so, an *arithmetic logic unit* is used.

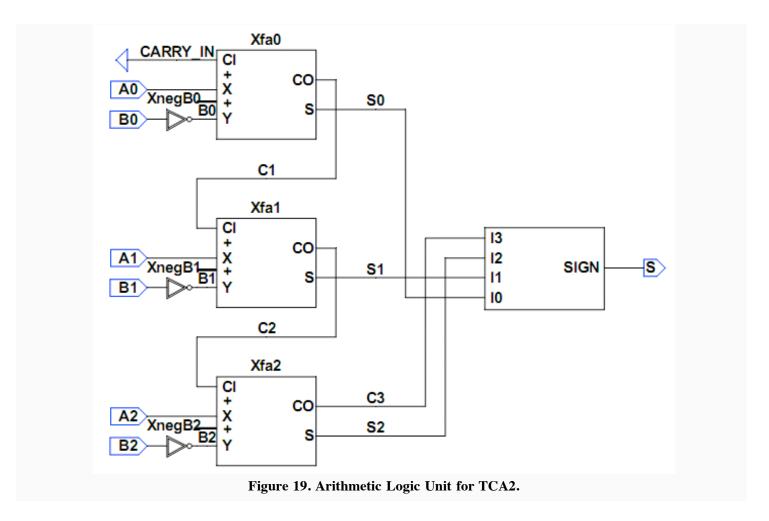

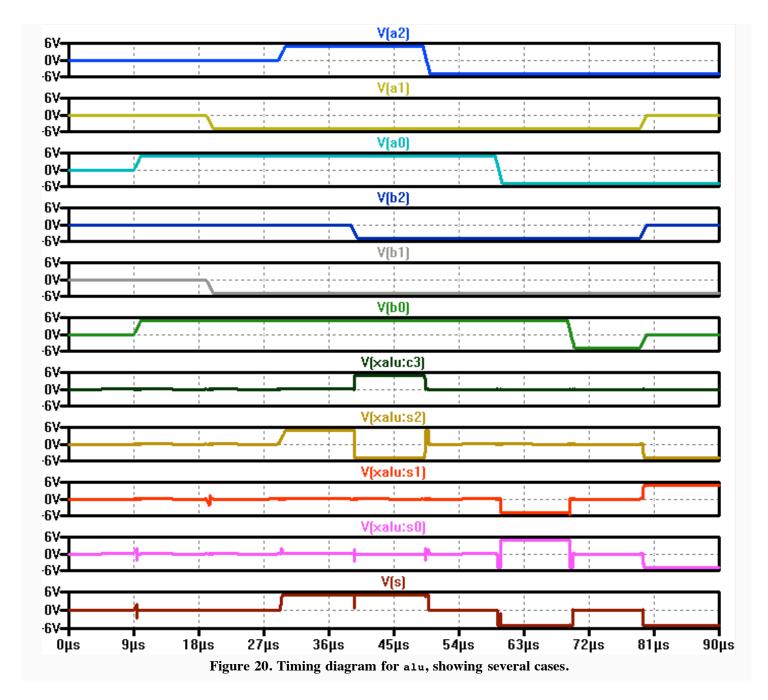

#### 4.5.5.1. ALU

The ALU is a large component consisting of an inverter, 4-trit ripple-carry adder, and a sign detector. As an example, the following inputs A and B cause the following outputs S to occur:

**Table 11. ALU Test Cases / Examples**

|           |                  |                  |     |     | Test Cases                   | , 231200121P101 |                  |

|-----------|------------------|------------------|-----|-----|------------------------------|-----------------|------------------|

| Time (ns) | A                | B                | A   | B   | Difference                   | Difference      | <b>S</b> Meaning |

| 0         | 000              | 000              | 0   | 0   | 0000                         | 0               | 0 =              |

| 10        | 001              | 001              | 1   | 1   | 0000                         | 0               | 0 =              |

| 20        | $0\overline{1}1$ | $0\overline{1}1$ | -2  | -2  | 0000                         | 0               | 0 =              |

| 30        | $1\overline{1}1$ | $0\overline{1}1$ | 7   | -2  | 0100                         | 9               | 1 >              |

| 40        | $1\overline{1}1$ | 111              | 7   | -11 | $1\overline{1}00$            | 18              | 1 >              |

| 50        | 111              | 111              | -11 | -11 | 0000                         | 0               | 0 =              |

| 60        | 111              | 111              | -13 | -11 | $00\overline{1}1$            | -2              | 1 <              |

| 70        | 111              | 111              | -13 | -13 | 0000                         | 0               | 0 =              |

| 80        | 101              | $0\overline{1}0$ | -10 | -3  | $0\overline{1}1\overline{1}$ | -7              | 1 <              |

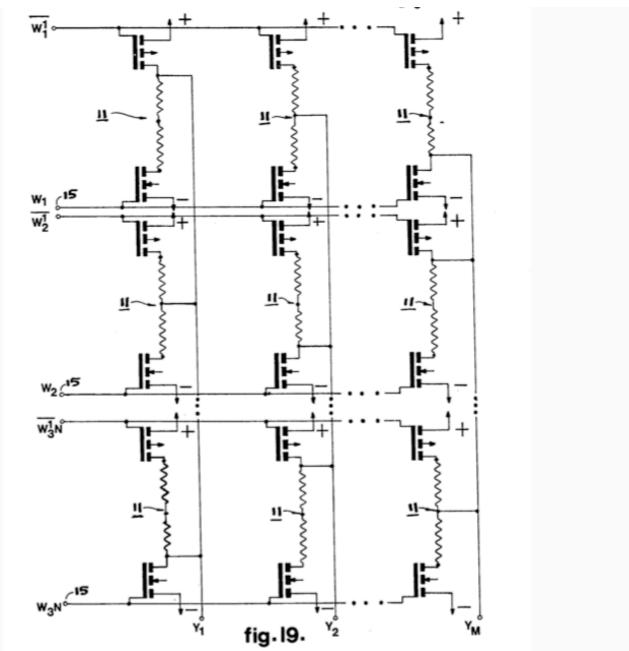

The ALU is built from these operations, in sequence:

- **Negation**: a bank of Simple Ternary Inverters (section **D.3.2**) on the R2 input.

- **Addition**: implemented using an 4-trit ripple carry adder (section **B.1.6**). Since R2 is inverted, this is equivalent to R1 R2 (subtraction).

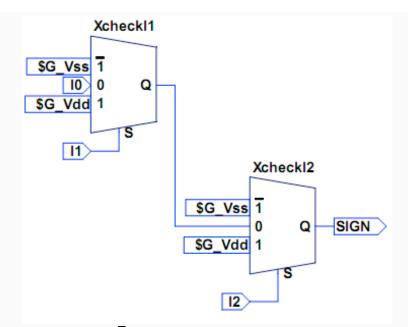

- **Sign checking**: the S trit is set to the most-significant non-zero trit of the difference, or 0 if it is zero, using a *sign detector circuit* (section **B.1.2**).

A schematic of the ALU is as follows:

The timing diagram matches the behavioral model, but it is executed at an order of magnitude slower to allow the carries in the ripple carry adder to propagate:

I also implemented a behavioral model of the ALU, quickly computing the comparison result using a mathematical expression, for comparison purposes. The timing diagram below shows the timing diagram ALU (excluding input signals):

### 4.5.5.2. CMP Instruction Example

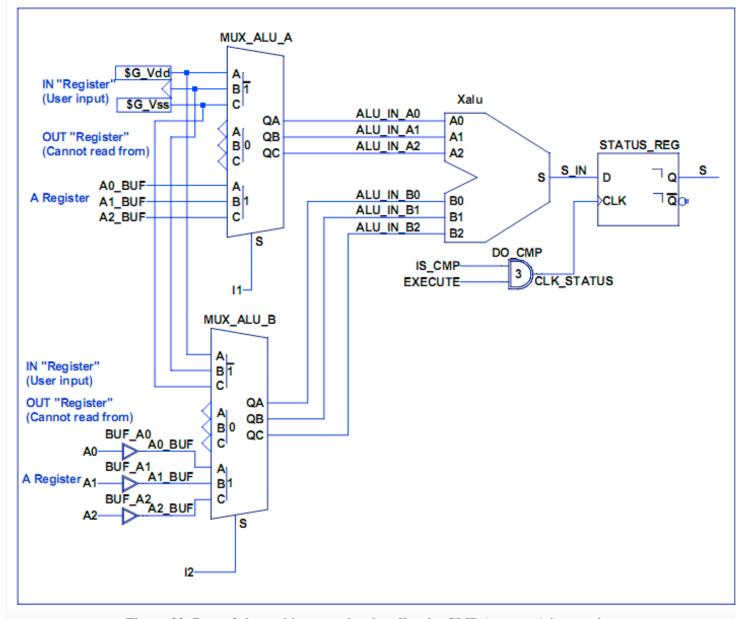

To integrate the ALU with the remainder of the computing architecture, I designed the following circuitry:

Figure 22. Part of the architecture that handles the CMP (compare) instruction.

The multiplexers (section **D.8**) select which inputs to compare, and the contents are then fed to the ALU. The sign result is sent to the status register, clocked in during the EXECUTE phase if the current instruction is a compare instruction, in a manner similar to how the lwi instruction clocks in input. The above circuitry can be dropped in in-place into TCA0 to add the CMP instruction, since the IS\_CMP control signal is available.

An assembly program named asm/cmptest.t was written to test this architecture. It is as follows:

```

; Test cmp (compare) instruction and lwi (load word immediate)

lwi -3 ; load A with 0i0

cmp in, a ; compare A to IN (probably 10i)

cmp a, in ; now S should be opposite

```

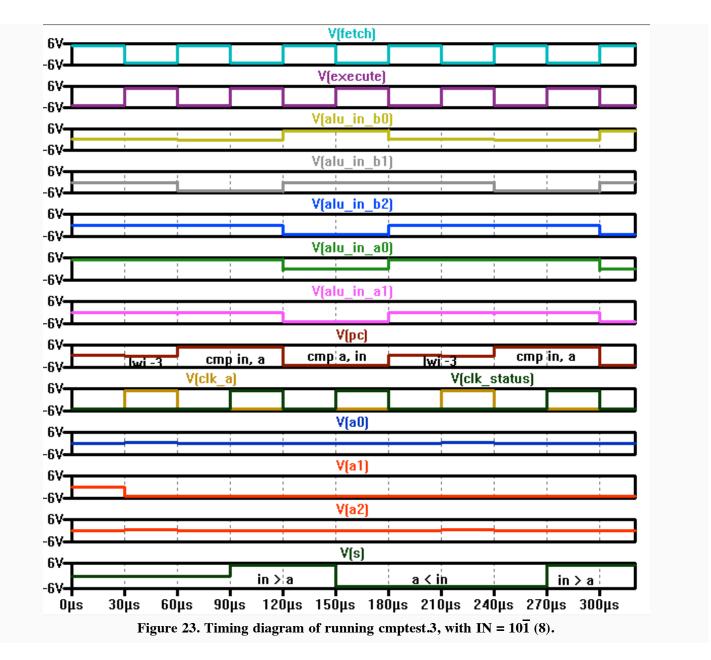

As an example, this assembly program was ran on the architecture with the IN register hardwired to  $10\overline{1}$  (8). The timing diagram is as follows:

First A is loaded with  $0\overline{1}1$  (-3), then IN is compared to A. Since 8 > -3, the status trit, S, is set to 1 for "greater than".

Next, the opposite comparison is performed, compare A to IN. Since -3 < 8, S is set to  $\overline{1}$  for "less than". The status trit remains unchanged during the next execution of lwi, but is set to 1 on the next cmp in, a.

Two major changes were needed to the architecture to support this instruction:

- All registers were changed from Mouftah's master-slave tri-flop (section **D.5.6**) to a custom edge-triggered tri-flop design (section **D.5.7**).

- Accumulator outputs were buffered (see section **D.3.2**) before connecting to the 9:3 multiplexers. Without buffering, the accumulator register would undergo undesired changes as the output feeds back to the input from the multiplexers. This can happen because the multiplexers (section **D.8**) operate using *transmission gates*—bidirectional CMOS switches.

### 4.5.6. BE Instruction

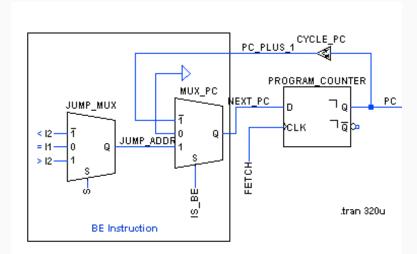

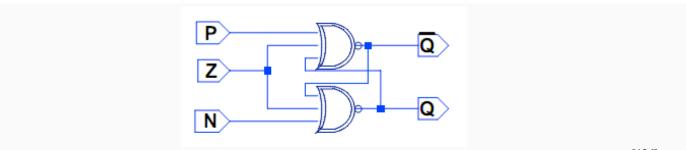

The final instruction to implement for a complete system is *branch-if-equal*. This instruction takes the machine code format  $1 \times y$ . If the status trit of the system is 0 (meaning the last comparison instruction resulted in "equal"), the instruction causes the system to jump to the first immediate address given (x, x) available in the I1 signal), otherwise to jump to the second immediate address given (y, 12).

Changes to NEXT\_PC signal are necessary to support this instruction. NEXT\_PC is now connected to the output of a 3:1 multiplexer, rather than the output of a cycle up gate (which incremented the program counter by one on every FETCH cycle). The MUX\_PC multiplexer allows for the IS\_BE control signal to switch between the jump address JUMP\_ADDR, and the next address in the incrementing sequence, PC\_PLUS\_1. Additionally, JUMP\_ADDR is connected to the output of another multiplexer, JUMP\_MUX, that selects the address to jump to based on the result of the status trit. Essentially, the BE instruction changes what is loaded into PC next on the FETCH rising edge:

Figure 24. Part of the architecture that supports the BE instruction.

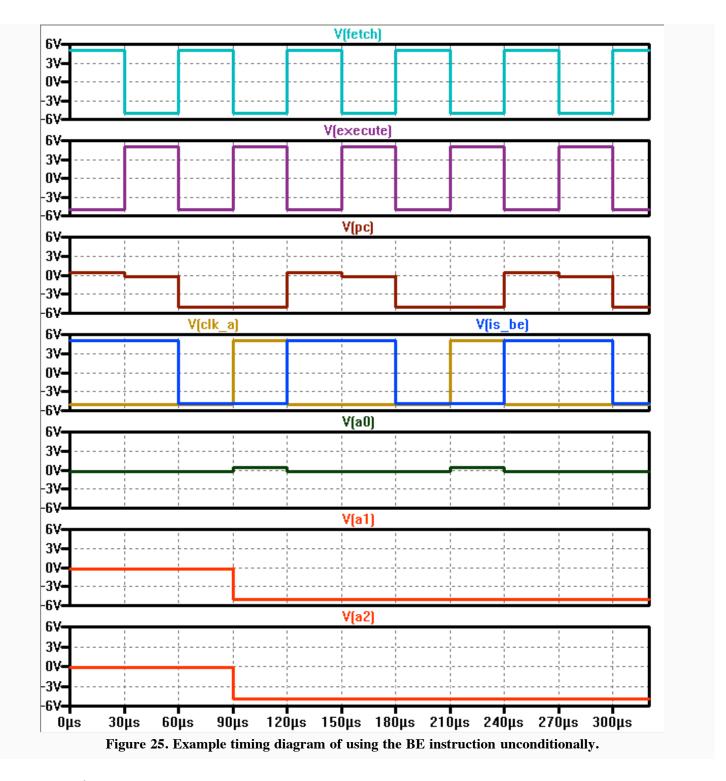

### 4.5.6.1. BE Instruction Example

For fast simulation, a new architecture, available as main\_jmptest.asc, was designed to only implement the LWI and BE instructions. A simple test program was written as follows:

```

start: be end, end

skipped: lwi 4

end: lwi -4

```

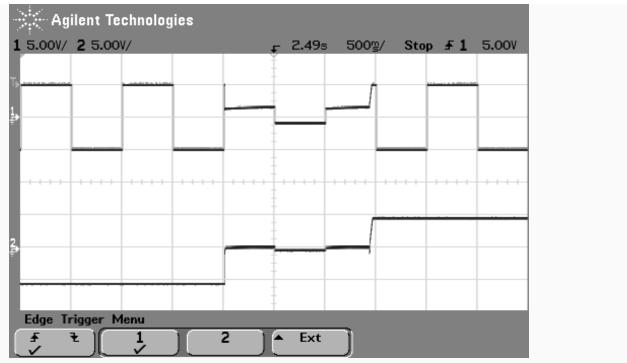

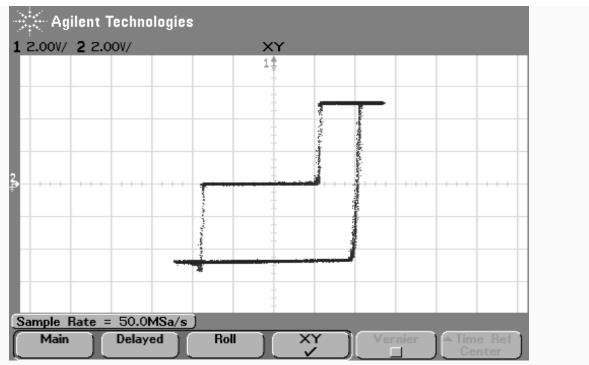

The second instruction (at address 1) is skipped over by the first instruction (at address 0), jumping to the last instruction (address  $\overline{1}$ ). The accumulator is loaded with 4 instead of -4, and PC cycles from 0, 1, 0, 1, skipping over  $\overline{1}$ :

## 4.5.7. Guessing Game Program

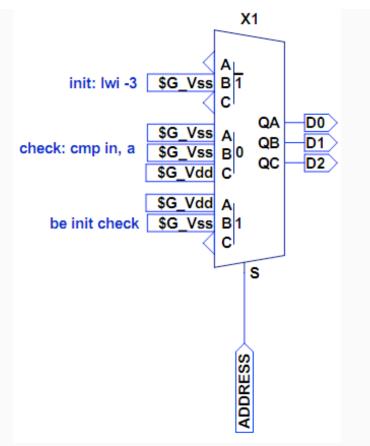

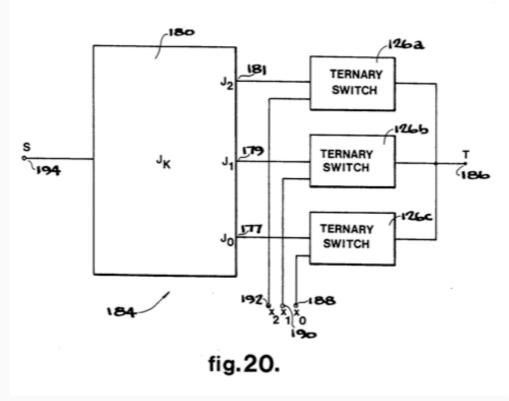

Putting it all together, the Trinary Computer Architecture v2 (TCA2), supporting the LWI, CMP, and BE instructions to run the guessing game, is as follows:

Figure 26. 3-trit Trinary Computer Architecture v2.0, with guessing game loaded.

This circuit is available as main.asc in the git repository, circuits directory<sup>[56]</sup> for simulation. Note that full simulation can take quite a while because the complete system is modeled at the transistor-level. On a 2.4 GHz Intel Core 2 Duo with 2 GB 667 MHz DDR2 SDRAM (MacBook Pro running Windows XP in VMWare), main.asc takes about 30 minutes to simulate.

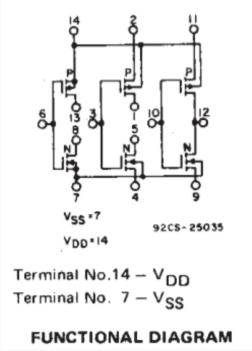

This complete architecture requires 161 chips: 42 x CD4016, 119 x CD4007, in addition to 340 resistors. For four transistors per CD4007 (two complementary MOSFET pairs are used), 6 per transmission gate (two per gate, but four for the two inverters) times 4 per chip = 1,484 transistors total, about 2/3 of the Intel 4004 processor<sup>[57]</sup> with 2,300 transistors. However, the TCA2 is significantly less complex than the 4004.

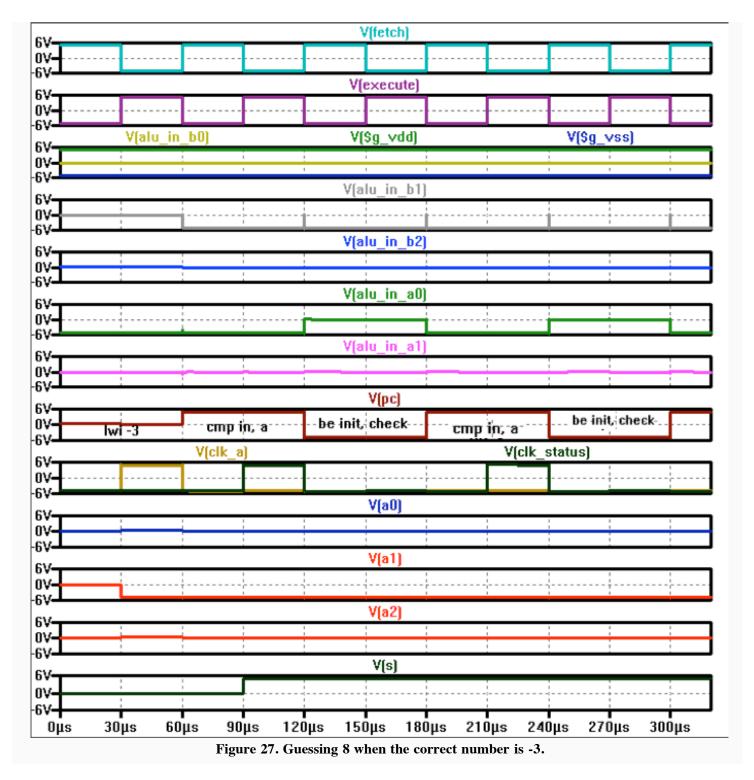

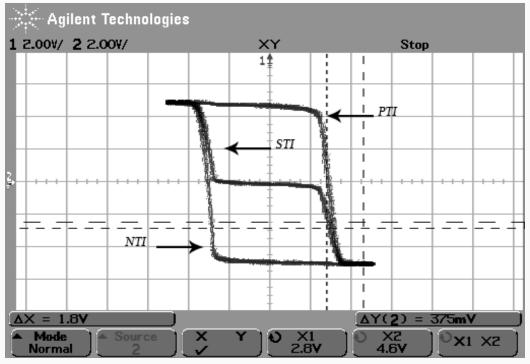

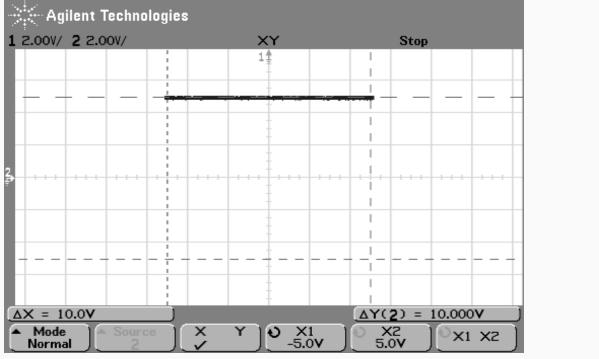

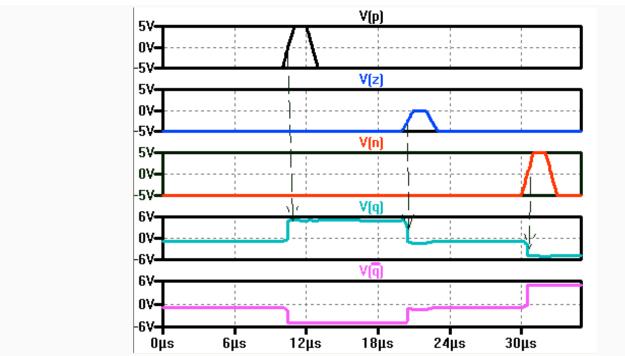

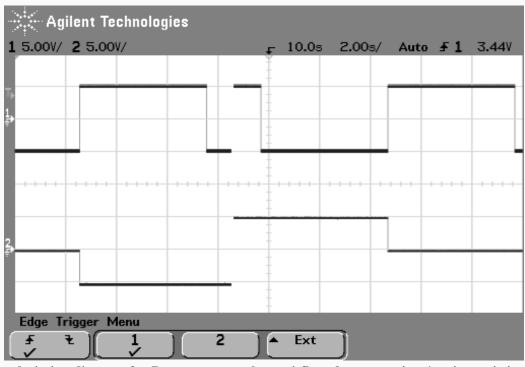

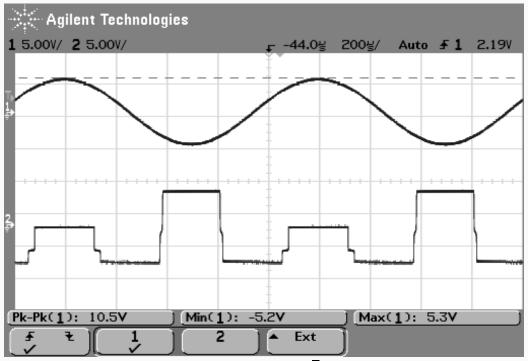

In this example, 8 is guessed ( $10\overline{1}$ , hardcoded on the user input line) when -3 ( $0\overline{10}$ ) is correct. 8 is greater, so the status line is high.  $8 \neq -3$ , so the program keeps looping over cmp in, a, be init, check:

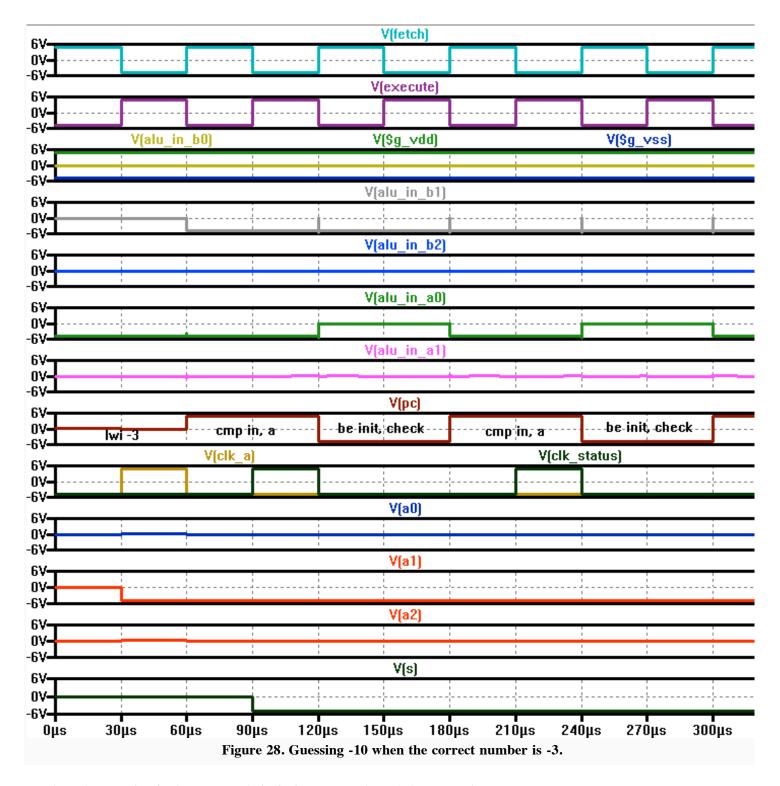

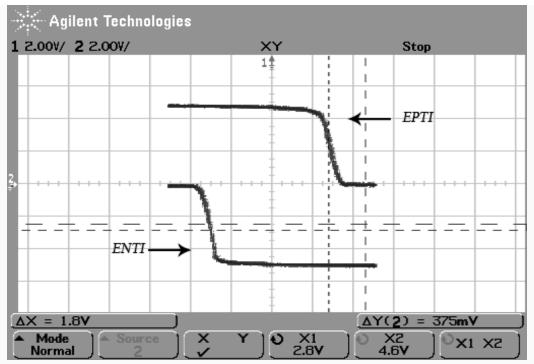

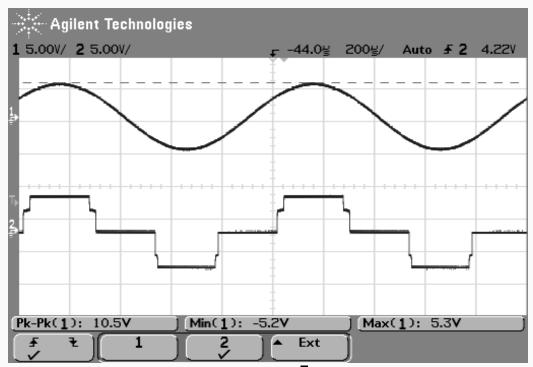

This time IN is set to -10,  $\overline{101}$  when -3 is correct. -10 is less, so the status line goes low, and keeps looping:

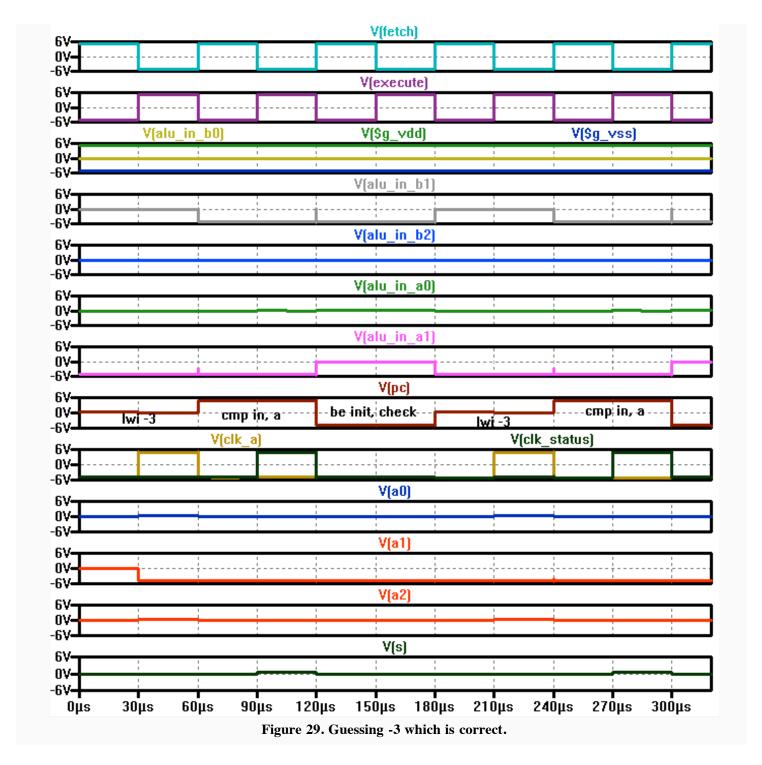

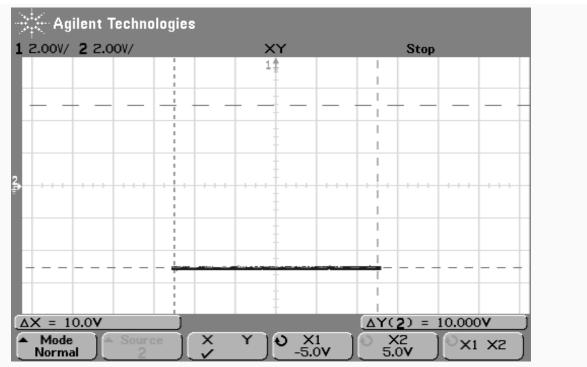

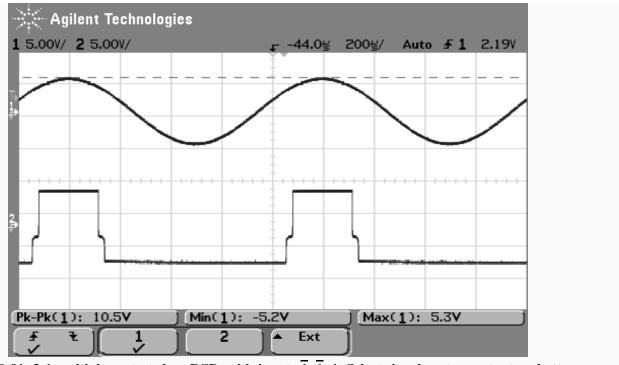

Lastly, when IN is -3, the status trit is 0 since IN = A and the guess is correct:

The branch goes back to lwi and reloads A (which, in this example, has not changed). The guessing game is functional on the trinary computer architecture.

# 5. Evaluation

The primary advantage of trinary, as discussed in section 2.1, is that fewer wires are necessary to represent the same range of numerical values. The number of wires per value is a quantifiable metric that can be used to compare the efficiency of binary and trinary systems.

The following table shows how the various quantities in the system are more compactly represented in trinary

than in binary:

Table 12. Evaluation of 3-trit Trinary Architecture vs. Binary

| Quantity                | States           | Trinary<br>Trits | Binary<br>Bits | Count if<br>Binary | States<br>Wasted | % States<br>Wasted | % Wires<br>Increased |

|-------------------------|------------------|------------------|----------------|--------------------|------------------|--------------------|----------------------|

| Machine Operation Codes | 3 (lwi, be, cmp) | 1                | 2              | 4                  | 1                | 25%                | 50%                  |

| Register Address        | 3 (in, out, a)   | 1                | 2              | 4                  | 1                | 25%                | 50%                  |

| Status code             | 3 (<, =, >)      | 1                | 2              | 4                  | 1                | 25%                | 50%                  |

The table above requires some explanation. As an example, the processor *status code* is required to represent three states: less than, equal to, or greater than. In trinary, only one wire is required to represent the three states. In binary, two bits are required, since one bit represents only two states. A fractional bit count can be calculated by  $\log(3) / \log(2)$  as 1.58 bits, but fractional bits cannot be realized as fractions of a wire, needless to say. Therefore, in binary the one extra state is wasted since it is not used. One state out of four possible states that can be represented with two bits is a 25% waste of representable states. Not only does a binary representation of the status code waste 25% of the available states, but it requires 50% more wires than in trinary (two wires versus one). For the given architecture, trinary is clearly superior for these reasons.

Trinary can be evaluated based on part count as well. The complete TCA2 architecture requires 161 chips: 42 x CD4016, 119 x CD4007, in addition to 340 resistors. For four transistors per CD4007 (two complementary MOSFET pairs are used), 6 per transmission gate (two per gate, but four for the two inverters) times 4 per chip, tis amounts to 1,484 transistors total, about 2/3 of the Intel 4004 processor<sup>[57]</sup> with 2,300 transistors. However, the TCA2 is significantly less complex than the 4004, so it cannot be directly compared. For a meaningful comparison, an analogous binary architecture would need to be designed and compared.

Furthermore, the trinary architecture could be compared on power usage. However, without an analogous binary architecture, this cannot be done.

The 3-trit architecture design itself was completed successfully. Not only was a transistor-level simulation completed, but a second simplified architecture was designed to run a second game. As intended, I designed an architecture to run a guessing game, but also a reduced architecture to run a Christmas lights game.

Recall that this project was part of the overall Ternary Computing Testbed effort, which also included tasks to design a compiler for an extended trinary architecture, as well as physical implementation of the computing architecture. A physical implementation of TCA0 was successfully built without the register and instruction decoder.

# 6. Conclusion and Future Directions

In conclusion, a functional transistor-level SPICE simulation of a simple 3-trit trinary architecture running a simple game was successfully simulated. The computer was built from the ground up using MOSFET transistor models to construct the logic gates, and the logic gates in turn were used to design higher-level architectural components. Lastly, a guessing game was written in assembly and loaded on the computer, where it was simulated and behaved as expected.

The deliverables of my project have been finished, but a future project could explore several additional aspects of trinary computing, including: comparing the power usage and cost of trinary and binary computers per bit, characterizing and optimizing the performance of trinary logic gates, and designing trinary VLSI integrated circuits.

## 7. Works Cited

- 1. D.E. Knuth, The Art of Computer Programming Volume 2: Seminumerical Algorithms, pp. 207-208. Addison-Wesley, 3rd ed., 1998. ISBN 0-201-89684-2. Available: http://jeff.tk/wiki/Image:Knuth-TaoCPVol2-pg207%2C8.pdf

- 2. The Elements of Computing Systems: Building a Modern Computer from First Principles by Noam Nisan and Shimon Schocken (MIT Press, 2005).

- 3. Connelly, Jeff. Jeff.tk Trinary/Meetings. Available: http://jeff.tk/wiki/Trinary/Meetings

- 4. Connelly, Jeff; Patel, Chirag; Chavez, Antonio. Jeff.tk Trinary/Status. Available: http://jeff.tk/wiki/Trinary/Status

- 5. Connelly, Jeff; Patel, Chirag; Chavez, Antonio. Jeff.tk Trinary. Available: http://jeff.tk/wiki/Trinary

- 6. Chavez, Antonio and Connelly, Jeff. Trinary/Tools Jeff.tk. Available: http://jeff.tk/wiki/Trinary/Tools

- 7. Chavez, Antonio and Connelly, Jeff. Trinary/CPU Simulation Jeff.tk. Available: http://jeff.tk/wiki/Trinary/CPU\_Simulation

- 8. Chavez, Antonio. Trinary/Compiler Jeff.tk. Available: http://jeff.tk/wiki/Trinary/Compiler

- 9. Swanson, William. *Introduction to Binary Numbers*. 2002. Available: http://www.swansontec.com/sbinary.htm

- 10. davido, Perl Monks. *Ternary operator (there's no Trinary operator)*. Available: http://www.perlmonks.org/?node\_id=562203

- 11. Wall, Larry. perl.com: Apocalypse 3. Available: http://www.perl.com/pub/a/2001/10/02/apocalypse3.html?page=6

- 12. Wall, Larry. et. al. *Programming Perl*, 3rd. Edition. ISBN: 978-0596000271 Section 3.16: Conditional Operator.

- 13. The Antikythera Mechanism Research Project. Available: http://www.antikythera-mechanism.gr/project/overview

- 14. Lexikon. *Analog Computers*. Available: http://www.computermuseum.li/Testpage/AnalogComputers.htm

- 15. National Semiconductor, Application Note 31. September 2002. *Op Amp Circuit Collection*. Available: http://www.national.com/an/AN/AN-31.pdf

- 16. Goldstrasz, Thomas et. al. *Computers During World War Two*. Available: http://waste.informatik.huberlin.de/Diplom/WW2/default\_e.html

- 17. Bains, Sunny. *Analog computer trumps Turing model*. EE Times. 11/03/1998. Available: http://www.eetimes.com/story/OEG19981103S0017

- 18. Principia Cybernetica Web: *Digital Computer*. Available: http://pespmc1.vub.ac.be/ASC/DIGITA\_COMPU.html

- 19. Maney, Kevin. USA Today, September 1997. *Debate Stirs Over Origins of Computers*. Available: http://www.scl.ameslab.gov/ABC/Articles/Debate9-97.html

- 20. Bebop's BYTES Back. *Claude Shannon's master's Thesis*. Available: http://www.maxmon.com/1938ad.htm

- 21. Hannah, Eric. *United States Patent 7309866: Cosmic ray detectors for integrated circuit chips*. Available: http://tinyurl.com/3ysdmk

- 22. Hayes, Brian. American Scientist: Computing Science: Third Base, 2001. Available: http://dx.doi.org/10.1511/2001.40.3268 and mirrored at http://jeff.tk/w/index.php? title=Image:American\_Scientist\_Online\_-\_Third\_Base.pdf

- 23. A. Srivastava and K. Venkatapathy, "Design and Implementation of a Low Power Ternary Full Adder,"

- VLSI Design, vol. 4, no. 1, pp. 75-81, 1996. doi:10.1155/1996/94696. Available: http://jeff.tk/wiki/Image:Design\_and\_Implementation\_of\_a\_Low\_Power\_Ternary\_Full\_Adder.pdf

- 24. J.T. Butler, Multiple-Valued Logic in VLSI, IEEE Computer Society Press Technology Series, Los Alamitos, California, 1991.

- 25. A.K. Jain, M.H. Abd-E1-Barr and R.J. Bolton, "A new structure for CMOS realization of MVL functions," International Journal of Electronics, vol. 74, no. 2, pp. 251-263, 1993.

- 26. S.L. Hurst, "Two decades of multiple valued logic--an invited tutorial," in Proceedings of IEEE International Symposium on Multiple-Valued Logic, p. 164, May 1988.

- 27. S.L. Hurst, "Multiple-valued logic--its status and its future," IEEE Transactions on Computers, vol. C-33, no. 12, pp. 1160-1179, December 1984.

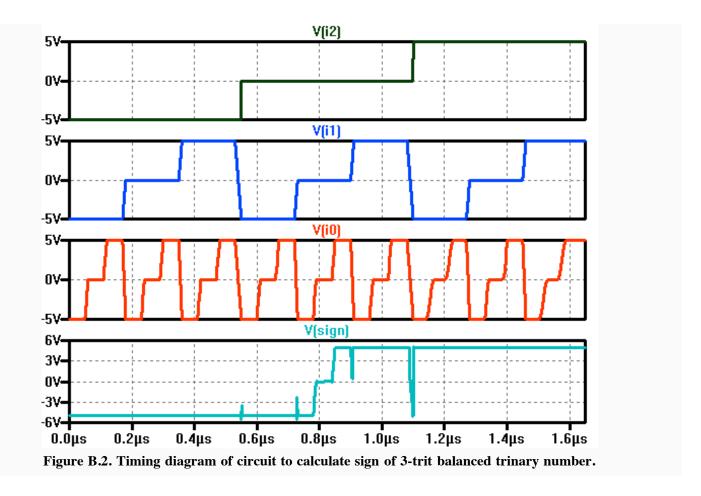

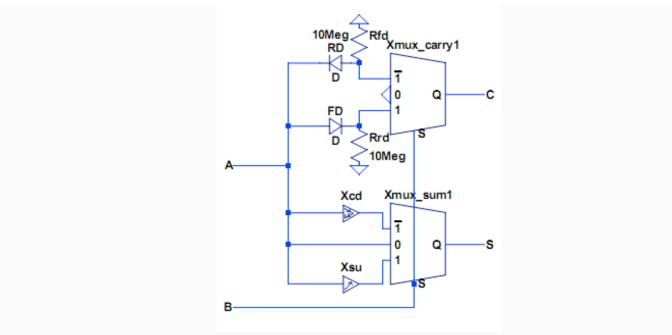

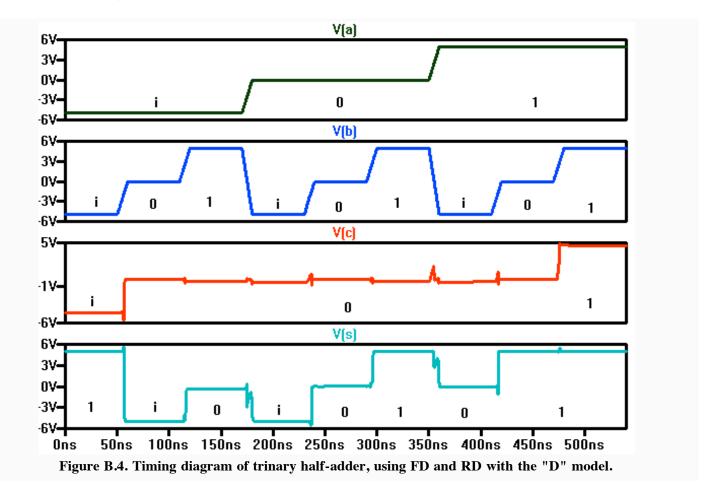

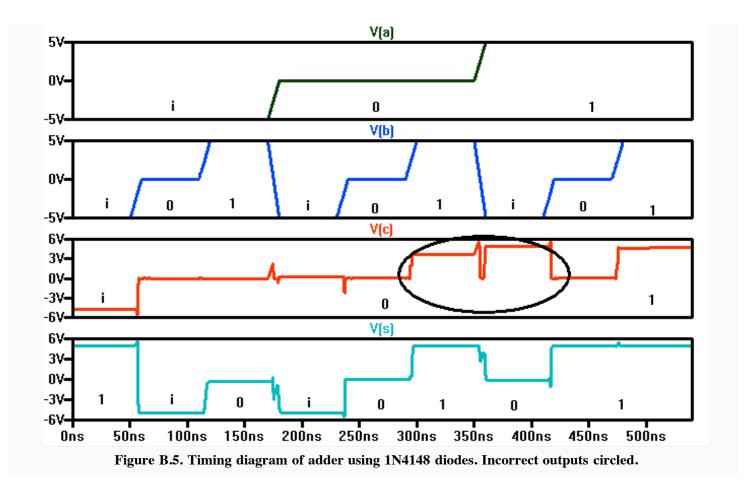

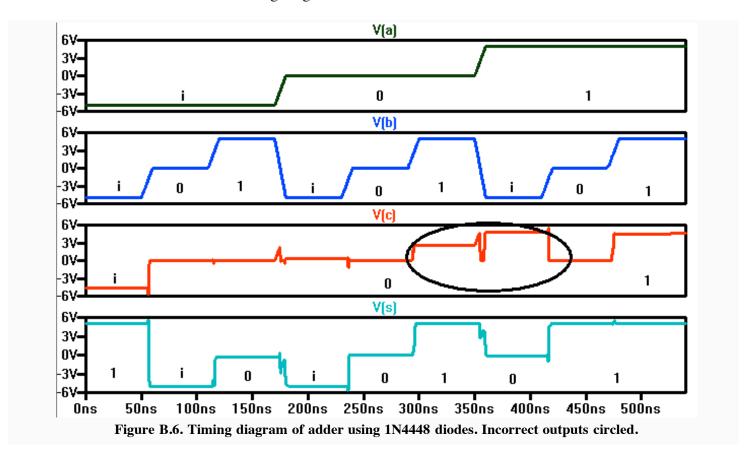

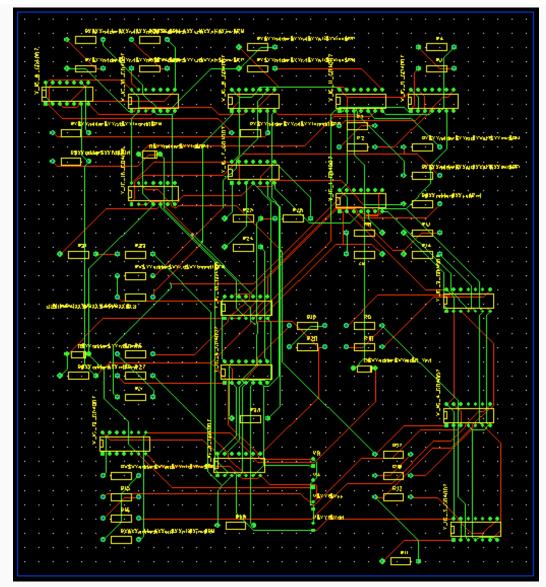

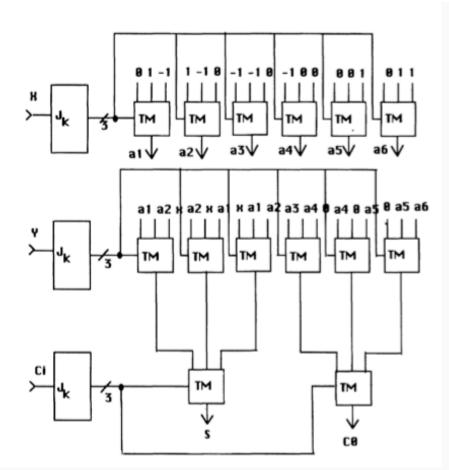

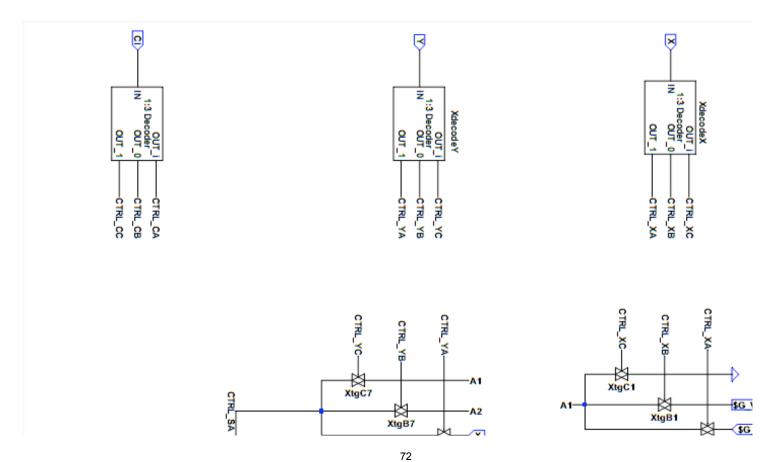

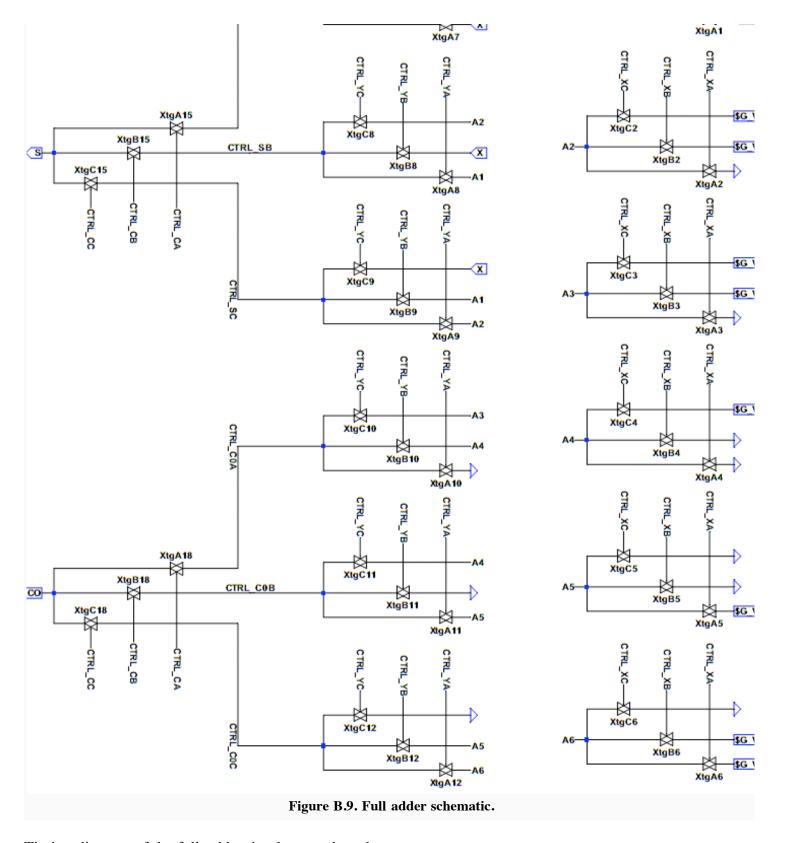

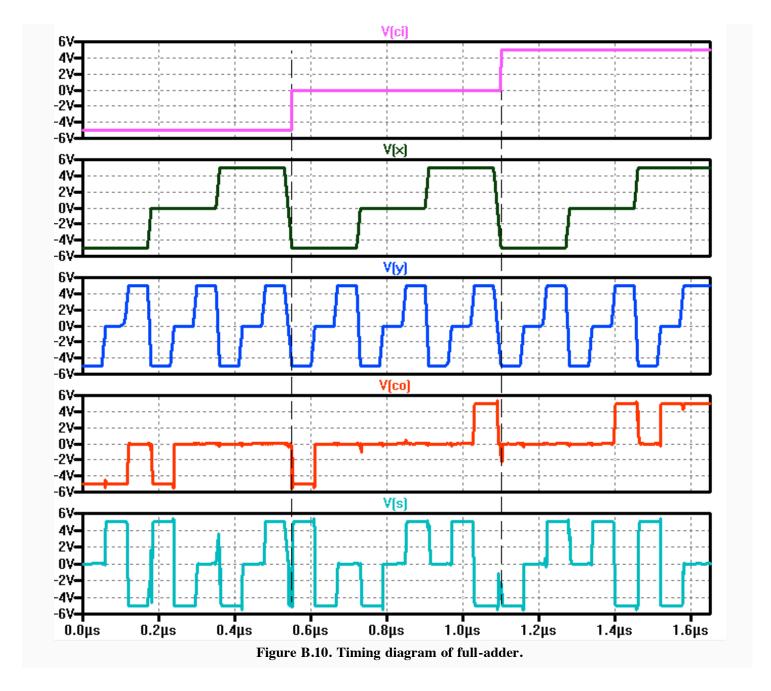

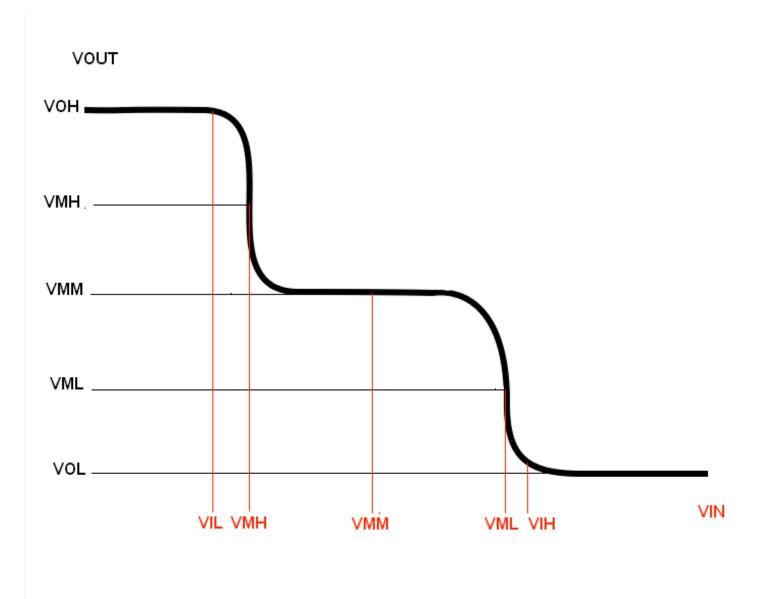

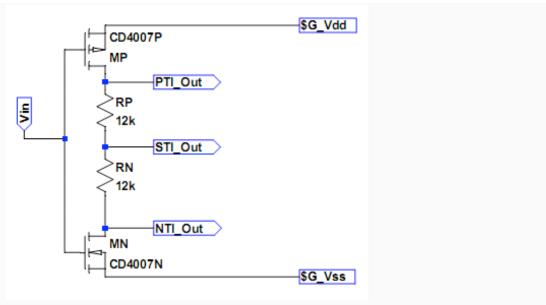

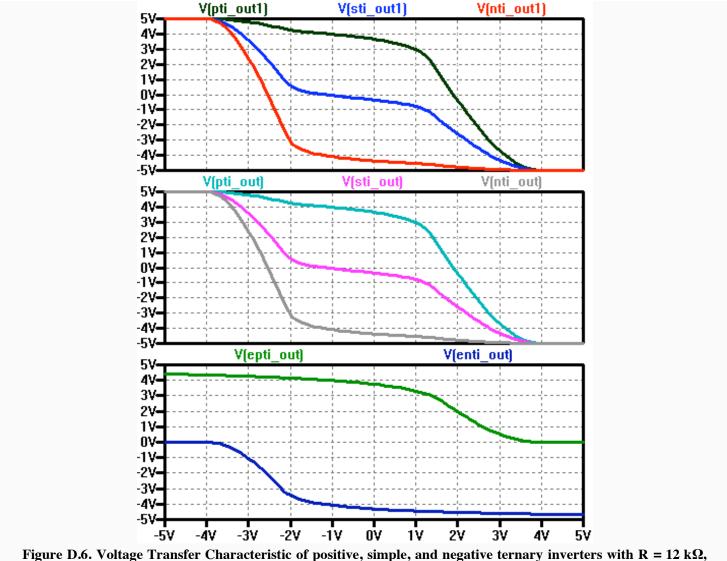

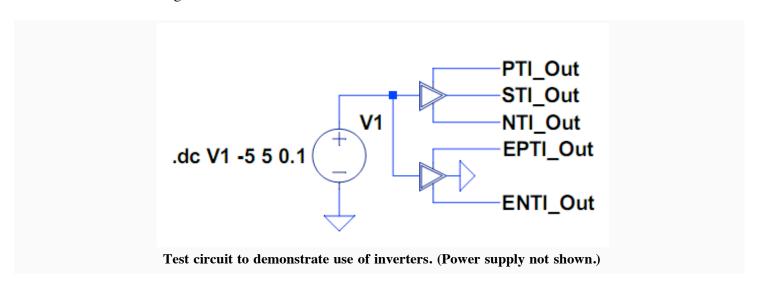

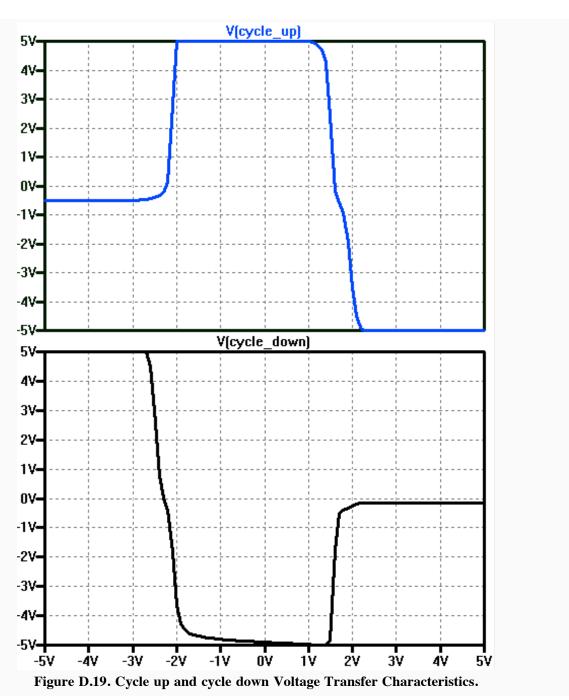

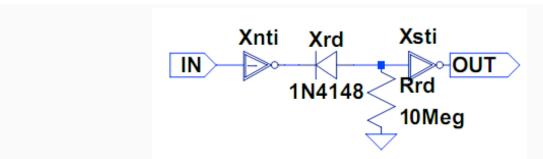

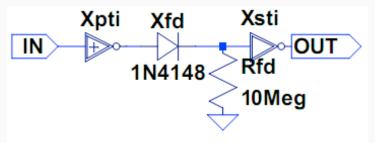

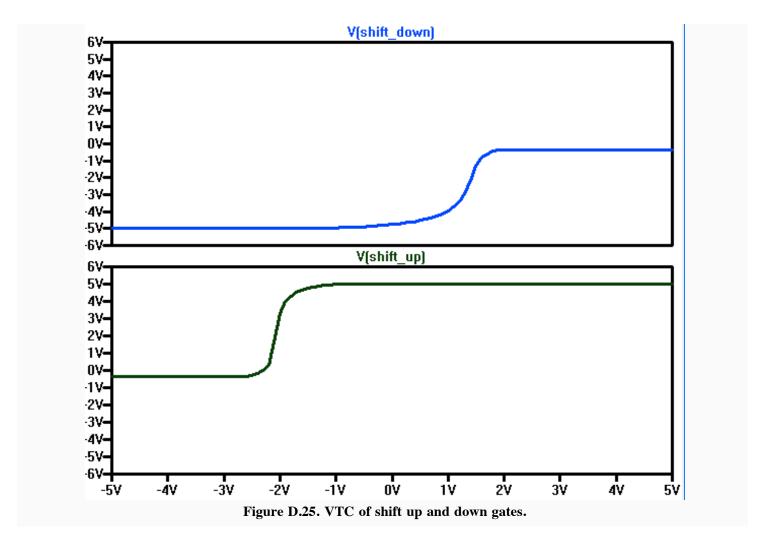

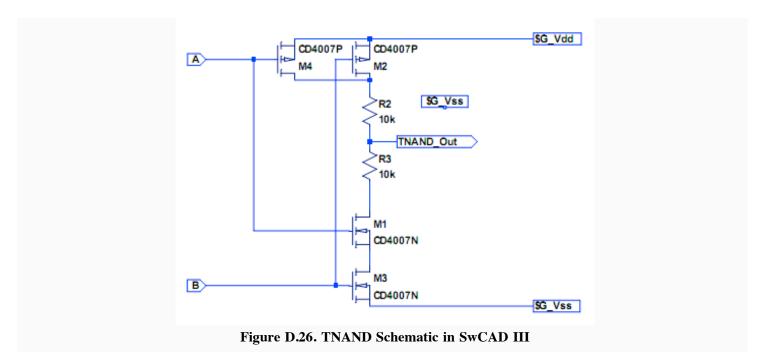

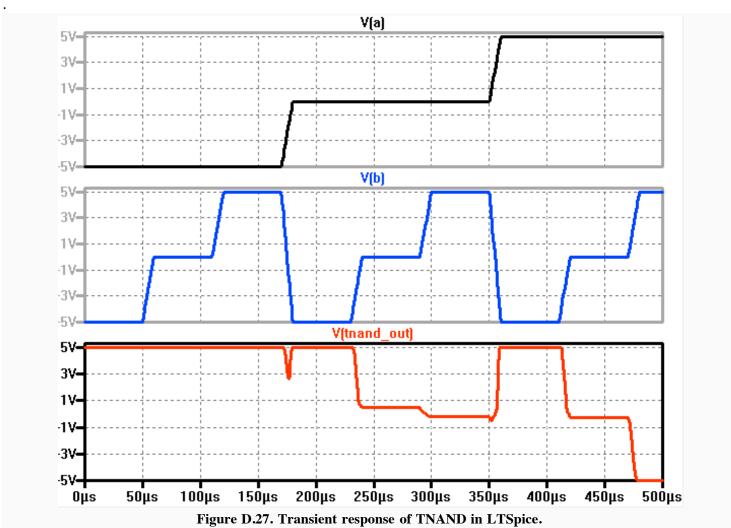

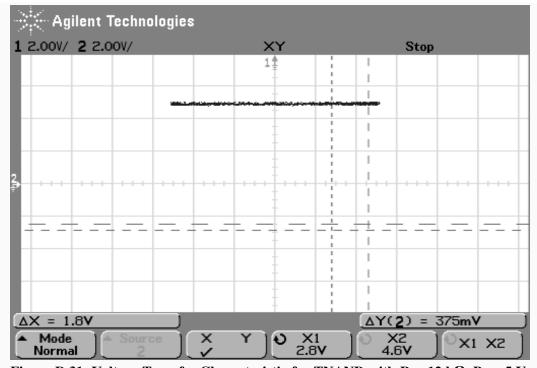

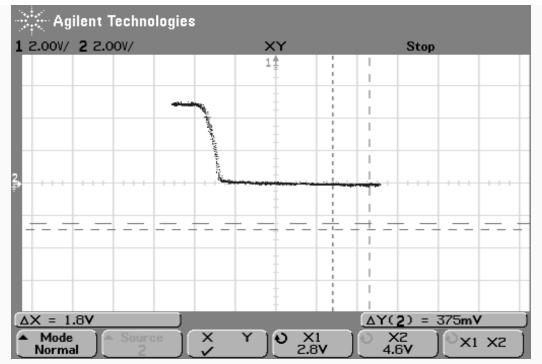

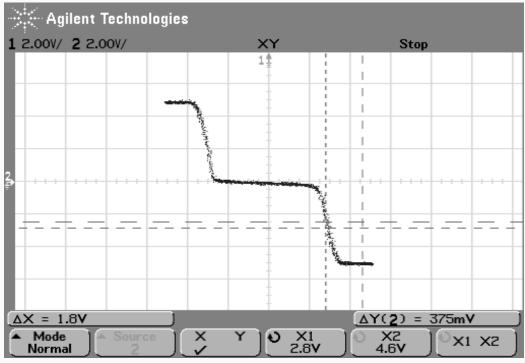

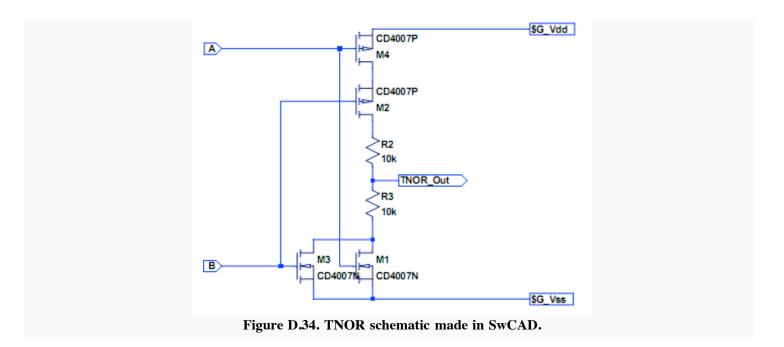

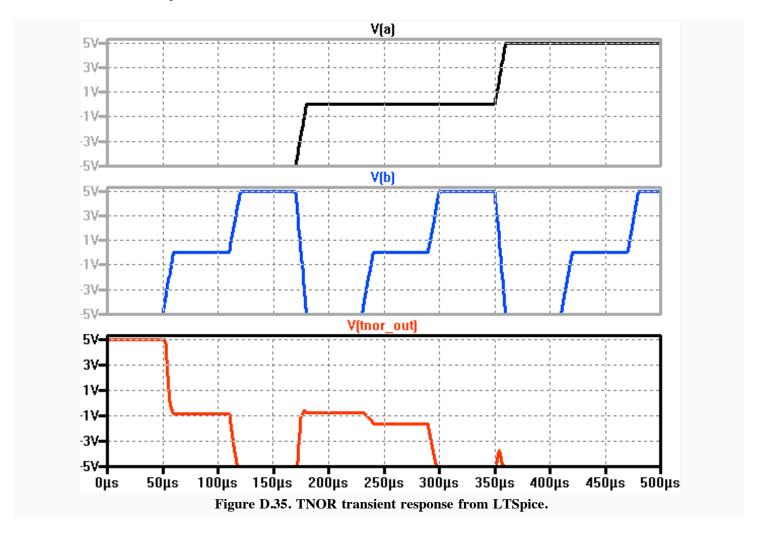

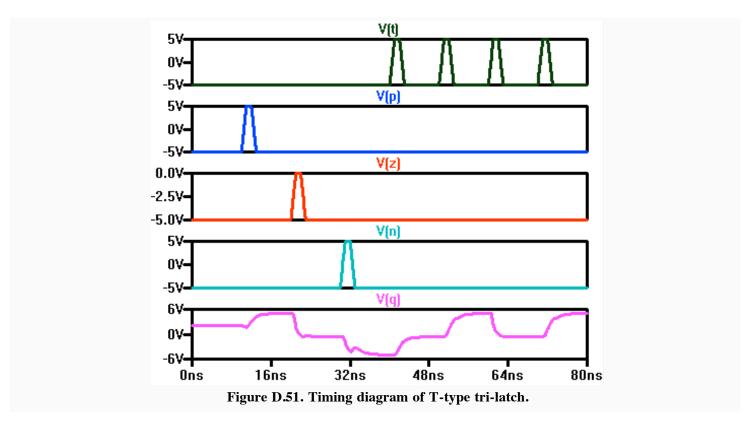

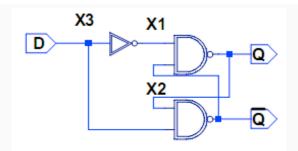

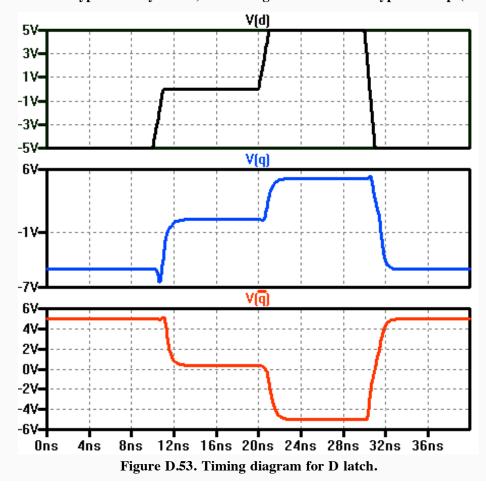

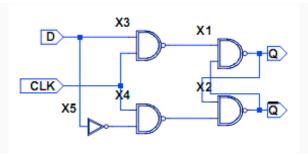

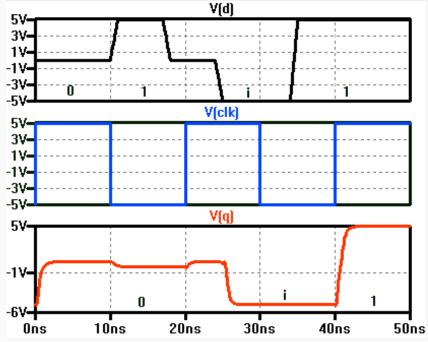

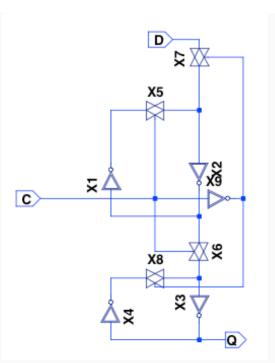

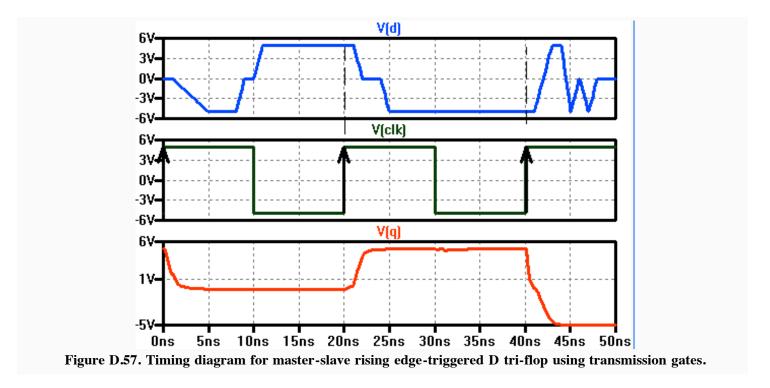

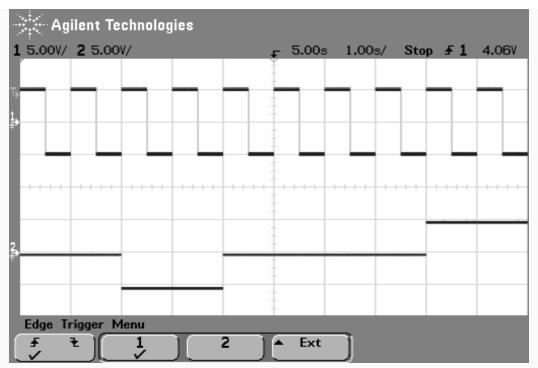

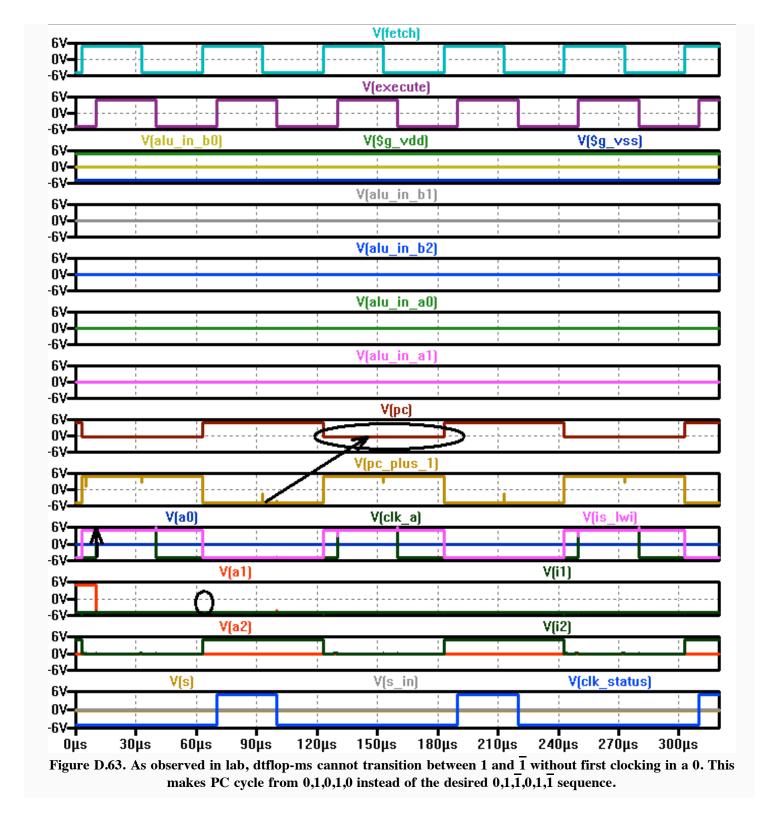

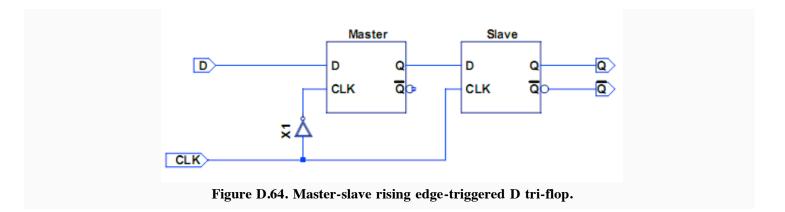

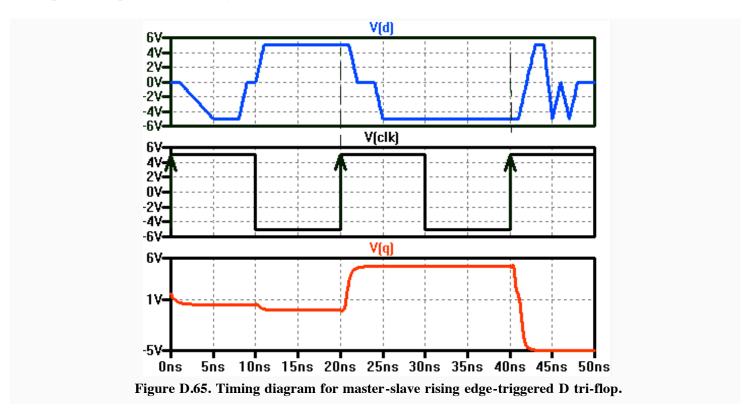

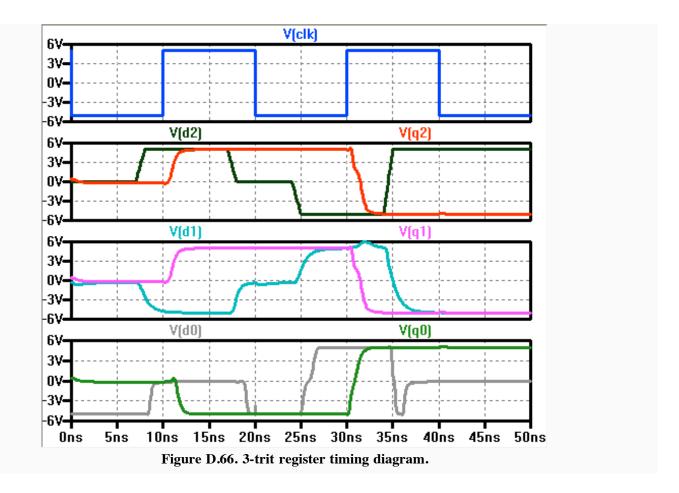

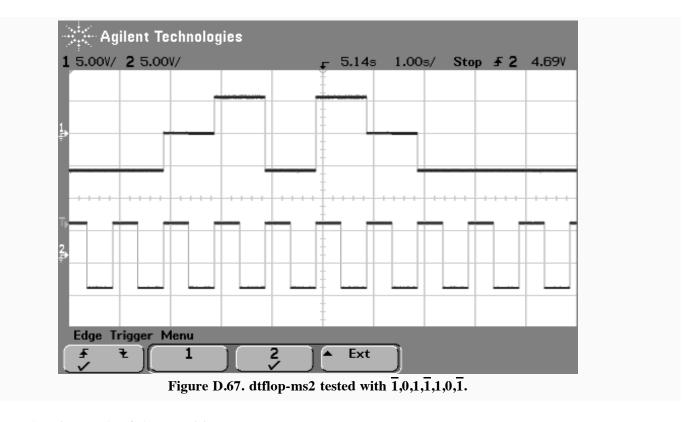

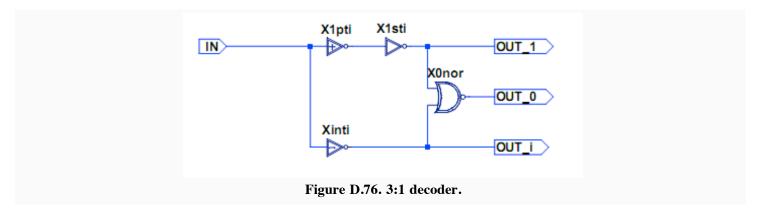

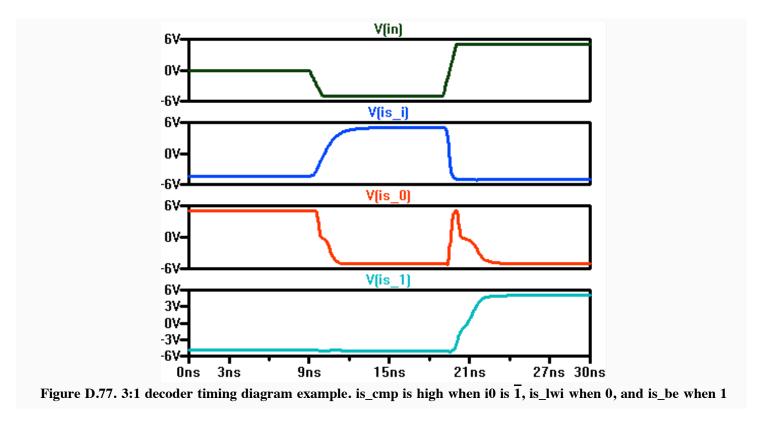

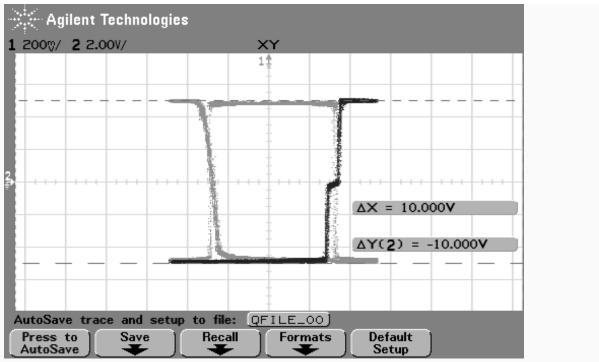

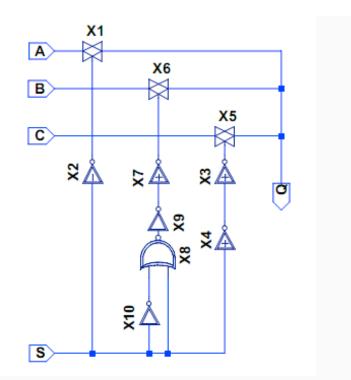

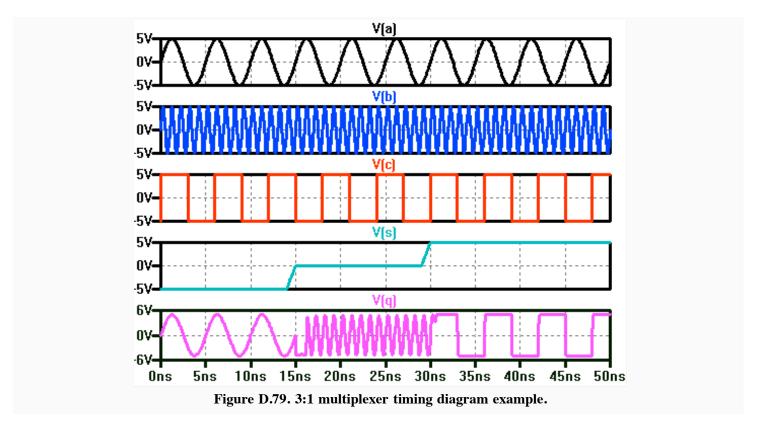

- 28. S.L. Hurst, "Multiple-valued logic--its status and its future," IEEE Transactions on Computers, vol. C-33, no. 12, pp. 1160-1179, December 1984.