# MESL: Proposal for a Non-volatile Cascadable <u>Magneto-Electric Spin Logic</u>

# Akhilesh Jaiswal<sup>1,\*</sup>, and Kaushik Roy<sup>1</sup>

<sup>1</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, 47907, USA

\* jaiswal@purdue.edu

# Abstract

In the quest for novel, scalable and energy-efficient computing technologies, many non-charge based logic devices are being explored. Recent advances in multi-ferroic materials have paved the way for electric field induced low energy and fast switching of nano-magnets using the magneto-electric (ME) effect. In this paper, we propose a voltage driven logic-device based on the ME induced switching of nano-magnets. We further demonstrate that the proposed logic-device, which exhibits decoupled read and write paths, can be used to construct a complete logic family including XNOR, NAND and NOR gates. The proposed logic family shows good scalability with a quadratic dependence of switching energy with respect to the switching voltage. Further, the proposed logic-device has better robustness against the effect of thermal noise as compared to the conventional current driven switching of nano-magnets. A device-to-circuit level coupled simulation framework, including magnetization dynamics and electron transport model, has been developed for analyzing the present proposal. Using our simulation framework, we present energy and delay results for the proposed Magneto-Electric Spin Logic (MESL) gates.

# Introduction

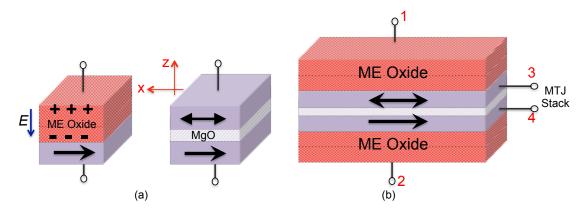

**Figure 1**. (a) (Left) Figure illustrating the ME switching of a ferro-magnet with applied electric field. A positive voltage on the upper terminal switches the magnet in positive x direction and *vice-versa* (Right) An MTJ stack consisting of an MgO sandwiched between two nano-magnets. The resistance of the MTJ is a function of the voltage and the relative orientation of the magnetization directions. (b) The proposed four terminal logic-device. The upper (lower) nano-magnet can be switched by application of a voltage pulse on terminal 1 (2). The resistance of the MTJ stack can be sensed between terminals 3 and 4. The thickness of the ME oxide and the MgO spacer can be tuned independently to improve the write-efficiency and the sensing margin simultaneously.

CMOS technology has been the driving force behind the ever improving computing efficiency for the past few decades [1],[2]. However, as the miniaturization of CMOS devices continues, issues like the leakage power consumption, short channel effects, increased variability *etc.* have necessitated exploration of novel devices [3], [4]. Further, with the current emphasis on smart sensors and Internet of Things (IoT), low leakage non-volatile computing devices have became more attractive than ever before. Such beyond-CMOS logic devices are expected to augment/complement the existing CMOS technology [5].

Spin based logic devices are a promising candidate for beyond-CMOS technologies due to 1) non-volatility (ability to retain data in absence of power supply) and hence low leakage power consumption and 2) area-efficiency. As such, many proposals for logical operations using spin devices can be found in the literature. All spin logic (ASL) [6], [7] is one of the widely studied logic families based on non-local spin currents. The dependence of ASL logic on non-local spin currents presents a major drawback due to short *spin-flip* lengths in metallic channels. On the other hand, non-volatile logic based on magnetic tunnel junctions (MTJs) embedded within CMOS logic circuits were explored in [8]. In addition, ME based logic devices have

been explored in [9], [10]. The ME logic presented in [9] suffers from the requirement of a complex DC (direct current) bridge including three resistors for cascading. In [10], an XOR device was proposed, however details of cascading and the complexity of the required cascading circuits is missing. Recently, a spin logic based on magneto-electric switching and the Inverse Rashba Edelstein effect was proposed in [11]. In the present paper, we not only demonstrate that our proposed logic-device can function as XNOR, NAND and NOR gate based on the configuration but also show that easy cascadability can be achieved by using minimal number of CMOS devices.

Specifically, we combine two scalable physics, 1) the switching of a ferro-magnet through a multi-ferroic material using the ME effect and 2) the resistance change of an MTJ as a function of the magnetization directions of the constituting ferro-magnets, to propose a non-volatile cascadable Magneto-Electric Spin Logic (MESL). The key highlights of the present work are as follows:

- We exploit the inherent coupling of multi-ferroic materials with the underlying magnetization direction of a ferro-magnet to achieve voltage driven low energy switching of nano-magnets. By stacking two such nano-magnets, in contact with respective ME oxides, we form an MTJ stack. We demonstrate that the resulting device can be used as a logic-element that can be used to implement complex Boolean functions.

- 2) Using a coupled magnetization dynamics and electron transport simulation, we show that the proposed logic-device exhibits good scalability, better robustness with respect to the influence of thermal noise and high switching speed as compared to the conventional current driven switching of nano-magnets.

- Realizations of two input XNOR, NAND and NOR gates, forming a complete logic family, has been demonstrated. Further, we show that the proposed MESL gates can be easily cascaded using a *global-reset* operation and *domino-style* clocking.

- 4) Typically CMOS logic family requires area expensive storage elements (for example, a flip-flop circuit), in order to retain the output of the logic gates. Such flip-flop circuits become redundant in the proposed MESL gates due to its inherent non-volatility.

# **ME Effect and Proposed Logic-Device**

ME effect is the physics of generating magnetization from an applied electric field [12],[13]. ME devices usually consists of a single phase or composite multi-ferroic material (for example  $BiFeO_3$  [14],  $BaTiO_3$  [15]) in contact with a nano-magnet. Application of an electric field to the multi-ferroic material results in an effective magnetic field experienced by the nano-magnet. If the generated magnetic field is strong enough, the magnetization of the nano-magnet can be reversed. This electric field driven switching of the nano-magnets, shows better energy efficiency and speed, as compared to the classic current induced spin-transfer-torque switching [16].

In the case of a single phase ME oxide (like BiFeO<sub>3</sub>), the switching of the nano-magnet due to applied electric field can be explained as follows [14]. BiFeO<sub>3</sub> is a ferro-electric material. Ferro-electricity in BiFeO<sub>3</sub> arises due to the shift of Bi<sup>+</sup> cations owing to its hybridization with the surrounding oxygen atoms [17]. The electric polarization of BiFeO<sub>3</sub>, which is coupled to the (anti) ferromagnetism of the constituent Fe atoms, can be switched by the application of an electric field. Further, the (anti) ferromagnetism of BiFeO<sub>3</sub> can be coupled to the ferro-magnetism of an underlying nano-magnet. The magnetization of the nano-magnet can be switched in response to the applied electric field across BiFeO<sub>3</sub> [14]. The various coupling mechanisms that lead to electric-field driven reversal of magnetization direction in the underlying ferromagnet is currently a topic of intense research [14],[15].

Nevertheless, the efficiency of the ME effect is usually abstracted by the ME-coefficient denoted as  $\alpha_{ME}$  [14].  $\alpha_{ME}$  is the ratio of magnetic field generated per unit applied electric field. Experimentally,  $\alpha_{ME}$  of  $1 \times 10^{-7}$  s m<sup>-1</sup> has been reported in the literature [14]. Schematically, an ME switched nano-magnet is shown in Fig. 1(a). When an electric field is applied in the +z direction, the nano-magnet switches to the +x direction due to the ME effect. If the direction of the applied electric field is reversed, the nano-magnet switches to -x direction.

Along side the ME switched magnet in Fig. 1(a), we also show a conventional MTJ stack consisting of an oxide-spacer separating two nano-magnets. A parallel alignment of the magnetization directions in both the nano-magnets results in a low resistance state, while an anti-parallel alignment leads to a high resistance state. The difference in the parallel and anti-parallel resistance is usually indicated by a term called Tunnel Magneto-Resistance (TMR) ratio. In order to maximize the TMR, MgO is usually used as the oxide-spacer in the MTJ stack. The use of MgO as the oxide-spacer can be justified from first principles analysis [18], which indicates that the coupling of the Bloch states between the nano-magnet and MgO has an important role in deciding the overall resistance of the MTJ stack.

Thus, we are dealing with two oxides - ME oxide for switching the nano-magnet and MgO for reading the state of the MTJ stack. In Fig. 1(b), we show the proposed device structure. It consists of two nano-magnets in contact with respective ME oxides. Due to their multi-ferroic nature, each of the ME oxides are coupled to the magnetization direction of the underlying

nano-magnet. When a positive voltage is applied on the upper or the lower ME oxide, the corresponding nano-magnets switch to +x direction, while for a negative voltage the magnets point in the -x direction. The upper and the lower nano-magnets are separated by an MgO spacer to form an MTJ stack, thus constituting the four-terminal device structure.

The four-terminal nature of the proposed device leads to decoupled read and write paths. Terminals 1 and 2 can be used as the write terminals by applying proper voltage levels to switch the underlying nano-magnets. We assume the ME oxides are thick enough such that the tunneling current flowing through the ME oxides is small enough to be neglected. On the other hand, the state of the device can be read by passing a current (or applying a voltage) between terminals 3 and 4. The proposed logic-device thus exhibits 1) low energy consumption due to electric field switching 2) decoupled read/write path such that respective oxides (ME oxide and MgO) can be optimized separately for read and write operations. In the next section, we describe how the proposed logic-device of Fig. 1(b) can be used for constructing non-volatile XNOR, NAND and NOR gates.

# ME Logic Family and Cascadability

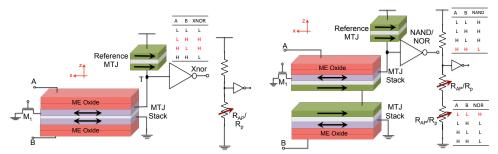

**Figure 2**. (a) Proposed ME XNOR gate. Only when both the ferro-magnets point in the same direction, the output of the inverter goes high, thus implementing an XNOR function. Inset shows the truth table for the XNOR function. L represents a digital 0 and H represents a digital 1. (b) Proposed ME NAND/NOR gate. For NAND operation, the inverter is sized such that the output goes low only if both the MTJ stacks are in anti-parallel (high-resistance) state. Whereas, for NOR operation, the sizing of the output inverter is such that it goes high only if both the MTJ stacks are in parallel (low-resistance) state.

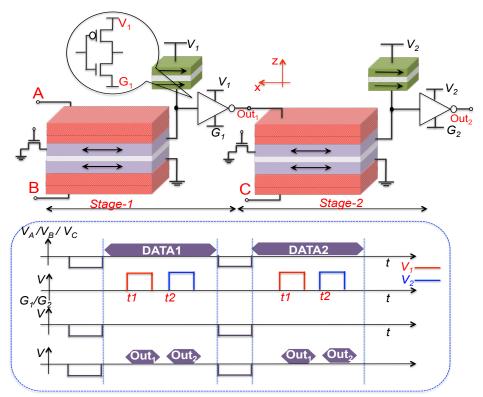

**Figure 3**. Figure illustrating cascading of two ME XNOR gates. Initially, a reset operation is carried out by applying negative voltage pulses on terminals 'A', 'B', 'C', ' $G_1$ ' and ' $G_2$ '. On the other hand, when data is applied the two stages are activated in a typical domino-style, one after another. A representative timing diagram illustrates the waveforms on various nodes.

The proposed two-input XNOR gate is shown in Fig. 2(a). The inputs to the XNOR gate are terminals 'A' and 'B'. A positive voltage represents a digital '1' and a negative voltage represents a digital '0'. If, both the inputs are the same, the two nano-magnets will either point in +x direction or in -x direction and the MTJ stack would be in the low resistance (parallel) state.

The voltage divider consisting of the reference MTJ and the actual MTJ stack, will drive the output of the inverter high, if and only if the MTJ stack is in parallel (low resistance) state. Thus, an XNOR function can be implemented using the configuration shown in Fig. 2(a). It is to be noted that while the resistance of the MTJ is being sensed, the voltage divider effect results in a non-zero voltage on the upper ferro-magnet denoted as node 'T' in Fig. 2(a) . Since the upper ferro-magnet constitutes one of the plates of the upper ME capacitor, the voltage at node 'T' might switch the direction of the upper ferro-magnet. In order to avoid any inadvertent switching of the ferro-magnet, the sensing voltage, the resistance of the reference MTJ and the trip-point of the inverter were selected such that the voltage at node 'T' is less than the minimum voltage required to switch the ferro-magnet.

Next, we propose an ME NAND gate as illustrated in Fig. 2(b). The proposed NAND gate is composed of a series connection of two ME logic-devices. Each of the two series connected ME logic-device consists of an ME oxide in contact with a nanomagnet and separated by a fixed magnet using MgO spacer. The two MTJ stacks, shown in Fig. 2(b), switch to the high resistance anti-parallel state, only if the corresponding inputs are high. The output circuit forms a voltage divider as shown on the right hand part of Fig. 2(b). The ratio of the widths of PMOS and NMOS transistors in the output inverter are chosen such that the inverter output goes low if and only if both the MTJ stacks are in the high resistance (anti-parallel) state (or in other words both the inputs 'A' and 'B' are high). Thus, the circuit in Fig. 2(b) implements a NAND function by proper selection of the transistor widths. Interestingly, the same circuit shown in Fig. 2(b) can also mimic the behavior of a NOR gate. For the NOR gate, the PMOS and NMOS transistors in the inverter are sized such that, output of the inverter goes high if and only if both the MTJ stacks are in low resistance state (or in other words only if both 'A' and 'B' are low).

Now that we have all the basic gates for computations, we would present the cascadability of our proposed logic gates. As an example, let us consider, cascading two ME-XNOR gates. As shown in Fig. 3, the output of the first XNOR gate is connected directly to the input of the next XNOR gate. Initially, we do a reset operation by application of a negative voltage pulse so that all the magnets point in the -x direction. This can be achieved by applying a negative voltage on input terminals 'A', 'B' and 'C', as shown in the timing diagram of Fig. 3. Simultaneously, we pull the 'G<sub>1</sub>' and 'G<sub>2</sub>' terminals of the inverter to negative reset voltages, thus, driving the output of inverters to negative voltages. As such, a global reset can be achieved by simply applying a negative voltage on all the input and the intermediate terminals.

After the reset phase, terminals 'G<sub>1</sub>' and 'G<sub>2</sub>' are kept at zero volts for normal operation. Data inputs can now be applied on terminals 'A', 'B' and 'C'. Based on the the inputs at 'A', 'B' and 'C' the input magnets would flip if required, making the MTJ stack either high or low resistance. We then apply, voltage pulses on nodes 'V<sub>1</sub>' and 'V<sub>2</sub>' one after another, in a typical domino style [19]. When a voltage pulse is applied on node 'V<sub>1</sub>', stage 1 (see Fig. 3) evaluates and the node 'Out<sub>1</sub>' goes high or to zero volts. If 'Out<sub>1</sub>' is high, the next stage magnet corresponding to terminal 'Out<sub>1</sub>' switches to +x-direction. If, however, the inputs are such that node 'Out<sub>1</sub>' remains at zero volts, the corresponding next stage magnet does not switch and stays in the desired -x direction. Once the first stage has evaluated, we apply a pulse on terminal 'V<sub>2</sub>', stage-2 evaluates and produces the desired output on 'Out<sub>2</sub>'.

Thus, easy cascadability, is achieved by use of the reset scheme and domino style clocking. Though, clocking is necessary for functioning of the proposed gates, it has been used in almost all non-volatile spin logic to reduce leakage power consumption [6], [11].

### **Modeling and Simulation**

Next, we describe the modeling and simulation framework that was developed to evaluate the proposed ME gates. The device level simulation framework consisted of coupled magnetization dynamics and electron transport model. The required voltage and the time taken for deterministic switching of the nano-magnet due to the ME effect were obtained from stochastic-magnetization dynamics equations including thermal noise. On the other hand, the resistance of the MTJ stack in parallel and anti-parallel state, as a function of the applied voltage was estimated using Non-equilibrium Greens function (NEGF) formalism [20].

Under mono-domain approximation, the magnetization dynamics were modeled using the well-know phenomenological equation called the *Landau-Lifshiz-Gilbert* (LLG) equation [21]. LLG equation can be written as [22]

$$\frac{\partial \widehat{m}}{\partial \tau} = -\widehat{m} \times \vec{H}_{EFF} - \alpha \widehat{m} \times \widehat{m} \times \vec{H}_{EFF} \tag{1}$$

where  $\tau$  is  $\frac{|\gamma|}{1+\alpha^2}t$ . In (1),  $\alpha$  is the Gilbert damping constant,  $\gamma$  is the gyromagnetic ratio,  $\hat{m}$  is the unit vector in the direction of the magnetization, t is time and  $H_{EFF}$  is the effective magnetic field.  $H_{EFF}$  can be written as

$$H_{EFF} = \vec{H}_{demag} + \vec{H}_{interface} + \vec{H}_{thermal} + \vec{H}_{ME}$$

<sup>(2)</sup>

where  $\vec{H}_{demag}$  is the demagnetization field due to shape anisotropy.  $\vec{H}_{interface}$  is interfacial perpendicular anisotropy,  $\vec{H}_{thermal}$  is the stochastic field due to thermal noise and  $\vec{H}_{ME}$  is the field due to ME effect.

| Table 1. Summary of Parameters used for our simulations |                   |

|---------------------------------------------------------|-------------------|

| Parameters                                              | Value             |

| Magnet Length $(L_{mag})$                               | $45nm\times2.5$   |

| Magnet Width $(W_{mag})$                                | 45nm              |

| Magnet Thickness $(t_{FL})$                             | 2.5nm             |

| ME Oxide Thickness $(t_{ME})$                           | 5nm               |

| Saturation Magnetization $(M_S)$                        | 1257.3 KA/m [28]  |

| Gilbert Damping Factor ( $\alpha$ )                     | 0.03              |

| Interface Anisotropy $(K_i)$                            | $1mJ/m^2$ [28]    |

| ME Co-efficient ( $\alpha_{ME}$ )                       | $0.15/c^*ms^{-1}$ |

| Relative Di-electric constant ( $\epsilon_{ME}$ )       | 500 [11]          |

| Temperature $(T)$                                       | 300K              |

| CMOS Technology                                         | 45nm PTM [29]     |

| *c = Speed of light.                                    |                   |

$\vec{H}_{demag}$  can be written in SI units as [23]

$$\vec{H}_{demag} = -M_S(N_{xx}m_x\hat{x}, N_{yy}m_y\hat{y}, N_{zz}m_z\hat{z})$$

(3)

where  $m_x$ ,  $m_y$  and  $m_z$  are the magnetization moments in x, y and z directions respectively.  $N_{xx}$ ,  $N_{yy}$  and  $N_{zz}$  are the demagnetization factors for a rectangular magnet estimated from analytical equations presented in [24].  $M_s$  is the saturation magnetization. The interfacial anisotropy can be represented as [25]

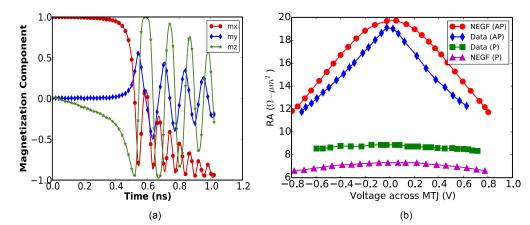

Figure 4. (a) A typical evolution of magnetization components mx, my, mz on application of a voltage pulse. The magnet is being switched from +x direction to -x direction. (b) The parallel and anti-parallel resistance obtained from our NEGF model [26] and benchmarked to experimental data from [27]. The resistance-voltage characteristics of Fig 4(b), were abstracted into a behavioral model for simulation.

$$\vec{H}_{interface} = \left(0\hat{x}, 0\hat{y}, \frac{2K_i}{\mu_o M_S t_{FL}} m_z \hat{z}\right) \tag{4}$$

where  $K_i$  is the effective energy density for interface perpendicular anisotropy and  $t_{FL}$  is thickness of the free layer. As mentioned earlier, the ME effect can be abstracted through the parameter  $\alpha_{ME}$  [11]

$$\vec{H}_{ME} = \left(\alpha_{ME} \left(\frac{V_{ME}}{t_{ME}}\right) \hat{x}, \ 0 \hat{y}, \ 0 \hat{z}\right) \tag{5}$$

where,  $\alpha_{ME}$  is the co-efficient for ME effect,  $V_{ME}$  is the voltage applied across the terminals of the ME capacitor and  $t_{ME}$  is thickness of the ME oxide, responsible for induction of a magnetic field in response to an applied electric field.  $\vec{H}_{ME}$  was multiplied with suitable constant for unit conversion.

The thermal field was included by the following stochastic equation [30]

$$\vec{H}_{thermal} = \vec{\zeta} \sqrt{\frac{2\alpha k_B T}{|\gamma| M_S Vol \ dt}} \tag{6}$$

where  $\vec{\zeta}$  is a vector with components that are zero mean Gaussian random variables with standard deviation of 1. Vol is the volume of the nano-magnet, T is ambient temperature, dt is simulation time step and  $k_B$  is Boltzmann's constant.

Equations (1)-(6) constitute a set of stochastic differential equations. This system of equations was solved numerically by using the Heun's method [31]. The solution of the given set of equations, enable us to get the required voltage as well as the switching time for the nano-magnets used in our simulations. The various device dimensions and material parameters used in our simulations are summarized in Table I. A typical evolution of the magnetization components in response to an voltage pulse is shown in Fig. 4(a).

It is to be noted that, multi-ferroics and ME effect is currently an active research area [12], [13]. Although many theoretical works have proposed models for describing the origin and the behavior of the ME effect, yet a detailed understanding of the physics of ME effect is still under intense research investigation. Further, experimental demonstration of ME switched ferro-magnets can be found in the literature as in [14], yet a global magnetization reversal by ME effect has remained elusive. Due to lack of such experimental results, the ME parameters mentioned in Table I, are not tied to any particular material system or experiment, they are more like predictive parameters that abstract the details of the ME switching into a simple model which can be used in conjunction with the LLG equation to predict the switching time and energy. A more rigorous benchmarking of ME parameters for future logic devices can be found elsewhere as in [32]. Note, the functionality of the present proposal does not depend on the exact values of the ME parameters used for simulation. Therefore, our simple ME model serves the purpose to check the feasibility of our present proposal from device as well as circuits perspective.

The magnetization dynamics equations were coupled with the resistance of the MTJ stack, which was modeled using the non-equilibrium Green's function (NEGF) formalism. A detailed description of the NEGF model for MTJs can be found in [26]. The parallel and anti-parallel resistance obtained from our experimentally benchmarked NEGF equations were then abstracted into a behavioral model. The magnetization dynamics equations along with the resistance of the MTJ stack obtained from the NEGF equations, provided a coupled device model that can be used for characterizing the proposed logic-device.

# **Device Characteristics**

Any emerging logic technology must exhibit desirable characteristics with respect to scalability, speed of operation *etc*. Using our simulation framework presented in the previous section, we highlight some of the key characteristics of the logic-device proposed in Fig. 1(b) - a) scalability b) stochastic switching dynamics and c) switching speed.

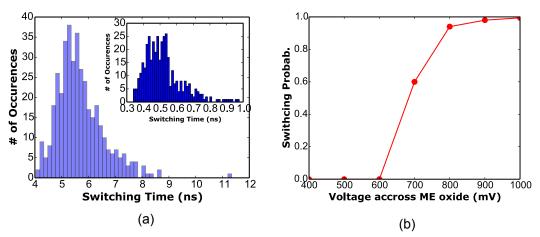

Figure 5. (a)The distribution of switching time for a typical STT based mechanism for constant input current. Inset shows corresponding distribution of switching time for ME based switching for a constant applied electric field. (b) Switching probability as a function of applied voltage across the ME oxide for a switching delay of 500ps. The switching probability has been obtained by running 1,000 LLG simulations with thermal noise.

#### A. Scalability

The device in Fig. 1(b) shows good scaling in terms of voltage and energy requirements. This desirable scaling trend can be attributed to the decrease in the ME capacitance with the decrease in ME oxide area. In fact, the switching energy (proportional to  $CV^2$ , C being the ME oxide capacitance and V the voltage required to switch the nano-magnet) linearly decreases with the scaling in ME oxide area and has a square law dependence with respect to voltage scaling.

Additionally, the proposed device also requires an MTJ stack for a read-out operation. Recently, many experimental works [33], [34] have demonstrated scaling of the MTJ structure to as small as 20nm in diameter. Thus, in terms of areal dimensions of the ME oxide as well as the MTJ stack, the proposed device shows desirable scaling trend.

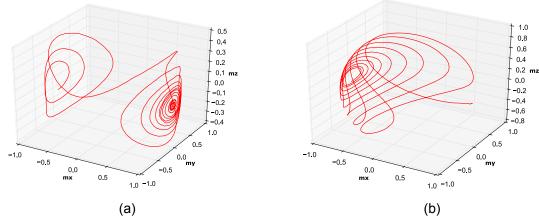

Figure 6. (a) A typical trajectory followed by the magnetization vector when switched using STT mechanism. The STT mechanism initially acts as an antidamping torque and subsequently as a damping torque thereby switching the state of the ferro-magnet. (b) A typical trajectory followed by the magnetization vector when switched using the ME mechanism. With application of an external voltage the magnetization tries to orient itself towards the direction of the ME field and finally dampens, resulting in a  $180^{\circ}$  switching of the ferro-magnet.

#### B. Stochasticity

The switching dynamics of a nano-magnet is known to be a stochastic process due to the random thermal field as per equation (6). The stochastic switching behavior of the nano-magnets have been exploited for random number generation [35] and in neuromorphic applications [36]. However, in the present scenario for Boolean logic gates, we need deterministic switching process. Thermal noise has a lesser detrimental effect on ME switched nano-magnets as opposed to the conventional Spin Transfer Torque (STT) switching mechanism. For STT switching, the switching process is initiated by the thermal field. STT effect dominates only when thermal noise has sufficiently disturbed the initial direction of the magnetization vector from its *easy axis* [37]. On the other hand, ME switching does not require such an initiation of the switching process by the thermal field.

In Fig. 5(a), we have shown the distribution of the switching time for constant current in case of STT switching process and for constant voltage for ME switched nano-magnets. It can be observed that, the spread in distribution of switching time is much lesser for ME switching as compared to the STT switching dynamics. For a given time duration (500ps), the switching probability versus the voltage across the ME oxide is shown in Fig. 5(b). Based on Fig. 5(b), we selected the operating voltage such that the switching probability is  $\sim$ 1.

#### C. Switching Speed

ME driven magnetization dynamics can lead to sub-1ns switching speed as compared to the STT mechanism which typically requires 5-10ns of switching time. For STT switching, the STT effect acts as an anti-damping torque initially and as a damping torque subsequently thereby switching the nano-magnet. A typical STT switching curve is shown in Fig. 6(a). On the other hand, ME switching follows a much simpler dynamics, similar to the switching process due an external magnetic field, as shown in Fig. 6(b). For the material parameters shown in Table I, the nano-magnets used in our simulations could switch within 500ps. Thus, as compared to other non-volatile logic devices based on injection of spin current and STT switching mechanism [7], the proposed logic-device shows faster switching speed. In practice, the total switching time would be the sum of the switching time of the ferro-electric polarization in the ME oxide and the ferro-magnetic switching estimated from our LLG equations. Theoretically, the ferro-electric switching time can be of the order ~ 70ps [38], which is much less than the ferro-magnetic switching time estimated from our simulations. We have therefore, neglected the ferro-electric switching time in our calculations.

# **Results and Discussions**

The energy associated with a single gate, for example the XNOR gate of Fig. 2(a), can be estimated as follows. The total switching energy would consists of the energy to reset the two nano-magnets, the energy to switch the nano-magnets depending on the incoming data and the energy to turn ON the transistor M1 shown in Fig. 2(a).

$$E_{Swi\ Total} = 2C_{ME}V_{Reset}^2 + 2C_{ME}V_{Data}^2 + C_GV_G^2 \tag{7}$$

where  $C_{ME}$  is the capacitance of the ME capacitor,  $C_G$  is the gate capacitance of transistor M1,  $V_{Reset}$  is the reset voltage,  $V_{Data}$  is the voltage on terminals 'A'/'B' and  $V_G$  is the gate voltage for transistor M1. Using our simulation  $E_{Swi \ Total}$  was estimated to be 5.5 fJ. Similarly, the read-out energy would consists of the energy associated with the voltage divider and the inverter. From our simulations, the read-out energy was estimated to be 30 fJ, assuming a time duration of 500ps.

# Conclusions

Non-volatile logic devices are of particular interest given the current emphasis on low power mobile devices, event-driven sensing and Internet of Things. In the present work, we have exploited the ability to switch a ferro-magnet using the ME effect, to propose a non-volatile logic-device. Besides its inherent non-volatility, the present proposal achieves significant benefits in terms of switching energy of the ferro-magnets due to the use of ME effect. Further, the proposed MESL gates can be easily cascaded to implement more complex Boolean functions. From a device perspective, the proposed logic-device shows good scalability, better robustness to thermal fluctuations and high switching speed. We envisage that the proposed MESL gates could be a promising candidate for beyond-CMOS low leakage logic devices.

# Acknowledgments

The work was supported in part by, Center for Spintronic Materials, Interfaces, and Novel Architectures (C-SPIN), a MARCO and DARPA sponsored StarNet center, by the Semiconductor Research Corporation, the National Science Foundation, Intel Corporation and by the DoD Vannevar Bush Fellowship.

# References

- Auth, C. et al. A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In VLSI technology (VLSIT), 2012 symposium on, 131–132 (IEEE, 2012).

- [2] Borkar, S. Thousand core chips: a technology perspective. In Proceedings of the 44th annual Design Automation Conference, 746–749 (ACM, 2007).

- [3] Roy, K., Mukhopadhyay, S. & Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer cmos circuits. *Proceedings of the IEEE* 91, 305–327 (2003).

- [4] Mayer, F. et al. Impact of SOI, Si 1-x Ge x OI and GeOI substrates on CMOS compatible tunnel FET performance. In 2008 IEEE International Electron Devices Meeting, 1–5 (IEEE, 2008).

- [5] Roy, K., Jung, B., Peroulis, D. & Raghunathan, A. Integrated systems in the more-than-moore era: designing low-cost energy-efficient systems using heterogeneous components. *IEEE Design & Test* 33, 56–65 (2016).

- [6] Behin-Aein, B., Datta, D., Salahuddin, S. & Datta, S. Proposal for an all-spin logic device with built-in memory. Nature nanotechnology 5, 266–270 (2010).

- [7] Augustine, C. et al. Numerical analysis of domain wall propagation for dense memory arrays. In Electron Devices Meeting (IEDM), 2011 IEEE International, 17-6 (IEEE, 2011).

- [8] Matsunaga, S. *et al.* Fabrication of a nonvolatile full adder based on logic-in-memory architecture using magnetic tunnel junctions. *Applied Physics Express* 1, 091301 (2008).

- [9] Hu, J.-M., Li, Z., Lin, Y. & Nan, C. A magnetoelectric logic gate. physica status solidi (RRL)-Rapid Research Letters 4, 106–108 (2010).

- [10] Sharma, N., Bird, J., Dowben, P. & Marshall, A. Compact-device model development for the energy-delay analysis of magneto-electric magnetic tunnel junction structures. *Semiconductor Science and Technology* **31**, 065022 (2016).

- [11] Manipatruni, S., Nikonov, D. E. & Young, I. A. Spin-orbit logic with magnetoelectric nodes: A scalable charge mediated nonvolatile spintronic logic. arXiv preprint arXiv:1512.05428 (2015).

- [12] Fiebig, M. Revival of the magnetoelectric effect. Journal of Physics D: Applied Physics 38, R123 (2005).

- [13] Spaldin, N. A. & Fiebig, M. The renaissance of magnetoelectric multiferroics. Science 309, 391–392 (2005).

- [14] Heron, J. et al. Deterministic switching of ferromagnetism at room temperature using an electric field. Nature 516, 370–373 (2014).

- [15] Lahtinen, T. H., Franke, K. J. & van Dijken, S. Electric-field control of magnetic domain wall motion and local magnetization reversal. *arXiv preprint* arXiv:1109.5514 (2011).

- [16] Slonczewski, J. C. Current-driven excitation of magnetic multilayers. Journal of Magnetism and Magnetic Materials 159, L1-L7 (1996).

- [17] Ramesh, R. Electric field control of ferromagnetism using multi-ferroics: the bismuth ferrite story. *Philosophical Transactions of the Royal Society of London A: Mathematical, Physical and Engineering Sciences* 372, 20120437 (2014).

- [18] Butler, W., Zhang, X.-G., Schulthess, T. & MacLaren, J. Spin-dependent tunneling conductance of fe- mgo- fe sandwiches. *Physical Review B* 63, 054416 (2001).

- [19] Rabaey, J. M., Chandrakasan, A. P. & Nikolic, B. Digital integrated circuits, vol. 2 (Prentice hall Englewood Cliffs, 2002).

- [20] Datta, D., Behin-Aein, B., Salahuddin, S. & Datta, S. Quantitative model for tmr and spin-transfer torque in mtj devices. In *Electron Devices Meeting* (*IEDM*), 2010 IEEE International, 22–8 (IEEE, 2010).

- [21] Gilbert, T. L. A phenomenological theory of damping in ferromagnetic materials. *IEEE Transactions on Magnetics* 40, 3443–3449 (2004).

- [22] d'Aquino, M. Nonlinear magnetization dynamics in thin-films and nanoparticles. Ph.D. thesis, Università degli Studi di Napoli Federico II (2005).

- [23] Wang, Z. et al. Magnetization characteristic of ferromagnetic thin strip by measuring anisotropic magnetoresistance and ferromagnetic resonance. Solid State Communications 182, 10–13 (2014).

- [24] Aharoni, A. Demagnetizing factors for rectangular ferromagnetic prisms. Journal of applied physics 83, 3432–3434 (1998).

- [25] Jaiswal, A., Fong, X. & Roy, K. Comprehensive scaling analysis of current induced switching in magnetic memories based on in-plane and perpendicular anisotropies. *Journal on emerging and selected topics in circuits and systems* (2016).

- [26] Fong, X. et al. Knack: A hybrid spin-charge mixed-mode simulator for evaluating different genres of spin-transfer torque mram bit-cells. In 2011 International Conference on Simulation of Semiconductor Processes and Devices, 51–54 (IEEE, 2011).

- [27] Lin, C. et al. 45nm low power cmos logic compatible embedded stt mram utilizing a reverse-connection 1t/1mtj cell. In 2009 IEEE International Electron Devices Meeting (IEDM), 1–4 (IEEE, 2009).

- [28] Ikeda, S. et al. A perpendicular-anisotropy cofeb-mgo magnetic tunnel junction. Nature materials 9, 721-724 (2010).

- [29] [Online] http://ptm.asu.edu/.

- [30] Brown Jr, W. F. Thermal fluctuations of a single-domain particle. Journal of Applied Physics 34, 1319–1320 (1963).

- [31] Scholz, W., Schrefl, T. & Fidler, J. Micromagnetic simulation of thermally activated switching in fine particles. Journal of Magnetism and Magnetic Materials 233, 296-304 (2001).

- [32] Nikonov, D. E. & Young, I. A. Benchmarking spintronic logic devices based on magnetoelectric oxides. Journal of Materials Research 29, 2109-2115 (2014).

- [33] Kim, W. et al. Extended scalability of perpendicular stt-mram towards sub-20nm mtj node. In Electron Devices Meeting (IEDM), 2011 IEEE International, 24-1 (IEEE, 2011).

- [34] Gajek, M. et al. Spin torque switching of 20 nm magnetic tunnel junctions with perpendicular anisotropy. Applied Physics Letters 100, 132408 (2012).

- [35] Kim, Y., Fong, X. & Roy, K. Spin-orbit-torque-based spin-dice: A true random-number generator. *IEEE Magnetics Letters* 6, 1–4 (2015).

[36] Sengupta, A., Panda, P., Wijesinghe, P., Kim, Y. & Roy, K. Magnetic tunnel junction mimics stochastic cortical spiking neurons. *arXiv preprint* arXiv:1510.00440 (2015).

- [37] Mojumder, N. N. & Roy, K. Proposal for switching current reduction using reference layer with tilted magnetic anisotropy in magnetic tunnel junctions for spin-transfer torque (stt) mram. IEEE Transactions on Electron Devices 59, 3054-3060 (2012).

- [38] Li, J. et al. Ultrafast polarization switching in thin-film ferroelectrics. Applied physics letters 84, 1174–1176 (2004).