Published by JINST as 2021\_JINST\_16\_P12028

©2021 CERN for the benefit of the FASER Collaboration.

Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license.

# The trigger and data acquisition system of the FASER experiment

# **FASER** collaboration

Henso Abreu<sup>1</sup> Elham Amin Mansour<sup>2</sup> Claire Antel<sup>2</sup> Akitaka Ariga<sup>3,21</sup> Tomoko Ariga<sup>4</sup> Florian Bernlochner<sup>5</sup> Tobias Boeckh<sup>5</sup> Jamie Boyd<sup>6</sup> Lydia Brenner<sup>6</sup> Franck Cadoux<sup>2</sup> David W. Casper<sup>7</sup> Charlotte Cavanagh<sup>8</sup> Xin Chen<sup>9</sup> Andrea Coccaro<sup>10</sup> Stéphane Débieux<sup>2</sup> Sergey Dmitrievsky<sup>11</sup> Monica D'Onofrio<sup>8</sup> Candan Dozen<sup>9</sup> Yannick Favre<sup>2</sup> Deion Fellers<sup>12</sup> Jonathan L. Feng<sup>7</sup> Didier Ferrere<sup>2</sup> Enrico Gamberini<sup>6</sup> Edward Karl Galantay<sup>2</sup> Stephen Gibson<sup>13</sup> Sergio Gonzalez-Sevilla<sup>2</sup> Yuri Gornushkin<sup>11</sup> Carl Gwilliam<sup>8</sup> Shih-Chieh Hsu<sup>14</sup> Zhen Hu<sup>9</sup> Giuseppe lacobucci<sup>2</sup> Tomohiro Inada<sup>9</sup> Sune Jakobsen<sup>6</sup> Eliott Johnson<sup>2</sup> Enrique Kajomovitz<sup>1</sup> Felix Kling<sup>15</sup> Umut Kose<sup>6</sup> Susanne Kuehn<sup>6</sup> Helena Lefebvre<sup>13</sup> Lorne Levinson<sup>16</sup> Ke Li<sup>14</sup> Jinfeng Liu<sup>9</sup> Chiara Magliocca<sup>2</sup> Josh McFayden<sup>17</sup> Matteo Milanesio<sup>2</sup> Sam Meehan<sup>6</sup> Dimitar Mladenov<sup>6</sup> Théo Moretti<sup>2</sup> Magdalena Munker<sup>2</sup> Mitsuhiro Nakamura<sup>18</sup> Toshiyuki Nakano<sup>18</sup> Marzio Nessi<sup>6</sup> Friedemann Neuhaus<sup>19</sup> Laurie Nevay<sup>13</sup> Hidetoshi Otono<sup>4</sup> Carlo Pandini<sup>2</sup> Hao Pang<sup>9</sup> Lorenzo Paolozzi<sup>2</sup> Brian Petersen<sup>6</sup> Francesco Pietropaolo<sup>6</sup> Markus Prim<sup>5</sup> Michaela Queitsch-Maitland<sup>6</sup> Filippo Resnati<sup>6</sup> Chiara Rizzi<sup>2</sup> Hiroki Rokujo<sup>18</sup> Elisa Ruiz-Choliz<sup>19</sup> Jakob Salfeld-Nebgen<sup>6</sup> Osamu Sato<sup>18</sup> Paola Scampoli<sup>3,22</sup> Kristof Schmieden<sup>19</sup> Matthias Schott<sup>19</sup> Anna Sfyrla<sup>2</sup> Savannah Shively<sup>7</sup> Roland Sipos<sup>6</sup> John Spencer<sup>14</sup> Yosuke Takubo<sup>20</sup> Noshin Tarannum<sup>2</sup> Ondrej Theiner<sup>2</sup> Eric Torrence<sup>12</sup> Serhan Tufanli<sup>6</sup> Svetlana Vasina<sup>11</sup> Benedikt Vormwald<sup>6</sup> Di Wang<sup>9</sup>

<sup>&</sup>lt;sup>1</sup>Department of Physics and Astronomy, Technion—Israel Institute of Technology, Haifa 32000, Israel

<sup>&</sup>lt;sup>2</sup>Département de Physique Nucléaire et Corpusculaire, University of Geneva, CH-1211 Geneva 4, Switzerland

<sup>&</sup>lt;sup>3</sup>Albert Einstein Center for Fundamental Physics, Laboratory for High Energy Physics, University of Bern, Sidlerstrasse 5, CH-3012 Bern, Switzerland

<sup>&</sup>lt;sup>4</sup>Kyushu University, Nishi-ku, 819-0395 Fukuoka, Japan

<sup>&</sup>lt;sup>5</sup>Universität Bonn, Regina-Pacis-Weg 3, D-53113 Bonn, Germany

<sup>&</sup>lt;sup>6</sup>CERN, CH-1211 Geneva 23, Switzerland

<sup>&</sup>lt;sup>7</sup>Department of Physics and Astronomy, University of California, Irvine, CA 92697-4575, USA

<sup>&</sup>lt;sup>8</sup>University of Liverpool, Liverpool L69 3BX, United Kingdom

<sup>&</sup>lt;sup>9</sup>Department of Physics, Tsinghua University, Beijing, China

<sup>&</sup>lt;sup>10</sup>INFN Sezione di Genova, Via Dodecaneso, 33–16146, Genova, Italy

ABSTRACT: The FASER experiment is a new small and inexpensive experiment that is placed 480 meters downstream of the ATLAS experiment at the CERN LHC. FASER is designed to capture decays of new long-lived particles, produced outside of the ATLAS detector acceptance. These rare particles can decay in the FASER detector together with about 500–1000 Hz of other particles originating from the ATLAS interaction point. A very high efficiency trigger and data acquisition system is required to ensure that the physics events of interest will be recorded. This paper describes the trigger and data acquisition system of the FASER experiment and presents performance results of the system acquired during initial commissioning.

<sup>&</sup>lt;sup>11</sup>Joint Institute for Nuclear Research, Dubna, Russia

<sup>&</sup>lt;sup>12</sup>University of Oregon, Eugene, OR 97403, USA

<sup>&</sup>lt;sup>13</sup>Royal Holloway, University of London, Egham, TW20 0EX, UK

<sup>&</sup>lt;sup>14</sup>Department of Physics, University of Washington, PO Box 351560, Seattle, WA 98195-1560, USA

<sup>&</sup>lt;sup>15</sup>Deutsches Elektronen-Synchrotron DESY, Notkestrasse 85, 22607 Hamburg, Germany

<sup>&</sup>lt;sup>16</sup>Department of Particle Physics and Astrophysics, Weizmann Institute of Science, Rehovot 76100, Israel

<sup>&</sup>lt;sup>17</sup>Department of Physics & Astronomy, University of Sussex, Sussex House, Falmer, Brighton, BN1 9RH, United Kingdom

<sup>&</sup>lt;sup>18</sup>Nagoya University, Furo-cho, Chikusa-ku, Nagoya 464-8602, Japan

<sup>&</sup>lt;sup>19</sup>Institut für Physik, Universität Mainz, Mainz, Germany

<sup>&</sup>lt;sup>20</sup>Institute of Particle and Nuclear Study, KEK, Oho 1-1, Tsukuba, Ibaraki 305-0801, Japan

<sup>&</sup>lt;sup>21</sup>Department of Physics, Chiba University, 1-33 Yayoi-cho Inage-ku, Chiba, 263-8522, Japan

<sup>&</sup>lt;sup>22</sup>Dipartimento di Fisica "Ettore Pancini", Università di Napoli Federico II, Complesso Universitario di Monte S. Angelo, I-80126 Napoli, Italy

#### **Contents** The FASER experiment at the CERN LHC 2 TDAQ system overview 4 **TDAQ** hardware components 6 3.1 LHC signals and the FASER clock 6 3.2 PMT digitizer board 8 3.3 General Purpose I/O module 3.4 Trigger logic board 9 3.5 Tracker read-out 13 3.6 Crates 14 3.7 Computing and networking components 14 DAQ software 16 4.1 DAQ software framework 16 4.2 Data format and event size 17 4.3 Read-out software: digitizer 18 4.4 Read-out software: GPIOdrivers 19 5 Controls and monitoring software 20 5.1 Run control and configuration 20 5.2 Monitoring 21 5.3 DCS 23 **25 Commissioning and system performance** Digitizer standalone commissioning 25 6.1 6.2 TLB standalone commissioning 27 6.3 TRB standalone commissioning 30 6.4 DAQ software and server performance tests 32 6.5 Combined system measurements 33 Summary **39**

## 1 The FASER experiment at the CERN LHC

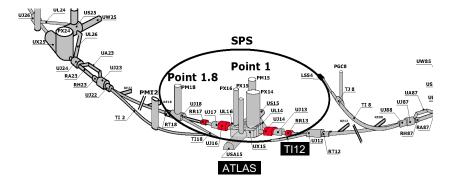

The FASER experiment [1, 2] is a new small experiment located along the beam collision axis line of sight (LOS), about 480 m downstream of ATLAS, in the TI12 tunnel in the LHC complex at CERN, as shown in figure 1. The FASER detector design is motivated by the signature of a new particle, such as a dark photon, decaying to two high-energy oppositely charged particles, such as an electron-positron pair [3, 4]. For a dark photon of 100 MeV mass and 1 TeV energy, the two particles to which it will decay are expected to be extremely collimated; this leads to requirements for a strong magnetic field and excellent tracking resolution, such that the electron and positron can be identified, as well as good energy measurements for electromagnetic deposits. The detector design has as additional drivers the cost and tight timeline between experiment approval (March 2019) and desired installation (before the Run 3 data taking would start). This results in a detector that recycles active components from other experiments and minimizes services to simplify installation and operation. About 500–1000 Hz of energetic particles from the interaction point (IP) will be recorded by the trigger and data acquisition (TDAQ) system of the experiment during proton–proton (pp) collisions in ATLAS. Despite its simple design, the TDAQ system necessitates robustness and stability to guarantee high efficiency in recording signal events, which are expected to be rare.

**Figure 1**. The FASER location: TI12 tunnel, 480 m downstream of the ATLAS interaction point. The detector is located along the beam collision axis line of sight.

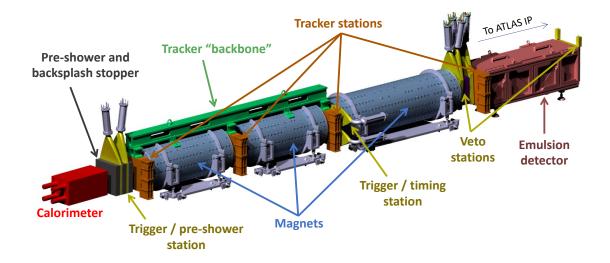

The FASER detector, all components of which are shown in figure 2, is a 5.5 m-long spectrometer, with a 20 cm aperture and a decay volume length of 1.5 m. The detector consists of tracking stations, scintillator stations and a calorimeter. It is complemented by additional detector components that constitute the FASER $\nu$  part of the experiment [5, 6], which aims at precisely measuring cross-sections of neutrinos originating from the ATLAS IP. FASER $\nu$  is composed of a 1.1 tn emulsion film detector with tungsten plates and is complemented by an additional tracker station, referred to as the interface tracker station, IFT, and scintillators. This part of the detector was proposed and approved later than the rest.

The FASER detector volume is dominated by three dipole permanent magnets of a fixed  $0.55\,\mathrm{T}$  field with Samarium Cobalt ( $\mathrm{Sm_2Co_{17}}$ ) magnetic material. They are based on a Halbach array design [7], which maximizes the field without the need for complicated support infrastructure. The first of the three magnets has a length of  $1.5\,\mathrm{m}$  and surrounds the experiment's decay volume. The other two magnets are each  $1\,\mathrm{m}$  long.

The tracker is a key component of the FASER detector. It is composed of four tracking stations of three silicon layers each. Each silicon layer is composed of 8 double-sided silicon strip modules, resulting in 96 modules in total. ATLAS SCT [8] spare modules are used, carefully selected based on a series of quality assurance tests. The modules are assembled in aluminum frames and read out using general purpose readout boards. A mechanical structure connecting the three stations and the two magnets that make up the FASER spectrometer, guarantees the relative alignment between these tracking stations, while the IFT is mechanically attached to the detector frame with a separate support structure. For smooth operations, the front-end electronics are kept at a stable temperature using a water chiller placed in T112 close to the detector.

Four scintillator stations provide trigger signals. The first of the stations is located in front of the FASER $\nu$  emulsion detector. The second is located in front of the first magnet and is composed of four layers with an absorber block of lead between the first two and the last two. Each layer has a detection efficiency above 99.9% for minimum ionizing particles, resulting in a very high veto efficiency for any muon-induced background. These first two stations are referred to as the 'veto stations'. The third station, or 'timing station', is located on the other end of the first magnet and is used to detect the presence of charged particles in the detector. It also provides a measurement of the arrival time of any charged signal with respect to the pp interaction at the ATLAS IP to a precision of less than 1 ns. The fourth scintillator station, or 'preshower station', is located in front of the calorimeter. Two scintillators are interleaved by graphite blocks to minimize back-scatter of low energy particles from the calorimeter and 3 mm tungsten layers to create a simple pre-shower detector that can help identify a physics signal of energetic photons. The veto and pre-shower stations use 2 cm thick, 30 cm×30 cm plastic scintillators, while the timing station employs two 1-cm thick, 20 cm×40 cm blocks arranged to form a 40 cm×40 cm single layer. All scintillators are connected to photomultiplier tubes (PMTs) and are read out via a commercial CAEN digitizer board.

Triggering capability is also provided by the calorimeter, which is otherwise used to identify electrons and photons and to measure their energies. Four spare LHCb outer electromagnetic calorimeter [9] modules are used. They provide energy resolution of about 1% for 100 GeV to TeV energy deposits. They have a total depth of 25 radiation lengths, but with no longitudinal shower information. They are connected to PMTs, which are read out via the same digitizer board used for the scintillators.

A LED-based system is used for calibrating and monitoring the stability of the response of the calorimeter modules and scintillators. It provides short light pulses of the order of 10 ns with variable amplitude sent via optical fibers to the calorimeter modules or scintillators. The calibration is performed by producing signals and measuring the gain as a function of the PMT bias voltage.

The tracker readout boards and the CAEN digitizer board are described in section 2, together with other general aspects of the FASER's TDAQ system. The boards are described in more detail and together with the rest of the TDAQ hardware components in section 3. The power supplies, chiller, temperatures (both of detector components and the environment) and humidity are controlled and/or monitored using a dedicated detector control system (DCS). The TDAQ software components (including for the monitoring and DCS) are described in the subsequent sections 4 and 5.

The FASER detector is being tested and commissioned in three phases: (a) individual detector

Figure 2. A CAD drawing of the FASER detector.

pieces and electronics cards were tested in dedicated labs at the CERN Meyrin site or the University of Geneva; (b) large detector pieces assembled in groups, including a complete TDAQ chain, were tested in a dedicated surface area at the CERN Prevessin site; (c) the full detector, except for the components corresponding to FASER $\nu$ , was assembled in the TI12 tunnel by March 2021 and full-system tests have been taking place since. All testing steps have used either generator pulses or cosmic muons. The FASER $\nu$  installation and commissioning are envisaged for autumn 2021. The aim is to have the full detector ready in early 2022 for commissioning with beams and subsequent data taking. This paper includes commissioning results of the TDAQ system in section 6, focusing the discussion to TDAQ aspects only. Sections 6.1–6.3 describe the individual component testing and commissioning, section 6.4 describes the DAQ software and server performance tests and section 6.5 presents full-system commissioning results. The FASER TDAQ system described in this paper is sized to that required for the full detector, including the tracker and scintillator stations corresponding to the FASER $\nu$  part of the experiment.

## 2 TDAQ system overview

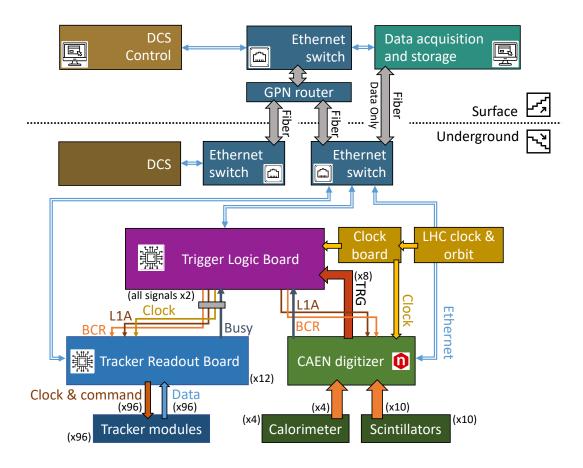

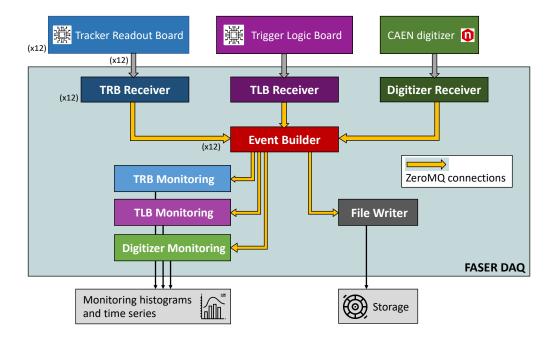

The FASER TDAQ system is designed to maximize stability and robustness during data taking, to ensure that the FASER experiment will record with high efficiency data that may contain rare new physics processes. To achieve this, the FASER TDAQ system employs a simple architecture, shown in figure 3, that minimizes the number of different hardware components, as well as the cables and equipment in the experimental area, which will be inaccessible during data taking. The FASER experiment is planned to be operated remotely only, without shifters populating a control room: the TDAQ system relies on sufficient monitoring to guarantee its robust functioning.

The experiment will be triggering on any high-energy particle traversing its detector volume. It is expected from simulations and in-situ measurements [2] that at an instantaneous luminosity of  $2 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> about 500–1000 Hz of particles, dominated by muons originating from the ATLAS IP, will leave signals in the FASER scintillators, while about 5 Hz of energetic signatures

**Figure 3**. A simple schema of the FASER TDAQ architecture. The numbers in parentheses indicate the number of channels or lines. The blue double-line arrows indicate the connections via Ethernet. The grey thick arrow indicates fibers from the TI12 tunnel to the surface. The digitizer, clock board and TLB are housed in a VME crate. The TRBs are located in two dedicated mini-crates just above the tracker structure, one of the two housing the IFT TRBs.

will be deposited at the FASER calorimeter. The digitizer, connected to the scintillators and calorimeter channels, generates trigger signals when the detector signals exceed a preset threshold; the scintillator trigger threshold will be below that of a single minimum ionizing particle, while the calorimeter threshold will be set to trigger on electromagnetic showers depositing more than about 20 GeV of energy. A separate trigger signal arrives from the LED calibration system. The trigger signals are received by the Trigger Logic Board (TLB), the central triggering board of the FASER TDAQ system, which subsequently provides a global trigger accept signal (L1A). The L1A signal is transferred to the detector readout boards (the tracker readout board, TRBs, for the tracker, as well as the digitizer for the scintillators and the calorimeter) for reading out their data. The readout boards receive two additional signals: a clock signal, synchronous to the LHC 40.08 MHz clock, coming from a dedicated LHC board and stabilised in a clock-cleaner board, as well as a bunch counter reset (BCR) signal, generated by the TLB on every LHC orbit signal. The TLB also

generates the bunch counter ID (BCID), indicating the number of clock cycles that have passed between the last BCR and the trigger signal.

The data of the various detector components is read out upon a L1A. Data fragments are transmitted over gigabit Ethernet from the TLB, the TRBs and the digitizer to the Event Building processes running on a conventional server on the surface. Time-stamp and run number is added and the full event is recorded to disk. Additional data quality monitoring is implemented in other processes running on the same server. The data size is about 25 kBytes per event, dominated by the PMT readout.

All software components of the TDAQ system are implemented on top of an open-source lightweight C++ software framework, DAQling [10], developed at CERN to be used as the core for DAQ systems of small and medium-sized experiments. DAQling offers configuration management, control of distributed applications, monitoring and messaging functionality, as well as a set of generic utilities. It has been adapted, with the support of its developers, to the needs of the FASER DAQ system.

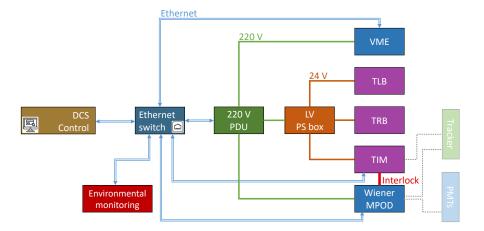

The FASER detector is controlled and monitored via the DCS, connected to two dedicated servers located on the surface, running the standard LHC Supervisory Control and Data Acquisition (SCADA) system, WinCC OA [11]. All DCS components in the experimental cavern are connected to a dedicated Ethernet switch, from where data (commands) are transferred to (from) the servers on the surface. Standard industry protocols (OPC-UA / MODBUS-TCP) are used to handle the communication between the different devices controlled and monitored by the DCS and the software back-end. The DCS makes use of commodity devices where possible, such as high and low-voltage power supplies. An electronics board (the TIM board) was developed for FASER and is used for monitoring environmental parameters of the tracker and as a hardware-level interlock to ensure the safety of the tracker.

## 3 TDAQ hardware components

This section describes the hardware components of the FASER TDAQ system. It starts with the trigger components, specifically those that feed signals into the TLB: the clock board (section 3.1) and the digitizer (section 3.2). It continues with a description of the custom board (section 3.3) used for the implementation of both the TLB and the TRBs. The TLB, representing the main trigger board of the experiment, is discussed in detail (section 3.4). A description of the TRB follows (3.5). The section closes with presentations of the crates where these boards are housed (3.6), as well as the DAQ components (3.7).

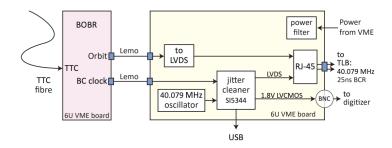

## 3.1 LHC signals and the FASER clock

The LHC clock (40.08 MHz) and orbit signal (11.245 kHz) are part of the beam synchronous timing (BST) system, transmitted to beam instrumentation equipment around the LHC over optical fibers using the TTC system [12]. For FASER, this signal is received over a single optical fiber by a legacy VME system, the BST receiver interface for beam observation system (BOBR) [13], produced by the LHC beam instrumentation group. This board extracts the LHC clock and orbit signals from the optical signals and converts them to electrical signals output on two front panel LEMO connectors. The LHC clock provided by the BOBR has a non-negligible jitter mainly due to noise in its power

Figure 4. Block Diagram of the FASER clock board.

module, changes during the energy ramp of the LHC, and is not guaranteed to be continuous when there is no beam in the LHC.

The electronic boards of the TDAQ system require a high-quality, uninterrupted reference clock that has a constant phase with respect to the LHC clock across power-cycles. The reference clock is provided to FASER by the FASER clock board (FClock), which cleans the jitter of the BOBR to less than 4 ps, measured with a Time-Interval-Error method.

The FClock is composed of an off-the-shelf clock-cleaner board (Si5342-D-EVB) mounted as a mezzanine on a purpose-specific VME adapter board. The FClock is powered through the VME interface, and the cleaned clock is sent as an LVDS signal via a RJ-45 connector to the TLB. The orbit signal, a 25 ns pulse centered on the rising edge of the clock, is converted to LVDS and sent on the same RJ-45 connector. A single-ended 1.8 V LVCMOS copy of the clock is also provided on a BNC connector directly to the digitizer. A block diagram of the FClock board is shown in figure 4.

The zero-delay feature of the jitter cleaner guarantees that the output FASER clock is aligned to the LHC clock with its phase unchanged across resets and power cycles. During the LHC cycle the frequency changes up to 550 Hz and the clock card allows to keep the FASER systems synchronised with the LHC clock.

### 3.2 PMT digitizer board

The readout electronics of the calorimeter and scintillator detectors need to sample the signals from the calorimeter and scintillator PMTs, provide trigger input signals to the TLB and buffer the calorimeter and scintillator data, which are read out upon a trigger L1A. This functionality is accomplished by using a VME-based system consisting of a single 16-channel, 14-bit CAEN VX1730 digitizer board [14] that is controlled and read out via Ethernet using the Struck Innovative Systems SIS3153 VME interface board [15]. The dynamic range of a digitizer channel is 2 V with a programmable offset of up to ±1 V that can be set independently on each channel. The signals on each channel are continuously digitized at 500 MHz and stored in a circular buffer to be read out on receiving a trigger signal. The on-board trigger logic runs at 125 MHz and for each channel a user-defined, fixed, absolute threshold can be set to generate an over/under-threshold signal. These are combined in pairs into eight trigger signals using a logical AND or OR, depending on the need. The eight trigger signals can either be used to trigger the readout internally for standalone testing or transmitted to the TLB as LVDS signals for logical combinations. In the latter case, the TLB L1A trigger decision is transmitted over a TTL LEMO signal from the TLB to the digitizer.

Upon receiving a L1A trigger signal, the board transfers the recorded samples into a FIFO readout buffer. The recorded data contain the data from all of the enabled channels as well as a 4-word data header. The data header contains the event counter and the time since the last BCR received from the TLB, both of which are used to identify the event. The time is measured in units of 16 ns which is later converted into the BCID in software. The full waveform for each channel is read out for a user-defined period, which in FASER is foreseen to be about  $1.2~\mu s$  at the beginning. This allows for a detailed offline analysis of the waveform, in particular in the case of any anomalous signal, at the cost of a rather large data size. This can later be reduced by a factor three (limited by the trigger latency) if no anomalous behavior is observed in early data. More advanced firmware with zero-suppression or digital pulse-processing are available from CAEN, which could reduce the data size further. These are currently not foreseen to be used. The readout FIFO is large (up to 1024 events), but can get full in case the readout of the board is unable to keep up. To avoid overflows, the board will raise a 'buffer-full' signal over the LVDS connection to the TLB once the buffer occupancy reaches a pre-defined threshold, which will halt any further triggers until occupancy drops below threshold.

The VX1730 board digitizes the signals at a frequency of 500 MHz. Its internal logic runs at 125 MHz while the readout is happening at 62.5 MHz. These frequencies cannot be synchronised to the LHC clock of 40.08 MHz. This leads to an intrinsic jitter for the trigger signals of 8 ns. To allow for precise measurements of the arrival time of each signal with respect to the collisions in the LHC, a copy of the LHC clock supplied from the FClock card is sampled on one digitizer channel. Offline data analysis uses a Fast-Fourier Transformation of this digitized clock to measure the phase of each event very precisely.

The configuration of the digitizer and the readout of the data FIFO buffer is performed using the Ethernet interface of the SIS3153 VME board. It communicates with the digitizer board using the VME backplane and translates the VME commands and data to simple UDP Ethernet packets, thus avoiding the need for a dedicated single-board computer in the VME crate.

#### 3.3 General Purpose I/O module

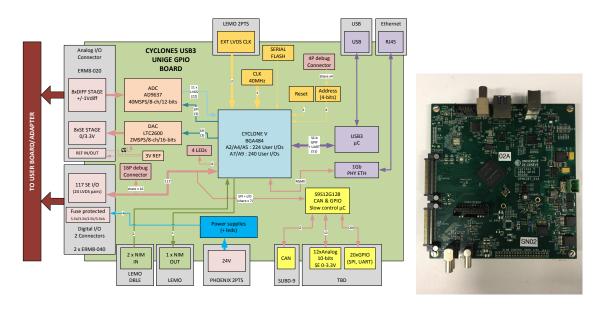

The TLB and TRB boards are both based on the 'Unige GPIO', a general purpose board developed by the University of Geneva for slow control and readout of particle physics ASICs, detectors tests, and qualification. For each application, such as for the TLB and TRB in the FASER experiment, a dedicated interface board needs to be developed to interface to the hardware. This interface board provides a connection for the analogue and/or digital inputs/outputs. The architecture of the 'Unige GPIO' board and a picture of the assembled board are shown in figure 5.

The core of the board is composed of a CYCLONE V A7 FPGA with 56.5K adaptive logic modules, ALMs, with 8 input look-up tables, LUTs, and 4 registers per ALM, 6.86 Mbits and 836 kbits of RAM per input type, respectively, 156 double 18x18 digital signal processor, DSP, blocks and 7 phase-locked loops, PLLs. The FPGA is driven either by a 40 MHz local clock or by an external clock via LVDS input through a dedicated 2 pin LEMO connector. For the board to interface with the experiment, two connectors dispatch 117 single-ended inputs/outputs, which can be configured through the FPGA firmware. More signals are available in the board but not used in FASER, neither in the TLB nor in the TRB.

Figure 5. The architecture of the "Unige GPIO" board and a picture of the assembled board.

Two interfaces can be used for readout and slow control. The first one is USB3, where the USB protocol is fully handled by an on-board FX3 Cypress micro-controller providing a 32-bit parallel interface clocked at 100 MHz. The FPGA has a maximum potential USB data throughput of 3.2 Gbit/s, but is ultimately limited to 1.8 to 2.5 Gbit/s depending on the host PC performance when connected with the board. The second interface is a 1 Gbit/s Ethernet with an on-board hardware chip driving the PHY layer, an Intel IP implemented in the FPGA for the MAC layer, and a 50 MHz Intel NIOS2 soft microcontroller running the ARP, IP, ICMP and UDP protocols used by the readout and the slow-control. On top of the two communication interfaces, a full and versatile FPGA library is available for the readout and the slow control of any small physics experiment or test bench. The firmware user interface is the same for both USB and Ethernet allowing the possibility to switch easily from one to another with just a synthesis of the firmware design. The communication is based on 32-bit words that encode a command word identifier, a board identification number of the board that is communicated with, the command type, and up to 16-bits of payload. The board always answers with similarly structured 32-bit words, acknowledging all known commands or returning an error in case any part of the command cannot be interpreted or the data the command requests contains an error. The board uses two independent data streams. The first is for bi-directional serial communication used to send commands and send or read back configuration data. The second is a uni-directional stream from the board to the host-PC transferring the event data to be recorded.

One single 24 V power supply input is required to power the board and 5.0 V, 3.3 V and 2.5 V are accessible through the user connectors for the interface board.

## 3.4 Trigger logic board

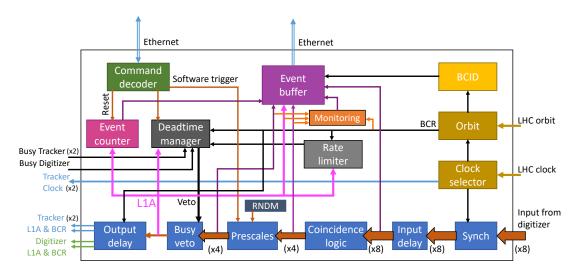

The TLB is the central trigger logic processor and distributor of a common (LHC or internal) 40.08 MHz clock and bunch-crossing reset signal. It receives and combines up to 8 trigger input signals from the digitizer and transmits the final trigger decision to all readout components.

In addition it manages the output rates via prescaling and veto functionality. The functionality implemented in the TLB is schematically shown in figure 6.

Figure 6. Schematic diagram of the functionality implemented in the Trigger Logic Board.

The TLB functionality is implemented in the firmware of a GPIO board described in section 3.3. It receives the LHC clock signal and BCR LVDS signal via a RJ45 connection. The BCR signal is distributed to the digitizer as a transistor-transistor logic, TLL, signal over a LEMO connection, while both the clock and BCR signal are transmitted as LVDS signals over two 15 m CAT7 cables to the crates that house the tracker readout boards. The TLB receives the trigger signals from the digitizer via a short, flat LVDS cable, and the trigger signal from the LED calibration system via a separate TTL signal on a LEMO input directly. Finally, the board receives and replies to slow control commands and transmits its data via Ethernet<sup>1</sup>. Both the digitizer and tracker can assert a busy signal.

The TLB synchronises the digitizer trigger signals to form 8 trigger lines in total. The 8 trigger lines (8 bits) are combined into 4 physics trigger items (4 bits) based on a LUT with a predefined coincidence logic loaded at configuration time. Two additional trigger bits are defined: an internally generated pseudo-random or fixed rate trigger, and another for the LED calibration signal but which can also be activated by a software command. Each item can be 'prescaled' by a factor *n*, meaning that only every *n*th signal is sent further. Finally, a logical OR between all trigger items is computed and defines the final trigger decision - or L1A - which is then transmitted to all readout components unless vetoed; several sources, further described below, can create a non-maskable veto. Upon an L1A, the TLB will send out a data packet containing: the event ID, BCID, orbit ID, trigger items before and after prescale, and the bits of the 8 trigger lines for the triggered and the following bunch-crossing. In addition, the TLB regularly publishes monitoring data packets containing trigger item counters before and after prescale (TBP and TAP) and after

<sup>&</sup>lt;sup>1</sup>While Ethernet is used in the final system, the board fully supports USB3 communication as well, as described in section 3.3.

veto (TAV), veto counters, and the logical OR of all trigger items before and after veto to enable the computation of the total fraction of vetoed events.

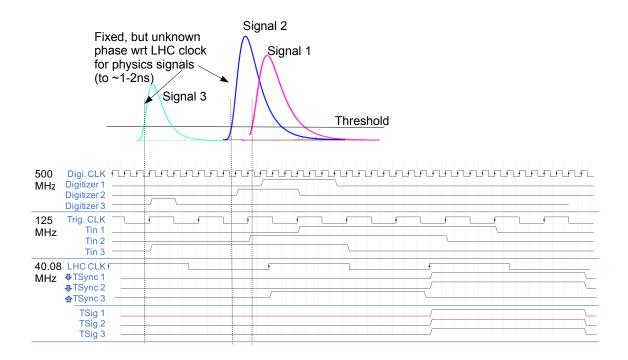

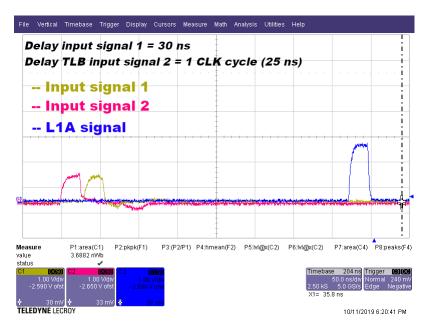

**Trigger timing** It is important that the input signals from the digitizer can be correctly synchronised to the LHC clock. The trigger input signals from an event may not arrive simultaneously because of differences in the time-of-flight of particles traversing the length of the detector and the different PMT response times. Figure 7 shows a timing plot of 3 incoming signals and their subsequent synchronisation. The input (Tin) signals appear 32 ns wide, thus covering over a full LHC clock cycle. The 8 ns jitter is avoided by having the option of sampling each input signal on the rising or falling LHC clock edge, as it is guaranteed that at least one edge is in phase with a stable section of the input signal; this option will be tuned in data taking with beam. The difference in arrival times between input signals may be large enough that the output (TSync) signals synchronised to the LHC clock do not land in the same clock cycle. An input delay can therefore be applied to each channel to synchronise the final trigger line output (TSig) signals. Once an L1A is generated, the L1A signal sent to the digitizer and the tracker can be separately delayed with a granularity of one bunch-crossing. This is to ensure that the readout window on each readout board is aligned with the complete data corresponding to the event that triggered the L1A. The final adjustable delay is the orbit delay. This delays the BCR transmission so that it can be tuned to occur during the LHC abort gap when no proton collisions occur.

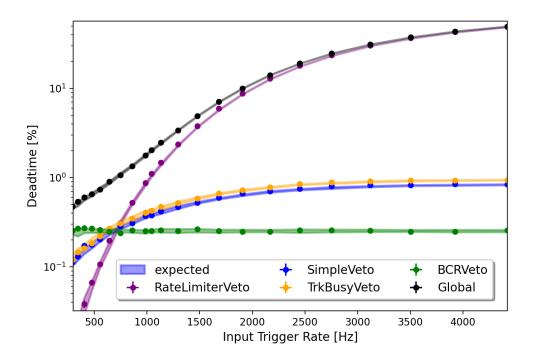

**Trigger veto** Different sources for trigger vetoes ultimately serve to limit the minimum spacing between consecutive triggers when subdetectors are busy reading out event data, or to limit the overall trigger rate, leading to system *deadtime*. The possible sources of trigger vetoes are listed below. The TLB will veto events while receiving a busy signal from a subsystem.

- *Tracker busy veto*: The TRBs can only receive and readout one L1A at a time. Each tracker readout board will assert a busy signal while its readout FIFOs are being read (see section 3.5). The duration of the busy signal is thus dependent on the hit multiplicity in an event.

- *Digitizer busy veto*: The digitizer will assert a busy signal if its internal readout buffer occupancy reaches a certain threshold. The busy signal is held until its buffer occupancy drops below threshold.

- Simple deadtime veto: All trigger decisions within a chosen fixed number of bunch-crossings after a L1A are vetoed. The simple deadtime is at minimum equal to the L1A delay to the tracker readout to avoid triggers before the tracker busy signal sets in. The combined simple plus tracker busy deadtime is expected to be on average 300 BCs in duration.

- *BCR veto*: Since SCT modules require 3 clock cycles to process a L1A and 7 clock cycles to process a BCR, an overlap of these is prevented by vetoing triggers for 9 clock cycles starting from 2 clock cycles before a BCR. This implies a fixed deadtime of 0.25% for random or cosmic-ray events, but will be zero for collision events as the BCR will be tuned to occur during the LHC abort gap.

- *Rate limiter*: In order to avoid uncontrolled high rates from an input channel suddenly becoming noisy, a rate limiter limits the L1A rate to 3 L1As per 15 orbits (or 2.2 kHz).

**Figure 7**. Example of input signals and how signals are synchronized. Only 3 of the 8 input channels are shown. The digizer runs at a 500 MHz clock. The digitized input signals (Digitizer 1, 2 and 3) are sampled at 125 MHz (Tin 1, 2 and 3) and with a 8 ns jitter to produce the trigger signals. These signals are synchronised with the LHC clock using either its rising or its falling edge; this option is configurable and is tuned in dedicated runs before data taking. In this example, the first two input channels are sampled for synchronization on the falling LHC clock (LHC CLK) edge, while the third channel is sampled on the rising edge as indicated on left in the figure. The synchronised signals (TSync 1, 2 and 3) can then be delayed so that the final trigger signals (TSig 1, 2 and 3) are all synchronised with each other; this option is also configurable and tuned in dedicated runs prior to data taking. In this example, TSig 3 is delayed by one clock cycle.

The dominant sources of deadtime are expected to be the combination of simple and tracker busy deadtime of 0.4% (0.7%) at 500 (1000) Hz, and the rate limiter, which would start dominating at 1 kHz at 1% deadtime. The BCR veto is expected to induce no deadtime for physics events as the BCR will be tuned to occur during the  $O(\mu s)$  LHC abort gap, while digitizer deadtime is expected to not be a limitation during stable running. A final measurement of the deadtime with respect to the expectation for a range in trigger input rates is presented in section 6.5 (see figure 28).

**TLB internal trigger generation** The TLB can generate an internal trigger in 3 different modes: (i) in fixed rate mode (ii) in pseudo-random rate mode and (iii) a single trigger via a command (software trigger). In fixed rate mode, a flat rate of a maximum of 100 kHz can be set. In pseudo-random rate mode, a total of 8 settings allow for an unprescaled average range in rate of roughly 15 Hz to 1.2 kHz. The pseudo-random trigger relies on a 22-bit seed, which is updated at every

clock cycle via a linear-feedback shift register. The seed is then aligned with a 22-bit mask that has the 13+N leading bits turned on, where N is the random trigger setting of 0–7. A trigger is fired if the seed and the AND of the mask align to zero. For instance, a random trigger setting of 0 (7), means a trigger will fire when the first 13 (20) bits of the seed are zero. A higher random rate setting therefore leads to a less frequently fired trigger as a greater number of zeros are required to align. The seed is incremented by one on every L1A to avoid repeating patterns in the linear-feedback shift register.

#### 3.5 Tracker read-out

The tracker readout board, or TRB, handles all communication with the attached tracker modules. It is responsible for configuration, propagation of trigger signals and readout of the data. It is based on the GPIO board described in section 3.3. The TRB itself receives trigger (L1A) and timing (clock and BCR) signals from the TLB, described in 3.4. Up to 8 SCT modules can be connected to one TRB via an adaptor board. The TRBs are located in a mini-crate, described in section 3.6. The adaptor board interfaces with the backplane of the mini-crate, which provides the timing and trigger signals. The board does not decode the module data except for finding the end of data marker. Its functionality can be divided into three parts: Communication with the host PC, configuration of the tracker modules and data taking.

In order to configure the tracker modules the TRB must send configuration commands and data encoded in a bit-stream to the tracker modules. To this end, the TRB firmware implements functionality to prepare the bit-stream from commands and data received from the host PC. An arbitrary combination of modules can be addressed simultaneously. In data taking mode the TRB transmits the trigger and timing signals to the enabled modules. When in this mode, two running modes are distinguished: calibration and physics data taking.

During physics data taking the L1A, BCR and clock signal are received from the TLB, processed in the TRB and sent to the modules with a fixed latency. Since the tracker readout has an internal pipeline of 132 bunch-crossings, the TLB L1A signal must arrive at the SCT modules 132 BCs after the charged particle traversed the tracker plane. There are inherent delays in signal propagation from the occurance of an event to the arrival of the L1A at the TRB, but to cover the full 132 BCs latency, both the TRB and TLB have a settable coarse time delay in BC increments for the L1A/BCR signals. A signal delay of up to 127 BCs on the TLB and a further adjustment of 0 to 7 BCs on a TRB are possible, where the latter allows to adjust for different particle times-of-flight at each tracker station location in the final detector setup. The tracker readout timing can be further adjusted with a resolution of 390 ps via an adjustment of the input clock phase on the TRB, so that hits are sampled on the pulse peak. The data received from each module upon an L1A are stored in the TRB in so-called Level 1 FIFOs - 16 FIFOs in total, as there is one per each side of a module. When any of these FIFOs are filled with data, the TRB asserts a hardware busy signal that is sent over the backplane to the TLB. Each event is associated with a BCID, calculated within the TRB using an internal counter and the BCR signal, and which is used later in the processing for data consistency checks, as described in section 4.

In calibration mode the L1A and clock signal are generated in the TRB, the former upon a command received from the host PC. It is possible to send one L1A at a time. However, every command sent to the TRB by software requires sending at least one 32-bit word and waiting for a

reply from the TRB. This implies that the rate of sending individual trigger commands is given by the latency of the data transfer of single words. This is in the order of milliseconds for UDP and tens to hundreds of micro seconds for USB. Thus the trigger rate is limited to a few hundred Hz when using the default UDP interface, which is unacceptably slow for calibration scans that require millions of triggers. To overcome this limitation, a firmware feature allows sending a burst of up to 4095 triggers with an adjustable latency in between. This allows trigger rates that are only limited by the speed with which the data is shipped to the readout PC. To avoid loss of data the delay between consecutive triggers is adjusted dynamically depending on the remaining space in the receiving FIFO. Complete events are formed and stored in a Level 2 FIFO until pushed out. A complete event consists of a header, containing the event ID. The header is followed by one or several TRB data words, containing the BCID as well as any errors that might have occurred. Appended to this is the module raw data prefixed with the module ID. Every word holding part of the event data contains a frame ID as well as a consecutive data frame counter to allow for reconstruction of the full event information. Additionally a cyclic redundancy check (CRC) value is computed over the full event data and can be used to identify any transmission errors.

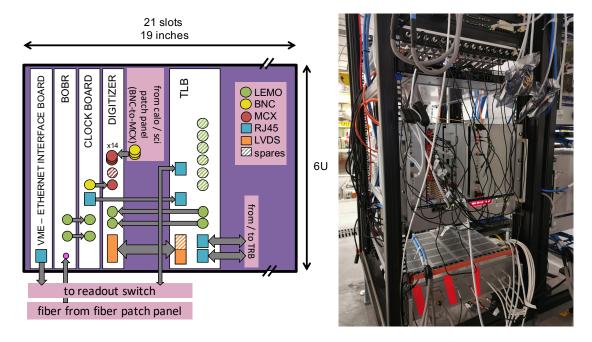

#### 3.6 Crates

The FASER trigger components are housed in two crates. The TRB modules use a dedicated minicrate that is located in a support structure just above the middle tracking station. The backplane is composed of 9 slots allowing the connection of 9 TRBs<sup>2</sup>. Individual LVDS pairs transfer CLK, L1A and BCR signals, and an open drain output transfers the BUSY signal from the TRBs. One temperature sensor and the 24 V power per TRB are also transferred through these slot connectors. Local DC/DC converters are also located on the backplane and allow the 3.3 V powering of 3 fanout chips used for the distribution of the individual TRB LVDS BCR, CLK and L1A from the single RJ45 connector connected to the TLB. The rest of the trigger boards are inserted in a standard VME crate<sup>3</sup>. A schema of the front panels of the boards and how they are connected are both shown in figure 8, alongside a picture of the crate, located in the rack in TI12.

### 3.7 Computing and networking components

The readout of the FASER front-end electronics as well as the detector control system is based on commercial Gigabit Ethernet using both copper and fiber-optic connections. As illustrated in figure 3, all Ethernet connections from the electronics cards and crates in the TI12 tunnel are aggregated in two Ethernet switches in TI12 for the DAQ and DCS signals, respectively. The DAQ switch is connected over more than 1.5 km long single-mode 10 Gbit/s optical fibers directly to a single DAQ server PC in a surface building at the LHC Point-1 area (SR1), while the DCS switch is connected to the DCS server PCs through the main SR1 gateway and a local switch over 1 Gbit/s optical fibers. The DAQ server is connected to the CERN general purpose network (GPN) through the same switch in SR1. Control of the DAQ and DCS systems as well as the transfer of data files to permanent storage in the CERN computing center are all done through this connection.

<sup>&</sup>lt;sup>2</sup>The 3 TRBs used for the IFT station will be housed in an identical mini crate situated on the detector close to the IFT.

<sup>&</sup>lt;sup>3</sup>The model of the VME crate is the following: http://www.wiener-d.com/sc/powered-crates/vme64-x/6u-vme64x-6021.html

**Figure 8**. The VME crate housing the BOBR, clock board, TLB and digitizer: a schematic view of the connections (left) and a picture of the rack where the crate is located in TI12 (right).

The network switches used by FASER are all 24-port Ruckus ICX-7450 switches with one or two additional fiber optics up-link modules as well as redundant power-supplies. The switches are configured and monitored by CERN central IT support.

Tests have shown that a single DAQ server is sufficient to run the full FASER DAQ readout software as described in section 4 provided it has sufficient computing capacity. The final DAQ server is a 1U, SuperMicro server with a 24-core, 48 thread AMD EPYC 7402P CPU, 64 GByte ECC DDR4 memory. Two 480 GB SSDs in RAID 1 are used to host the operating system, DAQ software and local log files, while two 8TB 7200 RPM hard-drives in RAID 1 are used as local disk storage, providing sufficient storage for more than one week of continuous data taking at the nominal trigger rate and data size. The server has redundant power supplies, connected to a central diesel-backed UPS for maximum reliability<sup>4</sup>. An identical, spare server is maintained in the same rack in SR1 as a backup in case of a major failure of the central DAQ server.

The DCS server resource requirements are more modest and two 1U, SuperMicro servers with a 4-core, 8 thread Intel Xeon E2244G CPUs and 16 GByte ECC DDR4 memory are used. Two 480 GB SSDs in RAID 1 are used to host the operating system, DCS software and local log files. As with the DAQ server, the DCS servers have redundant power supplies and a spare server is maintained as backup. All DAQ and DCS servers are running the CERN standard CentOS7 Linux distribution.

For the tests described in this document, the direct connection for the data path from TI12 to the SR1 server was not yet ready. Instead, the connection is done through the main SR1 gateway and the second switch in SR1 over 1 Gbit/s optical fibers. Additional tests are done with a server located in TI12, connected directly to the DAQ switch in TI12.

<sup>&</sup>lt;sup>4</sup>Data taking would be stopped in case of a power failure in TI12 as most of the electronics are not on UPS power.

The final DAQ server was only available for some of the tests described in this document, reported in sections 6.4 and 6.5. For earlier commissioning tests, an older server PC, borrowed from the ATLAS experiment, is used. The server is a 2012 Dell PowerEdge R410 with two Intel Xeon E5645 processors, each with six cores (twelve threads) running at up to 2.4 GHz. The server is equipped with 24 GBytes of DDR3 memory and a single 500 GByte hard-drive for storage.

# 4 DAQ software

The software used for the FASER DAQ processes is presented in this section. The FASER DAQ software is implemented on top of an external framework; this implementation is described in section 4.1. The data format and size are outlined in section 4.2. The specific software used for reading out the digitizer and GPIOs (TLB and TRB) is described in sections 4.3 and 4.4. Controls and monitoring software are discussed in the following section, section 5.

#### 4.1 DAQ software framework

The FASER DAQ software [16] is built on top of the DAQling framework [17]. DAQling is an open-source lightweight C++ software framework that can be used as the core of data acquisition systems of small and medium-sized experiments. It provides a modular system in which custom applications can be plugged-in. It also provides the communication layer based on the widespread ZeroMQ messaging library [18], error logging using ERS [19], configuration management based on the JSON format, control of distributed applications and extendable operational monitoring with web-based visualization.

The ensemble of FASER DAQ processes and their communication channels are illustrated in figure 9. Each readout electronics board in FASER is read out, configured and controlled by its own software process, referred to as a receiver process, the details of which are described in the following sections. During data taking, the receivers will assemble the data for each triggered event into the data fragment described in section 4.2, and push these one-by-one to the event builder process. The event builder merges all data fragments for a given event and pushes the full event to the file writer process, which is responsible for recording the events to the local disk. The DAQ processes can run on separate host PCs with communication over TCP with ZeroMQ between them, but since the total CPU requirement is modest, most tests and the final DAQ foresees running all processes on a single host, primarily using ZeroMQ IPC as the communication layer.

The merging of event fragments in the event builder into full events is done based on the event identifier number assigned in each front-end board, where the boards count the number of triggers they receive and assign the number sequentially. In order to ensure that the fragments truly belong to the same collision, the BCID, stored in the header of the detector data fragments is retrieved and checked. If the event builder detects an event where the BCIDs for the different fragments do not match, it will flag the event and raise an alarm once a certain threshold of events is reached. The event builder will also flag events where one or more fragments are not received within a programmable time-out and route such events to a separate data stream. The same happens for events where a fragment has been flagged as corrupted by the front-end receiver. The monitoring fragments from the TLB receiver will be routed to a separate stream. The full events in each stream are immediately pushed to the file writer and separately to any subscribing monitoring process,

**Figure 9**. Overview of the FASER DAQ software processes.

as explained later in section 5.2. The file writer does not decode the received data, but instead just concatenates the events into separate buffers for each stream, writing the buffer to disk once a threshold, typically 1 MByte, is exceeded. Each data stream has its own file on disk, indexed by stream name, run number and a rolling index per run. The files are closed and a new one opened when the filesize exceeds 1 GByte in order to keep the individual data-file at an easily manageable size.

#### 4.2 Data format and event size

The FASER data format defines the format of the data out of the TLB, digitizer and tracker readout boards, the readout receiver applications, and the data out of the event builder. The event format provides information redundancy to allow self-consistency checks of the event to be made. The basic unit of the FASER data, after it has been processed by the readout receiver application, is the data fragment. All fragments have identical structure and the same format of header. The header information is small in size and the identification of the fragment origin is possible with the header information only. The data format (header and trailer) provides means of identifying errors related to hardware or data flow issues. A schematic view of the event format structure is shown in figure 10.

**Figure 10**. The FASER event format. Sub-detector fragments refer to the TLB, digitizer and tracker. The full event and readout-receiver (ROR) event headers are generic; the readout (RO) event header is sub-detector specific.

The full event header is assigned to the event by the event builder. It contains information that identifies the event; it is composed by 13 words of variable size, which sum up to 352 bits (11 4-byte words), dominated by the words corresponding to the data size, the event counter, an event identifier number and the time stamp. The readout-receiver event header is assigned by the DAQ receiver application. It contains similar information to the full event header, but relevant to the corresponding sub-detector. Each readout-receiver event header has a size of 288 bits (9 4-byte words). The readout event header is assigned by the detector readout board directly, before the data are sent out. The content is specific to the sub-detector electronics.

Table 1 displays the typical FASER data size per component. The total size is around 22 kBytes per event, dominated by the PMT readout (19 kBytes per event) due to the long readout window foreseen at least during early data taking.

**Table 1.** Individual data fragment sizes and total size in kBytes. The per TRB payload size stated is the estimated average in the TI12 system during commissioning. The digitizer payload size is for all 16 channel readouts enabled and maximum readout window (1.2  $\mu$ s as used during initial data taking).

| Component        | Size [kBytes] |  |  |

|------------------|---------------|--|--|

| TLB              | 0.024         |  |  |

| TRB              | 9 x 0.2 (1.8) |  |  |

| Digitizer        | 19.2          |  |  |

| Total payload    | 21.0          |  |  |

| Total event size | 21.5          |  |  |

### 4.3 Read-out software: digitizer

The digitizer system is controlled and read out in software by a custom C++ library built on top of the C++ driver library supplied with the SIS3153 card for communication over Ethernet. It provides an API for configuring all aspects of the SIS3153 and VX1730 boards based on a JSON configuration file. All configuration parameters are read back and checked after being sent to the boards. The data readout is accomplished by polling the FIFO buffer size until non-zero and then requesting the SIS3153 board to read and send the data of one event at a time. Multiple UDP packets are needed to transmit a single event and the SIS3153 board is configured to transmit all of the UDP packets corresponding to one event without waiting for an acknowledge signal from the server. Each UDP packet is numbered, so that the software can handle out-of-order packets as well as detect if a packet is lost. In case of a packet being lost, it is not possible to re-transmit the lost

one as the data are not buffered after transmission, and the particular data fragment will be marked as corrupted. Reading just one event at a time ensures that the effect of such data loss is minimized.

The library can be used both in a standalone application, allowing commissioning of just the digitizer board, and by the digitizer receiver module inside the full FASER DAQ system. In the latter case, the receiver module implements the state transitions needed by the DAQ, receives the configuration from the central run control system (see, next section) instead of a local JSON file and the received data fragments are transmitted to the event builder after adding the common DAQ fragment header.

#### 4.4 Read-out software: GPIOdrivers

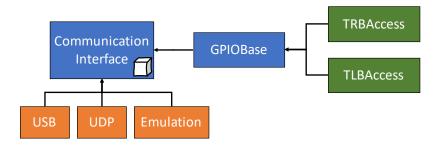

The communication with the GPIO board, which is used as the basis for the TRB and TLB, is encapsulated in a C++ library called *GPIOdrivers* [20]. The library provides a high level API tailored to the needs of the TRB and TLB. The serial communication with the hardware via USB and Ethernet links using the GPIO specific protocol is completely encapsulated in this library. The architecture and main features of the API will be discussed in the following.

The class structure of the GPIOdrivers library is shown in figure 11. It consists of three main parts: the encapsulation of the transport layer specific needs, the low level access to the GPIO board, and the TRB / TLB specific implementation of high level features.

- 1. On the transport layer the communication with the GPIO board is performed by sending and receiving 32-bit words. Two communication channels are needed by the GPIO board: one bi-directional for configuring the board and querying status information and an additional unidirectional channel from the GPIO board to the host PC, used to receive readout data. The corresponding functionality is defined in the abstract class *CommunicationInterface* and implemented in three derived classes, each of them handling data transfer via the UDP network protocol, via USB or emulating the hardware.

- 2. The low level functionality of the GPIO board is accessible via the GPIOBase class which holds an instance of the CommunicationInterface. It encapsulates the communication protocol of the GPIO board, allowing to send individual commands with arbitrary payload to the GPIO board. The integrity of the transmitted data is confirmed by a checksum shipped with every command. The hardware addresses of all available commands as well as all possible error codes are defined in this class for user friendly access. Retrieval of the status and firmware version of the GPIO board is also implemented here.

- 3. The high level interaction with the TRB / TLB firmware is implemented in two classes derived from the *GPIOBase* class: *TRBAccess* and *TLBAccess*. Both classes implement the access to the firmware functionality and registers provided by the respective firmware implementations. Helper functions to configure the GPIOBoards as well as default configurations for the TRB / TLB are provided. In addition, the TRBAccess class also encapsulates the communication with the attached tracker modules. The GPIO driver software waits to receive readout data from the GPIO boards, which is then buffered, analysed for errors, and packed into FASER data fragments, if needed in standalone running. To maximize the data throughput the receiving and processing of readout data is performed in separate threads.

**Figure 11**. Overview of the GPIODrivers class architecture. The CommunicationInterface class is abstract. The classes that handle data transfer (UPD, USB and the emulation of those) derive from it. An instance of that class is also included in the GPIOBase class, which provides the low-level functionality, from where the two implementations (TLB and TRB) derive.

The GPIODrivers package includes standalone programs to test the communication with the TRB / TLB boards, configure them and read out data. These programs can be use as templates for future projects. Beside standalone running of individual boards, the library is further employed in the tracker and trigger receiver modules within the context of the FASER DAQ framework (see section 4.1). For the latter, as in the case of the digitizer, configuration settings are loaded from the central run control system and receivers issue control commands to the boards depending on the run control state (see section 5.1). The received data fragments are transmitted to the event builder after adding the common DAQ fragment header.

# 5 Controls and monitoring software

Given the fact that the FASER experiment will be running on an operational model without shifters but with remote controls and monitoring of the detectors and TDAQ, special emphasis is given to the controls and monitoring infrastructure of the experiment. The run control and configuration software is summarised in section 5.1. The monitoring infrastructure put in place is outlined in section 5.2 and finally, the DCS software infrastructure, which uses that of the large LHC experiments as a guideline, is presented in section 5.3.

### 5.1 Run control and configuration

The low-level process control is implemented in DAQling on top of the 'supervisord' library [21]. Each process is started / stopped using supervisord and follows a common finite state machine (FSM) to control and synchronize the configuration and data taking steps. The control is steered by a Python library provided by DAQling, which communicates with the supervisord library and the individual processes using XML-RPC. This library is also responsible for transmitting the individual configuration for each module in the form of a JSON object, again sent using XML-RPC.

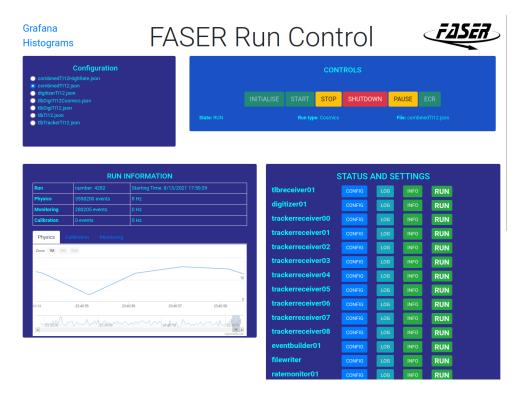

On top of the low-level control library, a FASER-specific Run Control web application (RCGui) has been built using the Python-based Flask web framework to allow easy control of the DAQ from remote machines as illustrated in figure 12. The web application allows the user to select between different pre-defined run configurations as well as editing all settings directly in the web browser. The application provides control to cycle through the FSM states and monitor the progression

of each process. It also provides easy access to the log file of each application as well as the monitoring data, as described in the next section. At the start of each run, the run control assigns a new sequential "Run number" to the data that will be taken and archives the full configuration used into an Oracle database along with a user supplied comment. Similarly when a data taking run is stopped, it allows for a user comment to be added to the run record in Oracle together with the total number of events recorded.

**Figure 12**. Example screen shot of the RCGui web application during cosmic ray data taking with the FASER detector.

### 5.2 Monitoring

Extensive monitoring has been put in place to monitor data flow and data variables at every step of the data acquisition. Two types of monitoring exist: (i) monitoring of a single variable, or metric, over time for monitoring of conditions; (ii) monitoring of histogrammed distributions of variables for data quality control.

Monitoring of metrics. Metrics are defined and regularly published in every DAQ process; for example, the total number of physics events that have been read out is a common metric for all DAQ processes. Metrics and handling of those are part of the DAQling infrastructure. Different metric types determine the final arithmetic applied upon publication, such as the computation of the average, the rate or current state of a variable over the publishing time interval. Metrics are published at regular intervals to InfluxDB [22] and redis [23], and viewed in Grafana [24] dashboards and the Run Control interface.

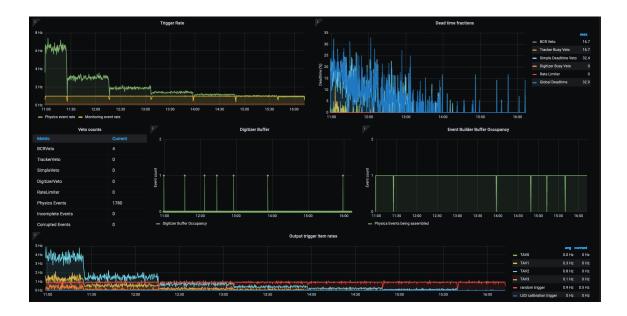

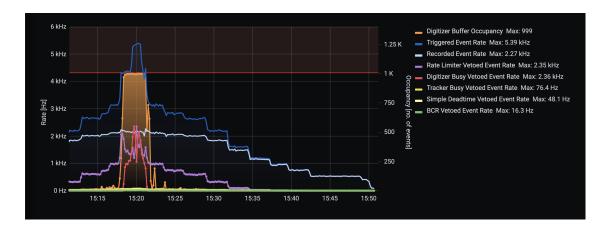

Examples of Grafana dashboards are shown in figures 13 and 14; they demonstrate, respectively, monitoring of the overall current status of the data acquisition system, and the time trends in rates and buffer occupancy.

**Figure 13**. Grafana dashboard of the DAQ status overview for an ongoing data taking run. Metrics of the trigger and data recording rate, DAQ module status and total error counts are displayed. In addition, current run details are shown.

**Figure 14**. Grafana dashboard of rate and buffer information during PMT high voltage scans: the total physics and monitoring event rate, deadtime fractions, buffer occupancies in the digitizer and software event builder, and rates of individual trigger items are monitored.

**Figure 15**. Histogram monitoring home page: the monitored histograms are displayed in a grid and they have their own options (ID, historic page icon, timestamp and custom tags). An example of a one-dimensional histogram is shown on the left and of a two-dimensional histogram is shown on the right.

**Monitoring of histograms.** Histograms are useful for monitoring extreme or rare outliers. Dedicated DAQ monitor modules receive copied event data from the event builder. The monitors unpack events to visualise event features in detail via histograms and metrics. Histograms are regularly published to the redis database, from which a separate histogram polling application extracts the histograms to display on a web interface.

The web interface is written in Javascript with the Vue [25] framework and communicates with a Flask [26] server written in Python. A histogram published in the database can then be retrieved by the Flask server and sent to the web application. From there, the Javascript library Plotly.js displays the different types of histograms in the browser. Histogram tagging and timestamps are used for easy navigation through the interface. Monitoring data arrives promptly to the histogramming tools and a histogram update frequency down to 5 s has been tested. The update frequency to be used for the data taking with beams will be fixed with operational experience. Example monitoring histograms are shown in figure 15.

#### **5.3 DCS**

The FASER DCS is designed to ensure the safety of the detector during the different operation modes, to monitor the operating parameters of the detector's power system and its environment, and to control and configure the detector's operational states. The software back-end of the DCS is implemented with the SIEMENS Simatic WinCC Open Architecture, which is a SCADA system used at CERN by the LHC experiments, as already introduced in section 2. The DCS components of the experiment and how they connect with each other are shown in figure 16.

The communications between the DCS back-end and the devices is routed through a commodity switch using standard 1 Gbit/s Ethernet, identical to the DAQ switches and network described in section 3.7. The Ethernet network of the devices is secured from the CERN general network.

**Figure 16**. The DCS components of the FASER experiment and the connections between them. The DCS connections to the detector are also shown.

The items controlled and monitored by the DCS can be grouped in the following categories:

- 1. Environmental parameters: The temperature and humidity of the tracker is monitored through a custom electronic board (TIM board). Data is transmitted to the DCS back-end via the industry standard Modbus protocol [27].

- 2. Tracker safety interlock: The TIM board also serves as a hardware-based safety interlock for the tracker. It is configured and monitored via Modbus by the DCS back-end.

- 3. HV and LV system: The main HV and LV system is based on the Wiener MPOD system [28] and is monitored and configured by the DCS via the OPC-UA.

- 4. Power Distribution Units: A commercially available Power Distribution Unit (NetIO Power-PDU 4C [29]) is controlled by the DCS via Modbus.

To ensure the safety of the detector, the DCS triggers alerts and automatic emergency procedures. The DCS also implements autonomous integrity checks and diagnostics and provides a user interface to inform FASER on-call experts on the state and status of the experiment.

Transitions between the different detector operational states are implemented as a FSM (see figure 17). Transitions are initiated either by a user input or by an autonomous protocol. The action of the transition is initiated by propagating a transition signal through a sub-system hierarchy which in turn triggers a series of autonomous protocols that configure the necessary parameters to achieve the transition between the different operational states.

The DCS also provides a user interface for configuring operational parameters of the power and interlock systems and an interface to a database to which operation-parameter configurations can be saved and extracted from. The DCS monitors approximately 600 parameters at a 1 Hz rate, collecting data at a rate of 1.3 kBytes/s.

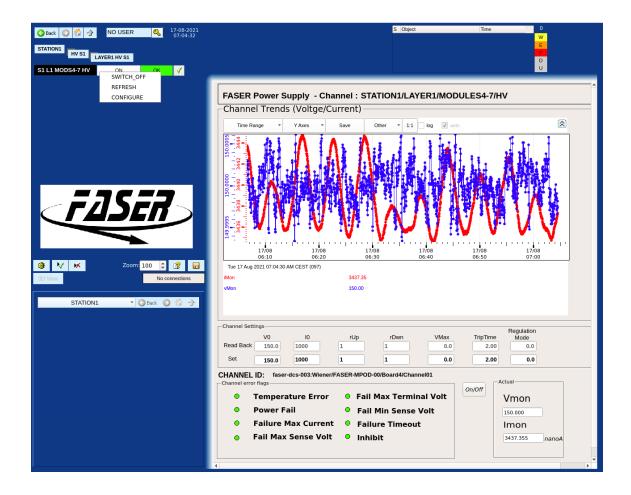

The DCS also records time-series of the detector parameters, as well as the operational state and the detector status. The time series are archived for later retrieval in an Oracle database, which ensures the quality of the data collected at a particular time. Figure 18 shows an example of DCS values retrieved and monitored in Grafana.

Figure 17. A DCS FSM panel via which the low and high voltage of a tracker station is controlled.

### 6 Commissioning and system performance

This section of the paper describes the TDAQ system commissioning in the three FASER commissioning phases introduced in section 1. The initial step of the system commissioning has been the qualification of the hardware and software components, which was achieved with basic testing and confirmation of the functionality. The subsequent step has been the assessment of the system performance, both of each component individually and of the full system combined. Results from both these steps are reported in the following sections, first for each component separately in sections 6.1–6.3, for the full DAQ system in section 6.4 and then for the full combined system with the complete detector connected in section 6.5. For all tests described in this section the system was sized up to what is required for the FASER experiment without yet accounting for FASER $\nu$ , i.e. for three tracking stations and three scintillator stations.

## 6.1 Digitizer standalone commissioning

The CAEN digitizer card and the Struck VME-to-Ethernet card were tested together using both signal generators and real PMT pulses with the digitizer self-triggering and the data read out over

**Figure 18**. Grafana dashboard of the DCS status overview during an ongoing combined system run. Metrics such as current tracker and PMT voltages, temperatures and power output are shown.

the Struck card either connecting directly to the Ethernet port on a Linux-based server or over a local network switch.

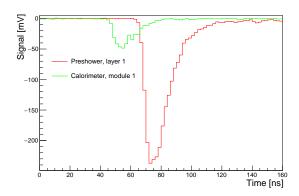

#### **6.1.1** Digitizer trigger timing

A critical aspect of the digitizer trigger functionality is the trigger latency and in particular the jitter in the output trigger signals as well as their synchronicity. This was tested with different types of signals, with the most accurate test being a square pulse sent to multiple inputs with small (1–4 ns) relative delays to ensure a fixed expected ordering of the trigger signals. The trigger output signals are routed back to other input channels on the digitizer and the trigger signal arrival times can be compared to the arrival time of the pulses. During this testing, one board was found to have an additional 8 ns jitter on some channels in an irreproducible fashion. Once discovered, the board was promptly exchanged by the manufacturer.

### 6.1.2 Readout performance

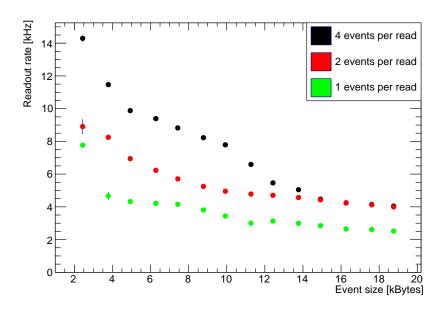

The maximum readout performance of different configurations for the readout are tested by filling the digitizer buffer with 1000 triggered events and measuring the time needed to read those out. The best performance is found when using the highest speed VME64x readout protocol (2eSST320) and the VME-to-Ethernet card configured to send up to its maximum 32 Ethernet packets (with up to 1440 bytes of VME data per packet) for each data request sent by the readout application. As UDP is used for the network data transfer, data loss will occur in case a packet is dropped on the network as the VME-to-Ethernet card does not have the capability to resend a lost packet when more than one packet is sent per readout request. The data requests are therefore always done for a single full event or a small multiple of events, so that only that or those events are affected by any data loss. The amount of data requested should also stay below the maximum possible data transfer

for a single data request  $(32 \times 1440 \text{ bytes} = 45 \text{ kBytes})$  in order to have the maximum resilience in handling packet drops.

A maximum readout rate at the nominal 19 kBytes fragment size of more than 2.5 kHz has been demonstrated when reading out a single complete event per request as shown in figure 19. This corresponds to a maximum bandwidth usage of almost 50 MBytes/s or about half the maximum network link speed. Higher readout rates are possible if the readout window and thus event size is reduced, but the effective bandwidth goes down due to the additional overhead of pulling individual events. The readout rate can be further improved by requesting multiple events per readout request as long as the total data size fits inside the maximum 45 kBytes per readout request. With that a maximum readout rate of almost 4 kHz can be achieved for the nominal digitizer fragment size. A further increase can be achieved by switching to using the larger Jumbo Ethernet packets (a data payload of up to 7168 bytes per packet instead of 1440 bytes) with almost 5 kHz reached in standalone testing when requesting four events per readout request.

In combined running, the full readout rate has not been achieved as the available bandwidth is reduced by the additional TRB and TLB readout data. Furthermore the current digitizer receiver application is single-threaded meaning that a single thread is both receiving the data, decoding it and preparing it for transmission to the event builder, adding latency between receiving one event and requesting the next one. Running with the digitizer in the production DAQ system, the maximum readout rate when requesting just one event per request is measured to be 2.2 kHz for the nominal event size. This increases to about 2.8 kHz when requesting two events per readout request. It was not possible to test with Jumbo frames in the production system due to the lack of a direct network connection, but in the test system the rate increased to 3 kHz when requesting four events per readout request. The multiple event requests slightly increase the risk of data loss and are not expected to be needed at the nominal FASER trigger rates, but could be deployed in case the physics trigger rates are higher than expected or for special high rate data taking.

## 6.2 TLB standalone commissioning

The functionality of the trigger logic board described in section 3.4 is tested in a lab setup in which a signal generator is used to supply various configurations of signals to the CAEN digitizer and the digitizer trigger outputs are fed to the TLB. The results are verified by studying the signal inputs and outputs on an oscilloscope and / or analysing the data output from the board.

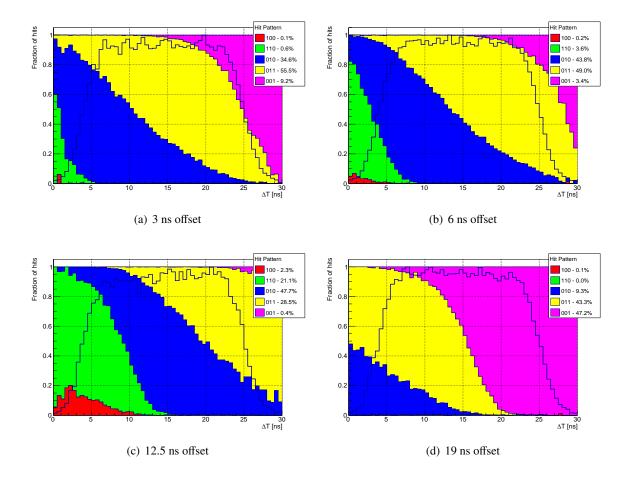

# 6.2.1 Signal timing

Input signals to the TLB can be individually timed via two functionalities to ultimately synchronise all input signals stably: a delay in increments of 1 BC up to 3 BCs total, and the option to sample an input signal on the falling or rising edge of the LHC clock. The input delay is tested by splitting the signal from a signal generator and purposefully delaying one of the signals by 30 ns (just over one LHC clock cycle) before feeding them to the digitizer. The TLB trigger LUT is configured to only trigger on the coincidence of the two input signals from the digitizer. Figure 20 shows two input signals, with a difference in arrival time of 30 ns, and the L1A signal sent out by the TLB. The L1A signal appears only once an input delay of 1 bunch-crossing is applied to the early signal, thereby showing that the TLB can successfully synchronise trigger input signals that would arrive

**Figure 19**. Maximum achievable read out rate for the digitizer as a function of the event size for three different groupings of the events.

**Figure 20**. An oscilloscope image of two trigger input signals sent by the digitizer. The TLB is set to only trigger on a coincidence of the two input signals. Input signal 1 is purposefully delayed by 30ns (over 1 clock cycle). A delay of 1 clock cycle is applied on input signal 2 on the TLB, which has resynchronised the input signals to give rise to an L1A.

at different times due to differences in signal processing, cable lengths and time-of-flight. The test is repeated for time differences of up to 3 clock cycles.

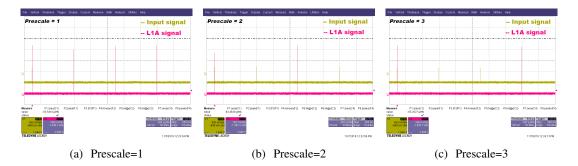

**Figure 21**. An oscilloscope image of a 2 kHz input signal sent from the digitizer to the TLB, and the subsequent TLB L1A signal, for different TLB prescale settings. The L1A signal appears only for every nth input signal where n is the prescale setting.

#### 6.2.2 Rate control

The rate on the TLB is controlled either by prescaling individual trigger items or via the vetoing of triggers due to several sources described in section 3.4.

The prescale functionality is tested on a single 2 kHz input signal from the digitizer to the TLB. Oscilloscope images of the input signal and the TLB L1A signal are shown in figure 21 for prescale settings of 1, 2 and 3. It is shown that only every nth trigger gives rise to an L1A signal where n is the prescale setting.

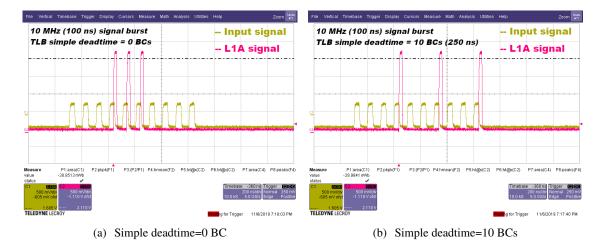

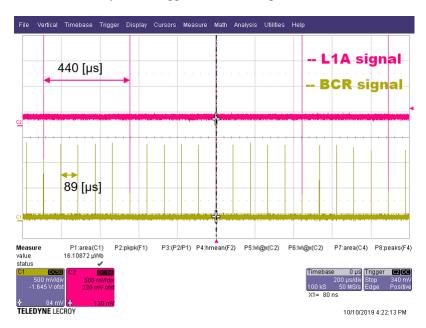

Three veto sources asserted by the TLB itself are tested in the lab setup, namely the simple deadtime veto, the rate limiter and the bunch-crossing reset veto. The simple deadtime veto is tested by supplying a 10 MHz 10-pulse signal burst to the digitizer-TLB system, as shown in figure 22 for a simple deadtime veto window of 0 and 10 bunch-crossings. While the former shows three L1A signals every 100 ns, the latter shows three consecutive L1A signals for every third input signal 300 ns after. The 2 input signals in between are vetoed as they lie within the 250 ns shadow of the simple deadtime veto. The results further demonstrate the rate limiter functionality, which has not allowed more than 3 L1A signals per burst, or per orbit. The rate limiter functionality is demonstrated again in figure 23. In this case the BCR signal from the TLB is fed into the digitizer. The rate limiter regulates the rate via a counter that increases upon an L1A and decreases by 1 on every 5th orbit. The veto sets in when the counter is above 3. Hence, the oscilloscope shot shows an L1A only for every 5th orbit signal, when the counter is decreased to 2 briefly, while the next 4 signals are vetoed.

### **6.2.3** Further trigger features

As described in section 3.4, the TLB has the capability to generate its own triggers, either at fixed or pseudo-random rate. Table 2 lists the average random trigger rate over 1 million triggered events for 8 different available settings on the TLB. The random trigger is shown to have a triggering range of 15 Hz - 1.2 kHz.

Other aspects are also verified; these include the BCR veto functionality and the expected BCID distribution in randomly triggered events, which is confirmed to be flat for BCIDs between 1 and 3555 and empty in the BCR veto window in BCIDs between 3556 and 3564. An essential

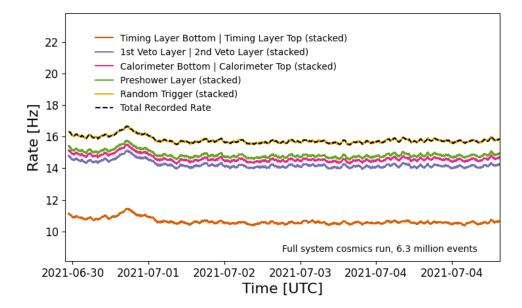

**Figure 22**. An oscilloscope image of a 10 MHz 10-pulse signal burst sent from the digitizer to the TLB, and the subsequent TLB L1A signal, for different TLB simple deadtime settings. For a simple deadtime of 0 BC, the L1A appears for 3 consecutive signals. For a simple deadtime of 10 BCs (250 ns), the 2 input signals following an L1A are vetoed. Only 3 L1As appear in total for a pulse burst due to the TLB rate limiter.