# The MAPS foil

S. Beolé<sup>a</sup>, F. Carnesecchi<sup>b</sup>, G. Contin<sup>c</sup>, R. de Oliveira<sup>b</sup>, A. di Mauro<sup>b</sup>,

S. Ferry<sup>b</sup>, H. Hillemanns<sup>b</sup>, A. Junique<sup>b</sup>, A. Kluge<sup>b</sup>, L. Lautner<sup>b,d</sup>, M. Mager<sup>b,\*</sup>,

B. Mehl<sup>b</sup>, K. Rebane<sup>b,e</sup>, F. Reidt<sup>b</sup>, I. Sanna<sup>b,d</sup>, M. Šuljić<sup>b</sup>, A. Yüncü<sup>f</sup>

<sup>a</sup> University and INFN Torino, Torino, Italy

<sup>b</sup> CERN, Geneva, Switzerland

<sup>c</sup> University and INFN Trieste, Trieste, Italy

<sup>d</sup> Technical University of Munich, Munich, Germany

<sup>e</sup> Tallinn University of Technology, Tallinn, Estonia

<sup>f</sup> University of Heidelberg, Heidelberg, Germany

### Abstract

We present a method of embedding a Monolithic Active Pixel Sensor (MAPS) into a flexible printed circuit board (FPC) and its interconnection by means of through-hole copper plating. The resulting assembly, baptised "MAPS foil", is a flexible, light, protected, and fully integrated detector module. By using widely available printed circuit board manufacturing techniques, the production of these devices can be scaled easily in size and volume, making it a compelling candidate for future large-scale applications.

A first series of prototypes that embed the ALPIDE chip has been produced, functionally tested, and shown to be working.

Keywords: Monolithic Active Pixel Sensors, Solid state detectors

## 1. Introduction

Monolithic Active Pixel Sensors (MAPS) have a number of distinctive properties, which make them the technology of choice for numerous tracking and vertex detectors, where low material budgets and high intrinsic resolutions are key (e.g. [1, 2, 3, 4, 5, 6, 7, 8, 9, 10]). The ALPIDE chip [11], which was developed for the new ALICE Inner Tracking System ("ITS2"), for instance, achieves an intrinsic spatial resolution of 5 µm and has a nominal thickness of only 50 µm, corresponding to 0.05 % of radiation length ( $X_0$ ). The ITS2 covers an area of 10 m<sup>2</sup>; it has recently been installed and is taking data at LHC, marking the first large-scale application of MAPS in high energy physics. A 60 m<sup>2</sup> tracker is envisaged for the ALICE3 detector, targeting installation during the LHC Long Shutdown 4 (2033–34), and asking for new module concepts that can be

Preprint submitted to Nucl. Instrum. Methods Phys. Res. A

<sup>\*</sup>Corresponding author: Email: Magnus.Mager@cern.ch

industrialised, while at the same time meeting stringent material budget constraints [4].

The R&D for replacing the inner-most layers of ITS2 by new MAPS layers (ITS3 project [3]) based on bent, wafer-scale sensors is currently ongoing. Through a reduction of the material budget by a factor of seven with respect to ITS2 and moving closer to the interaction point, ITS3 aims to achieve unprecedented position resolution figures. First results demonstrate the feasibility of bent MAPS [12], paving the way to new, optimised detector geometries. Within this R&D for bending thin silicon, the here-presented technique to both protect and interconnect sensors was conceived, making the technology potentially even more versatile while adding only a small amount of material.

Current lowest mass detector assemblies are typically based on thin chips that are glued onto thin printed circuit boards and interconnected e.g. with wire bonds or SpTAB bonding (see e.g. [13]). These assemblies are then held in flat position by external support mechanics or stiffeners.

In this paper, we propose, and demonstrate, a method to fully embed 50 µmthin MAPS into polyimide flexible printed circuit boards. The resulting assembly does not only protect the silicon chip, but also provides the electrical interconnection. Furthermore, the assembly remains flexible and protects the chips from breakage when bending them. Excluding the copper layer, our prototype has a material budget of around  $0.1 \% X_0$ , only twice that of the chip alone. Future optimisations of the process can potentially lower this further if required. The fill-factor of the copper layer will be subject to optimisation and hence its relative contribution to the total material budget will be highly application-dependent.

The process is inspired by previous works [14, 15], but differs in the choice of interconnection metallurgy and does not require a chip-level redistribution layer, simplifying the procedure and, importantly, making it compatible with industry-standard manufacturing techniques.

Our process can easily be extended to larger areas, integrating and interconnecting several chips. It can also be considered as a means of adding a coarse routing layer to large, stitched chips, for instance for improved power distribution.

The resulting assembly is a flexible, highly integrated, thin, and yet robust vertexing layer, that can be scaled to large surfaces.

## 2. The MAPS foil concept

The basic idea of the MAPS foil is to embed MAPS sensors, either single or multiple ones, into flexible printed circuit boards. A sandwich of polyimide films, glue and sensor is made, and the copper traces are connected to the sensor by through-hole metallisation.

The assembly provides three main features at once:

• Mechanical support: the polyimide serves as a support structure to which precise mechanical alignment holes can be added; in addition, a

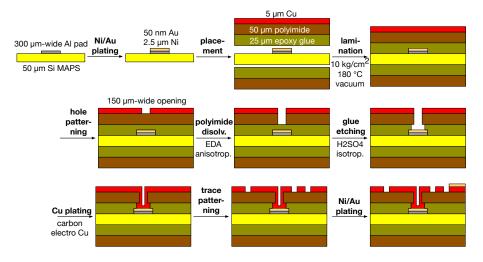

Figure 1: The MAPS foil production process steps (from top left to bottom right).

number of chips can be placed next to each other to form a multi-chip module

- Mechanical protection: the polyimide protects the silicon; it can be manipulated by bare hands easily

- Electrical interconnection: the top polyimide film can be copper-clad and structured to form electrical traces, like in ordinary printed circuit boards; they can be interconnected to the chip pads, by opening holes and metallising them

The foil moreover remains flexible (as long as the sensor  $is^1$ ) and can be shaped into e.g. cylindrical shapes. It can indeed prevent early breakage by smoothing out the stress distribution over the silicon.

#### 3. Process

The creation of the MAPS foil consists of two main stages: the embedding of the chip(s) between two polyimide films, and the electrical interconnection. The process, which is similar to the production of multi-layer printed circuit boards, is depicted in Fig. 1 and discussed hereafter. The mentioned material thicknesses are those used for the production of the first prototype and can be further optimised.

<sup>&</sup>lt;sup>1</sup>Despite the different layers of material, preliminary tests show that sensors can easily be bent to R = 30 mm (and very likely much further). More details will be subject of a future publication.

### 3.1. Chip preparation

The interconnection to the chip is based on metallisation, in a fashion similar to via plating in ordinary PCB manufacturing. For the metallurgy to work, the aluminium pads of the chip are first nickel-gold plated. A 2.5 µm-thick nickel layer is deposited with a 50 nm-thick gold finish.

## 3.2. Embedding

To tie the chip(s) to the polyimide, a thin glue layer is applied to the latter. The glue stems from an FR4 pre-preg<sup>2</sup> that is first applied to the polyimide film, and from which the fibres are removed afterwards. The polyimide-gluechip-glue-polyimide sandwich is then compressed and heated to cure the glue.

### 3.3. Interconnection

For the interconnection, a copper-clad polyimide is used when embedding the chip. In the next steps a hole is opened over the pad positions, subsequently in the copper layer, the polyimide and the glue. This is done in a wet-chemical fashion, with different chemicals for the different layers<sup>3</sup>. The copper etching is done by applying a UV mask, and the subsequent steps are self-aligned, i.e. they use the layers above as masks. Since the chip can be seen from below (there is no copper cladding underneath the chip), the alignment of the first mask can be done quite accurately, certainly to the required level of the order of 50 µm, which is given by the attainable structure size and the dimensions of the chip pads. Once the hole is opened, copper electro-plating is performed, creating the metal interconnection between the pad and the copper layer.

## 3.4. Trace patterning

The final steps consist in etching the traces on the copper (similar fashion as the hole opening in the copper), and the nickel-gold plating of contacts for interconnection of the foil to other devices.

## 4. Prototype

A first prototype was realised using ALPIDE sensors developed for the ITS2. ALPIDEs are  $30 \times 15 \text{ mm}^2$ -large MAPS fabricated in the TowerJazz 180 nm CMOS Imaging Technology [17], that are readily thinned down to approximately 50 µm. They feature about 60 large, 300 µm-diameter, pads that are distributed over the chip surface for interconnection to detector modules<sup>4</sup>, making them suited for the process explained here (cf. Fig. 2).

<sup>&</sup>lt;sup>2</sup>Ditron PRG-EP-84

$<sup>^{3}</sup>$ The process builds largely on the experience that was gained with GEM foils [16].

<sup>&</sup>lt;sup>4</sup>Within the ITS2, ALPIDEs are interconnected using wire-bonds through openings in a standard flexible printed circuit board that is placed over the chips, though different schemes were tried during the R&D phase, notably including laser soldering [2].

Figure 2: Photograph of the ALPIDE chip, displaying the pattern of the large pads used for interconnection, zooming on one of them.

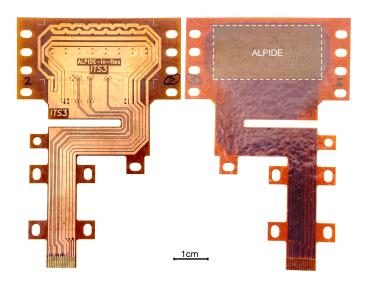

Figure 3: Photographs (front and back) of the assembly. The ALPIDE is embedded at the top part (annotated on the right).

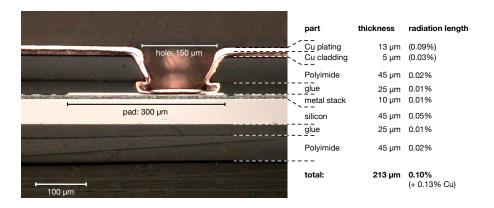

Figure 4: Cross-section of one interconnection point and associated material budget breakdown. Radiation lengths from [19], and assuming a generic value of 35.5 cm for the epoxy glue.

Figure 3 shows what the prototype assembly looks like. It is a single-sided circuit board, that can be connected to existing readout hardware developed within the ALICE ITS MAPS R&D [18].

Five of these assemblies were fabricated and electrically tested for possible malfunctions of the sensors<sup>5</sup>. None was showing evidence for breaking the sensor, while two had a slight misalignment of the pads and holes, leading to non-working interconnections. This was spotted already during manufacturing, and we do not consider this a principle problem.

Figure 4 shows the cross-section through one of the interconnections. The composition of the foil, the different characteristic geometries obtained from polyimide and glue openings, and the deposited copper plating that makes a solid contact are clearly visible. A material budget breakdown is given alongside, showing that the "extra" material accounts for roughly as much as the sensor itself. The copper layer is not included here, as its contribution will scale with the fill-factor of the traces as well as with the total thickness allowed for each specific application.

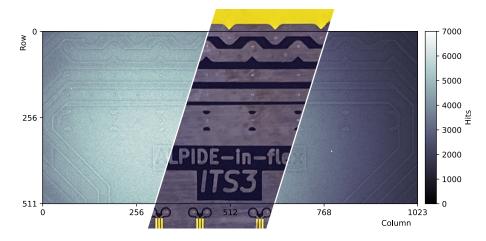

Three devices were successfully tested for functionality, including their response to an Sr-90 beta source, which created beta scattering images of the copper layers as shown in Fig. 5, nicely demonstrating the functioning of the assembly.

## 5. Discussion and relation to other methods

We would like to point out a few aspects that are key to our method, and make it distinct from other approaches:

<sup>&</sup>lt;sup>5</sup>The sensors were tested systematically beforehand by means of probe testing.

Figure 5: Beta scattering image, self-portrait, of the assembly as acquired by the embedded chip, while being exposed to electrons from a Sr-90 source. The central part is overlaid with a photograph of the assembly to guide the eye. The drop of hit frequency towards the right and edges of the pixel array is due to the positioning of the source.

- Subtractive manufacturing: The application of a solid glue layer and creation of the holes afterwards in a subtractive manner has an advantage over segmented gluing (e.g. by glue dispensing), since its initial application can be controlled more easily.

- **Symmetry:** The polyimide-chip-polyimide symmetry of the assembly reduces deformation after the gluing due to a mismatch of thermal expansion coefficients of chip, glue and polyimide.

- **Copper:** Using copper as metallisation material makes the method compatible with standard PCB/FPC manufacturing. An alternative approach using aluminium is however being investigated, since it allows to reduce the material budget. It would have the advantage of connecting aluminium pads to aluminium traces, but this requires custom equipment. There are, however, important difficulties when working with aluminium, which may motivate the use of copper. Aluminium is more fragile, tending to break more easily, effectively reducing the integration density. It also needs to be sputtered (not electroplated), which makes the creation of metallised holes much more difficult.

- Interconnection method: The interconnection by metallisation has a coarser feature size than, for instance, wire bonding. It has the advantage of a solid and robust interconnection, without the need of extra protection. In principle, wire bonds through larger openings could coexist if a higher connection density is needed.

#### 6. Summary & outlook

We demonstrated a method to construct detector modules by embedding sensors in polyimide films. The resulting first "MAPS foils" have outstanding properties, potentially allowing the production of large detector systems in an industrial fashion.

This first successful trial also sparked a number of activities aiming at the construction of multi-chip modules, embedding of wafer-scale chips, as well as using chips produced in a 65 nm process, which is the target technology node for the ITS3. In addition, investigations of using a laser assisted process for the hole formation and using aluminium instead of copper are ongoing. Finally, the robustness, including the ageing of the assemblies, is being studied.

MAPS foils are a novel way to solve the module integration problem, bridging semiconductor sensors to macroscopic detector elements in an integrated fashion. They are protected, versatile, and flexible, yet only adding a minimal amount of material to the bare sensors. This is an appealing combination for many applications that require minimal material budgets.

### Acknowledgements

M. Mager feels indebted to the late W. Dulinski for his inspiring demonstration of a very similar prototype at the Front End Electronics Workshop at the Argonne National Laboratory in May 2014 [15].

## References

- G. Contin, et al., The STAR MAPS-based PiXeL detector, Nucl. Instrum. Methods Phys. Res. A 907 (2018) 60-80. doi:10.1016/j.nima.2018.03. 003.

- [2] ALICE collaboration, Technical Design Report for the Upgrade of the ALICE inner tracking system, J. Phys. G 41 (8) (2014) 087002. doi: 10.1088/0954-3899/41/8/087002.

- [3] ALICE collaboration, Letter of Intent for an ALICE ITS Upgrade in LS3 (2019).

URL https://cds.cern.ch/record/2703140

- [4] ALICE collaboration, Letter of Intent for ALICE 3: A next generation heavy-ion experiment at the LHC (2022). URL https://cds.cern.ch/record/2803563

- [5] C. Dean (sPHENIX Collaboration), The sPHENIX experiment at RHIC, in: PoS ICHEP2020, 2021, p. 731. doi:10.22323/1.390.0731.

- [6] P. Senger, V. Friese, CBM Progress Report 2020 (2021). doi:10.15120/ GSI-2021-00421.

- [7] V. Zherebchevsky, V. Kondratiev, V. Vechernin, S. Igolkin, The concept of the MPD vertex detector for the detection of rare events in Au+Au collisions at the NICA collider, Nucl. Instrum. Methods Phys. Res. A 985 (2021) 164668. doi:10.1016/j.nima.2020.164668.

- [8] H. Abramowicz, et al., Conceptual design report for the LUXE experiment, Eur. Phys. J. ST 230 (11) (2021) 2445-2560. arXiv:2102.02032, doi: 10.1140/epjs/s11734-021-00249-z.

- K. Arndt, et al., Technical design of the phase I Mu3e experiment, Nucl. Instrum. Methods Phys. Res. A 1014 (2021) 165679. doi:https://doi. org/10.1016/j.nima.2021.165679.

- [10] Belle II Collaboration, Snowmass Whitepaper: The Belle II Detector Upgrade Program (2022). doi:10.48550/arXiv.2203.11349.

- [11] G. Aglieri Rinella (ALICE Collaboration), The ALPIDE pixel sensor chip for the upgrade of the ALICE Inner Tracking System, Nucl. Instrum. Methods Phys. Res. A 845 (2017) 583–587. doi:10.1016/j.nima.2016.05.016.

- [12] ALICE ITS project, First demonstration of in-beam performance of bent Monolithic Active Pixel Sensors, Nucl. Instrum. Methods Phys. Res. A 1028 (2022) 166280. doi:10.1016/j.nima.2021.166280.

- [13] M. Oinonen, et al., ALICE Silicon Strip Detector Module Assembly with Single-Point TAB Interconnections, in: 11th Workshop on Electronics for LHC and Future Experiments, 2005, pp. 92–97. doi:10.5170/ CERN-2005-011.92.

- [14] N. Chon-Sen, et al., Development of ultra-light pixelated ladders for an ILC vertex detector (2010). doi:10.48550/arXiv.1006.5424.

- [15] W. Dulinski, Post-processing steps for monolithic (CMOS) sensors: possible added-on value, Slides presented at the Front End Electronics (FEE 2014) (2014).

URL https://indico.cern.ch/event/276611/contributions/622863/attachments/502969/694527/dulinski\_FEE-2014.pdf

- [16] F. Sauli, The gas electron multiplier (GEM): Operating principles and applications, Nucl. Instrum. Methods Phys. Res. A 805 (2016) 2–24. doi:10.1016/j.nima.2015.07.060.

- [17] CMOS Image Sensor Tower Semiconductor (2022). URL https://towersemi.com/technology/cmos\_image\_sensor/

- [18] S. Siddhanta, et al., A Readout System for single ALPIDE sensors of the ALICE Inner Tracking System Upgrade, in: 2020 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), 2020, pp. 1–3. doi:10.1109/NSS/MIC42677.2020.9508095.

- [19] Particle Data Group, Review of Particle Physics, Prog. Theor. Exp. Phys. 2022 (8), 083C01 (2022). doi:10.1093/ptep/ptac097.