# Efficient Privacy-Preserving Machine Learning with Lightweight Trusted Hardware

Pengzhi Huang Cornell University ph448@cornell.edu Thang Hoang Virginia Tech thanghoang@vt.edu Yueying Li Cornell University yl3469@cornell.edu

Elaine Shi Carnegie Mellon University runting@gmail.com G. Edward Suh NVIDIA<sup>1</sup> / Cornell University edward.suh@cornell.edu

#### **ABSTRACT**

In this paper, we propose a new secure machine learning inference platform assisted by a small dedicated security processor, which will be easier to protect and deploy compared to today's TEEs integrated into high-performance processors. Our platform provides three main advantages over the state-of-the-art: (i) We achieve significant performance improvements compared to state-of-the-art distributed Privacy-Preserving Machine Learning (PPML) protocols, with only a small security processor that is comparable to a discrete security chip such as the Trusted Platform Module (TPM) or on-chip security subsystems in SoCs similar to the Apple enclave processor. In the semi-honest setting with WAN/GPU, our scheme is  $4\times-63\times$ faster than Falcon (PoPETs'21) and AriaNN (PoPETs'22) and 3.8×-12× more communication efficient. We achieve even higher performance improvements in the malicious setting. (ii) Our platform guarantees security with abort against malicious adversaries under honest majority assumption. (iii) Our technique is not limited by the size of secure memory in a TEE and can support high-capacity modern neural networks like ResNet18 and Transformer. While previous work investigated the use of high-performance TEEs in PPML, this work represents the first to show that even tiny secure hardware with very limited performance can be leveraged to significantly speed-up distributed PPML protocols if the protocol can be carefully designed for lightweight trusted hardware.

#### **KEYWORDS**

Multi-party computation, Secure hardware, Machine learning

## 1 INTRODUCTION

As the world increasingly relies on machine learning (ML) for everyday tasks, a large amount of potentially sensitive or private data need to be processed by ML learning algorithms. For example, ML models for medical applications may need to use private datasets distributed in multiple nations as inputs [39]. A cloud-based ML services process private data from users with pre-trained models to provide predictions [13, 50]. The data to be shared in these applications are often private and sensitive and must be protected

https://doi.org/XXXXXXXXXXXXXXX

This work is licensed under the Creative Commons Attribution 4.0 International License. To view a copy of this license visit https://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA. Proceedings on Privacy Enhancing Technologies YYYY(X), 1–22

© YYYY Copyright held by the owner/author(s).

from the risk of leakage. Government regulations may play an essential role as a policy, but cannot guarantee actual protection. We need technical protection for privacy-preserving machine learning (PPML) for strong confidentiality and privacy guarantees.

In this paper, we propose a new PPML framework, named Stamp (Small Trusted hardware Assisted MPc), which enables far more efficient secure multiparty computation (MPC) for machine learning through a novel use of small lightweight trusted hardware (LTH). MPC refers to a protocol that allows multiple participants to jointly evaluate a particular function while preventing their inputs from being revealed to each other. Ever since Yao's initial studies (later called Garbled Circuit) [96, 97] which gave such a secure protocol in the case of two semi-honest parties, many studies have been conducted to improve the efficiency, to expand to more than two parties, and to ensure the feasibility against malicious behaviors. Recently, there has been significant interest in using and optimizing MPC for secure machine learning computation [42, 58, 71, 88, 89]. However, the overhead for MPC-based PPML is still significant.

For low-overhead secure computation, trusted execution environments (TEEs) in modern microprocessors such as Intel SGX [14] AMD SEV [72] aim to provide hardware-based protection for the confidentiality and integrity of data and code inside. If the TEE protection and the software inside can be trusted, secure machine learning computation can be performed directly inside a TEE with relatively low overhead [41]. The TEE can also be used to improve cryptographic protocols by accelerating bootstrapping [40, 51] or simplifying protocols [2, 12, 20, 40]. However, it is challenging to build a secure environment inside a high-performance processor due to its large trusted computing base (TCB) and complex performance optimizations such as out-of-order execution, speculation, and caching. For example, multiple attacks have been shown for SGX [24, 84, 85]. Moreover, the TEE requires adding hardware protection to each type of computing engines (CPU, GPU, and accelerators), and significant changes to the software stack. As a result, developing and deploying a TEE for a new piece of hardware requires significant effort and time.

In this paper, we propose to leverage a small dedicated security processor, another type of trusted hardware that is widely deployed today, to reduce the MPC overhead. For example, small discrete security chips such as trusted platform module (TPM), Google Titan, and Apple T1 are widely used as a platform root-of-trust. For system-on-chip (SoC) designs, on-chip security subsystems like the Apple enclave processor perform security-critical operations such as secure booting, attestation, and key management.

1

Œ

<sup>&</sup>lt;sup>1</sup>This work was done while the author was at Meta.

While the high-level idea to combine trusted hardware and MPC has been explored before, we believe this work represents the first to investigate MPC acceleration using a small security processor. Clearly, such lightweight trusted hardware can only provide relatively low performance. The main question is if a low-performance trusted hardware can still be leveraged to provide meaningful speedups for MPC. In the following discussion, we refer to such small security processors as lightweight trusted hardware (LTH).

The key insight we leverage in STAMP is that non-linear operations, which can be performed very efficiently in plaintext, account for the major part of the overhead in MPC. MPC-based deep learning inference is not particularly expensive in computation but introduces large communication overhead due to multi-round data exchanges, especially when the network latency is high. This overhead leads to a very different cost distribution for MPC compared to plaintext computation. Profiling an inference task of AlexNet [44], which represents a classical deep learning model, shows that 85% of total plaintext execution time comes from linear operations such as convolution and fully-connected layers, while for MPC, this portion drops to only 5% with the remaining 95% coming from non-linear operations. Most of those non-linear operations are simple and cheap in plaintext (e.g., ReLU, MaxPooling, which are generally comparisons) with some exceptions (e.g., Softmax). This observation implies that even a lightweight trusted hardware can potentially speed up MPC-based PPML significantly if we can efficiently offload non-linear operations.

Stamp combines the advantages of MPC and trusted hardware by performing linear operations in MPC while leveraging LTH for non-linear operations. To realize this approach, we introduce new MPC protocols that efficiently offload non-linear operations while minimizing communications among multiple parties and between the LTH and an untrusted CPU/GPU. Although simple nonlinear operations can be performed inside the small LTH with sufficiently high performance, expensive operations such as Softmax require higher performance. To address the challenge, Stamp securely offloads parts of the expensive exponentiation operations to an untrusted CPU/GPU. The following describes the main technical contributions and advantages of Stamp.

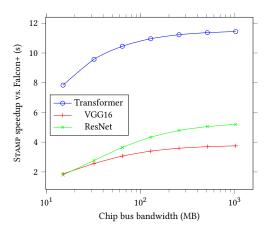

Insight and performance improvement. STAMP represents the first work to investigate if tiny low-performance security processors can still be leveraged to meaningfully speed-up MPC protocols. Our results demonstrate that even with trust in a tiny piece of discrete secure hardware similar to a TPM, significant speedups can be achieved for privacy-preserving neural network inference when the MPC protocol is carefully redesigned for efficient offloading of non-linear operations. We compared STAMP with three state-of-theart MPC protocols (Falcon [89], AriaNN [71], and CryptGPU [81]). The results show that STAMP achieves significantly lower inference overhead compared to the state-of-the-art MPC protocols on either CPUs or GPUs, under either a WAN or LAN setting, and using either a discrete security chip (LTH-chip) or a security processor on an SoC (LTH-SoC). STAMP is 4x to 63x faster in the semi-honest WAN/GPU setting, even with the tiny LTH-chip with a low-bandwidth interconnection, and reduces the inter-party communication by 7× to 10×. Stamp can also improve the performance of the MPC-based secure inference in malicious settings. Interestingly, the experimental results show that STAMP (LTH-SoC) can

even outperform a protocol that leverages a high-performance TEE (Intel SGX) with secure GPU outsourcing (Goten [61]) thanks to its ability to significantly reduce the inter-party communication. While Stamp can also be used with a high-performance TEE to further improve performance, this result suggests that tiny low-performance secure hardware can indeed be sufficient if it is primarily used for non-linear operations. Stamp provides the most significant performance improvements under GPU/WAN settings when WAN communication represents more of a performance bottleneck compared to GPU-based computation.

Malicious security. Stamp provides security guarantees under the honest-majority setting similar to previous schemes [58, 89], assuming that the majority (2 out of the 3 participants) are behaving honestly. If the corrupted party behaves semi-honestly, the protocol ensures that no information is obtained by any party without reconstructing a value. If a party is actively corrupted and behaves maliciously, we guarantee detection of such a behavior and output "abort" while still keeping the confidentiality of the data with extra steps. We show the security of Stamp using the standard simulation-based paradigm in Appendix C. We implement both semi-honest and malicious protocols in our end-to-end framework.

Prototype implementation. We implemented a functional prototype of both semi-honest and malicious protocols of STAMP in C++. The compilation framework and a small number of pure MPC-based operations (see §3.2 and Appendix A) are based on [89]. The baseline framework was significantly modified to incorporate new non-linear operation protocols, GPUs support, new networks and datasets, and a better socket library. The prototype implementation supports both CPU-only and GPU-assisted settings, and adds the same GPU support to our baseline for a fair comparison.

Evaluation and analysis. We demonstrate STAMP by supporting the secure inference of various networks including AlexNet [44], VGG16 [74], ResNet18 [29] and Transformer [92], over multiple datasets including MNIST [16], CIFAR-10 [43], ImageNet [70] and Wikitext-2 [53], under both WAN and LAN, and semi-honest and malicious settings. We provide theoretical analysis of the overhead and scalability analysis. We perform detailed experimental studies against state-of-the-art MPC protocols, and also protocols leveraging high-performance TEEs for a balanced discussion on the trade-off. We show that even a very small trusted hardware reduces the overhead of MPC protocols significantly while supporting various high-capacity networks, and STAMP can support larger models without extra overhead in most cases.

#### 2 MODEL

**System Model.** In our system, there are three parties who want to run a common ML model together using inputs from individuals. We assume that the model structure is publicly known. We assume that each party consists of two components: an untrusted machine (CPU/GPU) and an LTH module whose computational power is limited. LTH in each party communicates with each other through its host by establishing pairwise secure communication channels. **Threat Model.** The goal of STAMP is to protect the confidentiality and the integrity of ML model inference in the presence of a malicious adversary. We capture such confidentiality and integrity through simulation-based security [7, 8, 23]:

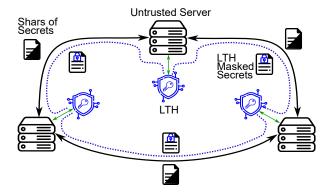

Figure 1: STAMP system and threat model. The black local machines owned by three parties, green local buses, and black inter-party communication channels are untrusted. The blue LTHs are trusted and contain secret keys shared among LTHs.

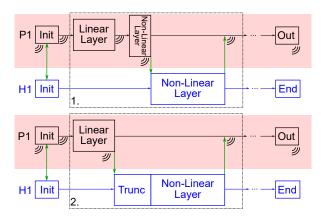

Figure 2: The STAMP execution flow on one of the parties. Inter-party communication (wave symbol) and the local communication with the LTH (green arrows) happen during initialization and execution, with (1) or without (2) the optimization in §4.2. An adversary has complete control over the data and operations in the red zone.

**Definition 1 (Simulation-based security: privacy and verifiability).** A protocol  $\pi_{\mathcal{F}}$  is said to securely realize the ideal functionality  $\mathcal{F}$  if for any probabilistic polynomial time (PPT) real-world adversary  $\mathcal{A}$ , there exists an ideal-world adversary  $\mathcal{S}$  such that for any PPT environment  $\mathcal{Z}$ , there exists a negligible function negl such that

$$|\Pr[\mathsf{Real}_{\Pi_{\mathcal{F},\mathcal{A},\mathcal{Z}(\lambda)}} = 1] - \Pr[\mathsf{Ideal}_{\mathcal{F},\mathcal{S},\mathcal{Z}(\lambda)} = 1]| \le \mathsf{negl}(\lambda)$$

We consider honest majority, meaning that at most one party (except its LTH) can be malicious. The other two parties can be semi-honest, in which they may try to learn secrets (e.g., inputs or weights provided by other parties) while still following the protocol faithfully. The malicious adversary can deviate arbitrarily from the honest protocol, and its goal can be breaking the integrity of the evaluation by providing incorrect results without being noticed, or breaking the confidentiality of the data by learning the secrets. We assume that there is no collusion between any of the parties.

Figure 1 provides an overview of the STAMP system. We assume that a party or its server is untrusted except for its LTH. In other words, an adversary may control any part of the server, including a virtual machine monitor, an operating system, drivers, storage, and others except for LTH. We assume that the confidentiality and integrity of LTH are protected and an adversary cannot obtain data on an LTH or alter its execution. To ensure that only valid secure hardware can participate in the protocol, LTH contains a unique private key and is authenticated through a Certificate Authority (CA) during the initialization step. As shown in Figure 1, the three LTHs act as three trusted third parties with established correlations (secret keys). Figure 2 shows that the data flow between an untrusted server (red) and an LTH (blue) during the STAMP execution. Data should be encrypted before being sent to the red zone, and any data from or operations conducted in the red zone should be verified assuming the presence of a malicious adversary.

Note that Stamp, similar to other secure computation techniques based on TEE, MPC and / or homomorphic encryption (HE), does not prevent attacks that poison the model through malicious inputs or extract information from the trained parameters or model outputs [9, 83]. To defend against such algorithmic attacks, a secure computing framework such as Stamp needs to be combined with other orthogonal defense techniques (e.g., Differential Privacy [1], out-of-distribution points removal [95]). Additionally, Stamp primarily targets private inference, not training, so training data poisoning attacks are not its main concern.

The security model and its detailed analysis are presented in Appendix C. Although we assume that LTH is secure, we discuss how LTH provides security benefits over TEEs in §3.3 under a hybrid MPC+trusted hardware threat model.

#### 3 BACKGROUND

In this section, we describe our notation, and then provide some basics of MPC and trusted hardware.

#### 3.1 Notation

We define *L* as the finite field size, and  $\mathbb{Z}_L$  to be the finite field we generally consider in this work. fp is the fix-point precision. We use the bold font a or A to represent a vector or a matrix. We use  $a_i$ , (a)<sub>i</sub> or  $A_{i,j}$  to represent the  $i^{\bar{t}h}$  element of the vector **a** or the element of the matrix A in the  $i^{th}$  row and in the  $j^{th}$  column. This is different from the bold  $A_i$ , which still represents a matrix. Throughout the paper, if not specifically mentioned, all operations are carried out within the finite field  $\mathbb{Z}_L$ . When needed, we use  $(a+b)_L$  to represent the modulo *L* operation for the output of the integer operations in brackets. We add a bar to a variable or operation, as  $\bar{a}$ ,  $\overline{\exp(a)}$ , to represent that a number or an output is a real number. The rightshift operation is indicated as  $\gg$  (e.g.,  $a \gg b = a/2^b$ ). We will often use two signed integers m, q to represent a positive real number  $\bar{a}$  as  $\bar{a} = 2^q \cdot (m \gg 52)$  where m represents the mantissa part of 52 bits with  $m \gg 52 \in [0, 1)$ , and  $q_L$  is the exponent part. This is actually the format in which floating point numbers are represented following the IEEE Standard for Binary Floating-Point Arithmetic (IEEE 754-1985) [38], but without sign on the mantissa part. We use  $\lfloor \bar{a} \rfloor$  to round a real number  $\bar{a}$  down to an integer.

## 3.2 Multiparty Computation

**Notation.** The sharing scheme used in this work is the 2-out-of-3 replicated secret sharing scheme (RSS) modulo L. Let  $P_1, P_2, P_3$  be the three parties participating in the evaluation. For convenience, we use  $P_{i-1}, P_{i+1}$  to refer to the previous and next party of one party (e.g., the previous and the next party of  $P_1$  are  $P_3$  and  $P_2$ ). The RSS of an integer secret  $x \in \mathbb{Z}_L$  is denoted as  $[\![x]\!]^L = ([\![x]\!]^L_1, [\![x]\!]^L_2, [\![x]\!]^L_3)$ , where L is the size of the finite field to which the shares belong and  $x = [\![x]\!]^L_1 + [\![x]\!]^L_2 + [\![x]\!]^L_3$ . When a secret x is shared as  $[\![x]\!]^L$ , party  $P_i$  holds  $([\![x]\!]^L_i, [\![x]\!]^L_{i+1})$  for i = 1, 2, 3. To generate the integer representation x based on the real value  $\bar{x}$ , we use two's complement fixed-point encoding with fp bits of precision. For a positive  $\bar{x}$  we have  $x = \lfloor \bar{x} \cdot 2^{\mathrm{fp}} \rfloor$ , while for a negative  $\bar{x}, x = \lfloor \bar{x} \cdot 2^{\mathrm{fp}} \rfloor + L$ , assuming that x is within the bound  $[\![-L/2^{\mathrm{fp}}, L/2^{\mathrm{fp}})\!]$ .

In our experiments, we mainly use the cases of l=32, with fp = 13 and  $L=2^l$  (which supports inputs from -262144 to 262144 –  $2^{-13}$ ), to match the bit-width used in the baseline MPC schemes. The security of a l=32 setting naturally comes from the random masking creating the shares. Multiple existing MPC schemes [11, 69, 71, 89] use the 32-bit secret sharing setting and already prove its security. Our protocol can also use a larger field such as a 64-bit setting if a wider range of values need to be supported.

Here, we explain how multiplications are performed under 2-outof-3 RSS. These operations follow the protocols defined in [15, 58, 88, 89]. We describe the rest of the baseline MPC operations including share creation, reconstruction, and aggregation in Appendix A.

**Multiplications.**  $[\![x\cdot y]\!]^L \leftarrow \Pi_{\mathsf{Mul}}([\![x]\!]^L, [\![y]\!]^L)$ : To get  $[\![z]\!]^L = [\![x\cdot y]\!]^L, P_i$  first computes  $\hat{z}_i = [\![x_i]\!]^L [\![y_i]\!]^L + [\![x_{i+1}]\!]^L [\![y_i]\!]^L + [\![x_i]\!]^L [\![y_{i+1}]\!]^L$ , then  $(\hat{z}_1, \hat{z}_2, \hat{z}_3)$  is already a valid 3-out-of-3 secret sharing of xy since  $z_1 + z_2 + z_3 = xy$ . A reshare is needed to maintain the consistency of the 2-out-of-3 sharing scheme. To avoid any possible leakage of information,  $P_i$  uses the 3-out-of-3 randomness  $\{\alpha_i\}$  to mask  $\hat{z}_i$  as  $z_i = \hat{z}_i + \alpha_i$ , then share it with  $P_{i-1}$ . Therefore, the parties obtain the necessary shares and build  $[\![z]\!]^L = [\![xy]\!]^L = (z_1, z_2, z_3)$ .

Matrix Multiplications. ( $[\![AB]\!]^L$ )  $\leftarrow \Pi_{\text{MatMul}}([\![A]\!]^L, [\![B]\!]^L$ ): To perform matrix multiplication  $[\![C_{a \times c}]\!]^L = [\![A_{a \times b}B_{b \times c}]\!]^L$ , simply applying  $\Pi_{\text{Mul}}$  for each multiplication leads to O(abc) shares to be sent. The parties can instead perform part of the addition of shares locally (i.e.,  $[\![\hat{C}]\!]_i^L = [\![A]\!]_i^L [\![B]\!]_i^L + [\![A]\!]_i^L [\![B]\!]_{i+1}^L + [\![A]\!]_{i+1}^L [\![B]\!]_i^L$ ) and then share  $[\![\hat{C}]\!]_i^L$  at once. This strategy yields only O(ac) transmission overhead. As stated in [88], convolutions can be expanded into overall larger matrix multiplications.

The above multiplication protocols work well for integer representations, but will cause errors with fixed-point representations. A truncation protocol (right-shift the results by fp bits) must follow after a multiplication to correct the fixed-point precision in 3-party MPC. We refer the readers to ABY3 [58] for more details on the 3-party truncation protocol, to prior work [22, 58] for the malicious variant of  $\Pi_{\text{MatMul}}$ , and to Appendix A for other basic operations.

#### 3.3 Trusted/Secure Hardware

Dedicated security hardware has a long history of being successfully used in many high-security use cases, starting as (co-)processors specializing in crypto operations. For example, smart cards [67] are widely used in financial transactions. Similarly, hardware security

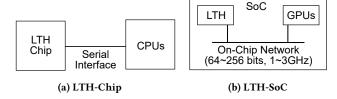

Figure 3: Two types of LTHs that STAMP considers.

modules (HSMs) such as IBM 4758 [18] have also been used to protect critical secret keys. Discrete security chips such as TPM [64], Google Titan [33], and Apple T1 provide hardware root-of-trust on many platforms. Modern System-on-Chip (SoC) designs also typically include a dedicated security processor with crypto engines for secure booting and other high-security operations: Synopsys tRoot hardware security module [80], Rambus RT-630 programmable root-of-trust (RoT) [35], Apple secure enclave [32], Qualcomm secure processing unit [34], etc. Even though their performance is limited and their implementations may still have security vulnerabilities [6, 27, 57], the small dedicated security processors are considered to be far more secure compared to high-performance processors. The dedicated security processors are also relatively easy to deploy as a separate chip or as an IP block.

For high-performance processors, the idea of trusted hardware developed into a trusted execution environment (TEE), which adds hardware-based security protection on a shared general-purpose processor running a full software stack [30, 72, 85]. A TEE aims to protect the integrity and confidentiality of the code and data inside, even when low-level software and/or the environment cannot be trusted. TEEs on modern processors can typically provide much higher performance compared to the dedicated security hardware, but also introduce new security challenges due to the large TCB and complex optimizations in high-performance processors [4, 19, 24, 26, 47, 48, 73, 90, 94]. The high-performance TEEs also require new hardware protection for each computing engine and significant changes to a complex software stack, making their deployment for new hardware challenging.

In this work, we consider lightweight trusted hardware (LTH) with performance and complexity similar to a traditional security chip or on-chip security subsystems in modern SoCs: a dedicated low-performance security processor that supports remote attestation to validate its identity and shared key exchanges (§4.1), has hardware crypto engines, and includes a programmable processor that can run code. We consider two types of LTH designs as shown in Figure 3: 1) a discrete security chip similar to a TPM (LTH-chip) running at a low clock frequency (tens of MHz), and connected to a CPU through a low-bandwidth interface; and 2) a security subsystem on an SoC (LTH-SoC) running at a much higher SoC clock frequency (1-3GHz), and connected to other processing engines (CPUs, GPUs, NPUs, etc.) on the same SoC through high-bandwidth on-chip networks. Our study suggests that even the LTH-chip can significantly improve the performance of the MPC-based PPML.

**Notation.** Each party  $P_i$  is equipped with a LTH  $H_i$ , which has a built-in PRF unit F (e.g., an AES engine) for pseudo-random number generation. We assume that even malicious participants cannot break the integrity and confidentiality guarantees that LTH provides. The protocols executed in  $H_i$  will be introduced in §4.

3.3.1 LTH Benefits. While it is difficult to quantify the security, we believe that LTH provides strong security and deployment benefits over high-performance TEEs. For example, the previous survey [19] provides an overview of the vulnerabilities in Intel SGX (high-performance TEE) and countermeasures. Most vulnerability categories (address translation, CPU cache, DRAM, branch prediction, rowhammer) in the survey do not apply to LTH due to the following reasons. Here, we provide a more detailed discussion of the security of LTH and list some attacks that LTH is more robust to.

**Physical isolation**: LTH is dedicated to a small set of security tasks, and physically separate from main processing cores with potentially malicious software. LTH tightly controls its software using secure booting and typically does not allow user software. Because hardware is not shared with potential attack software, there is much less concern for *timing-channel attacks* - a major challenge in today's TEEs.

Smaller TCB/attack surface, lower complexity: LTH uses a simple (in-order) processor with limited interfaces/commands for a small set of security tasks. Both hardware and software are much smaller and simpler compared to the main processors. For example, the dedicated security processors usually occupy less than 1mm² of the silicon area. On the other hand, a high-performance CPU takes hundreds of mm² and contains millions of lines of code (LoCs) [46], and is shared with many software components. Because there is no speculation or out-of-order execution, transient-execution attacks such as Meltdown/Spectre that can run commands or read memory without permission are not a concern for LTH. LTH does not have external memory (DRAM), and is not exposed to attacks on external memory such as DRAM probing and rowhammer attacks.

Side-channel protection: LTH such as smartcards, TPM, and others are usually equipped with dedicated crypto engines and countermeasures (e.g., tamper-resistant circuits [77] for TPM, randomized block design [56] for smart cards, etc.) against physical side channels such as power side channels, and without off-chip memory. In that sense, LTH is more robust against physical attacks. 3.3.2 LTH Limitations. The main limitation of LTH comes from its performance. LTH is typically not designed for high-performance computation. Both computation and communication on LTH are much slower compared to high-performance TEEs. As a result, the use of LTH comes with the additional challenges to support sufficient end-to-end performance. Traditionally, LTH is only used for small security-critical operations such as key management and infrequent signing. In order to leverage LTH for larger applications such as ML inference, we need to divide the workload and only offload small parts to LTH in a way that LTH does not become the performance bottleneck. In fact, STAMP had to be carefully designed to leverage low-performance LTH and our experimental results show that the overall performance still depends on the performance of LTH (LTH-chip vs. LTH-SoC). On the other hand, TEEs can closely match the performance of the underlying highperformance processors and can often be used to run the entire task such as ML inference inside, with minimal changes to the workload. If a high-performance TEE can be fully trusted, a TEE can replace the LTH in our scheme to provide higher performance or be used to run the entire ML inference without MPC.

While we believe that LTH provides stronger security compared to high-performance TEEs, we note that LTH can still have security vulnerabilities, similar to how secure cryptographic algorithms can be broken due to implementation-level vulnerabilities. For example, timing side channels and power interrupts may make TPM private key recovery possible [27, 57]. Smart cards, although practically considered secure enough and widely developed, have faced challenges including reverse engineering [65], micro probing [75], optical fault induction attacks [76], and others.

Compared to complex high-performance TEEs, LTH has far fewer vulnerabilities, making countermeasures easier to apply in terms of cost and design complexity. In practice, the main security concerns for today's TEE come from software-exploitable vulnerabilities. In that sense, LTH provides a major security benefit by removing most timing-channel or transient-execution vulnerabilities. While physical attacks are not considered a major threat in data-center environments, LTH can also provide strong physical security. LTH has no off-chip memory to protect, and often has anti-tamper/DPA countermeasures. In contrast, recent TEEs target weaker threat models against physical attacks. Intel removed the integrity tree for replay protection in Icelake/TDX. AMD SEV has no replay protection against physical attacks. NVIDIA GPU TEE (H100) does not even encrypt its high-bandwidth memory (HBM).

#### 4 THE STAMP PROTOCOL

This section introduces the details of the STAMP protocols for both semi-honest and malicious settings. We refer the reader to Appendix C for detailed security analysis.

## 4.1 Initialization phase

The initialization phase  $\Pi_{lnit}$  is a part of the offline phase (which needs no input data or model weights) of the protocol where the LTHs will have shared keys and initial values established in them if their identities are proven. Although  $\Pi_{lnit}$  plays an important role in our scheme, it is not where our main contribution lies, since mature remote attestation protocols already exist [3]. A simplified description of  $\Pi_{lnit}$  is shown in Protocol 1 .

The communication out of  $H_i$  has to go through  $P_i$ , which provides a corrupted party with a natural way to observe or even alter the communication among the LTHs. For semi-honest adversaries, the Diffie–Hellman key exchange protocol already prevents them from obtaining the key with bounded computational resources. If the corrupted party behaves maliciously,  $\Pi_{\text{Init}}$  does not have to take extra steps to detect such actions. If a malicious  $P_i$  modifies the remote attestation, a CA will not provide a certificate and  $P_i$  cannot create a certificate on its own, causing an abort. If a malicious  $P_i$  alters the transmission during key exchange, there will be no correct initialization established, and the protocol will abort later when data inconsistency is detected.

The shared keys and the PRF in the LTHs can support the pseudorandom number generation and are kept only known to the LTH, unlike the correlated randomness introduced in Appendix A. With the shared keys in §4.1 and a built-in PRF F, we can now construct  $\Pi_{\text{LTH.GenMask}}$  and  $\Pi_{\text{LTH.GenMaskShare}}$  in the LTH as Protocol 2 and Protocol 3. They are very similar with only a minor difference that  $\Pi_{\text{LTH.GenMaskShare}}$  always generates shares of  $\mathbf{0}$ . Four counters  $\{\text{ctr}_1^i, \text{ctr}_2^i, \text{ctr}_3^i, \text{ctr}_5^i\}$  are used in each  $H_i$  to maintain consistency among  $H_i$ s in a semi-honest setting, and additional four

## **Protocol 1** $\Pi_{lnit}$ Initialization

**Input.** Security parameter  $\lambda$ .

**Result.** Output (Success, L) if the remote attestation succeeds and aborts if failed. After the initialization, LTHs ( $H_i$ ) obtain shared keys and initial parameters.

- (1) Parties first agree to a L for the finite field  $\mathbb{Z}_L$ , size  $l = \log L$  bits, prime p, and their order to define the previous and next party.

- (2) P<sub>i</sub>s perform remote attestation on each H<sub>i</sub> to obtain a certificate from the CA and publicly share them to validate H<sub>i</sub>. Abort if validation fails.

- (3)  $H_i$  performs Diffie–Hellman key exchange with signature through the secure channel between  $P_i$ s to obtain  $O(\lambda)$ -bit PRF keys  $k_{i,i+1}, k_{i-1,i}$ , then use  $F_{k_{i,i+1}}$  to mask one key  $k'_{i-1,i} \equiv k_{i-1,i} + F_{k_{i,i+1}}(0) \mod p$  and send  $k'_{i-1,i}$  to  $H_{i+1}$  through  $P_i$ .  $H_i$  would receive  $k'_{i+1,i-1}$  from  $H_{i-1}$  and can recover  $k_{i+1,i-1} = k'_{i+1,i-1} F_{k_{i+1,i-1}}(0)$ .

**Protocol 2 m**

$$\leftarrow \Pi_{\mathsf{LTH.GenMask}}(n, L, j; i, \mathsf{ctr}_{i}^{i}, k_{j,j+1})$$

**Input.** The number of masks to be generated n, the index j for which counter, and which key to choose. The size of the finite field L, the counter  $\operatorname{ctr}_{j}^{i}$  and the key  $k_{j,j+1}$  are stored in the LTH.

**Output.** pseudo-random masks  $\mathbf{m} \in \mathbf{Z}_L$  and updated counter  $\operatorname{ctr}_j^i$ .  $\mathbf{m} = (F_{k_{j,j+1}}(\operatorname{ctr}_j^i), F_{k_{j,j+1}}(\operatorname{ctr}_j^i+1), ..., F_{k_{j,j+1}}(\operatorname{ctr}_j^i+n-1))$ . Update  $\operatorname{ctr}_i^i \leftarrow \operatorname{ctr}_i^i+n$ .

Protocol 3

$$(\llbracket \mathbf{m}_j \rrbracket_i^L, \llbracket \mathbf{m}_j \rrbracket_{i+1}^L) \leftarrow \Pi_{\mathsf{LTH.GenMaskShare}}(n, L; i, \mathsf{ctr}_s^i, k_{i,i+1}, k_{i+1,i-1}, k_{i-1,i})$$

**Input.** The number of masks to be generated n. The size of the finite field L and the counter and keys are stored in the LTH.

**Output.** pseudorandom masks  $[\![\mathbf{m}]\!]_i^L$ ,  $[\![\mathbf{m}]\!]_{i+1}^L \in \mathbb{Z}_L$

$$\begin{split} & [\![m_j]\!]_i^L = F_{k_{i,i+1}}(\mathsf{ctr}_s^i + j) - F_{k_{i+1,i-1}}(\mathsf{ctr}_s^i + j) \text{ for } j = 0,...,n-1 \\ & [\![m_j]\!]_{i+1}^L = F_{k_{i+1,i-1}}(\mathsf{ctr}_s^i + j) - F_{k_{i-1,i}}(\mathsf{ctr}_s^i + j) \text{ for } j = 0,...,n-1 \\ & \text{Update } \mathsf{ctr}_s^i \leftarrow \mathsf{ctr}_s^i + n. \end{split}$$

$\{\hat{\operatorname{ctr}}_1^i, \hat{\operatorname{ctr}}_2^i, \hat{\operatorname{ctr}}_3^i, \hat{\operatorname{ctr}}_s^i\}$  are needed in a malicious setting for reduplicate execution for the detection of inconsistency. Notice that Protocol 2 and Protocol 3 give the outputs to  $H_i$ , not  $P_i$ , and  $H_i$  may be set to give partial outputs in some protocols.

A proper remote attestation protocol is commonly supported on secure hardware, such as a TPM [64], and validates the LTH's identity and its state. This process can involve the acquisition of the certificate of a LTH from a trusted CA/Verifiers, which is usually the manufacturer of it.  $H_i$  after being verified, can perform pairwise Diffie-Hellman key exchanges with a signature to obtain the shared key  $k_{i-1,i}$  with  $H_{i-1}$ ,  $k_{i,i+1}$  with  $H_{i+1}$ , and then also  $k_{i+1,i-1}$  through sharing masks. The shared keys can support the pseudorandom number generation with PRF and are kept only known to the LTH.

## 4.2 Optimized ReLU with Matrix Multiplication

Non-linear layers used in a machine learning model are computationally light under plaintext. ReLU, for example, takes only one comparison and multiplexing. However, its complexity gets amplified significantly under the RSS scheme with more local computation steps and significant communication overhead.

Using each party's LTH and the common randomness established in §4.1, we can significantly reduce the overhead by "offloading" the non-linear operations to the LTH. For example, ReLU can be performed by: invoking  $\Pi_{\text{LTH.GenMask}}$  to get the pseudo-random masks, transmitting the masked shares, recovering the plaintext to

compute inside LTHs, and then generate and distribute the psuedorandom shares of the results. We show the details of this protocol ( $\Pi_{ReLU}$ ) in Appendix B.

In Stamp, we further optimize ReLU by combining it with truncation. For typical ML models [29, 44, 74, 92], ReLU is applied after matrix multiplications in convolution (Conv) or fully-connected (FC) layers. As introduced in §3.2, in a fixed-point setting, truncation is required after each multiplication to keep the consistency of the precision. If we apply  $\Pi_{ReLU}$  directly after the completion of multiplications, the communication overhead will be the multiplication / truncation overhead and the  $\Pi_{ReLU}$  overhead summed, which is not optimal. Since the truncation itself is also a simple non-linear function in plaintext (which is just right-shift), we can exploit this common structure in deep learning models and merge the truncation with the following non-linear operations to be simply computed together in plaintext inside the trusted LTH.

The protocol  $\Pi_{MatMulReLU}$ , detailed in Protocol 4, demonstrates how ReLU can be combined with truncation after matrix multiplication. The steps for a semi-honest setting are colored black, with additional steps for a malicious adversary marked blue. We use this notation in other protocols as well.  $\Pi_{MatMulReLU}$  reduces the total communication rounds of matrix multiplication and ReLU combined to 2 from at least 3, by merging the transmission needed for truncation and sharing shares masked by psuedorandom masks generated by LTHs in step 2) and 3). The malicious version generally adds replicate parallel operations and requires replicate sharing of the same values to validate the integrity. Parties compare the copies of intermediate results and final outputs from different sources to achieve malicious security with abort. We also use  $\Pi_{mal-arith-mult}$  of [58] to ensure correct 2-out-of-3 shares after local multiplication.

One may notice that the workload is not balanced among the three parties if we fix i. In the protocol, the party index i can be any of  $\{1, 2, 3\}$ , which means that the three parties can start the protocol simultaneously with a disjoint dataset. Therefore, when provided with a batch B of inputs for evaluation, each party can work on the B/3 data and start the corresponding protocol simultaneously, balancing resource usage and reducing overall latency.

## 4.3 Extensions to Other Operations

$\Pi_{ReLU}$  can be extended to  $\Pi_{MaxPooling}, \Pi_{BatchNorm}, \Pi_{LayerNorm}$  that are common non-linear operations needed in deep learning networks.  $\Pi_{MaxPooling}$  needs comparisons and multiplexing.  $\Pi_{BatchNorm}$  need about two and  $\Pi_{LayerNorm}$  needs about three multiplications for each element on average. Their low complexity allows them to be offloaded to the LTH in a similar way as  $\Pi_{ReLU}$  by changing the exact plaintext function executed inside.  $\Pi_{MatMulReLU}$  can be extended to other operations in a similar way by changing step 5) of it. To optimize neural networks in our experiments, we mainly also use  $\Pi_{MatMulMaxPoolReLU}, \Pi_{MatMulBatchNormReLU}$  which merge the truncation with different joint non-linear layers.

#### 4.4 Softmax

Exponentiation is crucial in modern deep learning models, such as logistic and softmax functions. In this work, we focus on softmax, which is extensively used in modern models such as Transformers [92]. Classical MPC softmax implementations [42, 66] leads to a large overhead due to two main reasons: the complex protocol for

**Protocol 4**  $[\![ReLU(A \times B)]\!]^L \leftarrow \prod_{MatMulReLU} ([\![A]\!]^L, [\![B]\!])$ : Multiply A and B, then output the shares of the ReLU of the results.

- (1) P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub> locally computes [Ĉ]<sup>I</sup><sub>i</sub> = [R]<sup>I</sup><sub>i</sub> × [B]<sup>I</sup><sub>i</sub> + [R]<sup>I</sup><sub>i</sub> × [B]<sup>I</sup><sub>i+1</sub> + [A]<sup>I</sup><sub>i+1</sub> × [B]<sup>I</sup><sub>i+1</sub>.

Malicious: Parties instead perform II<sub>mal-arith-mult</sub> of [58] to ensure that the multiplications (before truncation) were performed faithfully by parties. In the end, the 2-out-of-3 sharing [Ĉ] is distributed.

- (2)  $P_i$  calls  $H_i$  to execute  $\Pi_{\text{LTH.GenMaskShare}}(a \times c, L)$  to obtain the masks  $\llbracket \mathbf{M} \rrbracket_i \in \mathbf{Z}_L^{a \times c}$ , then compute  $\hat{\mathbf{C}}_i' = \llbracket \hat{\mathbf{C}} \rrbracket_i^L + \llbracket \mathbf{M} \rrbracket_i$ .  $P_{i-1}$  also calls  $H_{i-1}$  to perform  $\Pi_{\text{LTH.GenMaskShare}}(a \times c, L)$  to obtain  $\llbracket \mathbf{M} \rrbracket_{i-1} \in \mathbf{Z}_L^{a \times c}$  and  $\hat{\mathbf{C}}_{i-1}' = \llbracket \hat{\mathbf{C}} \rrbracket_{i-1}^L + \llbracket \mathbf{M} \rrbracket_{i-1}$ .  $\underbrace{Malicious}_{\text{Instead of doing the semi-honest protocol}, P_{i+1}, P_{i-1} \text{ generates } \llbracket \mathbf{M} \rrbracket_{i+1} \leftarrow \Pi_{\text{LTH.GenMask}}(a \times c, L, i+1) \text{ and } \hat{\mathbf{C}}_{i+1}' = \llbracket \hat{\mathbf{C}}' \rrbracket_{i+1}^L + \llbracket \mathbf{M} \rrbracket_{i+1}. P_{i-1}, P_i \text{ also generates } \llbracket \mathbf{M} \rrbracket_{i-1} \text{ invoking } \Pi'_{\text{LTH.GenMask}}(a \times c, L, i-1), \hat{\mathbf{C}}_{i-1}' = \llbracket \hat{\mathbf{C}}' \rrbracket_{i-1}^L + \llbracket \mathbf{M} \rrbracket_{i-1}.$

- (3)  $P_i$  and  $P_{i-1}$  send  $\hat{\mathbf{C}}'_i$  and  $\hat{\mathbf{C}}'_{i-1}$  to  $P_{i+1}$ .

Malicious: Instead of doing the semi-honest protocol,  $P_{i+1}, P_{i-1}$  send  $\hat{\mathbf{C}}'_{i+1}$  to  $P_i; P_{i-1}, P_i$  send  $\mathbf{C}'_{i-1}$  to  $P_{i+1}$ .

- (4)  $P_{i+1}$  computes  $\hat{\mathbf{C}}' = \hat{\mathbf{C}}'_i + \hat{\mathbf{C}}'_{i-1} + [\![\hat{\mathbf{C}}']\!]_{i+1}^L$  and passes it to  $H_{i+1}$ .  $\underline{\underline{Malicious}}_{i}$  Instead of doing the semi-honest protocol,  $P_i$ ,  $P_{i+1}$  compare the two received copies and abort if inconsistency is found.  $P_i$  computes  $\hat{\mathbf{C}}' = \hat{\mathbf{C}}'_{i+1} + [\![\hat{\mathbf{C}}]\!]_{i-1}^L + [\![\hat{\mathbf{C}}]\!]_i^L \text{ and passes it to } H_i, P_{i+1} \text{ computes } \hat{\mathbf{C}}' = \hat{\mathbf{C}}'_{i-1} + [\![\hat{\mathbf{C}}]\!]_{i+1}^L \text{ and passes it to } H_{i+1}.$

- (5) **LTH Only** :  $H_{i+1}$  generates the masks  $[\![M]\!]_{i+1}$  by invoking  $\Pi_{\mathsf{LTH.GenMaskShare}}(a \times c, L)$  and recovers the plaintext through truncation:  $\hat{\mathbb{C}} = \lfloor (\hat{\mathbb{C}}' + [\![M]\!]_{i+1}) \rfloor \gg \mathsf{fp}$ . Note that  $[\![M]\!]_{i+1} + [\![M]\!]_{i} + [\![M]\!]_{i-1} = 0$ . Set  $\mathbf{D} = (\hat{\mathbb{C}} > \mathbf{0})$ . Then  $H_{i+1}$  invokes  $\Pi_{\mathsf{LTH.GenMaskShare}}(a \times c, L)$  to get  $[\![Z^*]\!]_i^L \in \mathbb{Z}_L^{a \times c}$ ,  $[\![Z^*]\!]_{i+1}^L \in \mathbb{Z}_L^{a \times c}$ , and compute:  $([\![Z_{j,k}]\!]_i^L, [\![Z_{j,k}]\!]_{i+1}^L) = ((D_{j,k}?C_{j,k}:0) + [\![Z^*]\!]_{j,k}^L, [\![Z_{j,k}]\!]_{i+1}^L)$ . Return them to  $P_{i+1}$ .  $P_i$  and  $P_{i-1}$  call  $H_i$  and  $H_{i-1}$  to invoke  $\Pi_{\mathsf{LTH.GenMaskShare}}(a \times c, L)$  to get  $[\![Z]\!]_{i-1}^L \in \mathbb{Z}_L^{a \times c}$ . Malicious: Instead,  $H_{i+1}$  generates masks with  $\Pi_{\mathsf{LTH.GenMask}}(a \times c, L, i 1)$  to recover the plaintext  $\hat{\mathbb{C}} = \lfloor (\hat{\mathbb{C}}' [\![M]\!]_{i-1}) \rfloor \gg \mathsf{fp}$ , with the remaining being the same.  $H_i$  does as above respectively with index i replacing index i+1, replacing  $\Pi_{\mathsf{LTH.GenMask}}$  with  $\Pi'_{\mathsf{LTH.GenMask}}$ , and fixes that the plaintext results are added to mask share i.  $\Pi_{\mathsf{LTH.GenMaskShare}}(a \times c, L)$  is invoked at last to generate the shares.  $H_{i-1}$  also generates the remaining share for  $P_{i-1}$ .

- (6)  $P_{i+1}$  send  $[\![\mathbf{Z}]\!]_i^L$ ,  $[\![\mathbf{D}]\!]_i^L$  to  $P_i$ , send  $[\![\mathbf{Z}]\!]_{i+1}^L$ ,  $[\![\mathbf{D}]\!]_{i+1}^L$  to  $P_{i-1}$ . Now,  $[\![\mathbf{Z}]\!]_i^L$  and  $[\![\mathbf{D}]\!]_i^L$  are calculated and shared with each party.  $\underline{Malicious}$ :  $P_i$  shares  $[\![\mathbf{Z}]\!]_{i-1}^L$ ,  $[\![\![\mathbf{D}]\!]_{i-1}^L$  and  $[\![\mathbf{Z}]\!]_i^L$ ,  $[\![\![\!\mathbf{D}]\!]_i^L$  to  $P_{i-1}$  and  $P_{i+1}$  respectively. Each party checks the results from the two parallel computations and aborts if an inconsistency is found.

approximating exponentiation and the max function applied before softmax. A recent study [91] shows that softmax is the main source of overhead when running a Transformer network with an MPC protocol and also introduces a numerical stability problem.

The Softmax on a vector  $\mathbf{x}$  is defined as follows:

$$Softmax(\mathbf{x}) := \exp(\mathbf{x}) / \sum_{i=1}^{n} \exp(\mathbf{x}_i)$$

(1)

In a regular ML setting, exponentiation can easily lead to overflow, a problem exacerbated in fixed-point representations used by MPC protocols. The traditional solution is to subtract the maximum value of the input vector  $\mathbf{x}$  from every element before applying the softmax function, ensuring the maximum input value is 0 and preventing overflow. However, this additional max operation introduces significant MPC overhead as shown in a recent study [91].

A naïve extension of the previous protocol for exp would be to move exp to the LTH, similar to the other non-linear operations in  $\Pi_{\text{ReLU}}$ . This would not work due to the low computational power of the LTH and the large amount of computation required for exp compared to other operations. Under our assumption on the trusted hardware (details in §5), tests show that 1 million 32-bit multiplications take less than a second, while double-precision exponentiation takes over a minute. Unlike simple non-linear operations, exp needs to be done with floating point arithmetic for high precision, involving tens of multiplications per exp and creating significant overhead and a new bottleneck for our scheme on a small LTH.

Our solution is to split and "offload" the computation to the untrusted local machine. The most complex part of the exp operation is performed by the powerful but untrusted CPU/GPU, and then the

results are assembled within the LTH. The protocol is based on the property  $\exp(a+b+c)=\exp(a)\exp(b)\exp(c)$ , allowing untrusted machines to compute exp on individual shares so that only simple multiplications are needed on LTH. However, the conversion between fixed-point representations and real-number arithmetic is non-trivial under MPC. In Protocol 5, we expand the exponent part (see §3.1) to contain all possible results of  $\exp([\![x]\!]_i^L)$ , specifically for  $L=2^{32}$ . Overflow would not occur after this adjustment, even without invoking the max function before Softmax.

## 4.5 Integrating STAMP into Real Systems

A full implementation of STAMP requires four main functions to be performed by LTH: attestation during the initialization phase, pseudorandom number generation for masking, communication between LTH and a host CPU, and the rest of the protocol mainly for in-LTH computation. From the functionality point of view, all these operations can be implemented in software on any security processor if it is equipped with a unique device secret key in hardware that can be used for attestation. Fortunately, most security hardware today supports attestation and meets this requirement. From the performance point of view, our prototype and experimental evaluation assume that LTH has hardware AES engines for pseudorandom number generation to match the LTH-CPU communication bandwidth, while assuming that all other LTH operations are performed in software. More specifically, the performance evaluation is based on software run-time on a tiny microcontroller (Arduino Due) with an ARM Cortext-M3 that is also used in TPM, which represents today's low-end security processor.

## **Protocol 5** $\Pi_{Softmax}(\mathbf{x})$ compute softmax

**Input.**  $\{P_i\}$  have replicative shares of  $\mathbf{x} \in \mathbb{Z}_L^n$ .

Output.  $\{P_i\}$  get  $[\exp(\mathbf{x})]^L$

**Initial values.** The LTHs save  $(q_L, m_L)$  for later use, setting  $(m_L \gg 52) = \lfloor \overline{\exp(L \gg \mathrm{fp}) \cdot 2^{-q_L}} \rfloor$  with  $\mathrm{fp} = 13$  is the fixed-point precision under  $L = 2^{32}$ , where we save  $q_L \in \mathbb{Z}_{2^{32}}$ ,  $m_L \in \mathbb{Z}_{2^{52}}$ , so  $(m_L \gg 52) \in [0, 1)$  and  $q_L$  will not overflow. We note  $\bar{\mathbf{x}}$  to be the real values that  $\mathbf{x}$  represents.

- (1) For each  $\llbracket x_j \rrbracket^L$ ,  $P_i$  computes  $\bar{r} = \overline{\exp(\llbracket x_j \rrbracket_{i-1}^L \gg \mathrm{fp})}$ . Let  $\bar{r} = \overline{\exp(\llbracket x_j \rrbracket_{i-1}^L \gg \mathrm{fp})} = 2^{q_j} \cdot (m_j \gg 52)$  where  $m_j$  has no sign, since it is always positive. (Notice that  $|q_j| = |\lfloor \log_2(\exp(\llbracket x_j \rrbracket_{i-1}^L \gg \mathrm{fp})) \rfloor| = \lfloor \lceil \llbracket x_j \rrbracket_{i-1}^L \gg \mathrm{fp} \rceil \cdot \log_2(e) \rfloor \rfloor < 2^{30}$ , so 32 bits are enough to store  $q_j$  and support additions without overflow). Invoke  $\Pi_{\mathsf{LTH.GenMask}}$  from  $H_i$  to generate two masks  $\alpha_j \in \mathbb{Z}_{2^{52}}$  and  $\beta_j \in \mathbb{Z}_{2^{32}}$  for j = 1, ..., n with the corresponding dimensions, and send  $\{m_j^* = (m_j + \alpha_j)_{2^{52}}, q_j^* = (q_j + \beta_j)_{2^{32}}\}$  for i = 1, ..., n to  $P_{i+1}$ .

- <u>Malicious</u>:  $P_{i-1}$  follows the same computation to get  $\{m_j^*, q_j^*\}$  to  $P_{i+1}$ .  $P_{i+1}$  additionally compute  $\bar{r} = \overline{\exp([x_j]_{i+1}^L \gg fp)}$  and obtain  $\{'m_j^*, q_j^*\}$  by masking the mantissa and exponent part with masks from  $\Pi'_{\mathsf{LTH.GenMask}}$ , send them to  $P_i$ .

- (2) P<sub>i+1</sub> receives {q<sub>j</sub><sup>\*</sup>, m<sub>j</sub><sup>\*</sup>} and computes 2<sup>q̂j</sup> · m̂<sub>j</sub> := exp(([x<sub>j</sub>]]<sub>i+1</sub><sup>L</sup> + [x<sub>j</sub>]]<sub>i</sub><sup>L</sup>)<sub>L</sub> ≫ fp). Send {q\* + q̂, m\*, m̂} to H<sub>i+1</sub>.

<u>Malicious:</u> P<sub>i+1</sub> and P<sub>i</sub> compare the two received copies and abort if an inconsistency is found. P<sub>i</sub> do the same computation as above with index i replacing index i − 1, and send the obtained {'q\* + 'q̂, m\*, m̂} to H<sub>i</sub>.

- (3) LTH Only:  $H_{i+1}$  Generate  $\alpha_j$  and  $\beta_j$ , Compute  $q'_j = (q^*_j + \hat{q}_j) \beta_j = q_j + \hat{q}_j$ ,  $m'_j = (m^*_j \alpha_j) \cdot \hat{m}_j = m_j \cdot \hat{m}_j$ . Define the results  $2^{\hat{q}'_j} \cdot m'_j := \exp(\|x_j\|_L^L \gg \text{fp}) \cdot \exp((\|x_j\|_{l-1}^L + \|x_j\|_{l+1}^L)_L \gg \text{fp}) = \exp(((\|x_j\|_{l-1}^L + \|x_j\|_{l+1}^L)_L + \|x_j\|_{l+1}^L) + \|x_j\|_{l+1}^L) + \|x_j\|_{l+1}^L + \|x_j\|_{l+1$

- (b) If  $q'_j \in (qb, 3 * qb]$ , we are missing one  $\exp(-L \gg fp)$  to be multiplied for either reason mentioned above. Compute  $q''_j = q'_j q_L$ ,  $m''_j = (m^*_j \alpha_j) \cdot \hat{m}_j / m_L$ .

- (c) If  $q_j' \in (3 * qb, 5 * qb]$ , we are missing  $\exp(-2L \gg fp)$  to be multiplied for both reasons. Compute  $q_j'' = q_j' 2 * q_L, m_j'' = (m_j^* \alpha_j) \cdot \hat{m}_j/(m_L)^2$ . Now  $H_{i+1}$  obtains the corrected  $\exp(\bar{x}_j) = 2^{q_j''}(m_j'' \gg 52)$ .  $H_{i+1}$ .

- •Then compute softmax of the real values directly by Softmax( $\bar{\mathbf{x}}$ ) =  $\exp(\bar{\mathbf{x}})/\sum(\exp(\bar{\mathbf{x}}))$  which involves only O(n) additions, O(1) multiplications and divisions. Then convert the results to fixed-point representations, and invoke  $\Pi_{\mathsf{LTH.GenMaskShare}}$  for masks  $[\![\mathbf{m}]\!]_{i+1}^L$ ,  $[\![\mathbf{m}]\!]_i^L$  to output  $([\![\mathbf{y}]\!]_i^L, [\![\mathbf{y}]\!]_{i+1}^L)$  = (Softmax( $\mathbf{x}$ ) +  $[\![\mathbf{m}]\!]_i^L$ ,  $[\![\mathbf{m}]\!]_{i+1}^L$ ) to  $P_{i+1}$ .  $P_i$  and  $P_{i-1}$  call  $H_i$  and  $H_{i-1}$  to generate  $[\![\mathbf{m}]\!]_i^L = \Pi_{\mathsf{LTH.GenMaskShare}}(n)$  as  $[\![\mathbf{y}]\!]_{i-1}^L$ .

- Malicious:  $H_i$  does the computation accordingly, while allow masking the results with the index masks i.  $P_{i-1}$  calls  $H_{i-1}$  to generate  $(\llbracket \mathbf{m} \rrbracket_{i+1}^L, \llbracket \mathbf{m} \rrbracket_{i-1}^L) = \prod_{\mathsf{LTH.GenMaskShare}}(n, L)$  as  $(\llbracket \mathbf{y} \rrbracket_{i+1}^L, \llbracket \mathbf{y} \rrbracket_{i-1}^L)$ .

- (4) P<sub>i+1</sub> shares [y]<sup>L</sup><sub>i</sub> with P<sub>i</sub> and [y]<sup>L</sup><sub>i+1</sub> with P<sub>i-1</sub>

Malicious: P<sub>i</sub> shares [y]<sup>L</sup><sub>i-1</sub> to P<sub>i-1</sub> and [y]<sup>L</sup><sub>i</sub> to P<sub>i+1</sub> respectively. Each party checks the results of the two parallel computations and aborts if an inconsistency is found.

Consider Apple's Secure Enclave [31] as another example, which already includes a dedicated nonvolatile storage and a unique ID root (UID) cryptographic key to protect device-specific secrets for remote attestation, . It also includes a true random number generator (TRNG), an AES engine that may be used for pseudo-random number generation, a general-purpose CPU (Secure Enclave Processor), and a communication channel with the main CPU. While Apple does not disclose the throughput of the AES engine or the performance of the Secure Enclave Processor, they are likely sufficient for STAMP, as the AES engine is designed to encrypt NAND flash storage, and the processor runs at a high SoC clock frequency. Other SoC security subsystems, such as the Synopsys tRoot hardware security module [80], the Rambus RT-630 programmable root-of-trust (RoT) [35], and the Qualcomm secure processing unit [34] also support comparable hardware features, including a device-specific secret key, a hardware AES engine, and a general-purpose processor. Thus, we believe that STAMP can be realized on today's lightweight security hardware with minimal changes.

STAMP is designed to be used even with a tiny low-performance security processor, but it can also run on a high-performance TEE such as Intel SGX and AMD SEV implemented in software inside. Although performance should be better than the low-end LTH implementation, we believe that LTH can provide stronger security protection compared to the traditional TEEs (see §3.3).

## 5 EVALUATION

## 5.1 Experimental Setup

Implementation and baselines. We implemented STAMP in C++, building on Falcon [89]. We introduced new protocols, GPU support for linear layers, and we switched to ZeroMQ for networking. Falcon is the main framework we compare to, but the open-source project was not implemented to support GPUs and does not address a key protocol for Transformers: Softmax. Falcon+ introduces three main improvements: (1) GPU support for linear layers, (2) a new MPC protocol for  $\Pi_{\text{Softmax}}$  using the exponentiation protocol from [42] combined with Falcon's  $\Pi_{\text{Div}}$  and  $\Pi_{\text{Max}}$ , and (3) ZeroMQ for

networking to ensure better performance and a fair comparison with STAMP. These changes do not alter the threat model.

We also compare our scheme with AriaNN [71] and CryptGPU [81] as additional pure MPC baselines. Appendix D compares the theoretical complexities for Falcon+, AriaNN, and STAMP. AriaNN and CryptGPU show both advantages and disadvantages relative to Falcon in different settings prior to our optimizations. We discover in our experiment that AriaNN and CryptGPU consume a significant amount of memory: a server with 64GB DRAM can only process ResNet18 inference with a batch size of 8 using AriaNN, whereas 32GB suffices for a batch size of 128 with STAMP. Similarly, CryptGPU supports batch sizes of up to 8 for ResNet and 32 for VGG16. We adjusted batch sizes accordingly for these experiments, noting results with smaller batch sizes explicitly. Additionally, we compare STAMP with two high-performance TEE-based schemes: a full SGX solution, running entire inferences inside an SGX enclave; and Goten [61], which accelerates TEE-based private inference by offloading linear operations to untrusted GPUs using a secret multiplication protocol with Beaver triples. Both CryptGPU and Goten support only a semi-honest GPU setting.

Hardware and network. We conducted our experiments on Cloudlab c240g5 machines with Ubuntu 20.04 LTS, equipped with an Intel Xeon Silver 4114 10-core CPU (2.20 GHz) and an NVIDIA 12GB P100 GPU. The network setup mirrors previous studies [59, 71, 88, 89], with a LAN bandwidth of 625 MBps and a ping time of 0.2 ms, and a WAN bandwidth of 40 MBps and a ping time of 70 ms. Both semi-honest and malicious settings were tested. For the LTH-chip, we used an Arduino Due with an Atmel SAM3X8E ARM Cortex-M3 CPU (84MHz, 512 KB of Flash, and up to 96 KB of SRAM), which is used for a commercial implementation of TPM [78], to evaluate the LTH runtime. The LTH assumes a low-pin-count (LPC) bus, resulting in a 15MBps bandwidth limit. A maximum of 3MBps of random number generation can be achieved in a TPM [79], which is enough for its original use case, but not for our scheme. We assume an additional low-cost hardware AES engine [17] achieving a throughput of 14 GBps, making the LTH's pseudo-random number generation time negligible compared to data transmission time. Other details of the hardware can be seen in §5.4. For the LTH-SoC, we assume the same Cortex-M3 processor running at 1GHz and the 128-bit on-chip network (16GBps). The performance is estimated by scaling the execution time of the discrete LTH. We additionally provide a memory usage analysis of LTH in Appendix E, showing that STAMP can handle most models with our current LTH setting, and can be modified to handle even larger models with increased LTH local communication cost.

Neural networks and dataset. We use 8 neural networks: a small 3-layer fully-connected network with ReLU activations (Network-A, as in SecureML [59]), a small convolutional network with ReLU activation (Network-B, as in [69]), a small convolutional network with ReLU activation and maxpooling (Network-C, as in [49]), AlexNet [44], VGG16 [74], ResNet18 [29], a small Transformer [86] and a small Word2Vec [54]. We use a small Transformer and reduce the size of the last layer in Word2Vec to manage the computational expense of Softmax in pure MPC, especially in a WAN setting. The datasets used are MNIST [16] for the first four networks, CIFAR-10 [43] for AlexNet and VGG16, ImageNet [70] for ResNet18, and Wikitext-2 [53] for the Transformer and Word2Vec.

**Parameter choice.** As mentioned in §4.4, we choose  $L = 2^{32}$  and fp = 13 in our implementation. We pick the group size to be 2048 bits in Diffie–Hellman key exchange and use AES-128 for the pseudo-random number generation.

#### 5.2 Performance

Table 1 and Table 2 show the end-to-end latency (in seconds) of the inference on inputs of batch size 128 in semi-honest and malicious settings, respectively. Table 3 and Table 4 report the amount of data transmitted compared to baselines with traffic analysis tools or the data reported in the papers. '-' in the cells indicates that the implementation is missing or the network is too large for CPU evaluation. The brackets in the tables indicate an altered batch size for the cases when a large batch size did not fit into our machine. Only Falcon implemented its work in a malicious setting.

In the tables, we compare STAMP with Falcon [89], AriaNN [71], and CryptGPU [81], three of the state-of-the-art MPC frameworks implementing different optimizations for non-linear layer inference. AriaNN does not implement the execution of different parties on separate machines, but instead uses the local simulation of the network for performance evaluation. AriaNN does not support Transformer and Word2Vec because it does not support Softmax, and we could not use the open-sourced CryptGPU to run Transformer, because the provided version raised error when generating the secret sharing model due to compatibility issues. Depending on the structure of the machine learning network, STAMP with LTH-chip is  $4 \times$  to  $63 \times$  or  $6 \times$  to  $59 \times$  faster than the state-of-the-art MPC results with semi-honest or malicious settings in WAN / GPU environments. The advantage that we obtain under a LAN or CPU environment is smaller compared to a WAN/GPU environment. In the LAN, communication overhead is significantly reduced. With a CPU, the computation accounts for a larger portion of the execution time. These factors reduce the speedup, which is mainly accomplished by reducing the communication overhead of non-linear functions. STAMP with LTH-SoC achieves even higher speedup because LTH-SoC has higher performance compared to LTH-chip due to its higher clock frequency and the data movement between an LTH and a CPU/GPU is also faster on an SoC. The performance gap between LTH-SoC and LTH-chip is the largest in LAN / GPU environments where the local communication overhead is large. Also, for smaller networks, a GPU can be slower than a CPU. For a small amount of data and a small model, initialization and data movement may take more time than operating directly on a CPU.

We also compare Stamp with other schemes that rely on a high-performance TEE (Intel SGX): the full SGX solution and Goten [61]. The full SGX solution assumes that semi-honest parties can securely share their data with one party's SGX for evaluation. The experiments are run on SGX V1 with 16GB enclave memory on Azure Standard DC4s v3. For smaller networks such as Network-B, the full SGX solution is slightly slower (0.46 seconds) compared to STAMP (0.12), mainly due to initialization overhead. However, for larger networks such as ResNet18, the full SGX solution only takes 8.15 seconds, while STAMP (LTH-SoC) takes 148 seconds. This result is expected as the performance overhead of MPC-based secure computation is known to be substantially higher compared to the

Table 1: Inference time (s) of the entire batch of size 128 in a semi-honest setting. AriaNN has a reduced batch size of 64 and 8 for VGG16 and ResNet18 due to memory consumption, which also applies to other tables. Brackets indicate an altered batch size.

|            |           | ork-A         |               | Netw          | ork-B    |               | Network-C     |               |             |               |               |                |

|------------|-----------|---------------|---------------|---------------|----------|---------------|---------------|---------------|-------------|---------------|---------------|----------------|

|            | LAN       | LAN           | WAN           | WAN           | LAN      | LAN           | WAN           | WAN           | LAN         | LAN           | WAN           | WAN            |

| Framework  | GPU       | CPU           | GPU           | CPU           | GPU      | CPU           | GPU           | CPU           | GPU         | CPU           | GPU           | CPU            |

| Falcon+    | 0.082     | 0.112         | 1.478         | 1.393         | 0.203    | 0.2618        | 1.464         | 1.292         | 1.866       | 2.191         | 7.321         | 7.288          |

| AriaNN     | 0.256     | 0.512         | -             | 5.504         | -        | -             | -             | -             | 3.072       | 5.248         | -             | 17.02          |

| CryptGPU   | 0.449     | -             | 13.49         | -             | 0.333    | -             | 9.592         | -             | 0.752       | -             | 19.45         | -              |

| STAMP-chip | 0.073     | 0.077         | 0.251         | 0.294         | 0.117    | 0.114         | 0.278         | 0.293         | 0.680       | 1.298         | 1.024         | 1.494          |

| speed-up   | 1.11×     | 1.43×         | 5.87×         | $4.72 \times$ | 1.73×    | $2.29 \times$ | 5.25×         | 4.39×         | 1.10×       | 1.68×         | $7.14 \times$ | $4.87 \times$  |

| STAMP-SoC  | 0.0432    | 0.0472        | 0.2211        | 0.2641        | 0.0643   | 0.0613        | 0.1994        | 0.2408        | 0.1990      | 0.8163        | 0.5424        | 1.012          |

| speed-up   | 1.91×     | $2.37 \times$ | 6.69×         | $5.28 \times$ | 3.17×    | $4.28 \times$ | $7.34 \times$ | $5.37 \times$ | 3.78×       | $3.10 \times$ | 13.5×         | $7.20 \times$  |

| Goten      | 0.261     | -             | 3.304         | -             | 0.376    | -             | 4.097         | -             | 0.602       | -             | 5.589         | -              |

| Full SGX   |           | 0.4           | 462           |               |          | 0.            | 461           |               |             | 0.4           | 461           |                |

|            |           | Le            | Net           |               |          | Ale           | xNet          |               | Transformer |               |               |                |

|            | LAN       | LAN           | WAN           | WAN           | LAN      | LAN           | WAN           | WAN           | LAN         | LAN           | WAN           | WAN            |

| Framework  | GPU       | CPU           | GPU           | CPU           | GPU      | CPU           | GPU           | CPU           | GPU         | CPU           | GPU           | CPU            |

| Falcon+    | 2.592     | 4.603         | 8.867         | 9.563         | 4.276    | 11.78         | 38.56         | 43.06         | 4.026       | 16.20         | 321.0         | 334.7          |

| AriaNN     | 4.480     | 7.040         | -             | 18.30         | 9.984    | 19.20         | -             | 43.52         | -           | -             | -             | -              |

| CryptGPU   | 1.337     | -             | 19.12         | -             | 1.918    | -             | 35.90         | -             | -           | -             | -             | -              |

| Sтамр-chip | 0.969     | 3.075         | 1.315         | 3.255         | 1.564    | 9.263         | 2.463         | 9.449         | 0.5130      | 12.18         | 5.024         | 16.66          |

| speed-up   | 1.38×     | $1.49 \times$ | 6.74×         | $2.93 \times$ | 1.22×    | $1.27 \times$ | 14.6×         | $4.55 \times$ | 7.84×       | 1.32×         | 63.8×         | $20.08 \times$ |

| Stamp-SoC  | 0.2869    | 2.392         | 0.6328        | 2.573         | 0.305    | 8.029         | 1.229         | 8.215         | 0.3618      | 12.03         | 4.873         | 16.51          |

| speed-up   | 4.66×     | $2.02 \times$ | 6.27×         | $3.72 \times$ | 14.0×    | 1.52×         | 29.2×         | 5.24×         | 11.1×       | $1.34 \times$ | 65.8×         | $20.26 \times$ |

| Goten      | 0.944     | -             | 6.233         | -             | 0.778    | -             | 9.127         | -             | -           | -             | -             | -              |

| Full SGX   |           | 0             | 507           |               | 5.031    |               |               |               | 0.563       |               |               |                |

|            |           | VG            | G16           |               | ResNet18 |               |               |               | Word2Vec    |               |               |                |

|            | LAN       | LAN           | WAN           | WAN           | LAN      | LAN           | WAN           | WAN           | LAN         | LAN           | WAN           | WAN            |

| Framework  | GPU       | CPU           | GPU           | CPU           | GPU      | CPU           | GPU           | CPU           | GPU         | CPU           | GPU           | CPU            |

| Falcon+    | 49.36     | -             | 122.1         | -             | 545.9    | -             | 1439          |               | 1.631       | 8.687         | 81.93         | 90.82          |

| AriaNN     | 198.4     | -             | -             | -             | 1779(8)  | -             | -             | -             | -           | -             | -             | -              |

| CryptGPU   | 11.31(32) | -             | 55.43(32)     | -             | 45.20(8) | -             | 600.3(8)      | -             | 1.469       | -             | 47.19         | -              |

| Sтамр-chip | 26.55     | -             | 30.05         | -             | 309.7    | -             | 350.7         | -             | 0.628       | 7.556         | 1.727         | 8.869          |

| speed-up   | 1.85×     | -             | $4.06 \times$ | -             | 1.76×    | -             | $4.10 \times$ | -             | 2.33×       | $1.14 \times$ | $47.4 \times$ | $10.2 \times$  |

| STAMP-SoC  | 13.06     | -             | 16.56         | -             | 106.9    | -             | 148.0         | -             | 0.593       | 7.521         | 1.692         | 8.835          |

| speed-up   | 3.78×     | -             | 7.37×         | -             | 5.10×    | -             | 9.72×         | -             | 2.74×       | 1.15×         | 27.32×        | 10.2×          |

| Goten      | 6.208     | -             | 25.71         | -             | -        | -             | -             | -             | -           | -             | -             | -              |

| Full SGX   |           | 32.           | .422          |               |          | 8.            | 156           |               |             | 2.            | 23            |                |

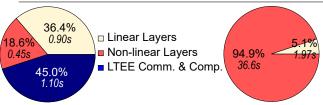

Figure 4: The breakdown of local machine execution time: linear layers, non-linear layers, and LTH-Chip bus communication & computation time. STAMP (left) and Falcon+ (right) on semi-honest inference over AlexNet under WAN/GPU.

performance overhead of a TEE. On the other hand, MPC is generally considered to be more secure compared to a high-performance TEE such as Intel SGX. As discussed in §3.3, we believe that LTH is easier to protect and deploy compared to high-performance TEEs.

When compared to Goten, which also relies on MPC for secure outsourcing of linear layers, the experimental results suggest that STAMP is faster in most cases even though LTH has much lower performance compared to Intel SGX. Goten is relatively slow for small networks, again partialy due to the SGX initialization overhead. For VGG16, Goten outperforms STAMP with a discrete security chip (LTH-chip), mainly due to the large performance gap between the

low-end LTH and a high-performance TEE (SGX) used by Goten. However, Stamp outperforms Goten in the WAN/GPU setting when running on a more powerful LTH (LTH-SoC), which has high local communication bandwidth and runs at a higher clock frequency. These results confirm the main intuition behind the Stamp design, that small high-security hardware can be sufficient when primarily used to perform non-linear operations.

In Figure 4, we show the time breakdown of semi-honest inference over AlexNet in the WAN / GPU setting. In both Stamp and Falcon+, linear layers take a similar amount of time. However, they contribute only 5.1% of the execution time in Falcon+, and over 36% in Stamp, because the non-linear layers' runtime is significantly reduced from about 94.9% to 18.6% (63.6% if we roughly consider all operations on LTH are related to non-linear layers. There is some overhead, such as the local transmission in step 4 of Protocol 4, which cannot be assigned to be only linear or non-linear operations). Table 5 shows another breakdown of the execution time in the WAN/GPU setting: CPU/GPU, communication, and LTH. Note

<sup>&</sup>lt;sup>1</sup>We believe Stamp outperforms in this case because Goten requires more communication for its secure multiplication. As the communication cost analysis for Goten is not available, we estimate the costs using analytical results in their paper (Table 1); and as an example, Goten's communication for VGG16 is estimated to be 273MB compared to Stamp's 188 MB.

STAMP-SoC

speed-up

20.06

6.82×

36.62

11.1×

Network-B Network-C Network-A WAN WAN WAN WAN WAN LAN LAN LAN LAN LAN LAN WAN **GPU CPU GPU GPU** CPU GPU CPU **GPU** CPU Framework CPU GPU CPU Falcon+ 0.1921 0.3293 3 3 5 9 3 3701 0.6279 0.6416 3 504 3.0743 5.639 6.758 23.26 20.8988 Sтамр-chip 0.0913 0.2567 0.5150 0.7307 0.1594 0.2860 0.5803 0.7246 1.157 3.661 2.196 4.258 speed-up  $2.10 \times$ 1.51× 6.52×  $4.61 \times$ 3.94×  $2.82 \times$ 6.04×  $4.24 \times$ 4.87×  $2.12 \times$ 10.6× 4.91× STAMP-SoC 0.0200 0.1854 0.6594 0.0357 0.4566 0.6010 0.0325 0.44370.1623 2.536 1.071 3.134 speed-up 17.5× 9.59×  $2.09 \times$ 7.57× 4.98× 173× 21.7× 5.11×  $7.67 \times$  $5.12 \times$ 3.06×  $6.67 \times$ AlexNet Transformer LeNet LAN LAN WAN WAN LAN LAN WAN WAN LAN LAN WAN WAN Framework **GPU** CPU **GPU** CPU **GPU** CPU **GPU** CPU GPU CPU GPU CPU 10.99 Falcon+ 7.492 15.38 28.82 32.57 13.89 41.88 100.9 123.2 56.10 777.9 821.3 STAMP-chip 2.106 10.64 2.929 10.80 3.653 36.80 5.538 36.10 2.073 47.37 13.03 59.30 speed-up  $3.56 \times$  $1.55 \times$  $9.84 \times$  $3.01 \times$  $3.80 \times$  $1.27 \times$ 18.2×  $3.41 \times$ 5.30×  $59.6 \times$ STAMP-SoC 47.02 58.95 0.5136 9.052 1 337 9.213 0.7738 33 92 2.659 33 22 1 720 12.68 speed-up 14.5× 1.82× 21.5×  $3.54 \times$ 17.9×  $1.37 \times$ 37.9×  $3.71 \times$ 6.39× 1.19× 61.3× 13.9× Word2Vec VGG16 ResNet18 LAN LAN WAN WAN LAN LAN WAN WAN LAN LAN WAN WAN CPU Framework GPU CPU **GPU** CPU GPU CPU GPU CPU **GPU** CPU GPU Falcon+ 136.9 407.8 1550 4993 3 985 32.80 202.5 231.2 Sтамр-chip 51.54 68.09 639.3 772.2 1.327 30.44 2.209 31.44 speed-up  $2.66 \times$ 5.99×  $2.43 \times$  $6.47 \times$  $3.00 \times$  $1.08 \times$ 91.6×  $7.35 \times$

Table 2: Latency (s) of running the entire batch of size 128 in a malicious setting.

Table 3: Communication (MB) for the entire batch of size 128 in a semi-honest setting. Brackets indicate an altered batch size.

299.1

16.6×

1.258

$3.17 \times$

30.37

1.08×

2.140

94.6×

31.37

$7.37 \times$

166.2

9.33×

| Fram     | ework       | Network-A | Network-B | Network-C | LeNet | AlexNet | Transformer | VGG16    | ResNet18 | Word2Vec |

|----------|-------------|-----------|-----------|-----------|-------|---------|-------------|----------|----------|----------|

| Falcon+  | Inter-party | 1.536     | 6.272     | 64.87     | 95.33 | 173.5   | 72.21       | 1730     | 22933    | 12.61    |

| AriaNN   | Inter-party | 2.816     | -         | 38.54     | 55.04 | 121.6   | -           | 1161     | 18944    | -        |

| CryptGPU | Inter-party | 3.012     | 9.911     | 33.35     | 122.7 | 99.05   | -           | 1714(32) | 2729(8)  | 95.46    |

| STAMP    | Inter-party | 0.2058    | 0.8371    | 5.328     | 7.931 | 12.31   | 19.21       | 187.7    | 2106     | 0.4624   |

| JIAMP -  | LTH-CPU     | 0.4585    | 0.7958    | 7.235     | 10.24 | 18.53   | 2.270       | 202.5    | 3044     | 0.412    |

Table 4: Inference communication (MB) of the entire batch of size 128 in a malicious setting.

| Framework |             | Network-A | Network-B | Network-C | LeNet | AlexNet | Transformer | VGG16 | ResNet18 | Word2Vec |

|-----------|-------------|-----------|-----------|-----------|-------|---------|-------------|-------|----------|----------|

| Falcon+   | Inter-party | 10.51     | 41.33     | 423.4     | 620.1 | 1135    | 340.0       | 11543 | 139287   | 99.49    |

| Cmaarn    | Inter-party | 0.8443    | 2.0704    | 21.02     | 28.80 | 48.68   | 131.2       | 838.6 | 7500     | 25.08    |

| Stamp -   | LTH-CPU     | 1.070     | 1.856     | 16.88     | 23.90 | 43.23   | 5.296       | 472.5 | 7103     | 0.826    |

Table 5: Inference time (s) breakdown of a batch of size 128 in a semi-honest WAN/GPU setting, comparing with Falcon+.

| Framework Component |         |      |       |      |       |      |       |      |       |      |       |      | former |      |       |      |       |      |       |

|---------------------|---------|------|-------|------|-------|------|-------|------|-------|------|-------|------|--------|------|-------|------|-------|------|-------|

|                     |         | Time | Ratio  | Time | Ratio | Time | Ratio | Time | Ratio |

|                     | CPU/GPU | 0.04 | 17%   | 0.06 | 23%   | 0.19 | 19%   | 0.28 | 21%   | 0.29 | 12%   | 0.30 | 6%     | 12.8 | 43%   | 98.0 | 28%   | 0.47 | 27%   |

| Stamp               | Comm.   | 0.18 | 70%   | 0.16 | 58%   | 0.35 | 34%   | 0.35 | 27%   | 0.94 | 38%   | 4.56 | 91%    | 3.34 | 11%   | 44.0 | 13%   | 1.22 | 71%   |

|                     | LTH     | 0.03 | 13%   | 0.05 | 19%   | 0.48 | 47%   | 0.68 | 52%   | 1.24 | 50%   | 0.16 | 3%     | 13.8 | 46%   | 207  | 59%   | 0.03 | 2%    |

| Falcon+             | CPU/GPU | 0.08 | 6%    | 0.20 | 14%   | 1.80 | 25%   | 2.50 | 28%   | 4.09 | 11%   | 3.95 | 1%     | 47.6 | 39%   | 523  | 36%   | 1.55 | 2%    |

| raicon+             | Comm.   | 1.40 | 94%   | 1.27 | 86%   | 5.52 | 75%   | 6.37 | 72%   | 34.4 | 89%   | 317  | 99%    | 74.4 | 61%   | 916  | 64%   | 89.3 | 99%   |

that the CPU/GPU execution time is also reduced because major parts of most non-linear computations are moved to LTH.

**Discussion.** The acceleration achieved by Stamp varies significantly with the architectural design of the model. Convolutional neural networks (CNNs), such as AlexNet and VGG16, exhibit less pronounced speed improvements compared to language models like the Transformer and Word2Vec. This discrepancy aligns with the observation that language models employ computationally intensive non-linear operations more frequently, notably Softmax in our case. For instance, the Transformer model applies Softmax within each of its multiple attention heads. Word2Vec, despite its