# Task-based preemptive scheduling on FPGAs leveraging partial reconfiguration

Gabriel Rodriguez-Canal gabriel.rodcanal@ed.ac.uk EPCC at the University of Edinburgh Edinburgh, United Kingdom

Yuri Torres Escuela de Ingeniería Informática Valladolid, Spain

# Abstract

FPGAs are an attractive type of accelerator for all-purpose HPC computing systems due to the possibility of deploying tailored hardware on demand. However, the common tools for programming and operating FPGAs are still complex to use, especially in scenarios where diverse types of tasks should be dynamically executed. In this work we present a programming abstraction with a simple interface that internally leverages High-Level Synthesis, Dynamic Partial Reconfiguration and synchronisation mechanisms to use an FPGA as a multi-tasking server with preemptive scheduling and priority queues. This leads to an improved use of the FPGA resources, allowing the execution of several different kernels concurrently and deploying the most urgent ones as fast as possible.

The results of our experimental study show that our approach incurs only a  $10\pm5\%$  overhead in the worst case when using two reconfigurable regions, whilst providing a significant performance improvement of at least  $24\pm21\%$  over the traditional full reconfiguration approach.

*Keywords:* FPGA; Partial Reconfiguration; Heterogeneous systems; Preemptive scheduling

# 1 Introduction

The end of Moore's law and loss of Dennard's scaling has motivated the search for alternative ways of improving the performance of high-performance computational systems. As a result, heterogeneous systems, primarily composed of CPUs and GPUs have become commonplace in modern High Performance Computing (HPC) machines [2]. However, these architectures are not ideally suited for all codes, and it has been found that when HPC applications are bound by aspects other than compute, for instance memory bound codes, moving to a dataflow style and exploiting the specialisation of FPGAs can be beneficial [7–9]. Nonetheless, FPGAs have not yet been adopted by any of the large supercomputers, which is due to the challenges associated with both their programmability and flexibility. The former has been partially addressed by High Level Synthesis (HLS) tooling, enabling Nick Brown EPCC at the University of Edinburgh Edinburgh, UK

Arturo Gonzalez-Escribano Escuela de Ingeniería Informática Valladolid, Spain

the programmer to write their code in C or C++. However the latter has been less explored. This is because the entire FPGA is often stalled during fabric reconfiguration which means that dynamic scheduling and preemptive execution of workloads is uncommon.

In this paper we propose a programming abstraction to enable the leveraging of an FPGA as a multi-tasking computational resource with preemptive scheduling and priority queues. We utilise both the traditional full reconfiguration mechanism that halts and wipes the entire FPGA, and the Dynamic Partial Reconfiguration (DPR) mechanism, reconfiguring several partial areas of the FPGA independently enabling these to execute different kernels. The work described in this paper hides the complex and low-level details associated with using dynamic partial reconfiguration and synchronisation mechanisms to support on-the-fly instantiation, stopping and resumption of kernels on specific parts of the FPGA fabric whilst the rest of the chip continues executing other workloads independently. In our approach, tasks are programmed as OpenCL kernels and managed with the Controller model [14, 15, 21], which is a heterogeneous programming model implemented as a C99 library of functions. Controller aims to efficiently manage different types of devices with a portable interface and in this paper we describe an extension to support multiple kernels and preemption on dynamic partial reconfiguration capable FPGA systems. Furthermore, the scheduler that we have developed supports First-Come-First-Served (FCFS) preemptive scheduler with priority queues, significantly increasing the flexibility of Controller and how it maps tasks to the FPGA. It should be noted that we largely use the term *task* and *kernel* interchangeably in this paper.

This work extends a previous prototype presented in [20], significantly enhancing the scheduler to provide improved policies and lower overhead due to a simplification of the synchronisation mechanisms. Furthermore, we have also decoupled our two techniques for dynamic partial reconfiguration and kernel interruption/resumption, allowing for preemption when using full FPGA reconfiguration. The rest of the paper is organised as follows: Section 2 describes the background to this work, surveying FPGAs and the Controller task-based model, before exploring related activities which tackle flexible execution of kernels on FPGAs. This is then followed by Section 3 where we present the techniques and extensions that have been developed as part of this work, both on the on-chip FPGA infrastructure side and also on the host side including integration with Controller and development of a FCFS scheduler. Section 4 then describes the programming level abstractions provided to the user to enable convenient FPGA kernel state storage and loading, supporting the preemption of kernels on reconfigurable architectures. Section 5 reports the results of an experimental study where we evaluate our approach, and lastly Section 6 draws conclusions and discusses further work.

The novel contributions of this paper are:

- An approach which provides the ability to undertake low overhead, fine grained, task swapping on an FPGA which delivers the flexibility of task-based models to reconfigurable architectures.

- Support for the preemption of FPGA kernels, where higher priority kernels can interrupt running tasks which will then be restarted, based on their current computed state, at a later time.

- An experimental study to explore the performance properties of using dynamic partial reconfiguration and FPGA kernel preemption.

# 2 Background and related work

#### 2.1 Field Programmable Gate Arrays (FPGAs)

Field Programmable Gate Arrays (FPGAs) are a type of reconfigurable architecture where the electronics of the chip can be configured at runtime to undertake specific activities. This ability to tailor the electronics of the chip to the workload in question is potentially beneficial when compared against more general purpose architectures, such as CPUs or GPUs, for high performance workloads for a number of reasons. Firstly, codes which are memory or microarchitecture bound on general purpose architectures can benefit from this specialisation because the electronics executes the algorithm directly, without black-box layers comprising the general purpose micro-architecture and associated assumptions [7]. Secondly, removing the need to support aspects within the CPU's microarchitecture such as branch prediction, precise exceptions and register renaming, which can add considerable complexity, can result in reduced power draw and the ability to leverage more of the chip for computation. Lastly, it has been observed that FPGAs often deliver good strong scaling performance, especially with smaller local problem sizes due to CPU or GPU having to ramp up the clock frequency which the FPGA does not need to do. [13]

A tradition way of describing FPGAs is as containing large amounts of reconfigurable logic which are sitting within a sea of reconfigurable interconnect. However, whilst this is correct, it oversimplifies the technology because, in addition to the reconfigurable logic provided via Look Up Tables (LUTs), modern FPGAs also contain fast on-chip memories, such as Block RAM (BRAM), and Digital Signal Processing (DSP) slices that can be used to undertake arithmetic operations. FPGAs are configured via a binary bitstream, which will set up the constituent parts of the FPGA as appropriate. These bitstreams are built via a vendor's tooling, and in this paper we focus on AMD Xilinx FPGAs where their Vivado tool is used to design and implement the FPGA logic. Whilst full reconfiguration of the entire FPGA is most common, more recently Dynamic Partial Reconfiguration (DPR) has become possible, where only specific parts of the FPGA are reconfigured whilst other parts of the chip are unaffected and can continue to run independently.

Historically, FPGAs were programmed via esoteric Hardware Description Languages (HDL), such as Verilog and VHDL. However more recently High Level Synthesis (HLS), which enables programmers to write code in C or C++ and for this to be synthesised down to the HDL level, have become more popular. Combined with the very significant investment being made by vendors in their FPGA software ecosystems, writing codes for FPGAs is increasingly becoming much more a question of software development rather than hardware design.

In this paper we undertake our experiments upon a Zynq-7020 FPGA mounted on a Pynq-Z2 board. The Zynq is a popular type of FPGA which combines the CPU (known as the Programmable Subsystem) with the configurable fabric (known as the Programmable Logic). The Zynq-7020 contains a dual-core ARM Cortex-A9 which is running Linux, with the reconfigurable programmable logic partition containing 53,200 LUTs, 4.9 Mb of BlockRAM (BRAM), and 220 DSP slices. The host board contains 512MB of DRAM which is accessible to both the CPU and reconfigurable logic, with the CPU driving the reconfiguration of the FPGA based upon a user's bitstream.

# 2.2 The task-based programming model and Controller

In the task-based programming model programmers decompose their problem into distinct tasks which, apart from consuming inputs and generating outputs, are usually self contained. Tasks become eligible to run when all their inputs have been generated from preceding tasks, and are then scheduled for execution on the most appropriate compute resource. The output(s) of a task will then be used as inputs by subsequent tasks in the overall computation. It has been argued by the community that writing parallel codes which follow the task based model is advantageous for numerous reasons. Firstly the model promotes asynchrony, where decomposing a problem into many small, independent, tasks can significantly reduce the amount of synchronisation that would be imposed by other approaches. Secondly, the scheduling of tasks can often be done in a manner that maps a task to its most appropriate compute resource, for instance to a CPU or GPU, and potentially helps hide the complexities of mixing architectures from the perspective of the programmer. Thirdly, task-based programming can often assist in providing improved levels of resilience, where if a compute resource becomes unavailable then tasks are simply rescheduled elsewhere.

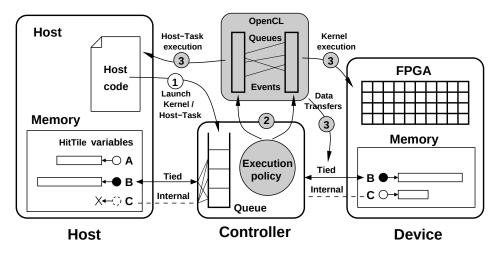

There have been many implementations of the task-based model in HPC programming technologies, including OpenMP tasks [5], OmpSs [10], and StarPU [4]. Controller [14, 15] is another such example and aims to provide a heterogeneous task-based parallel programming model implemented as a C99 library. The framework provides an abstraction for programming using different types of devices, such as sets of CPU-cores, GPUs, and FPGAs. As illustrated in Figure 1, in Controller the model is based around the Controller entity. Each of these is associated with a particular device and manages the execution on, and data-transfers to or from, that device. Programmer's code is executed on the main thread, using the Controller high-level API to enqueue computation tasks for devices. Each Controller entity has its own thread that dequeues and launches the execution of the kernels associated with the tasks.

The Controller runtime resolves data dependencies between tasks, performing data transfers in a manner that is transparent to the end programmer. Requests for kernel execution and data-transfer are stored in three internal queues of the device driver, one controlling the execution order of kernels, one for host-to-device transfer, and one for deviceto-host transfers. This design has been demonstrated to provide fast control operation and an efficient overlapping of computation and data transfers where possible [14]. Portability across architectures is achieved using bespoke runtime backends for different device technologies, such as CUDA or OpenCL, to implement the calls which manage the low-level device queues and events. Furthermore, Controller is agnostic of the language chosen by the programmer for writing their kernel code. Most commonly users leverage OpenCL as this targets the widest range of devices, however more specialised kernels can be written in the native programming models of the accelerator such as CUDA for Nvidia GPUs.

In [21] the authors provided support for Controller to leverage Intel Stratix-10 FPGAs as a target device. However, a major limitation was that full reconfiguration of the entire FPGA was required when mapping a task to the device, meaning that only one kernel could execute on the FPGA at any given time and as such it was common for the compute resource to be significantly under-utilised. The key challenge here was that there was a miss match between the scheduling flexibility commonly provided by task-based models, and the limitations imposed by having to reconfigure the entire FPGA via full reconfiguration.

#### 2.3 Existing task-based models targeting FPGAs

Technologies including oneAPI [1], OmpSs [11], EngineCL [12], Kokkos [22], OpenCL [16], and OpenACC [18] have been developed or enhanced to support FPGAs. Using these technologies it is possible, although some with a greater level of ease than others, to mix execution across different architectures.

However, despite improving general programmability by supporting a common host-side programming abstraction, these approaches all fail to fully exploit the full potential of FPGAs. This is mainly a flexibility issue, where these frameworks lack the support do independently swap in and out tasks of varying sizes onto an FPGA accelerator whilst other tasks are running and remain unaffected. Furthermore these frameworks do not support preemption of kernels on the FPGA which, whilst it is secondary in importance to the issue of flexibility, still provides benefit for some workloads.

The authors of [23] tried to address these limitations with their task-based library that targets System on-a Chip (SoC) deployment based on OpenCL using dynamic partial reconfiguration. They support kernel preemption by enabling checkpointing at the end of each OpenCL workgroup, and whilst this is a natural consistency point in the OpenCL model, the coarse-grained nature of the approach limits scheduling flexibility. For example, tasks of higher priority may need to wait until a previous workgroup with lower priority tasks finishes. Moreover, the user must write their kernel interfaces in a manner that are conformant to the interfaces of the FPGA's reconfigurable regions, causing a conflict between the high-level OpenCL description and the management of the lower-level on-chip infrastructure, which increases the overall development complexity. It is important that this aspect is abstracted from the programmer because of the expertise required on behalf of the programmer to get this right. Furthermore, the authors use the ZUCL framework [19] to support their approach, which is a predefined static system using the entirety of the FPGA regardless of the number of kernels that are actually being executed by the application.

FPGA support provided within OmpSs [6] delivers fast checkpointing on the FPGA via on-chip memory and highlevel kernel code annotations. However, their work leverages this mechanism only for fault tolerance and does not consider or support preemptive scheduling.

# 3 Approach to support preemptive scheduling on FPGAs

In contrast to previous techniques, our approach enables one to leverage the FPGA in a flexible manner through the use of a dynamic partial reconfiguration capable design for each number of reconfigurable regions. This approach avoids potential decreases in the final design clock frequency which can occur because of unnecessarily high occupation, leading

Figure 1. The Controller programming model, generic FPGA backend. Extracted from [21].

to missed opportunities for optimisation in the routing phase of the tooling. To achieve this we focus on two areas; the on-chip FPGA infrastructure and the integration on the hostside of the Controller runtime.

# 3.1 On-chip infrastructure

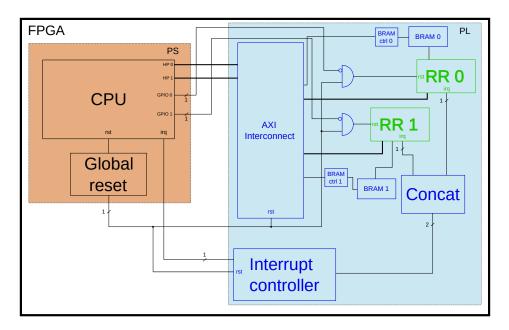

Figure 2 illustrates the architecture of the static part of the on-chip infrastructure in our approach. This is known as the *shell*, and is deployed to the FPGA to provide infrastructure and management capabilities such as configuration of the reconfigurable regions and the ability to share memory between the CPU and the reconfigurable logic. The blue box in Figure 2 represents the Programmable Logic (PL) part of the Zynq FPGA, where each constituent box is known as an *IP block*.

The user's tasks, known as kernels at the hardware level, are *dropped into* one of two reconfigurable regions (denoted RR in Figure 2), although it should be noted that our approach and shell is scalable to any number of regions. Our approach targets HLS kernels that are generated by Xilinx's HLS tooling and using a single master memory interface (known as AXI4-Master) to connect to the board's DRAM memory. Furthermore, a slave interface (known as an AXI4-Slave) is used for the HLS kernel's control ports and this is standard with HLS. It should be noted that, whilst these interfaces are fixed in the design, the user need not use HLS if they do not wish, any type of IP block can be placed into the reconfigurable regions as long as it conforms to the interfaces. Whilst this interface configuration is fairly standard for HLS IP blocks, it is possible to regenerate the shell with a different number and type of interface(s) as required.

The interrupt controller registers interrupts generated by the reconfigurable regions upon completion, and therefore the CPU can detect when kernels have finished execution. To support preemption of kernels, the shell must be able to interrupt a kernel, saving its context and state, to later resume it. The shell features two on-chip BRAM memory banks (one per reconfigurable region) in which is stored the interrupted kernel's state at arbitrary intervals whose frequency is defined by the user. BRAM memory is used since its speed and closeness to the reconfigurable regions results in very low latency, minimising the overhead of the context saving operation. These BRAM banks are also connected to a BRAM controller which enables access to this memory from the CPU, supporting overall book-keeping of the kernel's state when kernels are being swapped in and out by the scheduler controlling execution from the host.

Our approach increases the complexity of undertaking a reset, as it must be possible to reset both the entire FPGA and individual reconfigurable regions. The former is achieved via the shell's *global reset* (see Figure 2). The latter is supported by specific reset functionality for each reconfigurable region implemented using the GPIO ports of the CPU. Because, by default, reset is active low for HLS kernels the GPIO signal is negated and then the logical *and* operation is applied with the global reset signal. The application of the reset signal is asynchronous which means that the kernel might be interrupted unpredictably, this is handled by the software abstractions that are described in Section 4.2 to ensure that a task can be resumed later from a consistent state.

This shell design is provided in *netlist* form and packaged as a Tcl script, which is the standard scripting language for Xilinx tools, with the reconfigurable regions instantiated as black boxes. Consequently, to generate the Vivado hardware design one executes the Tcl script with, as an argument, the number of reconfigurable regions that are required. This step is not intended to be completed by the programmer, but instead either by a more FPGA experienced systems team member who will then build and deploy the shell onto the FPGA, or provided pre-built.

**Figure 2.** Overview architecture of our shell which supports dynamic partial reconfiguration and preemption of tasks. In this illustration there are two Reconfigurable Regions (RRs) into which kernels are dynamically swapped in and out which is independent of the other region.

### 3.2 Integration into the Controller framework

A new Controller backend has been written to interact with the shell design that was described in Section 3.1 which targets the Zynq-7020 FPGA and Pynq-Z2. To undertake low level communication with the FPGA, we use the Pynq C API [17] which exposes rudimentary functionalities, such as the loading of full and partial bitstreams, the interaction with design IP such as interrupt controllers or DMA engines through memory mapping, and host-device shared memory. Building on the C Pynq API means that this work is compatible with any other FPGA from the Zynq-7000 family with little modification required.

Each reconfigurable region is treated by our Controller backend as an independent accelerator, ensuring that tasks can be executed across these regions in parallel. To achieve this we replicate Controller's device specific queue for each reconfigurable region, and each instance is managed by a separate thread. A request to reconfigure a region is implemented as an internal task, queued and executed like any other task. This approach simplifies the backend structure and enforces the scheduling of a reconfiguration request before the associated task execution on the fabric.

A complication is that it is only possible to reconfigure one region at a time because the Zynq only provides a single Internal Configuration Access Port (ICAP) [26] which is actually used for the partial reconfiguration. Consequently a lock is required to enforce synchronisation between reconfiguration requests in the Controller queues. The Zynq-7000 FPGA family architecture supports shared memory which can be accessed by both the FPGA fabric and host CPU. This memory can be both the fast on-chip BRAM and also the slower off-chip DRAM, and because both the FPGA fabric and CPU can access these spaced directly it means that datamovement operations can be implemented as zero-copy.

Furthermore, the Controller backend leverages Userspace I/O (UIO) to interact with the shell's interrupt controller for detecting interrupts raised by the reconfigurable regions that, as described in Section 3.1, indicate kernel termination. To avoid constantly polling for these interrupts we use the *select()* system call to activate the manager CPU thread when an interrupt is received. The Controller backend then queries the interrupt controller to determine which region raised the interrupt.

### 3.3 The Controller FPGA scheduler

Building atop the Controller backend described in Section 3.2, we then used the ability to undertake dynamic partial reconfiguration to build a First Come First Served (FCFS) scheduler for our tasks, which provides the ability to specify task priorities and undertake preemption.

In order to test the scheduler we simulate scenarios where both the time of the next task arrival and the task parameters are randomly generated. This is undertaken by pregenerating a sequence of tasks, ordered by a random arrival time, where each task has a random priority, a randomly chosen kernel code to execute (from a given set), and random arguments. Our scheduler is modular such that the main scheduling functionality including the management of the queues and service of tasks is separate from our test scenario, which generates random tasks. Consequently it is possible to use this schedule in a test or production mode, and furthermore possible to fairly easily extend or adapt the underlying scheduling logic and to manage any number of reconfigurable regions.

The scheduler presented in [20] was extended to support the preemption of tasks using full reconfiguration. Under this full reconfiguration regime the entire FPGA is halted until reconfiguration has completed, and therefore the state of running tasks must be saved in advance. As a consequence, kernel swap operations are mutually exclusive with kernel tasks, unlike with the dynamic partial reconfiguration approach where reconfiguration latencies are hidden by computation. Upon termination of full reconfiguration the state of the interrupted tasks is restored.

The main loop of our scheduler is presented in Algorithm 1. It consists of an infinite loop that serves one task per iteration and terminates when all of them have completed. At the beginning of each iteration, the function *waitForInterrupt()* will wait for either one of two events: an interrupt or a timeout. An interrupt is received when a kernel has finished its execution whilst a timeout happens when a new task has arrived. This guarantees a task waits efficiently for a task through the select() system call. Line 3 in Algorithm 1 tests for the termination condition and, if no such condition is present then tasks are served either as they arrive, between lines 6 and 8, or from the queue whenever a task finishes execution between lines 10 to 14. It can be seen that, whenever the arrival of tasks ceases, then tasks are drawn from the queue and served to the available reconfigurable regions. Therefore, as long as there are enough tasks in the queue, the reconfigurable regions will be assigned tasks. This was not ensured in the previous version of the scheduler that was presented in [20] which, although it kept the regions at full occupation in many scenarios, was not guaranteed for all mixes of tasks. Finally, line 17 updates the timeout for the next arriving task.

Algorithm 2 presents the swap mechanism of our approach, where it can be seen that full reconfiguration encompasses more steps and book-keeping than dynamic partial reconfiguration. Whenever partial reconfiguration is chosen, the partial bitstream corresponding to the incoming kernel is selected at line 2 and then the scheduler instructs the Controller runtime to perform the reconfiguration at line 3. Otherwise, for full reconfiguration, all the running kernels in the reconfigurable region other than the one requested are preempted to save their state. This step is fundamental to prevent restarting kernels that had already computed work. A simpler approach would adding a synchronisation point for all the kernels before the reconfiguration, but this would add to the overhead of the reconfiguration latency, proportional to the size of the FPGA. Line 10 selects the bitstream that includes the incoming kernel in the requested

reconfigurable region, leaving the other kernels unchanged. Line 11 then performs the same task as line 3 and, after the reconfiguration, line 12 sets up the hardware design for operation. This includes setting up and mapping to memory the reconfigurable region's interfaces and controllers, such as for interrupts and BRAM. Finally, between lines 13 and 18, the preempted kernels are restored to resume execution.

| Algorithm 1 Main loop of the scheduler.                      |  |  |  |  |

|--------------------------------------------------------------|--|--|--|--|

| 1: while true do                                             |  |  |  |  |

| 2: waitForInterrupt(timeout)                                 |  |  |  |  |

| 3: <b>if</b> hasFinished(N, tasks_to_arrive) <b>then</b>     |  |  |  |  |

| 4: break                                                     |  |  |  |  |

| 5: end if                                                    |  |  |  |  |

| 6: <b>if</b> $tasks_to_arrive \land timeout = 0$ <b>then</b> |  |  |  |  |

| 7: $task \leftarrow getArrivedTask()$                        |  |  |  |  |

| 8: serveTask(task)                                           |  |  |  |  |

| 9: else                                                      |  |  |  |  |

| 10: <b>for all</b> $r \in R$ <b>do</b>                       |  |  |  |  |

| 11: <b>if</b> $isFree(r)$ <b>then</b>                        |  |  |  |  |

| 12: $task \leftarrow getTaskFromQueue()$                     |  |  |  |  |

| 13: serveTask(task)                                          |  |  |  |  |

| 14: <b>end if</b>                                            |  |  |  |  |

| 15: <b>end for</b>                                           |  |  |  |  |

| 16: <b>end if</b>                                            |  |  |  |  |

| 17: <i>updateTimeout(timeout)</i>                            |  |  |  |  |

| 18: end while                                                |  |  |  |  |

#### Algorithm 2 Swap function

| 1:  | if partial then                                          |

|-----|----------------------------------------------------------|

| 2:  | partial_bitstream ←                                      |

|     | get_partial_bitstream(incoming_task)                     |

| 3:  | doSwap(partial_bitstream)                                |

| 4:  | else                                                     |

| 5:  | for all $r \in R$ do                                     |

| 6:  | <b>if</b> $running(r) \land r \neq r_{swap}$ <b>then</b> |

| 7:  | evictKernel(r)                                           |

| 8:  | end if                                                   |

| 9:  | end for                                                  |

| 10: | full_bitstream ←                                         |

|     | getFullBitstream(incoming_task)                          |

| 11: | doSwap(full_bitstream)                                   |

| 12: | setupFPGA()                                              |

| 13: | for all $r \in R$ do                                     |

| 14: | <b>if</b> $evicted(r) \neq r_{swap}$ <b>then</b>         |

| 15: | restoreContext(evicted_task[r])                          |

| 16: | launch(evicted_task[r])                                  |

| 17: | end if                                                   |

| 18: | end for                                                  |

| 19: | end if                                                   |

|     |                                                          |

The process of serving a task consists of the following steps: (1) Find an available region, i.e., a region where the

last task running has already finished. (2) In case no available region was found, if preemption is disabled enqueue the task. If preemption is enabled, check if there is a region executing a task with lower priority. In that case, stop the kernel execution in that region, save the context and state, enqueue the stopped task, and consider the region as available. (3) If the kernel loaded in the available region is distinct from the kernel of the incoming task, enqueue a swapping task to reconfigure the RR. (4) Launch the new task. If it was a previously stopped task, its context is copied back to the device before launching.

# 4 **Programmer's abstractions**

Whilst dynamic partial reconfiguration is abstracted from the programmer by the FPGA shell and new Controller backend that were described in Section 3, in order to leverage preemption of kernels then some explicit support is required from the programmer. We provide high-level kernel code abstractions that allow programmers to store the state of their kernel at arbitrary points during the execution of the task, instead of waiting for a specific pre-defined consistency point. Traditional FPGA checkpointing methods, such as readback or scan-chain, commonly incur either high time overhead by write the state of the whole FPGA fabric [3] or resource usage overhead by extending the existing circuit with state access support structures [25], respectively. Instead, by providing HLS kernel code abstractions we can provide more choice to the programmer so that they can choose when they store the state and the state storage is limited to a specific kernel.

#### 4.1 Kernel interface abstraction

The generation of interfaces in technologies such as Vitis HLS is done adding pragmas that can be cumbersome and error prone to write, especially for non-experts. Moreover, as described in Section 3.1, a requirement of dynamic partial reconfiguration is that HLS kernels to be deployed into a given reconfigurable region must present the same external interface to the shell. This means that they must conform to the same number of interface ports and port configurations, such as bus widths [26]. Consequently, abstractions to hide these low-level details to the programmer are beneficial as they simplify the overall code.

**Listing 1.** Sketch of a Median Blur kernel written with the Controller abstraction

```

CTRL_KERNEL_FUNCTION(

1

2

MedianBlur, PYNQ, DEFAULT,

KTILE_ARGS(KHitTile_int in_array,

3

KHitTile_int out_array),

INT ARGS(int H, int W, int iters),

5

FLOAT_ARGS(NO_FLOAT_ARG)) {

6

int k. row. col:

8

9

context_vars(k, row, col);

10

```

```

for_save(k, 0, iters, 1) {

11

12

for_save(row, 1, H+1, 1) {

for_save(col, 1, W+1, 1) {

13

14

window [0] = hit(

15

in_array , row-1, H_NCOL+col-1);

16

17

checkpoint(col);

18

} checkpoint(row);

19

} checkpoint(k);

20

}

21

}

```

The configuration of the interfaces is a parameter present in our Tcl configuration script that generates the shell's hardware design, as discussed in Section 3.1. In the Controller model, codes forming a task are wrapped with curly brackets and preceded by a kernel signature. This kernel signature is provided with a macro-function named CTRL\_KERNEL\_FUNCTION which specifies the kernel parameters in a form that is processed by the Controller library to generate the proper lowlevel interface. Listing 1 illustrates the definition of a Median Blur kernel, used in our evaluation in Section 5, where from the the signature contains the following possible parameters:

- CTRL\_KERNEL\_FUNCTION(K, T, S, A<sub>p</sub>, A<sub>i</sub>, A<sub>f</sub>):

- K is the name of the kernel.

- T indicates the backend type that will be targeted. Supported types are: CPU, CUDA, OpenCL, FPGA.

- S is the subtype of backend that will be targeted, e.g. DEFAULT.

- A<sub>p</sub> is a list of pointer non-scalar arguments defined with KTILE\_ARGS.

- A<sub>i</sub> is a list of integer scalar arguments defined with INT\_ARGS.

- A<sub>f</sub> is a list of floating point scalar arguments defined with FLOAT\_ARGS.

Whilst the first three of these arguments are obvious, the last three require explanation. The A<sub>p</sub> argument is required because Controller provides a wrapper structure for multidimensional arrays named *HitTile*, where any kind of nonscalar arguments are provided as *HitTile* arguments. The KTILE\_ARGS function enables the use of *HitTile* accessors within the kernel, effectively providing input and output arrays to the kernel, as discussed in [21]. The last two arguments, INT\_ARGS and FLOAT\_ARGS support passing integer and float scalar arguments, respectively and all these functions have variadic arguments to adapt the kernel interface to the number of arguments required by the programmer.

The corresponding code generated by the kernel signature for the kernel shown in Listing 1 is shown in Listing 2, where three integer arguments are provided by the user and five extra dummy arguments i\_args\_<n> are generated. Similarly, 8 dummy floating point and 1 dummy pointer arguments are generated to fill the argument count and provide a shell compliant interface. Finally, a pointer to a struct context is added for context book-keeping if the task is interrupted. **Listing 2.** Code generation for the signature of the Median Blur kernel

```

void MedianBlur(...,

int H, int W, int iters, int i_args_0, ..., int i_args_4,

..., volatile struct context * context, int * return_var);

```

#### 4.2 Programmer abstractions for preemption

Preemption of a kernel whilst it is running requires saving its state so that it can be resumed in the future. We propose a finer-grain approach compared to previous efforts, such as [23], which only store the context at the end of an OpenCL workgroup. Following our programmer-aware checking approach the programmer has the flexibility to indicate when and what data should be checkpointed during the kernel execution. To this end we provide several checkpointing macro-functions the first of which, context\_vars, enables the programmer to declare which variables should be stored in the checkpoints. The checkpoint macro stores one or more of these variables at a given execution point, and the for\_save macro-function is used in-place of the normal for loop construct, to provide support for resumption on a specific loop iteration. These macro calls are expanded at synthesis time and hence are translated to the HDL level,

Listing 1 provides an example of the use of these preemption macros, where at line 9 the integer variables k, row, and col are selected to be checkpointed, with lines 11, 12, and 13 using the for\_save macro to define loops and for these to be restarted as appropriate. The associated loop variables are checkpointed at lines 17, 18, and 19. This kernel saves the state at each iteration so that it can be resumed without discarding previously computed iterations. It should be noted that, in this example we have chosen to save this state at every iteration, which means that we are able to resume execution without discarding any of the previously computed iterations, although this might result in some storage overhead as described in Section 3.1 this is minimised by our shell using the fast on-chip BRAM memory for this checkpointing.

Listing 3. Definition of struct context.

```

struct context {

int var[N];

int init_var[N];

int incr_var[N];

int saved[N];

int valid;

};

```

Context saving is undertaken transparently by storing the state of variables into the context structure which is then stored in BRAM. Listing 3 illustrates the members of this structure, where in our prototype up to N integers can be nominated by the user to be saved (where N is a compile time parameter). Whilst integers suffice for our purposes in this paper, it is trivial to extend this structure to support other data types by adding additional member(s).

The field saved in Listing 3 stores information about whether corresponding variables have already been saved and this is read during a resume operation to determine whether they should be restored or not. The valid field is a safety check and used to indicate whether the kernel was interrupted during a data saving operation. This is required because preemption is asynchronous, and as such if it occurs during data saving then the stored state can be inconsistent. In such a case the resume operation will be undertaken with the previously saved values.

# 5 Experimental study

In this study we experiment with the scheduler described in Section 3.3 to operate upon randomly generated image filter tasks. The tasks chosen for the experimentation are blur image filters applied to images pre-stored in memory, and they execute one of four possible kernels: One iteration of Gaussian Blur, or Median Blur over one, two or three iterations. Tasks arrive at random times distributed over U(0, T) minutes. With five different priorities to generate a rich mixture of task preemption, task switching and FPGA reconfiguration. The tasks, their arrival time, and the image on which it should be applied, are randomly generated before the scheduler starts.

#### 5.1 Experimentation environment

The experiments were conducted on a Xilinx PYNQ-Z2 FPGA featuring a ZYNQ XC7Z020-1CLG400C of the Zynq-7020 family, an ARM Cortex-A9 dual core at 650 MHz CPU and 512 MB DDR3. The FPGA fabric is running at a clock frequency of 100MHz and HLS kernels were compiled using Xilinx Vitis HLS version 2020.2 with the hardware design and corresponding bitstreams generated with Xilinx Vivado v2020.2. Controller was compiled with GCC 7.3.0 and compilation scripts were generated with CMake 3.25.1.

Thirty tasks are generated for each experiment, where each task has a randomly chosen priority value from 0 to 4 with the same probability, with 0 being the highest priority. The kernel to be executed by the task is also randomly chosen with the same probability among the four possible kernels and we consider three different scenarios of service load by changing the maximum possible arrival time T of the tasks. This changes the average arrival rate of the tasks, where in the *Busy* scenario we use T = 0.1 minutes, in the *Medium* scenario T = 0.5 minutes and in the *Idle* scenario T = 0.8 minutes. All the tasks details (arrival time, kernel to execute and priority) are randomly chosen with a Tausworthe random generator initialised with a given seed for experiment reproducibility. We present results for 10 seeds of a Tausworthe random sequence starting at an arbitrarily chosen seed value: 28871727. The main observations can be extrapolated for other random sequences.

We have also designed experiments using different image sizes to generate different task loads distributions, and in this section we explore image sizes that are  $200 \times 200$ ,  $300 \times 300$ ,  $400 \times 400$ ,  $500 \times 500$  and  $600 \times 600$ . To study the scheduling behaviour of the tasks executing sequentially, compared to running in parallel, both one and two reconfigurable region scenarios are considered. We also study the effect of using scheduling policies with and without preemption, where preemption is activated when an arriving task has higher priority than one of the tasks currently in execution.

# 5.2 Resource usage

Our first study involved exploring the resource usage of our two kernels, the Median Blur and Gaussian Blur with and without support for preemption enabled. The purpose of this was to understand the FPGA resource overhead resulting from enabling preemption, and Table 1 presents these figures as reported by the HLS tooling. It can be seen that, as expected, with the Median Blur kernel when enabling preemption this increases the resource usage. However, surprisingly with the more complicated Gaussian Blur kernel when enabling preemption this reduces the overall usage rather than increases it. By analysing the logs and resource usage reports that are generated by the tooling we found that the HLS tool follows a different synthesis path for the Gaussian Blur kernel when preemption is enabled, generating different HDL target code that is fairly significantly different from when preemption is disabled. Nevertheless, it can be seen from Table 1 that the resource overhead of enabling preemption is minimal, especially for the LUTs. Incidentally, the reason we are not reporting BRAM usage in Table 1 is because, as described in Section 3.1 this sits external to the HLS kernel in the shell and can be sized as required to fit within the constrains of the available memory on the chip.

#### 5.3 Results

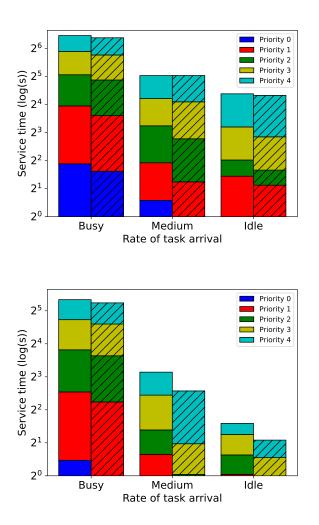

In order to show the effectiveness of our approach we are presenting results for the following metrics: (i) service time, defined as the time it takes for a task to be served since it is generated until it starts execution on the FPGA and (ii) throughput, defined as the number of tasks executed per second. We also compare the use of partial reconfiguration with the more conventional full reconfiguration approach. Figure 3 reports the service time for tasks in every priority queue both with and without preemption for 30 tasks at size  $600 \times 600$  accumulated by priority. We chose this number of tasks and image size as it provides a large enough workload and a sufficient number of tasks to study the behaviour of the scheduler. The results are presented both for one and two reconfigurable regions and, as can be seen, service times are longer for the busy rate of arrival than for medium and idle, as tasks have to wait a longer time until a region becomes available than when they arrive later, providing the opportunity for kernels to finish.

If the priority of an incoming task is higher than one of the tasks running, then its service time will be virtually zero. We can observe this by comparing the right bars of Figure 3 with the corresponding left bars. For this representative case, on average, preemption reduces service time substantially and this will be the case in general when incoming tasks present a higher priority than running tasks. These results demonstrate that our scheduler effectively reduces the total service time of tasks, thus increasing the flexibility, as preemption enables swapping in and out tasks upon a specific condition which, in this case, is the priority. The reduction in service time is heavily dependent on the structure of priorities of the generated tasks, both in terms of the number of tasks enqueued and the number of reconfigurations required by the incoming kernels which are not already loaded in the fabric. Note that a task will have to wait until previous tasks of higher or the same priority have completed. Additionally, as shown in Figure 3, the total service time decreases with the number of reconfigurable regions, as more opportunities are created for kernels of lower priorities to execute.

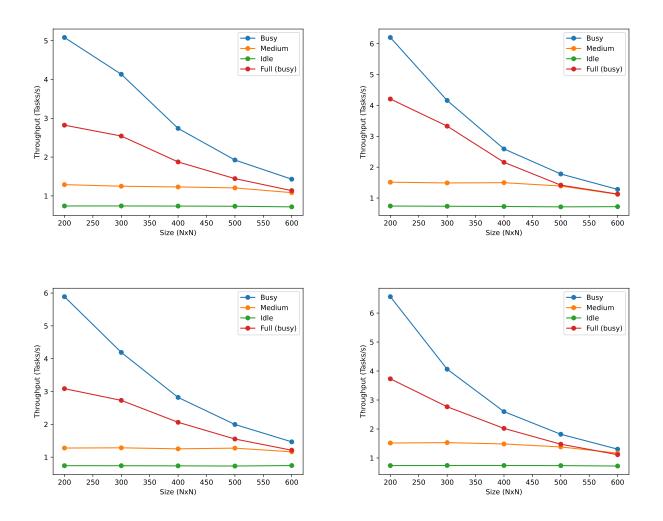

Figure 5 illustrates the throughput of the scheduler for 30 tasks with preemption and dynamic partial reconfiguration over two reconfigurable regions for two of the randomly chosen seeds. The throughput of the preemptive scheduling with full reconfiguration in the busy scenario is the highest achieved with this policy and is provided for comparison in Figure 5. As expected, the throughput increases with the rate of arrival of tasks, and as a general pattern the lower the dimensions of the images then the higher the throughput, as kernels complete their execution faster. It is also observable that the overheads incurred by preemption lead to a slightly lower overall throughput. These are most noticeable for a high rate of arrival of tasks, where throughput losses are 13.71% and 5.58% for the case with seed 28871727 and 1368297677, respectively, at size 200 and busy arrival rate. For the rest of cases the loss ranges between 1.38% and 3.60% for the seed 28871727 and -2.37% and 3.40% for the seed 1368297677. Most of this overhead is explained by the time taken by the extra partial reconfigurations required by preemption. The red lines in the graphs of Figure 5 report the throughput when full reconfiguration is instead used. In this situation it can be seen that full reconfiguration performs much worse than dynamic partial reconfiguration, even in the most favourable of case.

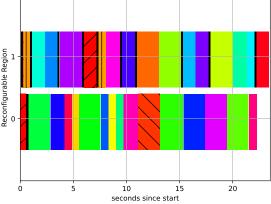

Figure 3 reports results from running an experiment with 30 tasks working with images of  $600 \times 600$  pixels on two reconfigurable regions for the seed 1368297677. The figure shows the results for full reconfiguration (left), and dynamic partial reconfiguration (right). Execution tasks are shown in colour and swap operations in black. Preempted tasks are presented with a hatched pattern.

Table 1. Single HLS kernel FPGA resource usage for Median Blur and Gaussian Blur when enabling or disabling preemption.

| Description                   | LUT resource usage % | DSP resource usage % |

|-------------------------------|----------------------|----------------------|

| Median Blur (no preemption)   | 0                    | 1                    |

| Median Blur (preemption)      | 1                    | 14                   |

| Gaussian Blur (no preemption) | 21                   | 12                   |

| Gaussian Blur (preemption)    | 17                   | 3                    |

**Figure 3.** Service times for 30 tasks at size  $600 \times 600$  for seed 1120249751, with one reconfigurable region in the diagram on the left, and two regions on the right. The bars in each plot represent non-preemptive execution on the left and preemptive execution on the right.

In the case of full reconfiguration, the kernel-code swap operation is executed in both reconfigurable regions concurrently, and therefore the whole FPGA fabric remains idle during reconfiguration. Figure 3-left shows that all the running tasks have to be preempted before full reconfiguration

**Figure 4.** Scheduling of 30 tasks at size  $600 \times 600$  over two reconfigurable regions for seed 1368297677. Full reconfiguration is on the left and partial reconfiguration on the right. Execution tasks shown in colour and swap operations in black. Preempted tasks present a hatched pattern.

and restored afterwards. This process, in addition to the necessary book-keeping, incurs large overheads. It can also be seen that the reconfiguration time of full reconfiguration is much larger than that of dynamic partial reconfiguration, consequentially penalising the overall execution time. As

Figure 5. Throughput for 30 tasks scheduled with preemption (top) and without preemption (bottom). Seed 28871727 (left) and 1368297677 (right).

a result of these performance penalties, the execution time with our approach is always shorter.

In the case of dynamic partial reconfiguration, whilst a reconfigurable region is executing either a kernel task or a kernel-code swap operation (indicated by black bands in the plot), the other region may be executing another kernel task with the same or different kernel code. In this scenario, more than one kernel can coexist on the FPGA and therefore there are no times when the reconfigurable regions are idle. Consequently, each reconfigurable region is always executing tasks or kernel-code swap operations, and by eliminating idle times, the execution time of the application is minimised. It can be seen that this technique makes better use of the FPGA resources than full reconfiguration.

In the case of dynamic partial reconfiguration, the time required by the kernel-code swap operations is proportional to the size of the region. However, for the full reconfiguration alternative the time required is proportional to the size of the whole FPGA. Therefore it can be seen that full reconfiguration is not recommended in this sort of workload since the reconfiguration time can increase with each new generation of FPGAs.

Tables 2 and 3 report the average service time for maximum priority tasks for busy, medium, and idle scenarios using preemptive and non-preemptive scheduling options in partial reconfiguration cases. Similarly, 4 and 5 present the same results for the minimum priority. Different seeds, randomly obtained from a Tausworthe generator, were used to select the arrival times and task priority. The number of tasks executed is always 30, scheduled on both one and two reconfigurable regions respectively. These tables demonstrate that, that as we displace from a busy scenario to a

**Table 2.** Average service time for maximum priority with standard deviation for 30 tasks scheduled on 1 RRs at size  $600 \times 600$ .  $\overline{T_m}$  is the average service time, where T can be B (busy), M (medium) or I (idle) and m can be P (preemptive) or NP (non-preemptive).

| seed       | $\overline{B_{np}}$ | $\overline{M_{np}}$ | $\overline{I_{np}}$ | $\overline{B_p}$ | $\overline{M_p}$ | $\overline{I_p}$ |

|------------|---------------------|---------------------|---------------------|------------------|------------------|------------------|

| 28871727   | 4.61                | 0.63                | 0.58                | 4.12             | 0.25             | 0.14             |

| 1368297677 | 5.16                | 3.18                | 1.44                | 4.12             | 1.77             | 0.41             |

| 3968565823 | 5.82                | 2.73                | 2.03                | 3.82             | 1.24             | 0.90             |

| 1120249751 | 3.69                | 1.50                | 0.97                | 3.07             | 0.76             | 0.62             |

| 3706141637 | 5.83                | 2.74                | 2.03                | 3.82             | 1.25             | 0.90             |

| 1838770479 | 3.98                | 2.36                | 1.32                | 3.36             | 0.92             | 0.28             |

| 980516246  | 4.60                | 0.65                | 0.98                | 3.20             | 0.29             | 0.30             |

| 407297508  | 3.40                | 1.44                | 0.81                | 1.38             | 0.34             | 0.31             |

| 3820789643 | 5.79                | 2.72                | 2.05                | 3.82             | 1.23             | 0.90             |

| 1227911765 | 2.88                | 0.80                | 0.32                | 2.86             | 0.16             | 0.06             |

|            |                     |                     |                     |                  |                  |                  |

**Table 3.** Average service time for maximum priority with standard deviation for 30 tasks scheduled on 2 RRs at size  $600 \times 600$ .  $\overline{T_m}$  is the average service time, where T can be B (busy), M (medium) or I (idle) and m can be P (preemptive) or NP (non-preemptive).

| seed       | $\overline{B_{np}}$ | $\overline{M_{np}}$ | $\overline{I_{np}}$ | $\overline{B_p}$ | $\overline{M_p}$ | $\overline{I_p}$ |

|------------|---------------------|---------------------|---------------------|------------------|------------------|------------------|

| 28871727   | 2.76                | 0.32                | 0.26                | 1.72             | 0.08             | 0.10             |

| 1368297677 | 3.05                | 1.32                | 0.40                | 1.47             | 0.38             | 0.09             |

| 3968565823 | 2.72                | 1.05                | 0.79                | 1.47             | 0.26             | 0.09             |

| 1120249751 | 1.39                | 0.84                | 0.64                | 0.78             | 0.22             | 0.21             |

| 3706141637 | 2.71                | 0.95                | 0.78                | 1.47             | 0.25             | 0.10             |

| 1838770479 | 2.21                | 1.02                | 0.50                | 1.19             | 0.03             | 0.09             |

| 980516246  | 2.39                | 0.94                | 0.85                | 1.18             | 0.10             | 0.14             |

| 407297508  | 1.92                | 0.41                | 0.11                | 0.43             | 0.08             | 0.04             |

| 3820789643 | 2.67                | 1.00                | 0.79                | 1.46             | 0.27             | 0.10             |

| 1227911765 | 1.47                | 0.27                | 0.11                | 0.98             | 0.14             | 0.07             |

medium or idle scenario, the service time is reduced. Consequently, less stressed scenarios obtain better results even for lower priority tasks, as there is a higher chance that a reconfigurable region is available upon task arrival.

For any of the scenarios (busy, medium or busy ) all the preemptive cases obtain better results than the non-preemptive ones. Therefore, highest priority tasks are served earlier if the preemptive policy is exploited. Adding a second reconfigurable region significantly improves service time of maximum priority tasks since more than one task can be executed at the same time on the FPGA. In conclusion, it is highly beneficial to increase the number of reconfigurable regions to as many as can be supported by the hardware resources.

**Table 4.** Average service time for minimum priority with standard deviation for 30 tasks scheduled on 1 RRs at size  $600 \times 600$ .  $\overline{T_m}$  is the average service time, where T can be B (busy), M (medium) or I (idle) and m can be P (preemptive) or NP (non-preemptive).

| seed       | $\overline{B_{np}}$ | $\overline{M_{np}}$ | $\overline{I_{np}}$ | $\overline{B_p}$ | $\overline{M_p}$ | $\overline{I_p}$ |

|------------|---------------------|---------------------|---------------------|------------------|------------------|------------------|

| 28871727   | 35.02               | 23.22               | 8.13                | 35.21            | 26.63            | 8.99             |

| 1368297677 | 39.28               | 28.00               | 7.29                | 40.15            | 28.12            | 7.90             |

| 3968565823 | 27.06               | 22.75               | 17.10               | 27.08            | 23.58            | 13.70            |

| 1120249751 | 28.67               | 14.18               | 11.64               | 28.86            | 15.66            | 12.83            |

| 3706141637 | 27.09               | 22.69               | 17.10               | 27.10            | 23.80            | 13.70            |

| 1838770479 | 39.45               | 31.77               | 4.09                | 39.45            | 32.12            | 4.55             |

| 980516246  | 30.45               | 19.01               | 4.77                | 30.33            | 19.10            | 7.22             |

| 407297508  | 30.11               | 23.61               | 4.47                | 29.85            | 24.97            | 4.84             |

| 3820789643 | 27.02               | 22.54               | 17.14               | 27.31            | 23.53            | 13.75            |

| 1227911765 | 32.86               | 18.79               | 3.21                | 32.77            | 20.59            | 2.80             |

**Table 5.** Average service time for minimum priority with standard deviation for 30 tasks scheduled on 2 RRs at size  $600 \times 600$ .  $\overline{T_m}$  is the average service time, where T can be B (busy), M (medium) or I (idle) and m can be P (preemptive) or NP (non-preemptive).

| seed       | $\overline{B_{np}}$ | $\overline{M_{np}}$ | $\overline{I_{np}}$ | $\overline{B_p}$ | $\overline{M_p}$ | $\overline{I_p}$ |

|------------|---------------------|---------------------|---------------------|------------------|------------------|------------------|

| 28871727   | 17.16               | 4.96                | 0.52                | 17.66            | 5.81             | 0.35             |

| 1368297677 | 19.46               | 6.08                | 0.16                | 19.50            | 6.54             | 0.18             |

| 3968565823 | 13.45               | 7.32                | 1.93                | 13.25            | 7.01             | 1.88             |

| 1120249751 | 13.86               | 3.37                | 0.62                | 13.56            | 3.98             | 0.65             |

| 3706141637 | 13.30               | 7.40                | 1.93                | 13.35            | 5.07             | 1.89             |

| 1838770479 | 19.99               | 1.44                | 0.63                | 20.08            | 1.64             | 0.94             |

| 980516246  | 14.80               | 0.66                | 0.48                | 14.75            | 0.70             | 0.47             |

| 407297508  | 12.54               | 2.32                | 1.19                | 12.70            | 2.61             | 1.19             |

| 3820789643 | 13.27               | 7.22                | 1.93                | 13.28            | 5.02             | 1.89             |

| 1227911765 | 16.21               | 1.56                | 0.34                | 15.87            | 1.80             | 0.34             |

|            |                     |                     |                     |                  |                  |                  |

Table 7 reports the average overhead of our preemption method with dynamic partial reconfiguration (left) and full reconfiguration (right). The overheads for dynamic partial reconfiguration were calculated as quotients of the average throughput of the experiments with 10 random seeds, which are presented in Table 6. In the case of full reconfiguration, these overheads were calculated as quotients with the busy rate of arrival with preemption as baseline. We tested the scheduler in scenarios involving tasks working in different image sizes to study the overhead of the preemption technique with different task loads. The overhead for dynamic partial reconfiguration is larger for busier scenarios, as the rapid arrival of tasks triggers more kernel preemptions. Similarly, the overhead is also greater for smaller image sizes since the execution time is shorter and the throughput is

**Table 6.** Average throughput with standard deviation for 30 tasks scheduled on 2 RRs at size  $600 \times 600$ .  $\overline{T}$  is the average throughput, where T can be B (busy), M (medim) or I (idle).

| size | $\overline{B_{np}}$ | $\overline{M_{np}}$ | $\overline{I_{np}}$ | $\overline{B_p}$  | $\overline{M_p}$ | $\overline{I_p}$  |

|------|---------------------|---------------------|---------------------|-------------------|------------------|-------------------|

| 200  | 6.87±1.16           | $1.42 \pm 0.12$     | $0.79 {\pm} 0.04$   | 6.27±1.23         | $1.42 \pm 0.12$  | $0.79 \pm 0.04$   |

| 300  | $4.53 \pm 0.50$     | $1.42 \pm 0.13$     | $0.79 \pm 0.04$     | $4.26 \pm 0.41$   | $1.40 \pm 0.13$  | $0.78 {\pm} 0.04$ |

| 400  | $2.94 \pm 0.25$     | $1.41 \pm 0.13$     | $0.79 \pm 0.05$     | $2.86 \pm 0.27$   | $1.39 \pm 0.14$  | $0.78 {\pm} 0.05$ |

| 500  | $2.02 \pm 0.13$     | $1.36 \pm 0.12$     | $0.78 {\pm} 0.04$   | $1.97 {\pm} 0.14$ | $1.34 \pm 0.15$  | $0.77 \pm 0.05$   |

| 600  | $1.46 \pm 0.09$     | $1.27 \pm 0.15$     | $0.77 \pm 0.05$     | $1.44 \pm 0.09$   | $1.23 \pm 0.18$  | 0.77±0.05         |

**Table 7.** Average overhead with standard deviation for 30 tasks scheduled on 2 RRs at size  $600 \times 600$ . Preemptive vs nonpreemptive with partial reconfiguration (left), preemptive with full reconfiguration vs preemptive with partial reconfiguration (right).  $\overline{T}$  is the average overhead for preemption with partial reconfiguration and  $\overline{F_T}$  is the overhead of preemption with full reconfiguration, where T can be B (busy), M (medium), I (idle).

| size | $\overline{B}$    | $\overline{M}$    | $\overline{I}$    | $\overline{F_B}$ | $\overline{F_M}$ | $\overline{F_I}$  |

|------|-------------------|-------------------|-------------------|------------------|------------------|-------------------|

| 200  | $0.10 {\pm} 0.05$ | $0.00 {\pm} 0.01$ | $-0.00 \pm 0.01$  | 0.25±0.30        | 0.27±0.23        | 0.28±0.22         |

| 300  | $0.06 \pm 0.07$   | $0.02 {\pm} 0.01$ | $0.01 {\pm} 0.01$ | $0.28 \pm 0.27$  | $0.28 \pm 0.23$  | $0.28 \pm 0.22$   |

| 400  | $0.03 \pm 0.02$   | $0.02 \pm 0.02$   | $0.01 \pm 0.01$   | 0.27±0.24        | $0.28 \pm 0.22$  | $0.28 \pm 0.21$   |

| 500  | $0.03 \pm 0.02$   | $0.02 \pm 0.03$   | $0.01 \pm 0.02$   | 0.26±0.22        | $0.27 \pm 0.21$  | $0.27 \pm 0.21$   |

| 600  | $0.01 {\pm} 0.01$ | $0.04 \pm 0.03$   | $0.01 {\pm} 0.01$ | 0.24±0.21        | $0.26 \pm 0.21$  | $0.27 {\pm} 0.20$ |

higher, leading to more reconfigurations. Note that the worst overhead obtained is  $10 \pm 5$  %, for size  $200 \times 200$  in and the busy rate of arrival. However, it becomes negligible for larger problem sizes, even in busy scenarios.

# 6 Conclusions

This work presented in this paper describes a task-based abstraction for programming FPGAs that enables task preemption using dynamic partial reconfiguration. Integrating with the existing Controller framework, we provide an approach which abstracts the low-level details around generation of a dynamic partial reconfiguration capable system and provide the programmer with a high-level API for simple management of kernel launch, data transfer and transparent book-keeping for context preemption. Furthermore, we provide transparent support for task scheduling by leveraging the default full reconfiguration mechanism that allows us to compare against the use of dynamic partial reconfiguration.

In this paper we have demonstrated that our approach enhances flexibility by reducing the service time of urgent tasks due to the ability to dynamically swap tasks in and out. The overhead of preemptive against non-preemptive scheduling when using dynamic partial reconfiguration is 10  $\pm$  5% in the worst case for two reconfigurable regions, but it becomes negligible for larger problem sizes. Our experiments also demonstrate significant performance gains over the traditional use of full reconfiguration, illustrating that the use of a partial reconfiguration approach is crucial if one is to achieve low latency and flexible task scheduling on FPGAs. For future work we plan to port our approach to the AMD Xilinx Versal architecture, which is not only a much larger FPGA which will be able to contain more complex tasks, but furthermore it will be interesting to explore how the hardened elements, such as the Network on Chip (NoC), interact with our approach. It will also be interesting to study task migration between FPGAs and othe architectures such as GPUs and CPUs, potentially moving running tasks to a more suited architecture mid-execution. Lastly we plan to explore the potential for reducing the overheads of dynamic partial reconfiguration by leveraging a custom ICAP controller, as the one provided by AMD Xilinx is only capable of exploiting up to 2.5% of the port's bandwidth [24] and thus results in significantly slower reconfiguration performance.

# 7 Acknowledgements

The authors acknowledge EPCC at the University of Edinburgh and EPSRC who have funded this work and the ExCALIBUR H&ES FPGA testbed for providing the FPGA compute resource. This research has been partially funded by Junta de Castilla y León - FEDER Grants, project PROPHET-2 (VA226P20).

# References

- [1] [n. d.]. Intel oneAPI. https://www.oneapi.com/spec/. [Online; accessed 9-May-2022].

- [2] [n.d.]. TOP500. https://www.top500.org/. [Online; accessed 9-May-2022].

- [3] 2022. Vivado Design Suite User Guide: Programming and Debugging. https://docs.xilinx.com/r/en-US/ug908-vivado-programming-

debugging/Configuration-Failures-in-Master-Mode. [Online; accessed 15-January-2022].

- [4] Cédric Augonnet, Samuel Thibault, Raymond Namyst, and Pierre-André Wacrenier. 2009. StarPU: a unified platform for task scheduling on heterogeneous multicore architectures. In *European Conference on Parallel Processing*. Springer, 863–874.

- [5] Eduard Ayguadé, Nawal Copty, Alejandro Duran, Jay Hoeflinger, Yuan Lin, Federico Massaioli, Xavier Teruel, Priya Unnikrishnan, and Guansong Zhang. 2008. The design of OpenMP tasks. *IEEE Transactions on Parallel and Distributed Systems* 20, 3 (2008), 404–418.

- [6] Marc Perelló Bacardit, Leonardo Bautista-Gomez, and Osman Unsal. 2021. FPGA Checkpointing for Scientific Computing. In 2021 IEEE 27th International Symposium on On-Line Testing and Robust System Design (IOLTS). IEEE, 1–7.

- [7] N. Brown. 2020. Exploring the acceleration of Nekbone on reconfigurable architectures. In 2020 IEEE/ACM International Workshop on Heterogeneous High-performance Reconfigurable Computing (H2RC). IEEE, 19–28.

- [8] Nick Brown. 2021. Porting incompressible flow matrix assembly to FP-GAs for accelerating HPC engineering simulations. In 2021 IEEE/ACM International Workshop on Heterogeneous High-performance Reconfigurable Computing (H2RC). IEEE, 9–20.

- [9] Nick Brown and David Dolman. 2019. It's all about data movement: Optimising FPGA data access to boost performance. In 2019 IEEE/ACM International Workshop on Heterogeneous High-performance Reconfigurable Computing (H2RC). IEEE, 1–10.

- [10] Javier Bueno, Judit Planas, Alejandro Duran, Rosa M Badia, Xavier Martorell, Eduard Ayguade, and Jesús Labarta. 2012. Productive programming of GPU clusters with OmpSs. In 2012 IEEE 26th International Parallel and Distributed Processing Symposium. IEEE, 557–568.

- [11] Jaume Bosch et al. 2018. Application acceleration on FPGAs with OmpSs FPGA. In 2018 Int. Conf. on Field-Programmable Tech. IEEE, 70–77.

- [12] Raúl Nozal et al. 2020. EngineCL: Usability and Performance in Heterogeneous Computing. Future Gen. Comp. Systems 107 (2020), 522–537.

- [13] Johannes Menzel, Christian Plessl, and Tobias Kenter. 2021. The Strong Scaling Advantage of FPGAs in HPC for N-body Simulations. ACM Transactions on Reconfigurable Technology and Systems (TRETS) 15, 1 (2021), 1–30.

- [14] Ana Moreton-Fernandez, Hector Ortega-Arranz, and Arturo Gonzalez-Escribano. 2018. Controllers: An abstraction to ease the use of hardware accelerators. *The International Journal of High Performance Computing Applications* 32, 6 (2018), 838–853.

- [15] Ana Moreton-Fernandez, Eduardo Rodriguez-Gutiez, Arturo Gonzalez-Escribano, and Diego R Llanos. 2017. Supporting the Xeon Phi Coprocessor in a Heterogeneous Programming model. In *European Conference on Parallel Processing*. Springer, 457–469.

- [16] Aaftab Munshi. 2009. The OpenCL specification. In 2009 IEEE Hot Chips 21 Symposium (HCS). IEEE, 1–314.

- [17] N. Brown. 2019. PYNQ API: C API for PYNQ FPGA board. https: //github.com/mesham/pynq\_api. [Online; accessed 20-June-2021].

- [18] OpenACC. [n.d.]. The OpenACC Application Programming Interface. https://www.openacc.org/sites/default/files/inline-images/ Specification/OpenACC-3.2-final.pdf. [Online; accessed 19-May-2022].

- [19] Khoa Dang Pham, Anuj Vaishnav, Malte Vesper, and Dirk Koch. 2018. ZUCL: a ZYNQ Ultrascale+ framework for OpenCL HLS applications. In FSP Workshop 2018; Fifth International Workshop on FPGAs for Software Programmers. VDE, 1–9.

- [20] Gabriel Rodriguez-Canal, Nick Brown, Yuri Torres, and Arturo Gonzalez-Escribano. 2023. Programming abstractions for preemptive scheduling in FPGAs using partial reconfiguration. In *European Conference on Parallel Processing*. Springer, 91–103.

- [21] Gabriel Rodriguez-Canal, Yuri Torres, Francisco J Andújar, and Arturo Gonzalez-Escribano. 2021. Efficient heterogeneous programming with FPGAs using the Controller model. *The Journal of Supercomputing* 77, 12 (2021), 13995–14010.

- [22] Christian R Trott, Damien Lebrun-Grandié, Daniel Arndt, Jan Ciesko, Vinh Dang, Nathan Ellingwood, Rahulkumar Gayatri, Evan Harvey, Daisy S Hollman, Dan Ibanez, et al. 2021. Kokkos 3: Programming model extensions for the exascale era. *IEEE Transactions on Parallel* and Distributed Systems 33, 4 (2021), 805–817.

- [23] Anuj Vaishnav, Khoa Dang Pham, and Dirk Koch. 2019. Heterogeneous resource-elastic scheduling for CPU+ FPGA architectures. In Proceedings of the 10th International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies. ACM, 1–6.

- [24] Kizheppatt Vipin and Suhaib A Fahmy. 2018. FPGA dynamic and partial reconfiguration: A survey of architectures, methods, and applications. ACM Computing Surveys (CSUR) 51, 4 (2018), 1–39.

- [25] Timothy Wheeler, Paul Graham, Brent Nelson, and Brad Hutchings. 2001. Using design-level scan to improve FPGA design observability and controllability for functional verification. In *International Conference on Field Programmable Logic and Applications*. Springer, 483–492.

- [26] Xilinx. [n.d.]. Vivado Design User Suite Guide Dynamic Function eXchange. https://bit.ly/3MEDZTI. [Online; accessed 9-May-2022].