# CiFHER: A Chiplet-Based FHE Accelerator with a Resizable Structure

Sangpyo Kim Department of Intelligence and Information Seoul National University Seoul, South Korea vnb987@snu.ac.kr

Jaeyoung Choi Department of Intelligence and Information Seoul National University Seoul, South Korea sojae0518@snu.ac.kr Jongmin Kim Interdisciplinary Program in Artificial Intelligence Seoul National University Seoul, South Korea jongmin.kim@snu.ac.kr

> Jung Ho Ahn Department of Intelligence and Information Seoul National University Seoul, South Korea gajh@snu.ac.kr

Abstract—Fully homomorphic encryption (FHE) is in the spotlight as a definitive solution for privacy, but the high computational overhead of FHE poses a challenge to its practical adoption. Although prior studies have attempted to design ASIC accelerators to mitigate the overhead, their designs require excessive chip resources (e.g., areas) to contain and process massive data for FHE operations. We propose CiFHER, a chiplet-based FHE accelerator with a resizable structure, to tackle the challenge with a cost-effective multi-chip module (MCM) design. First, we devise a flexible core architecture whose configuration is adjustable to conform to the global organization of chiplets and design constraints. Its distinctive feature is a composable functional unit providing varying computational throughput for the number-theoretic transform, the most dominant function in FHE. Then, we establish generalized data mapping methodologies to minimize the interconnect overhead when organizing the chips into the MCM package in a tiled manner, which becomes a significant bottleneck due to the packaging constraints. This study demonstrates that a CiFHER package composed of a number of compact chiplets provides performance comparable to state-of-the-art monolithic ASIC accelerators while significantly reducing the package-wide power consumption and manufacturing cost.

Index Terms—Fully homomorphic encryption, Domain-specific architecture, Chiplet

# I. INTRODUCTION

Privacy is no longer merely a virtue but a critical objective for corporates due to recently established strict data privacy policies, such as the California Consumer Privacy Act (CCPA) and the EU General Data Protection Regulation (GDPR). For example, Apple's App Tracking Transparency (ATT) policy cost technology companies \$15.8 billion in 2022 [65].

*Fully homomorphic encryption (FHE)* is emerging as an attractive solution providing strong privacy guarantees. FHE enables an unlimited number of computations directly on encrypted data without decryption; thus, it allows users to safely offload services without disclosing private information. Numerous studies have shown its applicability to practical privacy-preserving applications, including genomics [46], [56], biometrics [60], [76], and machine learning (ML) tasks [14], [24], [37], [61], [62].

There are two major competing classes of FHE based on the learning with errors (LWE) computational problem: one based on the ring LWE variant (e.g., BGV [15], BFV [16], [33], and CKKS [22] schemes) and the other based on the torus LWE (e.g., FHEW [31] and TFHE [23] schemes). This work focuses on the former class and, specifically, CKKS [22], which stands out among the state-of-the-art FHE schemes due to its relatively high performance [9] and

the ability to encrypt complex vectors. Such benefits make CKKS suitable for numerous practical tasks, particularly ML tasks.

Still, alleviating the computational and memory overhead of FHE is a challenging prerequisite for its widespread use as FHE workloads run over  $10,000 \times$  slower than their unencrypted counterparts [52], [81]. To mitigate the overhead, prior work has attempted hardware acceleration [2], [11], [34], [51], [55], [58], [80], [81], [95]. In particular, ASIC FHE accelerator proposals [55], [58], [81] achieved considerable performance enhancements. For example, ARK [55] can perform a CIFAR-10 CNN inference in 0.125 seconds with the ResNet-20 model, which takes 2,271 seconds in a single-threaded CPU [61]. However, these remarkable speedups owe to the massive chip area usage (373.6–472.3mm<sup>2</sup>) that enables the deployment of unconventionally large on-chip memory capacity (256–512MB) and substantial amounts of computational logic.

As prior massive FHE accelerator designs are prohibitively costly to realize, we turn to using a *multi-chip module (MCM)*. The cost of a chip skyrockets with the die area in recent technology nodes due to severe degradation in yield and high design complexity [45], [84]. By splitting a monolithic chip design into several small *chiplets*, an MCM drastically reduces the cost and becomes a scalable solution in the post-Moore era. Abundant studies [8], [43], [64], [84], [89], [96], including commercial chips [69], [70], [73], [94], have demonstrated the efficiency of MCMs in high-performance computing (HPC).

We propose CiFHER, a flexible and cost-effective MCM architecture for FHE. First, we propose a core architecture that is resizable at design time. Our *composable number-theoretic transform (NTT) unit*, which can provide varying computational throughput depending on the package configuration and technology demands, provides the resizing flexibility, enabling architects to split a monolithic design into multiple cores with a best-fit size for a given die area budget.

Given a chiplet architecture, we construct efficient package configurations of CiFHER, focusing on minimizing the high network cost of MCMs. Due to the technical constraints of a *network on package (NoP)* connecting chiplets, an MCM architecture becomes bottlenecked by the NoP communication among the cores; data communication has been a source of bottleneck even in prior monolithic accelerators, and MCM intensifies the problem. We address the problem by developing generalized data mapping methodologies optimized for the many-core MCM architecture. We also devise a *limb duplication* algorithm, which significantly reduces data communication during *base conversion (BConv)*, the second most dominant function in FHE.

Based on the analysis, we discover balanced combinations of the individual chiplet design, data mapping, and FHE algorithms under various design constraints. These optimizations enable CiFHER to achieve comparable performance to prior monolithic chips; a CiFHER package with 16 cores performs an encrypted CIFAR-10 CNN inference using the ResNet-20 model [61] in 0.189 seconds. Depending on the area budget, CiFHER provides various core configurations, ranging from four 47.08mm<sup>2</sup> core dies to sixty-four 4.28mm<sup>2</sup> core dies in default settings.

Overall, this work makes the following key contributions:

- We design a flexible chiplet core with a composable NTT unit, which allows the distribution of memory and compute resources across multiple dies while taking advantage of the vector NTT unit.

- We introduce generalized data mapping methodologies on a tiled FHE accelerator to resolve the NoP communication bottleneck of MCMs.

- We propose limb duplication, an algorithmic optimization tailored to the MCM design, reducing the amount of die-to-die communication, which would have caused significant latency and energy overhead.

# II. BACKGROUND & MOTIVATION

# A. Fully Homomorphic Encryption (FHE)

Homomorphic encryption (HE) is classified into leveled HE (LHE) and fully HE (FHE) depending on the problem size. LHE supports only a limited number of operations (ops) and is usually used in conjunction with other cryptographic protocols [42], [53]. In contrast, FHE solely supports an unlimited number of ops. A defining feature of FHE is *bootstrapping*. The LWE problem [77] forms the cryptographic basis for state-of-the-art HE schemes, and relies on the error in encryption for its security. When performing HE ops on encrypted data, the magnitude of errors increases, threatening data integrity unless managed properly. Bootstrapping reduces the magnitude of errors, thus allowing more HE ops performed. In a typical use case, a bootstrapping op is inserted after every predetermined number of HE ops is applied to the encrypted data.

# B. CKKS FHE Scheme

We briefly describe the CKKS FHE scheme, the main target of this paper. During CKKS encryption, a (vector) message composed of n numbers is first packed into a degree-(N-1) integer polynomial referred to as plaintext, which is an element of a cyclotomic polynomial ring  $\mathcal{R}_Q = \mathbb{Z}_Q[X]/(X^N + 1)$  with the degree  $N \ge 2n$  and the modulus Q. All integer ops are performed modulo-Q in  $\mathcal{R}_Q$ . A plaintext is encrypted into a ciphertext composed of two polynomials in  $\mathcal{R}_Q$ . We denote polynomials with bold characters (e.g., v), and ciphertexts encrypting polynomials with brackets ([v]). Then, the encryption of v can be formulated as  $[v] = (v_1, v_2) \in \mathcal{R}_Q^2$ . A high N value around  $2^{15}-2^{17}$  and Q as large as  $2^{1500}$  are utilized

A high N value around  $2^{15}-2^{17}$  and Q as large as  $2^{1500}$  are utilized to meet the security constraints of FHE [7], [28]. To handle such a large Q, residue number system (RNS) is utilized [21]. Q is set to the product of L number of small primes  $(q_i)$ , such that  $Q = \prod_{i=1}^{L} q_i$ . Then, each coefficient c of a polynomial is represented by an Ltuple of small residues (c mod  $q_1, \dots, c \mod q_L$ ). Each row of the matrix corresponding to the prime  $q_i$  is referred to as limb, which can be regarded as a polynomial in  $\mathcal{R}_{q_i} = \mathbb{Z}_{q_i}[X]/(X^N + 1)$ . Using RNS, modulo-Q ops between polynomials having large coefficients are replaced by a set of L pairwise modulo- $q_i$  ops between limbs having small word-sized coefficients. Also, the modulus can change over HE ops such that  $Q_{\ell} = \prod_{i=1}^{\ell} q_i$  is used at a particular moment. As a result, a polynomial at that moment is represented as an  $\ell \times N$  matrix of residues.

In a client-server scenario of FHE, the server performs  $HE \ ops$  to manipulate the message encrypted in a ciphertext. Mult/add between two ciphertexts (HMult/HAdd) or between a ciphertext and a plaintext (PMult/PAdd) are some of the most frequently used HE ops. Also, it is often required to change the data order inside the message vector composed of n numbers. Such data reordering can be performed with an HRot op, which evaluates the cyclic rotation of the message encrypted inside a ciphertext. Among these HE ops, HMult and HRot are the most computationally expensive due to complex *key-switching* procedures involved in them. Key-switching is a procedure to multiply a polynomial with *evaluation keys* (evks), which are special types of ciphertexts.

# C. Primary Functions of CKKS

We defer a more detailed explanation of each HE op to prior work [12], [21], [22], [38] and instead break down HE ops into *primary functions* to discuss their computational aspects.

Number-theoretic transform (NTT): To reduce the complexity of a polynomial mult, NTT is utilized. A polynomial mult in  $\mathcal{R}_{q_i}$  is equivalent to a negacyclic convolution between the coefficients. NTT, a type of discrete Fourier transform, and its inverse (iNTT) are defined for each  $q_i$ . (i)NTT reduces the overall complexity of the convolution into  $O(N \log N)$  for each limb by adopting a fast Fourier transform (FFT) algorithm [26].

**Base conversion (BConv)**: The modulus Q changes frequently over HE ops, which requires BConv to be performed on polynomials. For example, for a polynomial  $\mathbf{v} \in \mathcal{R}_{Q_{\ell}}$ , we often need to change its modulus to an *auxiliary modulus*  $P = \sum_{i=1}^{K} p_i$ . For this situation, 96% of BConv computation is spent on a matrix-matrix mult between a pre-computed *BConv table* (a  $K \times \ell$  matrix) and  $\mathbf{v}$  (an  $\ell \times N$ matrix) [55]. We obtain a new  $\mathbf{v} \in \mathcal{R}_P$  through BConv.

**Automorphism** ( $\phi_r$ ): During HRot, automorphism, which is a data permutation function, is performed. The *i*-th coefficient of a polynomial is mapped to the  $(i \cdot 5^r \mod N)$ -th position.

**Element-wise or constant functions**: Other than the aforementioned primary functions, we only perform element-wise mult/add or constant mult/add on polynomials for HE ops.

FHE computations are extremely expensive, mainly attributed to key-switching, which involves multiple (i)NTTs and BConvs. (i)NTT and BConv account for more than 80% of the total computations in CKKS [55], [58]. Thus, enhancing (i)NTT and BConv performance is essential to FHE acceleration.

# D. Previous ASIC FHE Accelerators

F1 [80] is the first ASIC accelerator that reports bootstrapping performance. However, F1 targets small parameters of  $N = 2^{14}$ and L = 16, with which it only partially supports bootstrapping. Subsequent accelerator proposals, BTS [58], CraterLake [81], and ARK [55], fully support bootstrapping by targeting larger parameters of  $N = 2^{16}-2^{17}$  and L = 24-60. BTS places 2,048 processing elements (PEs) in a grid and connects them by global wires that span the whole chip. Each PE contains a *butterfly unit* for (i)NTT, a multiply-accumulate unit for BConv, and a multiplier and an adder for element-wise functions. A butterfly unit is capable of performing the *butterfly ops* required in (i)NTT, which are shown in Eq. 1. ARK and CraterLake develop upon F1's design of placing  $\sqrt{N}$ parallel *lanes* in a cluster (CraterLake refers to it as lane group) that feeds data into massive vector NTT units (NTTUs). A vector NTTU contains  $\frac{1}{2}\sqrt{N}\log N$  butterfly units, placed in an organization directly reflecting the four-step FFT dataflow [10]. ARK deploys four NTTUs, and CraterLake 16.

I. Butterfly<sub>NTT</sub>

$$(a, b, w) = (a + b \cdot w, a - b \cdot w)$$

II. Butterfly<sub>INTT</sub> $(a, b, w) = (a + b, (a - b) \cdot w)$  (1)

To tackle the increased number of computations and size of the working set when using large parameters, CraterLake, BTS, and ARK all rely on enormous amounts of computational logic and on-chip memory capacity; the latter even reaches 256–512MB. These designs end up using massive chip resources, utilizing a monolithic die sized 373.6–472.3mm<sup>2</sup> and dissipating up to 317W of power.

#### E. Multi-Chip Module (MCM)

MCM is a promising solution for scaling chips in the post-Moore era. By organizing a module with multiple small dies, referred to as chiplets, and connecting them using advanced packaging technologies providing high bandwidth on-package interconnects [17], [41], [66], MCMs reduce the area of an individual die. Because the design and fabrication cost of a die substantially drops as the die area is reduced [45], [84], MCMs can greatly reduce the total cost. With yield and technology scaling declining over chip fabrication generations, MCMs have become one of the few left options for scaling systems. Recent Intel [73] and AMD [69], [70] CPUs are notable examples of MCMs; multiple chiplets containing several CPU cores and cache memory are integrated into a single package using EMIB [66] or CoWoS [41] packaging technologies. Also, numerous domain-specific architectures utilizing MCMs have been proposed [43], [64], [84], [88], [89]. Moreover, MCMs have been realized at various area granularity, ranging from AMD's high-end 74mm<sup>2</sup> die [70] to 6mm<sup>2</sup> die of Simba [84].

These recent trends motivate us to design an MCM architecture for cost-effective FHE acceleration. By using MCMs, we can enjoy the aforementioned benefits coming from a significant reduction in individual die areas. Also, this approach is highly scalable as we can reuse the same design for each chiplet and place multiple chiplets to facilitate developing various MCM FHE accelerators with different computational throughput and bandwidth required by the technology constraints and the purpose of use. Prior ASIC FHE accelerator proposals include high bandwidth memories (HBMs), already assuming the use of advanced packaging for connecting HBMs to the chip. The same packaging can be utilized to connect multiple chiplets with little additional cost [54]. We utilize the open specification of Universal Chiplet Interconnect Express (UCIe) [91] to design and evaluate the MCM FHE accelerator.

# **III. CIFHER MICROARCHITECTURE**

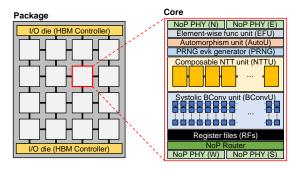

To reduce the high cost of a monolithic chip design, we propose CiFHER, an MCM architecture for FHE acceleration. CiFHER has a tiled architecture with multiple chiplet *cores* connected by a mesh NoP. Fig. 2 depicts the package and core organization of CiFHER. The main challenge in designing an MCM architecture lies in reducing the NoP pressure. As deployable bandwidth and topology are heavily restricted by the technology constraints of the NoP, we devise novel data mapping methodologies (§IV) and algorithms (§V) addressing the high latency and low bandwidth of NoP. Nonetheless, prior to determining the configuration of the MCM package, we will first architect the internals of a chiplet core.

## A. Core Organization

Prior accelerators either utilize little (PE in BTS) or big (cluster or lane group in F1, ARK, and CraterLake) cores without providing much flexibility in design. In contrast, we design the cores of CiFHER to have varying computational throughput, which can be adjusted at design time depending on the package configuration.

A core comprises a *composable NTTU*, a *systolic BConv unit* (*BConvU*), an *automorphism unit* (*AutoU*), an *element-wise function unit* (*EFU*), a *PRNG* evk generator (*PRNG*), a router and PHYs for NoP, and register files (RFs). We adopt the vector architecture utilized in F1, CraterLake, and ARK, where we place multiple parallel lanes in a core. Each lane has a dedicated RF space not accessible by the other lanes, which enables maximizing parallelism with low costs for synchronization and arbitration. The vector architecture has shown effectiveness in reducing the communication overhead and the RF bandwidth pressure, the major bottlenecks in FHE.

By effectively combining components from different vector accelerators with proper modifications, CiFHER provides an improved core design for FHE accelerators. In particular, we adopt the distributed RF, systolic BConvU, and AutoU structures from ARK, and adopt PRNG from CraterLake. A systolic BConvU is composed of multiple multiply-accumulate (MAC) units, forming an outputstationary systolic array.

To achieve a flexible core design, we aim to adjust configurations, particularly the number of lanes. While most functional units (FUs) readily adapt to lane count and throughput goals, the preceding vector NTTU presents a challenge. This critical vector core component is a substantial computing unit with its 2,048 butterfly units locked into a fixed organization.

The inflexibility of previous large-scale NTTU designs severely limits our design options, ultimately harming hardware efficiency. To manage the on-chip memory bandwidth demands of NTT computation, prior studies rely on deeply pipelined NTTU designs. These treat a length-N polynomial as an  $\sqrt{N} \times \sqrt{N}$  matrix, performing the NTT in four steps: column-wise  $\sqrt{N}$ -point NTT, twisting, transposition, and row-wise  $\sqrt{N}$ -point NTT. With N reaching  $2^{16} - 2^{17}$ , this vector NTTU becomes bulky and expensive. Worse, its singleconfiguration design forces us to use large chiplets to accommodate it, regardless of the actual computational throughput needed. This leads to underutilized NTTUs, creating an imbalanced and inefficient design for MCMs.

#### B. Composable NTT Unit

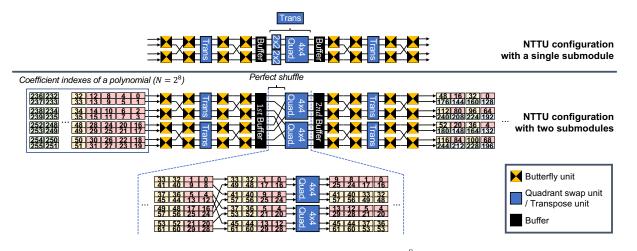

We devise a composable NTTU supporting various configurations with the number of lanes adjustable from 16 to 256. We also regard a length-N polynomial as a  $\sqrt{N} \times \sqrt{N}$  matrix and perform  $\sqrt{N}$ -point (i)NTT along the rows and then along the columns in sequence, but additionally apply the four-step FFT dataflow [10] to each of the rowand column-direction (i)NTTs. We obtain a compact NTTU spanning  $\sqrt[4]{N} = 16$  lanes shown in Fig. 1 (simplified to  $N = 2^8$ ), which we refer to as the *submodule* of our NTTU.

Up to 16 submodules can be stacked to deliver higher computational throughput for (i)NTT, providing flexibility for our design space exploration. We devise a method to combine multiple submodules to have them collaboratively perform (i)NTT on a limb by performing a perfect shuffle [87] between the submodules. The perfect shuffle enables the rearrangement of dispersed data across various submodules by transforming it into a sequence that can be effectively transposed using subsequent quadrant swap units. An exemplar two-submodule NTTU configuration for  $N = 2^8$  performing NTT is shown in Fig. 1. We regard a length- $2^8$  polynomial as a  $16 \times 16$

Figure 1: Exemplar configurations of a composable NTT unit, simplified to  $N = 2^8$ . A submodule, the smallest unit occupying  $\sqrt[4]{N}$  lanes, is shown above. A two-submodule configuration and its NTT process for a length-N polynomial are shown below.

Figure 2: The CiFHER package consists of multiple core chiplets and two I/O dies handling HBM. A core comprises functional units (FUs), register files (RFs), and networking components.

Table I: Target parameters of CiFHER.

| Param. | Ν        | L          | K          |                       | P                     | Security        |

|--------|----------|------------|------------|-----------------------|-----------------------|-----------------|

| Descr. | Degree   | # of $q_i$ | # of $p_i$ | $\prod_{i=1}^{L} q_i$ | $\prod_{i=1}^{K} p_i$ | (bits)          |

| Value  | $2^{16}$ | $\leq 48$  | 12         | $\leq 2^{1218}$       | $2^{336}$             | $\geq 128$ [12] |

matrix. The first half of a submodule performs a four-step NTT on a row (data indices: 0-15/16-32). It starts from stride-1 butterfly ops and ends with stride-8 ops to perform 16-point NTT on a row. Then the buffering and shuffling steps in the middle redistribute the data between different submodules so that each submodule holds data elements with stride 16 in the second buffer; i.e., each submodule holds the elements of a column. Finally, the second half of a submodule performs a four-step NTT on a column (data indices: 0-240/4-244, stride 16) by starting from stride-16 butterfly ops and ending with stride-128 ops to perform 16-point NTT on a column.

Our composable NTTU also allows up to  $\sqrt[4]{N} = 16$  cores to perform (i)NTT of a limb together. In this case, data exchange between the collaborating cores occurs after the buffering and shuffling steps in the case of NTT.

#### C. Word Length & Logic Optimization

We choose 32 bits as the word length to use in CiFHER as it is beneficial to use short word lengths for the efficiency of logical operations. While BTS and ARK utilize a word length of 64 bits, which has been traditionally used in CKKS libraries [20], [27], [32], F1 (32 bits), CraterLake (28 bits), and FPGA FHE accelerators (FAB [2] (54 bits) and Poseidon [95] (32 bits)) utilize shorter word lengths. Despite using a relatively short word length, we maintain high precision by the methods in [1] to utilize high scales ranging from  $2^{47}$  to  $2^{55}$ . Table I tabulates our target parameters.

We utilize the word-level Montgomery reduction circuit proposed in [67] with further enhancements using the signed Montgomery reduction algorithm in [82]. The circuit is utilized for all modular reduction circuits in CiFHER, including EFUs, NTTUs, PRNGs, and BConvUs.

**Systolic BConvU:** By using a 32-bit word length, more limbs are utilized (higher L and K) than 64-bit ARK. Thus, to provide higher word-level throughput for BConv, we use a longer  $1 \times 12$  BConv configuration per lane by default.

**EFU:** Inside an EFU, we place multiple modular multipliers, modular adders, and element-wise op circuits for specific purposes required in FHE (e.g., double-word accumulation and reduction). An EFU can perform compound element-wise ops to reduce the pressure on RFs.

#### IV. DATA MAPPING METHODOLOGY

#### A. Tiled Architecture

The technology constraints of NoP enforce CiFHER to be a tiled architecture connected by a mesh network. Due to the short channel reach of an advanced interface [91], a complex network topology that requires connections between distant nodes is less suitable for MCMs. Thus, we fix the topology to 2D mesh (see Fig. 2). Also, due to the high cost of NoP communication, we set the default bisection bandwidth of the entire package to 2TB/s, several to an order of magnitude lower than that of CraterLake (29TB/s) or ARK (8TB/s).

Prior FHE accelerators co-design the data mapping method with the network on chip (NoC) organization. They design complex NoC structures using direct connections between distant nodes with high bandwidth and uniform communication time. However, in an MCM architecture with a mesh network, communication latency between nodes is non-uniform, as distant nodes are separated by multiple hops. Lagging data from distant nodes causes others to wait idly, degrading the overall performance [84]. The low bandwidth of NoP exacerbates this problem. Therefore, we delve into data mapping methodologies to reduce the pressure of the network.

#### B. Combining Data Mapping Methods

Prior data mapping methods can be classified into *coefficient* scattering and *limb scattering*. Coefficient scattering is a method of distributing N coefficients of each limb equally to the entire computing units. By contrast, in limb scattering, each prime and the corresponding limbs are allocated to a specific computing unit. BTS and CraterLake use coefficient scattering, whereas F1 and ARK mostly use limb scattering. ARK temporarily switches to coefficient scattering during BConv, which we detail in V-A.

Due to the conflicting data access patterns of HE ops, core-tocore communication is inevitable regardless of the data mapping method. (i)NTT and BConv, the two most dominant primitives, require different data mapping due to their data access patterns. For a polynomial, expressed as an  $\ell \times N$  matrix, (i)NTT can be separately applied to each of  $\ell$  limbs, favoring limb scattering. By contrast, as BConv is mostly a matrix-matrix mult with a  $K \times \ell$  BConv table (see §II-C), data access is performed along the columns of a polynomial and makes coefficient scattering a better option. Thus, data exchange between cores is required either during (i)NTT (coefficient scattering) or BConv (limb scattering).

In an accelerator with many cores, both data mapping methods have limitations. As the number of limbs ( $\ell$ ) vary over HE ops, it is difficult to distribute the limbs equally to cores without causing fragmentation issues in limb scattering. A core will be assigned fewer limbs than others depending on  $\ell$  and wait idly for others to finish processing. In contrast, coefficient scattering is free from fragmentation issues because the degree of a polynomial (N) does not change. However, coefficient scattering has a scaling limit due to quadratic growth in the number of transferred packets with increasing cores. For example, during (i)NTT with c cores, coefficient scattering results in all-to-all data exchange between the cores, requiring a total of c(c-1) packets to be transferred. These issues become more severe as more cores participate in the distribution. Also, with more cores, additional performance degradation from long tail latency in lagging data occurs.

Therefore, in an MCM architecture with many cores and restrained NoP bandwidth, the combined use of limb scattering and coefficient scattering enhances performance, even with the increased total amount of transferred data due to performing data exchanges for both (i)NTT and BConv. We partition a polynomial in both limb and coefficient directions by dividing cores into *limb clusters* and *coefficient clusters*. A limb cluster is a set of cores each holding an evenly distributed subset of the coefficients of a limb. By contrast, the cores in a coefficient cluster partition the residues of a coefficient corresponding to different primes. Then, (i)NTT or BConv only incurs data exchange within each limb cluster or coefficient cluster, reducing the number of cores participating in the exchange. Thus, combining two data mapping methods suffers less from the aforementioned issues, leading to performance enhancement.

#### C. Generalized Data Mapping for a Tiled FHE Accelerator

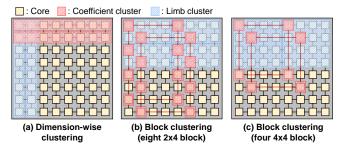

We introduce two generalized data mapping methods that combine coefficient scattering and limb scattering for mapping HE ops to a tiled architecture: *dimension-wise clustering* and *block clustering*. Dimension-wise clustering binds the cores on the same vertical line into a limb cluster and the cores on the same horizontal line into a coefficient cluster (or in the oppositice directions) on a mesh network. Fig. 3a shows an example of dimension-wise clustering on an  $8 \times 8$  mesh. This distribution method has the advantage that each data exchange process of (i)NTT and BConv can be performed without interference because data movement occurs in different axial

Figure 3: Generalized data mapping methods of CiFHER with 64 cores: (a) dimension-wise clustering and block clustering for two different exemplar block sizes of (b)  $2 \times 4$  and (c)  $4 \times 4$ .

directions. However, the configuration is fixed for a given mesh shape, potentially sharing the same limitations of prior mapping methods when the mesh shape is skewed.

Block clustering is a more generalized mapping method that places limb clusters in the form of blocks with an arbitrary size, and forms coefficient clusters with the cores in the same position within each block. Fig. 3b and Fig. 3c show configurations dividing an  $8 \times 8$  mesh into eight  $2 \times 4$  or four  $4 \times 4$  limb cluster blocks. Unlike dimensionwise clustering, various block clustering configurations are possible by changing the size of a block. We refer to the configuration on a  $d_x \times d_y$  mesh using a  $b_h \times b_w$  block size as  $d_x \times d_y$ -BK- $b_h \times b_w$ . Dimension-wise clustering is simply denoted as  $d_x \times d_y$ -DW, which is indeed a special variant of block clustering; e.g., Fig. 3a can be expressed as  $8 \times 8$ -BK- $8 \times 1$ . Also, limb scattering and coefficient scattering can be expressed as  $d_x \times d_y$ -BK- $1 \times 1$  and  $d_x \times d_y$ -BK $d_x \times d_y$ , respectively.

Determining the data mapping method of CiFHER is challenging as it requires considering various factors that have conflicting effects on its performance. In addition to the trade-offs discussed in §IV-B, generalized data mapping methods reduce the maximum number of hops a packet travels by restricting its destination to adjacent cores within a cluster. Also, it is challenging to balance the limb clusters and coefficient clusters; an unbalanced configuration would result in fragmentation or severe performance degradation as either (i)NTT or BConv ops must wait for the other to finish due to the dependency in common CKKS use cases. We account for these challenges by developing an extensive simulation tool for CiFHER, which we use for the evaluation in §VI.

# V. ALGORITHMIC OPTIMIZATIONS

# A. Limb Duplication for BConv

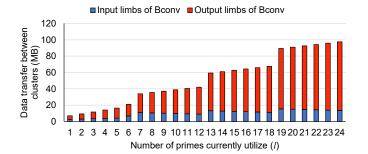

We propose a novel limb duplication algorithm, which duplicates the input limbs of BConv to reduce the amount of data communication caused by the redistribution of the output limbs during BConv. BConv requires gathering the residues from different cores. F1 uses parameters which allows performing BConv in parallel for each of the  $\ell$  limbs without redistribution of input data ( $\ell$  limbs) before BConv [20]. However, F1's method produces massive  $\ell^2$ output limbs, which need to be redistributed among cores. More recently proposed ARK adopts parameters that make BConv produce fewer limbs (roughly  $\ell \cdot \beta$  limbs for a small integer  $\beta$ ), which also significantly reduces the amount of computation [38]. However, as it becomes harder to parallelize BConv, ARK switches to coefficient scattering prior to BConv and switches back to limb scattering after BConv, inducing data redistribution of both input and output data of BConv. Fig. 4 shows the estimated amount of data transfer required for key-switching depending on  $\ell$  (the number of primes) when using

Figure 4: The amount of data transfer during key-switching using the method of ARK [55] under different  $\ell$  conditions.

ARK's method. As the number of input limbs is usually smaller than the number of output limbs, the output limbs of BConv account for most of the data transfer regardless of  $\ell$ .

To eliminate the data transfer required for the redistribution of generated limbs, limb duplication duplicates input limbs and broadcasts them to all the cores in a coefficient cluster so that each core holds the entire polynomial ( $\ell \times N$  matrix when only considering limb scattering). Then, each core performs BConv with a piece of the BConv table ( $K \times \ell$  matrix); e.g., a core in charge of the primes  $p_1, p_5$ , and  $p_9$  would only multiply the 1<sup>st</sup>, 5<sup>th</sup>, and 9<sup>th</sup> rows of the BConv table with the polynomial to obtain BConv results. As the output limbs already belong to the right owner, data redistribution after BConv is unnecessary.

However, limb duplication requires additional data transfer for broadcasting input limbs. The overhead of broadcasting varies depending on the ratio of the number of input limbs and the number of output limbs and the data mapping methodology. We can formulate the reduction in the number of transferred limbs compared to the ARK's method as in Eq. 2. broadcast<sub>overhead</sub> denotes the ratio of data transfer required for broadcasting compared to that required for even distribution and has a value greater than one.

$$\# limbs_{output} - \# limbs_{input} \times (broadcast_{overhead} - 1)$$

(2)

Eq. 2 must be larger than zero to make limb duplication beneficial. We selectively use limb duplication only when this condition is satisfied for each BConv. As there are much more output limbs than input limbs in general, limb duplication is usually beneficial for the reduction of communication.

#### B. An Eclectic Approach to Prior Algorithms

We adopt the state-of-the-art CKKS algorithms mostly from an FHE CPU library, Lattigo [32]. We combine the bootstrapping algorithms from [13], [19]. There are also accelerator-specific algorithms, which offers trade-offs between computation and off-chip memory access. They target evks and plaintext polynomials, which are loaded from the off-chip memory and are large in size, possibly inducing the off-chip memory bandwidth bottleneck. We explain how such algorithms can (or cannot) be applied to CiFHER.

**Minimum key-switching:** To reduce the memory access for evks, ARK builds on the algorithm proposed in [36] to suggest the minimum key-switching algorithm for HRot ops. Most of the evks are for HRot ops, which require a different  $evk_r$  for each rotation amount (r). The algorithm transforms a common computational pattern of sequential HRot ops with different rotation amounts forming an arithmetic progression into a recursive sequence of HRot ops with the same rotation amount equal to the common difference of the

| Table | II:  | Area    | breakdown   | of  | the   | default | configurations | of |

|-------|------|---------|-------------|-----|-------|---------|----------------|----|

| CiFHI | ER v | vith va | rying numbe | ers | of co | res.    |                |    |

|                                 | Area / core (mm <sup>2</sup> ) |                |                |                |                |  |

|---------------------------------|--------------------------------|----------------|----------------|----------------|----------------|--|

| Configuration                   | 4 core                         | 8 core         | 16 core        | 32 core        | 64 core        |  |

| Configuration                   | $(2 \times 2)$                 | $(2 \times 4)$ | $(4 \times 4)$ | $(4 \times 8)$ | $(8 \times 8)$ |  |

| Register files                  | 31.71                          | 15.86          | 7.93           | 3.96           | 1.98           |  |

| NTTU                            | 3.75                           | 1.82           | 0.88           | 0.43           | 0.22           |  |

| BConvU                          | 1.07                           | 0.65           | 0.44           | 0.34           | 0.28           |  |

| EFU                             | 0.72                           | 0.36           | 0.18           | 0.09           | 0.05           |  |

| AutoU                           | 2.32                           | 0.58           | 0.14           | 0.04           | 0.01           |  |

| PRNG                            | 0.71                           | 0.36           | 0.18           | 0.09           | 0.04           |  |

| Router/PHY                      | 6.80                           | 3.40           | 3.40           | 1.70           | 1.70           |  |

| Total                           | 47.08                          | 23.02          | 13.15          | 6.65           | 4.28           |  |

| Package area (mm <sup>2</sup> ) |                                |                |                |                |                |  |

| Cores                           | 188.32                         | 184.13         | 210.43         | 212.75         | 273.87         |  |

| I/O dies                        |                                |                | 36.71          |                |                |  |

| Total                           | 225.04                         | 220.84         | 247.14         | 249.46         | 310.59         |  |

progression. Then, only one  $evk_r$  is required for the whole sequence. CiFHER also adopts minimum key-switching as it is crucial for performance to reduce the off-chip memory access for evks.

**On-the-fly limb extension:** Plaintexts (polynomials) required for PMult ops also account for a considerable portion of off-chip memory access. For example, bootstrapping requires several GBs of plaintexts. On-the-fly limb extension compresses each plaintext to occupy only one limb per polynomial and generates the rest at runtime. However, the runtime extension involves NTT, incurring expensive NoP data transfer. As the overall cost for runtime extension exceeds the benefits coming from the reduced off-chip memory access in an MCM architecture, we do not use this algorithm in CiFHER.

**PRNG** evk generation: We adopt the PRNG evk generation from CraterLake. Half of polynomials composing evks are purely random. Therefore, by deploying deterministic PRNG circuits inside a chip, they can be generated on-the-fly using a short seed, reducing the off-chip memory access for evks to half [81]. As evks can be generated within each core in parallel, no additional overhead is required for MCMs.

#### VI. EVALUATION

# A. Implementation & Default Configurations

**Performance modeling:** We evaluate CiFHER by implementing a cycle-accurate simulator for multi-core systems. It takes a sequence of HE ops as input and translates it into a flow graph of instructions. It divides instructions into micro-instructions and maps the micro-instructions to chiplets according to the data mapping method. The simulator tracks the status of data transmission, data dependency between micro-instructions, and virtual channel allocation status of the NoP to avoid structural hazards and functionality issues. Micro-instructions are scheduled based on this tracking data. Our simulator adopts the decoupled data orchestration of CraterLake to prefetch data from HBM using the static nature of HE ops.

**Hardware modeling:** We synthesized logic components in RTL using the ASAP7 7.5-track 7nm process design kit [25]. Large SRAM components with a bank size larger than 2KB were evaluated using a memory modeling tool, FinCACTI [83]. We modified FinCACTI to match the IEEE IRDS roadmap [44], ASAP7, and other published data in 7nm nodes [18], [48], [50], [72], [86], [93]. We used published data for HBM [75] and PHYs [50], [91]. We integrated the results into the performance modeling tool to automatically derive power

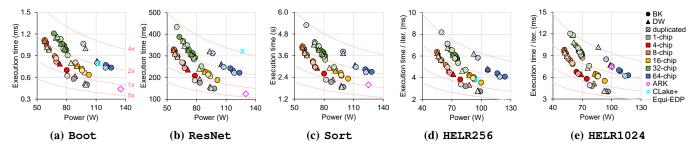

Figure 5: Performance comparison between CiFHER default configurations and prior vector FHE accelerators, (a)(b)(d) CLake+ and (a)(b)(c)(e) ARK, for the workloads. *n*-chip denotes the default configuration of CiFHER with *n* core chiplets, except for 1-chip, which is modified from 4-chip to integrate 4 cores into a monolithic die and has double bisection bandwidth to account for the bandwidth gap between NoC and NoP. BK: block clustering. DW: dimension-wise clustering. duplicated: using limb duplication.

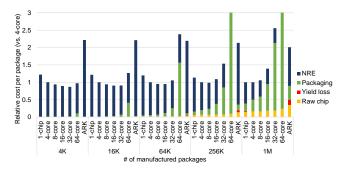

Figure 6: Relative manufacturing cost of CiFHER and ARK systems compared to the 4-core CiFHER system, depending on the number of manufactured systems.

and die area. Overhead due to long wires is also estimated in the tool. All components run at 1GHz.

**Manufacturing cost analysis:** We also estimated the relative cost of a CiFHER package using the cost modeling tool from [35], results of which are shown in Fig. 6.

**Routing and NoP implementation:** We used XY routing and  $5 \times 5$  virtual channel routers [30] for NoP communication, which is a simple yet effective solution for the highly balanced traffic pattern of CiFHER. Each input and output port has 4 virtual channels. We modeled NoP performance and energy using the specification of the UCIe advanced package with a PHY supporting 16GT/s of transfer rate [91].

**Memory instances:** Two types of RFs, the main *scratchpad RF* and an *auxiliary RF* for key-switching, are utilized in CiFHER. The RFs together can provide 6 reads and 6 writes per lane in a cycle through bank interleaving [74]. We modeled the NoP traffic for HBM access by injecting packets through edges connecting the I/O die and its adjacent cores on our simulator. The bandwidth of this edge is the same as that of edges connecting the cores. Two HBM stacks are utilized, each providing 500GB/s of bandwidth [47].

**CiFHER default configurations:** The default configurations have different numbers of cores but similar levels of total computational throughput and memory bandwidth. We can adjust the number of vector lanes in a core from 16 to 256. We fixed (# of cores) × (# of lanes in a core) to 1,024 to make different configurations have similar total computational throughput. We fixed the bisection bandwidth of the package to 2TB/s and decided the bandwidth of each edge by dividing it by the number of edges crossing the bisection. The aggregate capacity of auxiliary RFs was set to 16MB (e.g., 1MB per core in a 16-core configuration). Also, we used a total of 256MB for the scratchpad RF, which is sufficient for CiFHER and is the same as the RF capacity of CraterLake. Table II shows the area breakdown of the default configurations of CiFHER.

## B. Experimental Setup

We utilized four representative FHE workloads that have been utilized for evaluating the previous accelerators.

**CKKS bootstrapping (Boot)**: FHE CKKS workloads require frequent bootstrapping, each involving hundreds of HE ops. We performed bootstrapping for a ciphertext containing  $2^{15}$  complex numbers. We divided the execution time with the number of rescaling ops between consecutive bootstrapping execution (nine in our parameters with L = 48) to account for the frequency of bootstrapping.

**CNN inference (ResNet**): We used a CKKS implementation [61] of the ResNet-20 model for CIFAR-10. We report the latency of a single-image inference, which takes 2,271 seconds in the original single-threaded CPU implementation.

**Sorting**  $2^{14}$  **numbers (Sort**): We used the two-way sorting implementation from [40]. The original 32-thread CPU implementation takes 23,066 seconds to finish.

**Logistic regression training (HELR)**: We used the implementation from [37]. We performed encrypted training with binary classification for classifying the numbers 3 and 8 in the MNIST dataset. We iterated single-batch training 32 times and report the average execution time per iteration. We tested for two batch sizes of 256 (HELR256) and 1,024 (HELR1024).

We compare CiFHER with CraterLake and ARK using their reported performance and power values under 128-bit security constraints. For 12/14nm CraterLake, optimistic compensations for the difference in the technology node (14nm to 7nm [72]) were applied, which we refer to as CLake+.

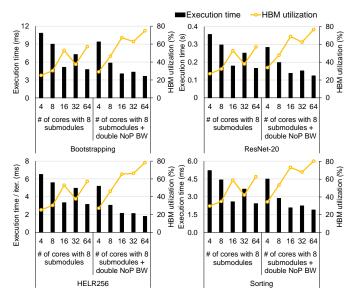

# C. Performance & Efficiency

Among the default configurations, 4-core CiFHER using dimension-wise clustering and limb duplication showed the best energy-delay product (EDP), whose values are shown with the  $1 \times$  equi-EDP lines in Fig. 5. We limited the number of limb clusters to eight to avoid severe fragmentation issues.

When we integrated the 4 cores into a single monolithic die and connected the cores in the NoC with  $2\times$  higher bisection bandwidth (1-chip in Fig. 5), additional performance and EDP enhancements were achieved. 1-chip CiFHER resembles ARK with datapath reduced to 32 bits and showed a similar EDP with the original 64-bit ARK except for HELR1024. ARK performs inferior in HELR1024 because we reordered the HE ops to further enhance the reuse of evks in the memory-bound region, which ARK identifies as a bottleneck of HELR.

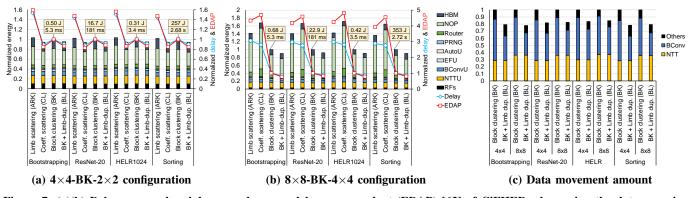

Figure 7: (a)(b) Delay, energy breakdown, and energy-delay-area product (EDAP) [63] of CiFHER when using the data mapping of ARK, CraterLake (CL), and our block clustering without (BK) and with limb duplication (BL). (c) Amount of data movement between cores as CiFHER performs each workload with and without limb duplication.

Table III: Execution time and relative energy-delay-area product(EDAP) [63] of CiFHER and prior vector FHE accelerators.

| Execution time (ms), the lower the better               |                                   |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                           |  |

|---------------------------------------------------------|-----------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--|

|                                                         | CLake+                            | ARK                                   | CiFHER<br>4 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 cores                                  | 64 cores                                  |  |

| Boot<br>ResNet<br>Sort<br>HELR256<br>HELR1024           | 0.79<br>321<br>-<br>3.81<br>-     | 0.44<br>125<br>1990<br>-<br>7.42      | 0.62<br>194<br>2282<br><b>3.34</b><br><b>5.16</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.64<br>189<br>2328<br>3.55<br>5.50       | 0.73<br>222<br>2683<br>4.09<br>6.20       |  |

| Relative EDAP (vs. 4-core CiFHER), the lower the better |                                   |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                           |  |

| Boot<br>ResNet<br>Sort<br>HELR256<br>HELR1024           | 2.04×<br>4.09×<br>-<br>1.40×<br>- | 1.46×<br>1.20×<br>2.04×<br>-<br>4.70× | $1.00 \times 1.00 \times 0.00 \times $ | 1.35×<br>1.26×<br>1.34×<br>1.41×<br>1.42× | 2.63×<br>2.56×<br>2.62×<br>2.80×<br>2.77× |  |

However, the fabrication cost of 1-chip CiFHER or ARK is significatly higher than chiplet-based CiFHER for reasonable production volumes (see Fig. 6), mainly due to the high non-recurring engineering (NRE) cost stemming from the large chip size. 1-chip CiFHER (respecitvely, ARK) has  $1.22 \times (2.22 \times)$  and  $1.37 \times (2.48 \times)$  higher NRE compared to 4-core and 16-core CiFHER, Although NRE can be amortized for large production volumes, the cost of 1-chip CiFHER becomes on par with that of 4-core CiFHER when one million packages are produced, which is a huge amount for domain-specific accelerators. Meanwhile, ARK is always expensive than 4-core CiFHER due to higher raw chip fabrication cost and yield loss.

Under the fixed computational throughput and bisection bandwidth of the package, as we split the chip and utilize smaller cores, performance and efficiency inevitably decline because more NoP data transfer is required. Thus, the area constraint is a decisive factor in an MCM FHE accelerator design. If the cost budget allows, as in recent AMD server CPUs (74mm<sup>2</sup> per compute die [70]), utilizing four cores would be best. Table III shows that 4-core CiFHER enhances efficiency in terms of energy-delay-area product (EDAP) [63] with comparable performance to prior monolithic FHE accelerators due to significantly lower power dissipation (see Fig. 5). Compared to ARK, 4-core CiFHER performs  $1.15 \times$  slower but reduces EDAP by  $2.03 \times$  in geometric mean (geomean) of the workloads. Compared to CLake+, it performs  $1.34 \times$  faster and results in a  $2.27 \times$  EDAP reduction. By contrast, if we can only afford dies as small as recent domain-specific MCM accelerators, such as NN-Baton [89] (2mm<sup>2</sup>) and Simba [84] (6mm<sup>2</sup>), 16-core or 64-core CiFHER needs to be utilized.

Our data mapping and limb duplication minimize the performance and efficiency degradation of many-core configurations. The best 16core and 64-core configurations respectively perform only  $1.03 \times$ and  $1.18 \times$  slower in geomean than 4-core. Compared to 4-core, EDP increases to  $1.23 \times (16\text{-core})$  and  $1.94 \times (64 \text{ core})$ , and EDAP increases to  $1.35 \times (16\text{-core})$  and  $2.67 \times (64\text{-core})$  in geomean using our optimized configurations, whereas a naïve configuration (e.g., 64core using limb scattering with ARK's method) would require  $17.1 \times$ higher EDP and  $23.6 \times$  higher EDAP in bootstrapping.

Meanwhile, due to the skewed organization, 8-core  $(2 \times 4)$  and 32-core  $(4 \times 8)$  configurations suffer from an imbalance in NoP throughput between the horizontal and vertical directions, increasing the tail latency. As a result, performance drops severely, making these configurations less attractive.

#### D. Sensitivity Study

We estimated energy, delay, and EDAP of CiFHER while incrementally applying block clustering (4×4-BK-2×2 and 8×8-BK-4×4) and limb duplication (see Fig. 7). Limb scattering of ARK shows 1.44–1.53× (4×4) and 2.89–3.06× (8×8) slow execution time compared to block clustering. Coefficient scattering of CraterLake is 1.10–1.13× faster than our method for the 4×4 configuration, whereas it is 2.76–2.81× slower for 8×8. The data exchange pattern during limb scattering is not all-to-all as we can group some limbs together to have data transfer occur within each group. By contrast, coefficient scattering requires all-to-all data exchange and thus scales inferior to limb scattering. Coefficient scattering consumes 2.07× more energy on NoP and shows 4.66× higher (worse) EDAP than our mapping in geomean for 8×8. Yet, all-to-all data exchange between 16 cores is manageable, making coefficient scattering faster than our mapping for 4×4.

Fig. 7c compares the amounts of data movement between the cores of CiFHER, with and without limb duplication. Limb duplication consistently eliminated 18–22% of the data movement between the cores. When applying limb duplication to our mapping in the  $4\times4$  configuration, we obtained  $1.10\times$  delay and  $1.16\times$  EDAP reductions in geomean, and the delay and EDAP gaps with coefficient scattering were also reduced to only 1.3% and 2.1% in geomean.

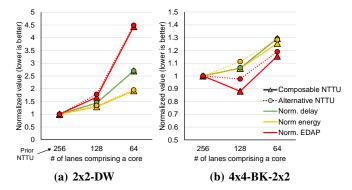

To assess the efficiency of composable NTTUs, we also measured delay, energy, and EDAP of CiFHER during bootstrapping with different single-core computational throughput, represented by the

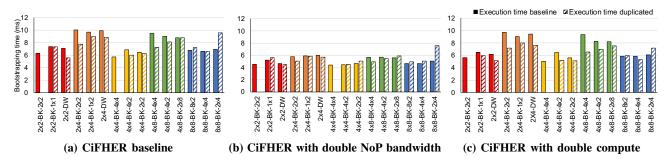

Figure 8: Bootstrapping performance of CiFHER with/without limb duplication. The three best-performing mapping configurations were selected for each number of cores. ARK's redistribution method for BConv was used when limb duplication was not used.

Figure 9: Normalized delay, energy, and EDAP of CiFHER when performing bootstrapping with various single-core computational throughput using the composable NTTU or an alternative NTTU.

number of lanes. We either use composable NTTUs or alternative NTTUs, which extend upon prior NTTUs by interpreting a length-N polynomial as a three-dimensional vector ( $N = \#_{lane} \times \#_{lane} \times N_{rest}$ ) and performing a sequence of  $\#_{lane}$ -point,  $\#_{lane}$ -point, and  $N_{rest}$ -point NTTs. Similar to prior NTTUs, twisting and transposing steps are appropriately inserted in between NTT steps. Alternative NTTUs can also adjust the computational throughput according to the number of lanes ( $\#_{lane}$ ); however, whereas data exchange in composable NTTUs mostly occur in between adjacent lanes, alternative NTTUs require data exchange with distant lanes, increasing overall energy and area due to long wires.

Composable NTTUs increase the efficiency of CiFHER for manycore configurations by enabling a compact MCM architecture with a balance between computational throughput and available data movement bandwidth. In the 2x2-DW configuration, where data transfer through NoP is relatively less heavy and high computational throughput is required for each core, energy and delay increased when prior NTTUs were replaced with composable NTTUs with lower throughput (see Fig. 9a). Specifically, the delay (respectively, energy) increases by  $1.43 \times (1.29 \times)$  and  $2.7 \times (1.92 \times)$  as the number of lanes in a core decreases from 256 to 128 and 64 by utilizing composable NTTUs. Conversely, in the 4x4-BK-2x2 configuration that demands substantial NoP data transfer, halving the number of lanes by using composable NTTUs do not increase the delay by a large margin. Using 128 lanes leads to a slight 6% increase in delay and improves the overall EDAP by 12% due to smaller chiplet area.

Composable NTTUs are more efficient in terms of energy and area compared to alternative NTTUs. In Fig. 9b, the reduction to 128 lanes using alternative NTTU also leads to an around 2% enhancement in EDAP. Nevertheless, due to the substantial wire requirements of alternative NTTUs, the energy consumption and area footprint are larger by  $1.05 \times$  for both when compared to those of composable NTTUs, culminating in an EDAP value  $1.10 \times$  larger than that achieved with composable NTTUs.

# E. Limb Duplication Effects

The effects of limb duplication differ by each configuration. We selected the three best-performing configurations for each number of cores in Fig. 5a and compared the performance of bootstrapping with and without applying limb duplication. Fig. 8a shows the results. Limb duplication improved bootstrapping performance by up to 31% for  $4 \times 8$ -BK- $4 \times 4$  but rather caused 28% performance degradation for  $8 \times 8$ -BK- $2 \times 4$ .

Although limb duplication makes fewer limbs exchanged, the bursty nature of data broadcasting causes network contention and introduces additional latency. The overhead of broadcasting in limb duplication is affected by the arrangement of limb clusters. Only  $8\times8$ -BK- $2\times4$  in Fig. 8a has a coefficient cluster composed of eight cores; coefficient clusters in the other configurations consist of one to four cores. The large number of cores in a coefficient cluster greatly increases the broadcasting latency, degrading performance.

As limb duplication is effective for reducing the NoP pressure, increasing the NoP bandwidth reduced the performance gains from limb duplication (see Fig. 8b). Limb duplication enhanced the performance of the baseline configurations by 7% in geomean. With the NoP bandwidth doubled, limb duplication rather decreased performance by 3% in geomean, and the maximum performance gain observed for 4×8-BK-4×4 was reduced to 14% from 31% in the baseline.

When we intensified the NoP bandwidth bottleneck by doubling computational throughput, performance gains from using limb duplication increased (see Fig. 8c). In these configurations, limb duplication enhanced performance by 14% in geomean, and the maximum performance gain reached 43%.

### F. Scalability

To evaluate the scalability of CiFHER, we estimated the performance of each workload while increasing the number of cores in Fig. 10. We set the internals of a core fixed to an eight-NTTUsubmodule setting (128 lanes). Limb duplication and  $d_x \times d_y$ -BK- $\frac{d_x}{2} \times \frac{d_y}{2}$  block clustering were used for a  $d_x \times d_y$  package configuration. We fixed the HBM bandwidth and the bisection bandwidth of a package. Thus, the bandwidth of a network edge decreases as the number of cores increases.

The limited bandwidth of NoP restricts the scalability of CiFHER. When we increased the total computational throughput by increasing the number of cores from 4 to 16,  $1.99-2.11 \times$  of speedups were achieved for the workloads. Increasing from 16 to 64 only resulted in a  $1.07 \times$  speedup. Therefore, increasing the number of cores without consideration for proper sizing of the core has an adversarial effect on

Figure 10: Performance of CiFHER while scaling the number of cores under default and double NoP bandwidth conditions. The number of NTT submodules in each core is fixed to eight.

efficiency. Meanwhile, skewed configurations (8-core and 32-core), which already suffer from the NoP bandwidth imbalance, showed suboptimal performance.

HBM bandwidth becomes the next limiting factor for scalability when NoP bandwidth is sufficient. Doubling NoP bandwidth mitigates the NoP pressure and improves the performance of the 16-core configuration by  $1.34 \times$  in geomean. Scalability slightly improves as 4-to-16 and 16-to-64 number-of-cores transitions result in  $2.23 \times$  and  $1.13 \times$  speedups. However, the degree of speedups still falls largely behind the increase in the number of cores as the hardware becomes bottlenecked by the HBM bandwidth, whose utilization reaches 75– 80% in the 64-core configuration.

## VII. RELATED WORK

**Function-level acceleration and leveled HE (LHE):** [52] accelerates non-RNS CKKS using Intel AVX-512 instructions and GPUs. HEXL [11] specifically utilizes AVX512-IFMA52 instructions for further CPU optimization. [97] accelerates (i)NTT through highradix FFT and instruction-level optimizations using Intel GPUs. [57] identifies off-chip memory access as the performance bottleneck of (i)NTT on GPUs and applies a better use of the memory hierarchy of GPUs, improving data reusability to address the bottleneck. [6] accelerates the BFV [4], [16] scheme by replacing the major functions with ones more suitable for GPUs. [5] further partitions data to multiple GPUs to exploit abundant parallelism inside BFV.

Numerous FPGA works attempted to optimize core HE ops by deploying tailored datapaths. [79] and [90] proposed specialized FUs for the BFV scheme. HEAX [78] and coxHE [39] designed FPGA modules targeting key-switching, a dominant HE op in CKKS. [59] supports larger parameters adequate for FHE CKKS; however, it only accelerates (i)NTT.

**Torus LWE (TLWE) FHE:** TLWE-based FHE schemes [23], [31] are fundamentally different from RLWE in that usually a single prime modulus (limb) is utilized. Recent studies have specifically targeted the TFHE [23] scheme. cuFHE [92] speeds up TFHE computations on a GPU by utilizing primitive functions accelerated in cuHE [29], which uses a specialized prime to reduce the cost of modular reduction. [71] implements an FPGA datapath for an optimized

TFHE bootstrapping algorithm using inter-operation parallelism. In TFHE, floating-point Fourier transform is often used instead of NTT. [68] utilizes bit-level parallelism and the NVIDIA cuFFT library to accelerate TFHE on GPUs. Matcha [49] is the first ASIC proposal and devises an approximate integer FFT method that replaces mult ops with shift and add ops.

Ring LWE (RLWE) FHE: [51] applies kernel fusion and parameter optimization to accelerate CKKS bootstrapping on GPUs. TensorFHE [34] utilizes the tensor cores in recent NVIDIA GPUs for (i)NTT. [85] introduces new microarchitectural extensions that minimize redundant data access to DRAM and enhance the computational throughput of modular reduction operations, further boosting the performance of FHE operations on current GPUs. FAB [2] reduces the working set to alleviate the off-chip memory bandwidth bottleneck even with limited FPGA memory space. Poseidon [95] builds a 512-lane vector FPGA architecture with FUs reducing the onchip memory bandwidth pressure, such as high-radix NTTUs. GPU and FPGA solutions achieve orders of magnitude higher performance compared to CPU but recent ASIC FHE accelerators [55], [58], [80], [81] introduced in Section II-D achieve even higher performance gains. [3] also introduces an FHE accelerator design using chiplets to reduce chip size but only covered a fixed number of chiplets, set as the sweet spot.

## VIII. CONCLUSION