# Performance analysis of InAIN/GaN HEMT and optimization for high frequency applications

Jagori Raychaudhuri<sup>a,b</sup>, Jayjit Mukherjee<sup>b</sup>, Amit Malik<sup>b</sup>, Sudhir Kumar<sup>b</sup> D.S. Rawal<sup>b</sup>, Meena Mishra<sup>b,\*</sup>, Santanu Ghosh<sup>a</sup>

<sup>a</sup>Department of Physics, Indian Institute of Technology, Delhi, Hauz Khas, Delhi-110016, India

<sup>b</sup>Solid State Physics Laboratory, DRDO, Timarpur, Delhi-110054, India

\*meena.mishra23@yahoo.com

## Abstract:

An InAlN/GaN HEMT device was studied using extensive temperature dependent DC IV measurements and CV measurements. Barrier traps in the InAlN layer were characterized using transient analysis. Forward gate current was modelled using analytical equations. RF performance of the device was also studied and device parameters were extracted following small signal equivalent circuit model. Extensive simulations in Silvaco TCAD were also carried out by varying stem height, gate length and incorporating back barrier to optimize the suitability of this device in Ku-band by reducing the detrimental Short Channel Effects (SCEs). In this paper a novel structure i.e., a short length T gate with recess, on thin GaN buffer to achieve high cut-off frequency ( $f_T$ ) and high maximum oscillating frequency ( $f_{max}$ ) apt for Ku-band applications is also proposed.

Keywords: InAIN/GaN, stem height, gate length, thin buffer, back barrier, recessed gate, TCAD

## 1. Introduction:

In the era of uprising demand of high power, high efficiency and high frequency [1,2,3] applications GaN is the most suitable candidate to deliver outstanding results since it is blessed with some superior qualities like wide bandgap, high saturation velocity etc [4,5]. AlGaN/GaN HEMTs are extremely popular as their RF performance is very good [6,7] and they are well suited for high power applications [8]. But we cannot neglect the reliability issues that they face due to the strain from the lattice mismatch [9 10]. With the increasing demand of high frequency applications several modification techniques were applied on AlGaN/GaN HEMTs. Scaling down the gate length is one of the solutions to increase the frequency of operation as there is an inverse relationship between cut off frequency and gate length [11,12]. But with drastic reduction of gate length, the short channel effects (SCE) arise and degrade the performance of the device [13,14,15]. Maintaining high aspect ratio  $(Lg/t_{bar})$  can resolve the issue of SCEs [16,17,18] but thinning down the barrier has shown surface depletion problems in AlGaN/GaN HEMT [19]. In the context of high frequency applications some new thin barrier heterostructures has come to play [20,21,22]. InAlN/GaN is one of the most promising contenders among them. Strain free lattice matched layer structure with 17% In, makes it more reliable [23,10,23] by reducing defects. High thermal stability is also

reported in some works [24]. Since these devices are thin barriered, in smaller gate length devices suppression of SCEs has been achieved up to a great extent. InAlN devices are showing good results in high frequency [25,26,27] high power and high temperature [24] applications.

But SCEs still persist when gate lengths are scaled down in the ultrashort regime. Thinning down top barrier is not a practical solution as it increases leakage and reduces 2DEG [26]. Introduction of Back barrier came to rescue [26,28], both InGaN and AlGaN back barriers helped to enhance RF performance of the device with sub-micron gate lengths [26,28,29]. With gate length, gate height of a T-gate also plays a role to determine the device performance. An optimised stem height can manifest good results reducing gate capacitances and gate resistances [30,31]. Despite having such remarkable material characteristics GaN is heavily vulnerable to traps [32, 33,34,35]. Barrier traps in InAlN/GaN is also reported [36,37] in several literatures that limit device performances.

In this paper we have studied an inhouse grown and fabricated HEMT with lattice matched InAIN barrier. We have examined the DC and RF characteristics of the device. The barrier traps were also characterised by Current- Deep Level Transient Spectroscopy (C-DLTS) technique. We have optimised the gate length and gate height to obtain better performance of the device in higher frequency regime by conducting simulation study on the same structure. The SCEs were also observed and we have studied how to mitigate them using an AlGaN backbarrier. Further from our simulations we have proposed submicron gate length with recess, on a thin GaN buffer with InAIN barrier, which shows promising results in high frequency applications.

# 2. Sample Details:

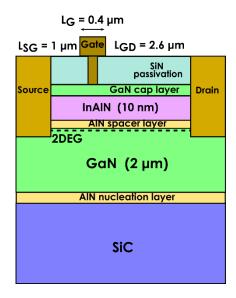

The layer structure of the inhouse grown device is shown in Fig. 1. The epistructure was grown by MOCVD technique. 10 nm thick InAlN layer with 17 % In was grown on  $2\mu$ m GaN layer. The GaN buffer is grown on SiC substrate. 1 nm of AlN spacer layer was used. The channel in the

heterostructure has a sheet charge density of  $1.85 \times 10^{13} \text{ cm}^{-2}$  and electron mobility of 1780 cm<sup>2</sup>/V.s. For device fabrication the source, drain ohmic contacts were realized using Ti/Al/Ni/Au metal stack followed by rapid thermal annealing. The MESA isolation was carried out using inductively coupled plasma reactive ion etching (ICPRIE) with Cl<sub>2</sub>/BCl<sub>3</sub> chemistry. Schottky gate contacts were realised using Ni/Au metal scheme. The gate length of the fabricated device was 400 nm with 100 nm stem height and gate width of 100 µm. The device was passivated with a 100 nm layer of plasma enhanced chemical vapour deposition (PECVD) grown SiN.

## 3. Experimental Details:

DC-IV and C-V characterizations were done using Keithley SCS 4200A semiconductor parametric analyzer. Output and transfer characteristics were measured. Temperature dependent DC measurements were conducted up to  $80^{\circ}$ C. C-V measurements were done. The barrier traps were characterized and forward gate current was modelled. S-parameter measurements were also carried out at different bias conditions to understand RF performance of the device. From the measured S-parameter data  $f_T$  and  $f_{max}$  were calculated and the device parameters were extracted following small signal equivalent circuit model. Simulation study was conducted in Silvaco TCAD to improve the device performance in higher frequency range.

## 4. Results and discussion:

# 4.1 DC -IV Characterization of the Device:

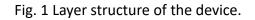

From the DC-IV transfer characteristics, the maximum transconductance,  $g_{m,max}$  is obtained as 430 mS/mm and from the DC-IV output characteristics, it is found that the device exhibits high saturation current (1 A/mm) (Fig. 2(a) and 2(b).) which reflects high 2DEG density yielded from matched epistructure.

Fig. 2 DC-IV characteristics of InAlN/GaN device (a) Transfer characteristics measured at  $V_{DS}$  = 5 V, inset shows the plot in logarithmic scale (b) Output characteristics (c) Transfer characteristics for a temperature range of  $30^{\circ}C - 80^{\circ}C$ .

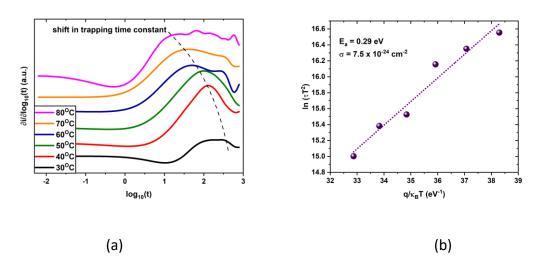

Temperature dependent DC-IV measurements were done over the range of  $30^{\circ}$ C to  $80^{\circ}$ C. From this measurement, negligible shift (0.12 V) in the threshold voltage (V<sub>T</sub>) indicates towards less accumulation of barrier traps (Fig. 2(c)).

## 4.2 Trap Characterization using C-DLTS:

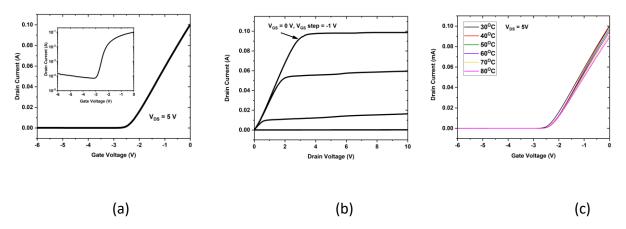

To observe trapping and to calculate the activation energy of the traps in barrier, we have used a filling pulse of 100 sec with  $V_{GS} = -2.4$  V and  $V_D = 3$  V ensuring that the depletion region extends only into the barrier. For the detrapping phase,  $V_{GS} = 0$  V and  $V_{DS} = 3$  V is applied for 1000 sec. The entire experiment is repeated up to  $80^{\circ}$ C in step of  $10^{\circ}$ C. The plot of the derivative of the drain current with respect to  $log_{10}(t)$  vs  $log_{10}(t)$  shows the dominant time constants responsible for the detrapping transients. With increase in temperature a leftward shift in the dominant time constants is observed (Fig. 3(a)). The Arrhenius formulation is utilized to extract the trap energy and it was calculated to be 0.29 eV from the conduction band (Fig. 3(b)).

Fig. 3 (a) C-DLTS spectra of the detrapping transients for different temperatures (the dotted line denotes the peak shifting with increasing temperature) (b) Arrhenius plot to calculate activation energy of the traps extracted from C-DLTS spectra

## 4.3 Modelling of Forward Gate Current:

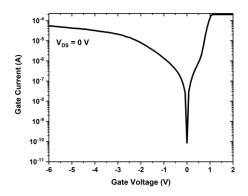

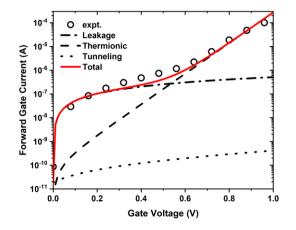

The forward gate current was showing the signatures of multiple processes (Fig. 4). In previous works the gate current was modelled following different mechanisms [38,39,40]. Here we have considered Thermionic Emission (T.E.), Trap assisted Tunneling (T.U.) and leakage (R.L.) components to model the forward gate current.

Fig. 4 Gate current measured at V<sub>DS</sub>=0V

To realize the forward gate current, we have used the following equations regarding the 3 components [42],

$$I_{TE} = I_{TE}(0) \left[ \exp\left(\frac{q(V - IR_S)}{\eta \kappa T}\right) - 1 \right]$$

(1)

$$I_{TU} = I_{TU}(0) \left[ \exp\left(\frac{q(V - IR_S)}{E_T}\right) - 1 \right]$$

(2)

$$I_{RL} = \frac{V - V_0}{R_L} \tag{3}$$

$$I_{TE}(0) = AA^* \frac{T^2 \phi_B}{\eta \kappa T} \tag{4}$$

$$I_{TU}(0) = q \nu_D N_{dis} exp(-\frac{\phi_B}{\kappa T})$$

(5)

Where  $I_{TE}$  (0),  $I_{TU}$  (0) are components at zero bias,  $R_L$  is the leakage resistance,  $R_s$  is the series resistance, T is the absolute temperature,  $E_T$  is the tunneling energy,  $\phi_B$  is the Schottky barrier height and  $\eta$  is the ideality factor A is the Schottky area of the device and A\* is the Richardson constant,  $v_D$  is Debye frequency and  $N_{dis}$  is dislocation density.

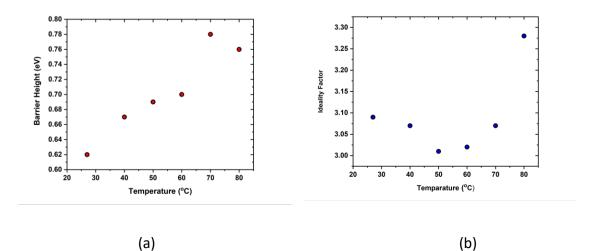

To realize the forward current first, schottky barrier height  $\phi_B$  and ideality factor  $\eta$  were calculated over the temperature range (Fig. 5). From Fig. 5(b) the ideality factor shows a higher value ( $\eta \approx 3 - 3.28$ ) over the experimental temperature regime. The high value of  $\eta$  indicates the existence of defect assisted tunneling along with the thermionic emission processes in the gate current [41, 42]. Hence, tunneling was considered with thermionic

emission and also combining these two mechanisms with leakage, the forward gate current of our device was successfully modelled (Fig. 6).

Fig. 5 Variation of (a) Barrier Height and (b) ideality factor with temperature

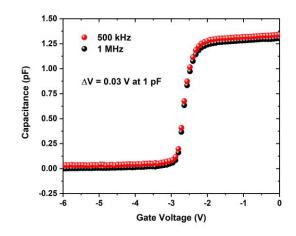

#### 4.4 C-V Characterization:

From multi frequency C- V measurement interface trap state ( $N_{it}$ ) and trap state density ( $D_{it}$ ) can be calculated considering the following equations [43]

$$N_{it} = C_b \Delta V/q \tag{1}$$

$$D_{it} = N_{it} / \Delta E_t \tag{2}$$

$$E_t = \kappa T \ln \left(\frac{f_1}{f_2}\right) \tag{3}$$

Where  $C_b$  is the barrier capacitance,  $E_t$  is the energy difference between the traps,  $f_1$ ,  $f_2$  are two different frequencies which are 1 MHz and 500 kHz for our experiment and  $\Delta$  V is the voltage difference for two different frequencies corresponding to the barrier capacitance.

Fig. 7 Experimental Capacitance- Voltage Characteristics at 500 kHz and 1 MHz

From experiment following these equations (Fig 7).  $N_{it} = 1.5 \times 10^{11} / \text{cm}^2$  and  $D_{it} = 8.3 \times 10^{12} / \text{eV}$  cm<sup>2</sup> are obtained. These results denote a good quality interface with less population of interface traps.

#### 4.5 RF Characterization:

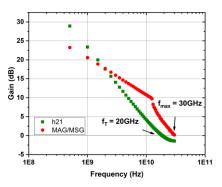

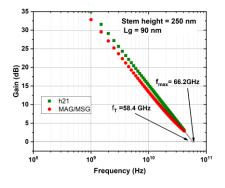

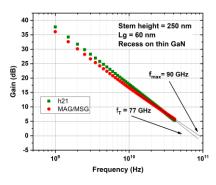

Cut-off frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{max}$ ) from unity current gain ( $h_{21}$ ) and Maximum gain (MAG/MSG) using S-parameter measurements at the bias point ( $V_{GS}$  = - 1.5 V,  $V_{DS}$  = 10 V) were calculated (Fig. 8).

Fig. 8  $f_T$  and  $f_{max}$  as calculated from the unity current gain  $(h_{21})$  and maximum gain (MAG/MSG) of the device

$f_T$  = 20 GHz and  $f_{max}$  = 30 GHz are extracted from measured S-parameters for the device. It is much less than what we expect from InAlN/GaN devices. In our device we have used a T-gate with stem height of 100 nm. A 100 nm stem height on a 10 nm barrier can induce increment in gate capacitances which in turn degrades the RF performance of the device.

To understand this, the device parameters were extracted from small signal equivalent circuit using measured S-parameters [44,45,46]. First the extrinsic parameters were calculated, then the intrinsic parameters were obtained. The list of parameters is shown in Table 1.

| Parameters |                           | Value  |

|------------|---------------------------|--------|

| Extrinsic  | $R_{g}\left(\Omega ight)$ | 5.02   |

|            | $R_{d}\left(\Omega ight)$ | 9.18   |

|            | $R_{s}\left(\Omega ight)$ | 11.1   |

|            | L <sub>d</sub> (pH)       | 76     |

|            | L <sub>g</sub> (pH)       | 28.4   |

|            | L <sub>s</sub> (pH)       | 1      |

|            | $C_{pg}(fF)$              | 100.75 |

|            | $C_{pd}$ (fF)             | 44.8   |

| Intrinsic  | $g_{m}(mS)$               | 62.5   |

|            | g <sub>d</sub> (mS)       | 7.46   |

|            | $R_{i}\left(\Omega ight)$ | 1.4    |

|            | $C_{gd}$ (fF)             | 52     |

|            | $C_{gs}(fF)$              | 285    |

|            | $C_{ds}(fF)$              | 16.5   |

|            | τ (ps)                    | 1.75   |

Table 1. Extracted device parameters using small signal equivalent circuit model for the device.

The table also indicates the increased value of gate capacitances which compromises the operating frequency of the device.

## 4.6 Simulation Study:

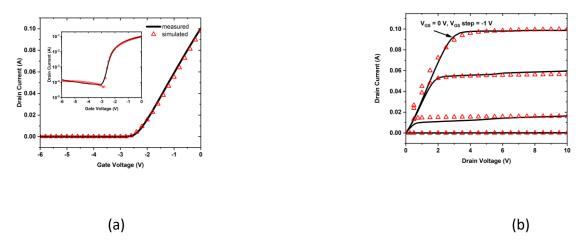

To understand the effect of structural parameters of the device on high frequency performances we have done a simulation study in Silvaco TCAD. We have varied device parameters, incorporated special structures to optimize the device performance. The experimental DC-IV (transfer, leakage and output) characteristics of the device was calibrated with the simulated results. The layer structure and device dimensions were kept same as our physical device as shown in Fig. 1. The physical models that were used are Fermi statistics, Shockley-Read-Hall (SRH) recombination, UST and GaNSat, Fldmob for mobility and Pipinys for the gate leakage. Fig. 9. shows the calibrated characteristics.

Fig. 9 Calibration of experimental device characteristics with simulated results for the InAIN/GaN HEMT (a) Transfer characteristics (b) output characteristics

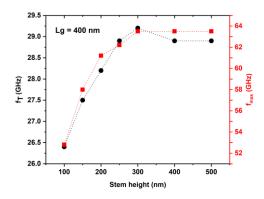

To understand how stem height impacts the optimum RF performance of the device, a simulation study was carried out by varying the stem height and observed the operating frequencies keeping the gate length 400 nm (Fig. 10).

Fig. 10 Variation of  $f_{\rm T}$  and  $f_{\rm max}$  with gate stem height in InAlN/GaN HEMT

Starting from 100 nm, it is observed that  $f_T$  and  $f_{max}$  were improving up to 300 nm stem height, beyond that the results are deteriorating due to the effect of gate resistances and gate capacitances.

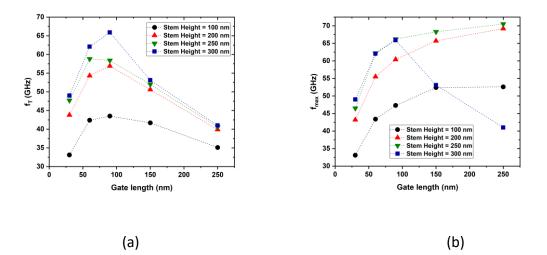

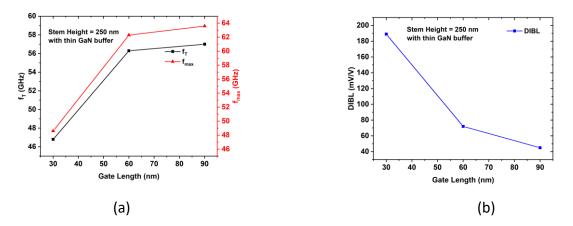

A popular way to increase the cut off frequency is scaling down the gate length. Therefore, we have scaled down the gate length up to 30 nm for different stem heights (Fig. 11). From Fig

Fig. 11 (a) Variation of  $f_T$  and (b)  $f_{max}$  with gate length in InAlN/GaN HEMT

11(a) it is observed that for all the stem heights, the  $f_T$  increases upto 90 nm gate length after which it deteriorates on further scaling. We are getting the highest  $f_T$  with a combination of 90nm gate length and 300 nm stem height. However, from figure 11(b) it is observed that the  $f_{max}$  is again highest upto 90 nm gate length. But when it comes to stem height 250 nm yields better  $f_{max}$  with 90 nm gatelength. Thus from the point of view of both  $f_T$  and  $f_{max}$ , T- gate with 250 nm stem height and 90 nm gate length was optimized. Fig 12. shows the frequency performance of the T- gate with 250 nm stem height and 90 nm gate length.

Fig. 12  $\,$   $\,f_{T}$  and  $f_{max}$  with T gate having 90nm length and 250nm stem height in InAIN/GaN HEMT

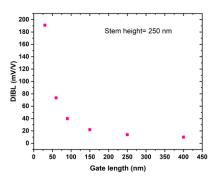

Since drastic cutting down of gate length invokes Short Channel Effects, scaling down to 60nm and 30 nm gate lengths doesn't yield better frequency performance.

To examine this, Drain Induced Barrier Lowering (DIBL) was calculated for different gate lengths keeping stem height 250 nm. From Fig 13 DIBL is quite evident in the cases of 60 nm and 30 nm gate lengths.

Fig. 13 Variation of DIBL with gate length in InAlN/GaN HEMT

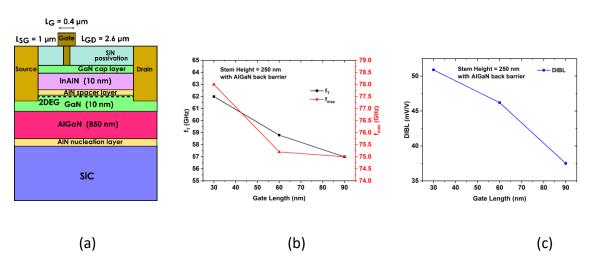

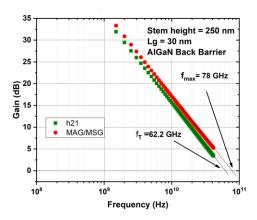

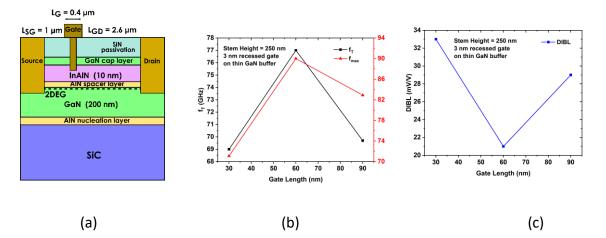

To suppress SCEs an 850nm Al<sub>.25</sub>Ga<sub>.75</sub>N back barrier was incorporated keeping 10 nm GaN channel on the same calibrated structure (Fig. 14(a)). Frequency performance improves even in 60nm and 30 nm gate length devices (Fig. 14(b)) as the back barrier suppresses the DIBL (Fig. 14(c)). Thus, scaling down can be successfully achieved with 30 nm gate length with AlGaN back barrier. Fig. 15 depicts good frequency performance with the above optimized structure.

Fig14. (a) Layer structure with backbarrier (b) Variation of  $f_T$ ,  $f_{max}$  and (c) Variation of DIBL with submicron gate length in InAIN/GaN HEMT with AlGaN back barrier.

Fig.15  $f_T$  and  $f_{max}$  of T gate having 30nm length and 250nm stem height in InAlN/GaN HEMT with AlGaN backbarrier.

Buffer free or thin buffer AlGaN/GaN structures are hot topic for discussion these days as they are showing promising results in terms of device performance [47,48]. It would be a nice idea to examine thin barrier structure on thin buffer structure. It would increase the throughput and incorporate the thin buffer related benefits into the device. Keeping this in mind, the same barrier layer on a thin GaN buffer of 200 nm thickness was simulated with the stem height at 250 nm for sub-100 nm gate length devices. The performance of thin buffer structure is almost similar to that of the conventional buffer. It shows appreciable frequency response with 90 nm get length but unlike the backbarrier structure 60nm and 30 nm show the degradation of RF performance due to the severity of SCEs. Comparative study of  $f_T$ ,  $f_{max}$  and DIBL for different gate lengths (sub-100 nm) on the thin GaN buffer structure is depicted in Fig. 16.

Fig. 16 (a) Variation of  $f_T$ ,  $f_{max}$  and (b) variation of DIBL with submicron gate length in InAIN/GaN HEMT on 200nm thin GaN buffer

Another way to combat SCEs is to use the recessed gate structure as it improves the aspect ratio ( $Lg/t_{bar}$ ) of the device [49]. A recessed gate on the thin GaN buffer layer structure is incorporated and a comparative simulation study is carried out for different sub-100 nm gate lengths. We have optimized the recess depth of 3 nm into the InAIN barrier to keep the 2DEG intact and to prevent further leakage (Fig. 17(a)).

Fig. 17 (a) layer structure grown on thin GaN with recessed gate (b) Variation of  $f_T$ ,  $f_{max}$  and (c) Variation of DIBL with submicron gate length with 3 nm recess in InAlN/GaN HEMT on 200nm thin GaN buffer

From Fig.17(b) the improvement in  $f_{T and} f_{max}$  is evident. From Fig.17(c) it is observed that the DIBL is reduced to a great extent in the case of 60 nm gate length. Although the DIBL increased in 30 nm gate length device but it didn't affect the frequency performance much. A recessed gate structure having 60 nm gate length and 250 nm stem height on InAlN barrier and thin GaN buffer heterostructure has been optimized. This device achieves a suitability in high frequency operation with  $f_T = 77$  GHz and  $f_{max} = 90$  GHz as shown in Fig. 18.

Fig.18  $f_T$  and  $f_{max}$  of T-gate having 60nm length and 250nm stem height with 3 nm recess in InAIN/GaN HEMT with 200nm thin GaN buffer.

## 5. Conclusion:

It is found that the InAIN/GaN HEMT device is yielding appreciable amount of drain current and transconductance due to its profound 2DEG density. From C-V analysis and transient characterizations insight about interface and barrier traps was determined. It is introspected how different mechanisms impact on forward gate current using thin barrier InAIN structure. The simulation study reveals the effect of stem height and gate length on f<sub>T</sub> and f<sub>max</sub>. T-gate with stem height of 250 nm with gate length of 90 nm shows high cut- off frequency of 58.4 GHz. With the incorporation of a 850 nm AlGaN back barrier, the short channel effects were suppressed and a higher cut -off frequency (62.2 GHz) using gate length of only 30 nm was obtained. The thin barrier of InAIN grown on thin GaN buffer has emerged as a potential contender for high frequency applications from the simulation study. A 3nm recessed T gate with length of 60 nm simulated on thin GaN buffer shows a promising result (f<sub>T</sub> = 77 GHz, f<sub>max</sub> = 90 GHz) in Ku-regime. This gives a scope to fabricate and validate this structure in future.

## Acknowledgment

The authors would like to thank GaN Team and Director SSPL, DRDO, Delhi for the valuable support and guidance to carry out the experimental work.

## **Data Availability Statement**

The data that support the findings of this study are available upon reasonable request from the authors.

## **Conflict of interest**

The authors declare that they have no known competing interests.

#### References

[1] T. Palacios, A. Chakraborty, S. Heikman, S. Keller, S. DenBaars, and U. Mishra, "Algan/gan high electron mobility transistors with ingan back-barriers," IEEE Electron device letters, vol. 27, no. 1, pp. 13–15, 2005.

[2] N. Adachi, Y. Tateno, S. Mizuno, A. Kawano, J. Nikaido, and S. Sano, "High temperature operation of algan/gan hemt," in IEEE MTT-S International Microwave Symposium Digest, 2005. IEEE, 2005, pp. 507–510.

[3] T. Palacios, Y. Dora, A. Chakraborty, C. Sanabria, S. Keller, S. DenBaars, and U. Mishra, "Optimization of algan/gan hemts for high frequency operation," 2006.

[4] C. Oxley and M. Uren, "Measurements of unity gain cutoff frequency and saturation velocity of a GaN HEMT transistor," IEEE Transactions on Electron Devices, vol. 52, no. 2, pp. 165–169, 2005.

[5] J. Milligan, S. Sheppard, W. Pribble, Y.-F. Wu, G. Muller, and J. Palmour, "SiC and GaN wide bandgap device technology overview," in 2007 IEEE Radar Conference. IEEE, 2007, pp. 960–964.

[6] J. W. Chung, T.-W. Kim, and T. Palacios, "Advanced gate technologies for state-of-the-art fT in AlGaN/GaN HEMTs," in 2010 International Electron Devices Meeting. IEEE, 2010, pp. 30–2.

[7] J. W. Chung, W. E. Hoke, E. M. Chumbes, and T. Palacios, "AlGaN/GaN HEMT With 300-GHz fmax," IEEE Electron Device Letters, vol. 31, no. 3, pp. 195–197, 2010.

[8] Y.-F. Wu, A. Saxler, M. Moore, R. Smith, S. Sheppard, P. Chavarkar, T. Wisleder, U. Mishra, and P. Parikh, "30-W/mm GaN HEMTs by field plate optimization," IEEE Electron Device Letters, vol. 25, no. 3, pp. 117–119, 2004.

[9] S. Park, C. Floresca, U. Chowdhury, J. L. Jimenez, C. Lee, E. Beam, P. Saunier, T. Balistreri, and M. J. Kim, "Physical degradation of GaN HEMT devices under high drain bias reliability testing," Microelectronics Reliability, vol. 49, no. 5, pp. 478–483, 2009.

[10] A. Chini, M. Esposto, G. Meneghesso, and E. Zanoni, "Evaluation of GaN HEMT degradation by means of pulsed I–V, leakage and DLTS measurements," Electronics letters, vol. 45, no. 8, pp. 426–427, 2009.

[11] Y.-R. Wu, M. Singh, and J. Singh, "Device scaling physics and channel velocities in aigan/gan hfets: Velocities and effective gate length," IEEE transactions on electron devices, vol. 53, no. 4, pp. 588–593, 2006.

[12] X. Yu, H. Tao, and W. Hong, "A ka band 15w power amplifier mmic based on gan hemt technology," in 2016 IEEE International Workshop on Electromagnetics: Applications and Student Innovation Competition (iWEM). IEEE, 2016, pp. 1–3.

[13] M. Allaei, M. Shalchian, and F. Jazaeri, "Modeling of short-channel effects in gan hemts," IEEE Transactions on Electron Devices, vol. 67, no. 8, pp. 3088–3094, 2020.

[14] O. Breitschadel, L. Kley, H. Gr " abeldinger, J. Hsieh, B. Kuhn, F. Scholz, and H. Schweizer, " "Shortchannel effects in algan/gan hemts," Materials Science and Engineering: B, vol. 82, no. 1-3, pp. 238– 240, 2001.

[15] P. S. Park and S. Rajan, "Simulation of short-channel effects in n-and ga-polar algan/gan hemts," IEEE Transactions on Electron Devices, vol. 58, no. 3, pp. 704–708, 2011.

[16] G. H. Jessen, R. C. Fitch, J. K. Gillespie, G. Via, A. Crespo, D. Langley, D. J. Denninghoff, M. Trejo, and E. R. Heller, "Short-channel effect limitations on high-frequency operation of algan/gan hemts for t-gate devices," IEEE Transactions on Electron Devices, vol. 54, no. 10, pp. 2589–2597, 2007.

[17] M. Higashiwaki, N. Onojima, T. Matsui, and T. Mimura, "High f t and f max algan/gan hfets achieved by using thin and high-al-composition algan barrier layers and cat-cvd sin passivation," Physica status solidi (a), vol. 203, no. 7, pp. 1851–1855, 2006.

[18] D. Guerra, R. Akis, F. A. Marino, D. K. Ferry, S. M. Goodnick, and M. Saraniti, "Aspect ratio impact on rf and dc performance of state-of-the-art short-channel gan and ingaas hemts," IEEE Electron Device Letters, vol. 31, no. 11, pp. 1217–1219, 2010.

[19] M. Higashiwaki, T. Mimura, and T. Matsui, "Millimeter-wave gan hfet technology," in Gallium Nitride Materials and Devices III, vol. 6894. SPIE, 2008, pp. 293–301.

[20] J. Kuzm´ık, "Power electronics on inaln/(in) gan: Prospect for a record performance," IEEE Electron Device Letters, vol. 22, no. 11, pp. 510–512, 2001. [21] M. Higashiwaki, T. Mimura, and T. Matsui, "Algan/gan heterostructure field-effect transistors on 4h-sic substrates with current-gain cutoff frequency of 190 ghz," Applied Physics Express, vol. 1, no. 2, p. 021103, 2008.

[22] T. Zimmermann, D. Deen, Y. Cao, J. Simon, P. Fay, D. Jena, and H. G. Xing, "Aln/gan insulated-gate hemts with 2.3 a/mm output current and 480 ms/mm transconductance," IEEE Electron Device Letters, vol. 29, no. 7, pp. 661–664, 2008.

[23] J. Kuzmik, G. Pozzovivo, C. Ostermaier, G. Strasser, D. Pogany, E. Gornik, J.-F. Carlin, M. Gonschorek, E. Feltin, and N. Grandjean, "Analysis of degradation mechanisms in lattice-matched inaln/gan highelectron-mobility transistors," Journal of Applied Physics, vol. 106, no. 12, p. 124503, 2009.

[24] F. Medjdoub, J.-F. Carlin, M. Gonschorek, E. Feltin, M. Py, D. Ducatteau, C. Gaquiere, `N. Grandjean, and E. Kohn, "Can inaln/gan be an alternative to high power/high temperature algan/gan devices?" in 2006 International Electron Devices Meeting. IEEE, 2006, pp. 1–4.

[25] H. Sun, A. R. Alt, H. Benedickter, E. Feltin, J.-F. Carlin, M. Gonschorek, N. R. Grandjean, and C. R. Bolognesi, "205-ghz (al, in) n/gan hemts," IEEE electron device letters, vol. 31, no. 9, pp. 957–959, 2010.

[26] D. S. Lee, X. Gao, S. Guo, D. Kopp, P. Fay, and T. Palacios, "300-ghz inaln/gan hemts with ingan back barrier," IEEE Electron Device Letters, vol. 32, no. 11, pp. 1525–1527, 2011.

[27] D. S. Lee, J. W. Chung, H. Wang, X. Gao, S. Guo, P. Fay, and T. Palacios, "245-ghz inaln/gan hemts with oxygen plasma treatment," IEEE Electron Device Letters, vol. 32, no. 6, pp. 755–757, 2011.

[28] D. S. Lee, X. Gao, S. Guo, and T. Palacios, "Inaln/gan hemts with algan back barriers," IEEE Electron Device Letters, vol. 32, no. 5, pp. 617–619, 2011.

[29] P. Murugapandiyan, S. Ravimaran, J. William, and K. M. Sundaram, "Design and analysis of 30 nm t-gate inaln/gan hemt with algan back-barrier for high power microwave applications," Superlattices and Microstructures, vol. 111, pp. 1050–1057, 2017.

[30] D. J. Denninghoff, S. Dasgupta, J. Lu, S. Keller, and U. K. Mishra, "Design of high-aspectratio t-gates on n-polar gan/algan mis-hemts for high fmax," IEEE electron device letters, vol. 33, no. 6, pp. 785–787, 2012.

[31] S. Tirelli, D. Marti, H. Sun, A. R. Alt, J.-F. Carlin, N. Grandjean, and C. R. Bolognesi, "Fully passivated alinn/gan hemts with ft/fMAX of 205/220 ghz," IEEE electron device letters, vol. 32, no. 10, pp. 1364–1366, 2011.

[32] S. C. Binari, K. Ikossi, J. A. Roussos, W. Kruppa, D. Park, H. B. Dietrich, D. D. Koleske, A. E. Wickenden, and R. L. Henry, "Trapping effects and microwave power performance in algan/gan hemts," IEEE Transactions on Electron Devices, vol. 48, no. 3, pp. 465–471, 2001.

[33] J. M. Tirado, J. L. Sanchez-Rojas, and J. I. Izpura, "Trapping effects in the transient response of algan/gan hemt devices," IEEE Transactions on Electron Devices, vol. 54, no. 3, pp. 410–417, 2007.

[34] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the dc and rf characteristics of algan/gan hfets," IEEE Transactions on Electron Devices, vol. 48, no. 3, pp. 560–566, 2001.

[35] M. Meneghini, N. Ronchi, A. Stocco, G. Meneghesso, U. K. Mishra, Y. Pei, and E. Zanoni, "Investigation of trapping and hot-electron effects in gan hemts by means of a combined electrooptical method," IEEE transactions on electron devices, vol. 58, no. 9, pp. 2996–3003, 2011.

[36] S. Martin-Horcajo, A. Wang, A. Bosca, M. Romero, M. J. Tadjer, A. D. Koehler, T. J. Anderson, and F. Calle, "Trapping phenomena in algan and inaln barrier hemts with different geometries," Semiconductor Science and Technology, vol. 30, no. 3, p. 035015, 2015.

[37] A. Sasikumar, A. Arehart, S. Martin-Horcajo, M. Romero, Y. Pei, D. Brown, F. Recht, M. di Forte-Poisson, F. Calle, M. Tadjer et al., "Direct comparison of traps in inaln/gan and algan/gan high electron mobility transistors using constant drain current deep level transient spectroscopy," Applied Physics Letters, vol. 103, no. 3, p. 033509, 2013.

[38] S. Turuvekere, N. Karumuri, A. A. Rahman, A. Bhattacharya, A. DasGupta, and N. DasGupta, "Gate leakage mechanisms in algan/gan and alinn/gan hemts: comparison and modeling," IEEE Transactions on electron devices, vol. 60, no. 10, pp. 3157–3165, 2013.

[39] D. Donoval, A. Chvala, R. Sramat y, J. Kov a'c, E. Morvan, C. Dua, M. DiForte-Poisson, and P. Kordos, "Transport properties and barrier height evaluation in ni/inaln/gan schottky diodes," Journal of applied physics, vol. 109, no. 6, p. 063711, 2011.

[40] J. Mukherjee, R. K. Chaubey, D. Rawal, and R. Dhaka, "Analysis of the post-stress recovery of reverse leakage current in gan hemts," Materials Science in Semiconductor Processing, vol. 137, p. 106222, 2022.

[41] L. Yang, B. Zhang, Y. Li, and D. Chen, "Improved schottky barrier characteristics for alinn/gan diodes by oxygen plasma treatment," Materials Science in Semiconductor Processing, vol. 74, pp. 42–45, 2018.

[42] P. Cui, J. Zhang, T.-Y. Yang, H. Chen, H. Zhao, G. Lin, L. Wei, J. Q. Xiao, Y.-L. Chueh, and Y. Zeng, "Effects of n2o surface treatment on the electrical properties of the inaln/gan high electron mobility transistors," Journal of Physics D: Applied Physics, vol. 53, no. 6, p. 065103, 2019.

[43] S. Latrach, E. Frayssinet, N. Defrance, S. Chenot, Y. Cordier, C. Gaquiere, and H. Maaref, "Trap states analysis in algan/aln/gan and inaln/aln/gan high electron mobility transistors," Current Applied Physics, vol. 17, no. 12, pp. 1601–1608, 2017.

[44] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the fet smallsignal equivalent circuit," IEEE Transactions on microwave theory and techniques, vol. 36, no. 7, pp. 1151–1159, 1988.

[45] A. Miras and E. Legros, "Very high-frequency small-signal equivalent circuit for short gatelength inp hemts," IEEE transactions on microwave theory and techniques, vol. 45, no. 7, pp. 1018–1026, 1997.

[46] J. Raychaudhuri, J. Mukherjee, S. Kumar, R. Bag, M. Mishra, and S. Ghosh, "Effect of different layer structures on the rf performance of gan hemt devices," Semiconductor Science and Technology, vol. 36, no. 10, p. 105005, 2021, DOI: 10.1088/1361-6641/ac1054.

[47] J. Raychaudhuri, J. Mukherjee, R. Bag, A. Malik, S. Kumar, D. Rawal, M. Mishra, and S. Ghosh, "Study of "thin buffer" gan on sic hemt and effect of bulk traps on it," Silicon, vol. 14, no. 18, pp. 12 505–12 512, 2022.

[48] D.-Y. Chen, A. Malmros, M. Thorsell, H. Hjelmgren, O. Kordina, J.-T. Chen, and N. Rorsman, "Microwave performance of 'buffer-free'gan-on-sic high electron mobility transistors," IEEE Electron Device Letters, vol. 41, no. 6, pp. 828–831, 2020.

[49] D. Kato, Y. Kajiwara, A. Mukai, H. Ono, A. Shindome, J. Tajima, T. Hikosaka, M. Kuraguchi, and S. Nunoue, "Suppression of short-channel effects in normally-off gan mosfets with deep recessed-gate structures," Japanese Journal of Applied Physics, vol. 59, no. SG, p. SGGD13, 2020.