PREPARED FOR SUBMISSION TO JINST

TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS 2023 GEREMEAS (CA), ITALY 02-06 October 2023

# Novel Developments on the OpenIPMC Project

Luigi Calligaris,<sup>1</sup> Carlos Ruben Dell'Aquila,<sup>1</sup> Antono Vitor Grossi Bassi,<sup>1</sup> André Muller Cascadan,<sup>1</sup> Luis Eduardo Ardila-Perez,<sup>2</sup> Marvin Fuchs,<sup>2</sup> Alp Akpinar,<sup>3</sup> Andrew Peck,<sup>3</sup> Daniel Gastler,<sup>3</sup> Giacomo Fedi<sup>4</sup>

<sup>1</sup>Center for Scientific Computing, São Paulo State University,

Rua Dr. Bento Teobaldo Ferraz 271, Bloco II - Térreo, 01140-070 São Paulo - SP, Brazil

<sup>2</sup>Institute for Data Processing and Electronics (IPE), Karlsruhe Institute of Technology (KIT),

Hermann-von-Helmholtz-Platz 1, D-76344 Eggenstein-Leopoldshafen, Germany

<sup>3</sup>Department of Physics, Boston University,

590 Commonwealth Avenue, Boston, MA 02215, US

<sup>4</sup>Blackett Laboratory, Physics Department, Imperial College London, Prince Consort Rd, London, SW7 2BW, UK

*E-mail:* luigi.calligaris@cern.ch

ABSTRACT: We present the recent developments in the context of the OpenIPMC project, which proposes a free and open-source Intelligent Platform Management Controller (IPMC) software and an associated controller mezzanine card for use in ATCA electronic boards. We discuss our experience in the operation of OpenIPMC on prototype boards designed for the upgrades of particle physics experiments at CERN and we show the addition of new features and support for new protocols in the firmware of the controller mezzanine card.

KEYWORDS: Modular electronics, Control and monitor systems online, Detector control systems

ArXiv ePrint: 2310.19742

# 1 OpenIPMC and its context

Numerous high-performance FPGA-based electronic boards have been designed for use in the upgrades of the HL-LHC [1] experiments for applications like detector control, calibration, trigger and data acquisition. Many of these boards are compliant with the PICMG Advanced Telecommunication Computing Architecture (ATCA) standard [2]. Examples of these boards are the Apollo [3], the Serenity [4], the ATLAS Trigger Processor [5] and the CMS DAQ and Timing Hub [6]. The ATCA standard requires all boards to be equipped with an Intelligent Platform Management Controller (IPMC), which monitors the health of the boards and manages their power state as part of the Hardware Platform Management (HPM) infrastructure. The OpenIPMC project [7] aims to create a low-cost, free and open-source IPMC solution which is fully customizeable by the ATCA board designer. The project has been documented in previous publications and is composed of a platform-independent software component implementing the IPMI behavior (OpenIPMC-SW) [8], a hardware mezzanine (OpenIPMC-HW) [9] suitable to be installed in the IPMC slot of a compatible ATCA carrier board and its firmware (OpenIPMC-FW) [9]. This firmware is composed of a triplet of executable binaries designed to run on the two ARM Cortex-M7 and -M4 cores of the STM32H7 microcontroller on the mezzanine. Two binaries contain the instructions executed by the two cores in normal operation and the third one is the bootloader, which runs on the Cortex-M7 core. The firmware, which is stored into the internal memory of the microcontroller, integrates OpenIPMC-SW with the necessary board-specific customizations and other board control services. In this document we present the latest developments on OpenIPMC-FW, which have mainly focused on satisfying the requirements of the Serenity and Apollo ATCA boards for use in the back-end systems of LHC experiments. Both boards will be hosted in electronics shelves located in the experimental areas and operated remotely from control rooms located in the surface.

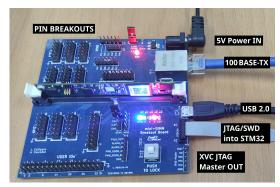

Figure 1: The OpenIPMC-HW mezzanine, version 1.1.

## 2 Developments on OpenIPMC-FW

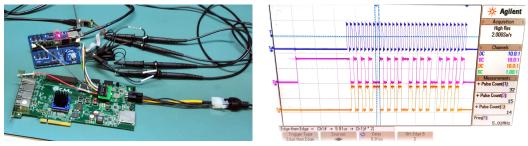

The firmware has been subject to extensive testing in the past three years, which led to improvements in its stability and performance. Tests and development were carried out by operating the mezzanine on the bench while hosted into a custom breakout development board (Fig. 2a), and by operating it in Pulsar-IIb [10], Apollo and Serenity boards hosted in suitable ATCA shelves at the São Paulo Research and Analysis Center (SPRACE) of UNESP, at Boston University, at the Karlsruhe Institute of Technology (KIT) and at CERN (Fig. 2b). Aside from improvements to the existing firmware components, new functionalities were added and then validated for stability. Furthermore, some small modifications to the hardware design - which will not be described in detail here - were

introduced to improve compliance with the ATCA standard, allowing to reset the IPMC without upsetting the operation of the payload when in active state.

(a) Breakout board being used for firmware development at SPRACE.

(b) Backend development setup at the CERN CMS Tracker Integration Facility.

Figure 2: Examples of OpenIPMC-HW setups used in our development.

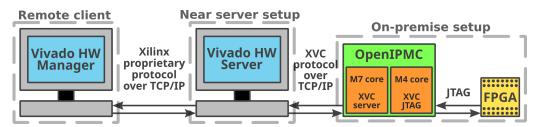

# 2.1 Support for Xilinx Virtual Cable

Support was added in OpenIPMC-FW for the Xilinx Virtual Cable (XVC) protocol, which allows an instance of the Vivado development suite running on a PC to control a JTAG master interface on the IPMC over the network (Fig. 3a). This interface, used to program and debug FPGAs and SoCs manufactured by AMD Xilinx, is broken out on a set of standardized pins on the OpenIPMC-HW edge connector, such that the board designer can route these JTAG signals to onboard devices. XVC support is not part of the ATCA standard but is important in the foreseen application of the IPMC in the back-end electronics of LHC experiments, as the latter make extensive use of FPGA devices. In the OpenIPMC-FW implementation, the bit-banging and capture of the JTAG output and input signals are offloaded to a DMA controller driven by a hardware timer. This offloading solution provides very fast and consistent timing for the signals while keeping the processor resource usage low. In our tests, we were able to successfully program FPGAs of the Spartan-6 (using the ISE 14.7 suite), Artix-7 and Kintex-7 (Fig. 3b) families, with a maximum configurable JTAG speed of 5.0 Mbps during bursts (Fig. 3c) and an average speed of 1-2 Mbps when using XVC over a low-latency LAN connection. Once validated with these tests, the XVC server has been adopted as a development tool and is now regularly used to debug the Zynq Ultrascale+ device installed on the Apollo board. We expect that a hardware revision of the Serenity board will enable the same function in the near future.

## 2.2 Support for Syslog

A mechanism to transmit alert, debug and monitoring messages from the IPMC devices to a monitor device over the network is very useful to identify software bugs and take action in case of faults, both during the early development phase in the laboratory using a small number of devices and, later, in the production phase when operating several hundred or thousand devices. The Syslog protocol is not part of either the IPMI or ATCA standards but has grown into one of the most

(a) Connection between Vivado, HW server, OpenIPMC XVC server and FPGA.

(b) XVC used to debug a Kintex-7 board. (c)

(c) Test pattern on TCK, TMS, TDI signals.

Figure 3: Testing of the XVC JTAG server implemented in OpenIPMC.

used standards in the IT industry to transport such messages over UDP/IP packets. The standard is defined in two incompatible versions by the IETF documents RFC 3164 [11] and RFC 5424 [12]. In OpenIPMC-FW, support for both of these standards was added, with the possibility for the user to choose - at compile time - which RFC standard to use for its Syslog client. A run-time configuration parameter allows the user to choose the UDP/IP address and port of the Syslog server which will receive the messages. Following the implementation of Syslog into the firmware, the client was successfully tested to interface with an instance of Grafana Loki OSS [13], a free and open-source log aggregator designed for cloud deployment.

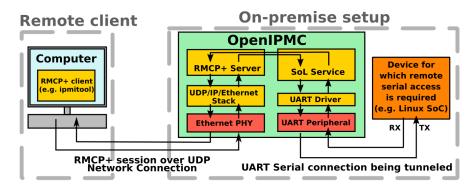

## 2.3 Support for RMCP/RMCP+ and Serial-Over-LAN

ATCA boards targeted by the OpenIPMC project, such as Serenity and Apollo, feature an onboard embedded computer running Linux to perform high-level tasks such as detector calibration. To facilitate the management of this computer when it has problems booting or is no longer directly accessible from the network, it is desirable to have remote access to its serial terminal, exposed on one of its UART interfaces [16]. The IPMI v1.5 standard [14], on which part of the ATCA standard is based, defines the use of the Remote Management Control Protocol (RMCP) to transport IPMI messages over the network, and the subsequent IPMI v2.0 standard [15] adds new IPMI features (RMCP+) to RMCP, including the possibility of tunneling the input and output of a serial line over a network session, a feature known as *Serial-over-LAN (SoL)* and shown on Fig. 4. OpenIPMC-FW has been updated to support RMCP+ SoL. This feature was tested in a bench top setup to monitor the boot log of a Raspberry Pi single-board computer and to access its Linux terminal via a remote connection established using the open source IPMI software package *ipmitool* [17]. The tests showed the SoL terminal session to work and helped to tune the buffer sizes to avoid dropped characters. Further tests are planned for Serenity and Apollo once the new revisions of these boards

Figure 4: Functional scheme of the Serial-over-LAN application case.

become available, providing the needed UART connections to the IPMC.

#### 2.4 YAFFS storage, TFTP server and configuration database

A subset of the configuration settings for the IPMC may need to be frequently changed by the user (e.g. changing the Syslog server address or forcing a specific IP address for the device) and therefore need to be stored in RAM to allow its manipulation. At the same time, it is desirable that these settings are not wiped upon a system reset and, therefore, a mechanism should make them persistent. OpenIPMC-FW has been updated to support the Yet Another Flash File System version 2 (YAFFS2)[18] to mount a file system in a region of the external 128 MiB QSPI flash installed on the mezzanine PCB. The file system can be browsed from the IPMC Command Line Interface (CLI) and files can be moved, copied, deleted and edited (Fig. 5). A Trivial File Transfer Protocol (TFTP)[19] server running in the firmware gives access to the mounted file system, such that files can be uploaded and downloaded remotely. Furthermore, OpenIPMC-FW saves run-time configuration settings in an in-memory dictionary, with entries which can be added, modified and deleted directly from the CLI by the user. The in-memory set of settings can also be saved into the file system as a set of human-readable files, which provides an excellent integration with the TFTP server. The settings stored in the file system are used to provide persistence and to bootstrap the in-memory configuration database after each reboot of the system.

| <pre>&gt;&gt; ls lost+found inode 2 etc inode 257 &gt;&gt; ls /etc syslog.conf inode 260 &gt;&gt; print /etc/syslog.conf syslog.ip=192.168.200.1 syslog.port=514</pre> | length 2032<br>length 2032<br>length 40 | drw- directory<br>drw- directory<br>-rw- data file |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------|

Figure 5: Browsing the content of the file system from the CLI.

#### 2.5 ClientID in DHCP

In a large ATCA electronic system, such as the back-end of an HL-LHC experiment, it is useful to assign an unique address to each specific slot able to accommodate an electronic board (*geographical addressing*), such that the identity and role of physically identical boards can be defined at runtime by the position they occupy. This organization helps the centralized management of the infrastructure and speeds up the replacement of failed boards, since the spares do not need to be pre-programmed with a specific identity and software before their insertion. The PICMG ATCA HPM.3 [22] standard defines a scheme to implement this geographical addressing using the DHCP protocol [20], which is commonly used in networks to auto-configure the connected devices. Following the HPM.3 specification, support was added into OpenIPMC-FW for option 61 of the DHCP standard [21] (ClientID), which allows a device to declare its identity using an unique 20-byte name when using the DHCP protocol to request an IP address. In the OpenIPMC-FW implementation, the device ClientID is built from from the unique ATCA shelf name and the slot position occupied by the board in the ATCA shelf, such that each slot corresponds to a well-defined IP address which can be used to remotely control and configure the board hosted into it.

#### **3** Conclusion and outlook

In this article, we discussed the recent developments in the OpenIPMC project. Support for Xilinx Virtual Cable (XVC) to program FPGAs, Syslog for sending alert and debugging messages, RMCP/RMCP+ and Serial-Over-LAN (SoL) to remotely access an onboard UART interface, and the creation of a configuration database are some of the most important firmware improvements. Most of these features have been implemented to fulfill specific requirements of the Serenity and Apollo ATCA boards, RMCP/RMCP+/SoL and the ClientID in DHCP being specified in the IPMI 2.0 standard from which PICMG 3.0 (ATCA) derives and the PICMG HPM.3 standard, respectively. Nevertheless, all the new features are commonly used in embedded computing applications and are expected to be available for use in applications beyond the aforementioned ATCA boards. For example, the XVC function in OpenIPMC enables remote programming and debugging for FPGA devices in experiments where physical access is restricted due to space or other constraints.

#### Acknowledgments

The authors acknowledge the Fundação de Amparo à Pesquisa do Estado de São Paulo (FAPESP) for its financial support through grants number 18/18955-0 and 18/25225-9 and the Brazilian National Council for Scientific and Technological Development (CNPq) for its support through the INCT CERN-Brazil program (406672/2022-9). Marvin Fuchs acknowledges the support by the Doctoral School "Karlsruhe School of Elementary and Astroparticle Physics: Science and Technology". We thank the members of the CMS Phase-2 Tracker Upgrade Data Processing Systems group, and in particular G. Iles, M. Pesaresi, P. Wittich, and T. Williams for the help in defining the requirements for IPMCs used in the Phase-2 back-end boards.

#### References

- I. Zurbano Fernandez *et al.*, "High-Luminosity Large Hadron Collider (HL-LHC): Technical design report," CERN, 2020, ISBN 978-92-9083-586-8, 978-92-9083-587-5, doi:10.23731/CYRM-2020-0010

- [2] PICMG, "PICMG 3.0 AdvancedTCA Base Specification", Revision 3.0, March 24, 2008.

- [3] A. Albert *et al.* "The Apollo ATCA Platform," PoS TWEPP2019 (2020), 120, doi:10.22323/1.370.0120 [arXiv:1911.06452 [physics.ins-det]].

- [4] A. Rose *et al.* "Serenity: An ATCA prototyping platform for CMS Phase-2," PoS TWEPP2018 (2019), 115 doi:10.22323/1.343.0115

- [5] G. Iakovidis, L. Levinson, Y. Afik, C. Alexa, T. Alexopoulos, J. Ameel, D. Amidei, D. Antrim, A. Badea and C. Bakalis, *et al.* "The New Small Wheel electronics," JINST **18** (2023) no.05, P05012 doi:10.1088/1748-0221/18/05/P05012 [arXiv:2303.12571 [hep-ex]].

- [6] V. Amoiridis *et al.* [CMS], "CMS phase-2 DAQ and timing hub prototyping results and perspectives," JINST **17** (2022) no.05, C05003 doi:10.1088/1748-0221/17/05/C05003

- [7] "OpenIPMC repository", https://gitlab.com/openipmc/openipmc. Accessed Oct 24, 2023.

- [8] L. Calligaris, A. Cascadan, L. E. Ardila-Perez, B. Casu, A. F. da Costa, A. A. Shinoda, L. Arruda Ramalho and O. Sander, "OpenIPMC: A Free and Open-Source Intelligent Platform Management Controller Software," IEEE Trans. Nucl. Sci. 68 (2021) no.8, 2105-2112 doi:10.1109/TNS.2021.3092689 [arXiv:2011.01088 [physics.ins-det]].

- [9] L. Calligaris, A. Cascadan, L. E. Ardila-Perez, M. Pesaresi, G. Fedi, A. Peck and D. Gastler, "A flexible and low-cost open-source IPMC mezzanine for ATCA boards based on OpenIPMC," JINST 17 (2022) no.03, C03007 doi:10.1088/1748-0221/17/03/C03007 [arXiv:2112.12888 [physics.ins-det]].

- [10] S. Ahuja et al., "A Full Mesh ATCA-based General Purpose Data Processing Board (Pulsar II)," doi:10.2172/1431570

- [11] C. Lonvick, IETF Network Working Group, "The BSD syslog Protocol," The Internet Society (2001), https://datatracker.ietf.org/doc/html/rfc3164.

- [12] R. Gerhards, IETF Network Working Group, "The Syslog Protocol," IETF Trust and the authors (2009), https://datatracker.ietf.org/doc/html/rfc5424.

- [13] Grafana Labs, "Grafana Loki OSS," https://grafana.com/oss/loki/.

- [14] Intel Hewlett-Packard NEC Dell, "Intelligent Platform Management Interface Specification v1.5," Document Revision 1.1, February 20, 2002.

- [15] Intel Hewlett-Packard NEC Dell, "Intelligent Platform Management Interface Specification v2.0," Document Revision 1.1, February 20, 2002.

- [16] AMD Xilinx, "Zynq UltraScale+ Device TRM," UG1085 (v2.3.1) January 4, 2023, https://docs.xilinx.com/r/en-US/ug1085-zynq-ultrascale-trm.

- [17] The ipmitool developers, "ipmitool," https://codeberg.org/IPMITool/ipmitool.

- [18] Charles Manning, Aleph One Ltd., "YAFFS2 Specification," https://yaffs.net/yaffs-2-specification.

- [19] K. Sollins, IETF Network Working Group, "The TFTP Protocol (revision 2)," IETF Trust and the authors (1992), https://datatracker.ietf.org/doc/html/rfc1350.

- [20] R. Droms, IETF Network Working Group, "Dynamic Host Configuration Protocol," IETF Trust and the authors (1997), https://datatracker.ietf.org/doc/html/rfc2131.

- [21] S. Alexander, IETF Network Working Group, "DHCP Options and BOOTP Vendor Extensions," IETF Trust and the authors (1997), https://datatracker.ietf.org/doc/html/rfc2132.

- [22] PICMG, "PICMG HPM.3 R2.0P LAN-Attached IPM Controller Specification", Revision 2.0, May 4, 2016.

- [23] IPC, "Design and Assembly Process Implementation for Bottom Termination Components (BTCs)", IPC-7093A, 2016,