# Amplifying Main Memory-Based Timing Covert and Side Channels using Processing-in-Memory Operations

Konstantinos Kanellopoulos<sup>†\*</sup> F. Nisa Bostancı<sup>†\*</sup> Ataberk Olgun<sup>†</sup>

A. Giray Yağlıkçı<sup>†</sup> İsmail Emir Yüksel<sup>†</sup> Nika Mansouri Ghiasi<sup>†</sup>

Zülal Bingöl<sup>†‡</sup> Mohammad Sadrosadati<sup>†</sup> Onur Mutlu<sup>†</sup>

<sup>†</sup>ETH Zürich <sup>‡</sup>Bilkent University

The adoption of processing-in-memory (PiM) architectures has been gaining momentum because they provide high performance and low energy consumption by alleviating the data movement bottleneck. Yet, the security of such architectures has not been thoroughly explored. The adoption of PiM solutions provides a new way to directly access main memory, which can be potentially exploited by malicious user applications. We show that this new way to access main memory opens opportunities for high-throughput timing attack vectors that are hard-to-mitigate without significant performance overhead.

We introduce IMPACT, a set of high-throughput main memory-based timing attacks that leverage characteristics of PiM architectures to establish covert and side channels. IM-PACT enables high-throughput communication and private information leakage. To achieve this, IMPACT (i) eliminates expensive cache bypassing steps required by processor-centric main memory and cache-based timing attacks and (ii) leverages the intrinsic parallelism of PiM operations. First, we showcase two covert-channel attack variants that run on the host CPU and leverage PiM architectures to gain direct and fast access to main memory and establish high-throughput communication covert channels. Second, we showcase a side-channel attack on a DNA sequence analysis application that leaks the private characteristics of a user's sample genome by leveraging PiM operations. Our results demonstrate that (i) our covert channels achieve up to 14.16 Mb/s communication throughput, which is 5.41× faster than the state-of-the-art main memory-based covert channels, and (ii) our side-channel attack allows the attacker to determine the properties of a sample genome at a throughput of 7.5 Mb/s with 96% accuracy. We discuss and evaluate several countermeasures for IMPACT to enable secure and robust PiM architectures.

#### 1. Introduction

Data movement between the main memory and the processor is a prevalent bottleneck present in today's computing systems [1–22]. Hence, both industry and academia have invested significant efforts to bring computation closer to where data resides, creating a paradigm called *processing-in-memory* (PiM) [1, 2, 8, 11, 13, 19, 23–28]. PiM solutions provide significant performance improvement and energy efficiency by alleviating data movement.

PiM solutions generally take one of two approaches: (i)

processing-near-memory (PnM), and (ii) processing-usingmemory (PuM). First, PnM techniques offload computation to compute units near memory arrays (e.g., in the logic layer of 3D-stacked memory or within the memory chip) [21, 29–42]. During recent years, multiple real-world PnM systems have emerged, such as UPMEM [43], AxDIMM [41], AiM [44], HB-PNM [45] and FIMDRAM [46]. At the same time, several academic works propose using general-purpose programmable PiM devices where the user application offloads instructions to the compute units inside the memory at fine-granularity [47] (e.g., PiM-enabled instructions [48]) or coarse granularity (i.e., full program [20, 49]). Second, PuM techniques propose exploiting the analog properties of memory operations and performing specialized PiM operations. Prior works improve the performance of workloads by providing bulk data copy and initialization, bitwise operations, and arithmetic operations using memory [49–64]. However, to the best of our knowledge, no prior work evaluates the security of PiM architectures against timing attacks.

Analyzing and evaluating the security of PiM architectures is critical to prevent widespread vulnerabilities as PiM architectures become widely available. After a thorough analysis of existing PiM architectures, in this work, we show that the adoption of PiM solutions creates opportunities for high-throughput main memory-based timing attacks for two main reasons: (i) PiM provides direct access to main memory, and (ii) a large set of existing practical defense mechanisms are not applicable in PiM systems.

- 1. Direct Access to Main Memory. Timing attacks in PiM architectures become easier to exploit with the direct memory access provided to user space applications by these architectures. The adoption of PiM techniques changes how applications and computation units access *main memory*: (i) due to area and thermal dissipation limitations, compute units in PnM architectures have small or no caches that allow the user space applications to bypass caches more easily (i.e., with fewer memory accesses), and (ii) PuM architectures provide the ability to offload specialized PiM instructions (e.g., bulk data copy and initialization, and bitwise/arithmetic operations) to the main memory that completely bypass the deep cache hierarchies of modern processors.

- **2. Hard-to-Mitigate with Practical Defenses.** A fundamental solution to memory-based timing attacks is to eliminate the timing channel itself. Prior mitigations explore fundamental

<sup>\*</sup>K. Kanellopoulos and F. N. Bostancı are co-primary authors.

solutions such as memory partitioning and enforcing constant-time memory accesses. However, these mitigations incur significantly high performance overheads (as shown in Section 6). Therefore, practical mitigations and detection mechanisms restricting access to timing channels are explored. Several prior works [65–68] propose cache management-based methods such as restricting the access to cache management instructions (e.g., clflush instruction in x86 systems [65]) and detecting timing attacks based on cache access patterns (e.g., a high number of cache misses can indicate a timing attack) [66–68]. These mechanisms are inapplicable to PiM-based attacks because these attacks completely bypass the cache hierarchy.

**Our goal** is to develop a set of high-throughput and hard-to-mitigate timing side and covert-channel attacks in PiM architectures. We expect and hope that IMPACT will bring attention to security issues in emerging PiM architectures and result in security awareness in PiM architecture designs.

In this work, we introduce IMPACT, a set of high-throughput main memory-based timing attacks that leverages PiM architectures to gain direct and fast access to main memory, establish high-throughput communication covert channels and leak secrets of concurrently running applications. IMPACT leverages the direct access, provided by PiM operations, to the shared DRAM row buffer and achieves high communication and information leakage throughput by (i) eliminating expensive cache bypassing steps required by other main memory- and cache-based timing cover-channel attacks and (ii) leveraging the intrinsic parallelism of PiM operations.

**Key Challenge and Limitations of Prior Work.** For successful main memory-based timing side- and covert-channel attacks, attacker processes (or sender and receiver processes for covert-channel attacks) need to access the main memory with high frequency to observe or change the states of the shared main memory structures. In traditional architectures, it is difficult to access the main memory with high frequency due to the deep cache hierarchies that filter the memory requests of attacker processes.

We analyze (Section 3.2) the effectiveness of the attack primitives that bypass caches and provide direct access to the main memory to leverage the main memory timing channel: clflush instruction, eviction sets, (remote) direct memory access, (R)DMA, requests, non-temporal memory hints (e.g., movnti instruction [69]), and PiM operations. None of these primitives used in traditional architectures provide *fast* and *reliable* direct memory access at the same time. In contrast, PiM operations provide fast and reliable direct memory access to the user space applications. Therefore, PiM architectures can be more amenable to high-throughput timing side- and covert-channel attacks compared to traditional architectures.

**IMPACT Covert-Channel Attack Variants.** We showcase two different timing covert-channel attack variants by exploiting PnM and PuM techniques. First, we build a PnM-based covert channel, IMPACT-PnM, that uses PiM-enabled instructions [48] to directly access the main memory. The sender bypasses the locality monitor employed by the system and of-

floads PiM-enabled instructions for computation directly inside the main memory. The receiver measures the time it takes to access a specific set of rows to retrieve the message encoded with row buffer hits and conflicts. IMPACT-PnM achieves 12.87 Mb/s communication throughput, which is up to 5.79× faster than the state-of-the-art main memory-based covert-channel attack [70]. Second, we present IMPACT-PuM, a PuM-based covert channel that leverages the inherent parallelism in main memory using bulk copy and initialization techniques, specifically RowClone [55], to quickly transmit messages through the shared row buffer states. This way, IMPACT-PuM transmits 16-bit large messages 14× faster than IMPACT-PnM and achieves communication throughput of 14.16 Mb/s (up to 6.38× faster than the state-of-the-art [70]).

IMPACT Side-Channel Attack. We showcase a side-channel attack on a DNA sequence analysis application: DNA read mapping. Preserving the privacy of DNA sequences is crucial, especially when the sequences are used for medical purposes. DNA read mapping finds the matching locations of short DNA fragments of the sample genome in the reference genome, which acts as a template genome to construct the complete genome of a given sample. Our side-channel attack leverages PiM operations and leaks the private characteristics of a user's sample genome by observing the memory access patterns of the DNA read mapping application. Our evaluation demonstrates that our side-channel attack enables determining the properties of a sample genome at a throughput of 7.5 Mb/s with 96% accuracy.

**Defense Mechanisms.** Based on our security analysis, we discuss three and evaluate two potential defense mechanisms that can mitigate IMPACT attacks by eliminating the timing channel. We discuss the performance versus security tradeoffs of these countermeasures. We demonstrate that the two best-performing defense mechanisms lead to high performance overheads of 25% and 16% on average across five data-intensive workloads.

This paper makes the following contributions:

- We present IMPACT, the first timing attack in PiM systems.

We leverage the direct memory access enabled by PiM operations to establish high-throughput and reliable timing covert channels.

- We showcase two IMPACT variants by exploiting PnM and PuM techniques: IMPACT-PnM and IMPACT-PuM. IMPACT-PnM allows the sender and the receiver to exchange messages by using PiM instructions. IMPACT-PuM further leverages the parallelism provided by bulk copy PuM techniques to improve the throughput. We extensively evaluate both IMPACT-PnM and IMPACT-PuM and show that they significantly improve communication throughput compared to the state-of-the-art main-memory-based covert channel.

- We showcase an IMPACT side-channel attack on DNA read mapping by leveraging PnM instructions. We show that our side-channel attack enables the attacker to leak sensitive information on the victim's sample genome with high throughput and a low error rate.

- We evaluate two defense mechanisms to protect the system

against IMPACT attacks caused by the adoption of PiM solutions. We discuss the trade-offs of these mechanisms to aid the adoption of robust and secure PiM architectures.

#### 2. Background

#### 2.1. DRAM Organization and Operation

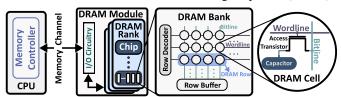

Organization. Figure 1 illustrates a DRAM module's hierarchical organization. A DRAM chip is organized into multiple DRAM banks, each of which shares a common I/O circuitry in a DRAM bank [71-75]. DRAM cells are organized as a two-dimensional array to form a bank and are addressed by its row and column [22,76-78]. The DRAM cell is connected to a bitline that is used to access the data stored in the cell and a wordline that controls access to the cell. Each DRAM cell in a DRAM row is connected to a common wordline via its access transistors. A bitline connects a column of DRAM cells to a DRAM sense amplifier to read or write data. A row of sense amplifiers is called a row buffer [55, 56, 79–82]. At the lowest level of the hierarchy, a single DRAM cell comprises 1) a storage capacitor that stores a single bit of data encoded using the charge level in the capacitor and 2) an access transistor that is used to read from and write to the storage capacitor [83–87].

Figure 1: Organization of a typical modern DRAM module.

**Operation.** The memory controller serves memory access requests. To serve memory requests, the memory controller issues DRAM commands, e.g., row activation (ACT), bank precharge (PRE), data read (RD), data write (WR), and refresh (REF). Between consecutive DRAM commands, the memory controller must obey standardized timings to ensure correct DRAM operation. For read and write requests, the memory controller first issues an ACT command to the corresponding bank, which opens the corresponding row. The data in the row is fetched to the row buffer, where it is temporarily stored. The data in the row buffer becomes accessible by a RD/WR command when the bitline and cell voltage are restored to a certain level. Hence, the memory controller should wait at least the activation latency  $(t_{RCD})$  between an ACT and a RD/WR command. All changes are propagated to the DRAM cells in the open row. Subsequent accesses to the same row can be served quickly without fetching the data to the row buffer, creating a row hit [88]. However, in the case where the target row is not in the row buffer, the memory controller issues a PRE command to close the already open row and issues an ACT command to fetch the target row, creating a row conflict/miss. The time interval for issuing 1) a PRE after an ACT must be at least restoration latency ( $t_{RAS}$ ) and 2) an ACT after a PRE must be at least the precharge latency  $(t_{RP})$ .

#### 2.2. Processing-in-Memory

Processing-in-memory (PiM) is a promising paradigm that moves computation closer to where the data resides, alleviating the data movement bottleneck between memory and the processor [1, 2, 8, 11, 13, 19, 23–28]. There are two main approaches to PiM: 1) processing-near-memory (PnM) and 2) processing-using-memory (PuM).

Processing Near Memory (PnM). In processing-near-memory (PnM) computation is placed near the memory arrays. PnM takes advantage of the computation capability of conventional memory controllers or the logic layer(s) of the 3D-stacked memory technologies [21, 29–42]. PnM logic can execute portions of applications (e.g., instructions [32,48], functions [28], whole application threads [20, 49]) depending on the PnM architecture. PnM computation units typically employ small caches due to 1) area constraints in the PnM logic and 2) the ineffectiveness of caches in improving the performance of a wide range of memory-intensive applications. Therefore, various PnM systems [28, 32, 48] execute the memory-intensive regions of applications on the PnM computation units, while executing the more cache-friendly regions of applications on the host CPU with a deeper cache hierarchy.

Processing Using Memory (PuM). Processing Using Memory (PuM) expands the functionality of the memory arrays with minimal changes so that they can perform computation [49–64]. This approach leverages the properties and operational principles of memory cells and arrays to perform computation, without the need for dedicated logic unit added to the memory system. PuM architectures take advantage of the high bandwidth of the memory arrays.

#### 2.3. Microarchitectural Timing Attacks

Microarchitectural timing attacks exploit the observable state changes in microarchitecture to build covert channel attacks that can propagate messages between processes and leak secrets of concurrently running processes. These attacks measure the time to complete an operation that depends on the shared structures in the system (e.g., accessing a memory location by going through the shared caches) to infer the states of these shared structures.

Main Memory Timing Attacks. Existing main memory timing attacks exploit several shared structures in the main memory to leak data, and one such structure is the row buffer. The row buffer acts as an internal cache inside DRAM banks. Thus, an attacker can understand if a row is recently accessed (i.e., already in the row buffer) or not by measuring access to that row. Based on this observation, prior works propose several attacks, revealing the DRAM address mapping and leaking keystrokes. DRAMA [70] (i) builds a covert channel that exchanges messages between processes using the row buffer conflicts and hits, and (ii) showcases a side-channel attack that can leak keystrokes in a real system. Similarly, many works [70, 89,90] exploit row buffer-based timing differences to determine DRAM address mappings. Other attacks based on the main memory exploit either the memory bus [91], or observations of latencies incurred by other memory-related operations such as memory deduplication [92, 93], and memory compression [94–101] and decompression [102].

#### 3. A Case for PiM-based Timing Attacks

The adoption of *processing-in-memory* (PiM) architectures has been gaining momentum in recent years because they provide high performance and low energy consumption by alleviating the data movement bottleneck. Therefore, it is timely and critical to analyze and evaluate the security of PiM architectures to prevent any of their vulnerabilities from causing widespread susceptibility as PiM architectures become widely available. Unfortunately, no prior work investigates and evaluates the security challenges of new and emerging PiM architectures. After a thorough analysis of existing PiM architectures, we show that the adoption of PiM solutions creates opportunities for highthroughput main memory-based timing attacks for two main reasons. First, the adoption of PiM solutions in the forms of processing-near-memory (PnM) and processing-using-memory (PuM) exposes the internal states of the main memory (e.g., row buffer states of DRAM banks) by providing direct access to the user space applications. Second, timing attacks in PiM architectures can be more difficult to detect and mitigate due to commonly employed mechanisms, like cache monitoring mechanisms that track the cache miss ratio during runtime to detect anomalies [66–68], being either inapplicable or performanceinefficient in PiM architectures.

#### 3.1. Row Buffer Timing Channel

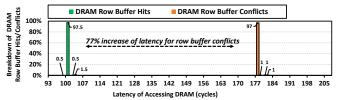

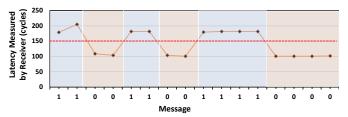

A DRAM row buffer acts as a direct-mapped cache inside a DRAM bank and is shared across applications that can access main memory. Accessing a row that is already cached in the row buffer results in a significantly lower latency because the memory controller does *not* need to issue additional commands, *PRE* to precharge the open row and *ACT* to fetch the target row to the row buffer. Therefore, it is possible for a user space application to infer whether a row is accessed recently by measuring the time it takes to access the row. To demonstrate the latency gap between different states of the row buffer, we evaluate microbenchmarks that create memory accesses that result in row buffer hits and conflicts, and we measure the latencies observed by the user space application. Figure 2 shows the breakdown of memory access latencies categorized into two classes: row buffer hits and conflicts.

Figure 2: The distribution of memory access latencies.

We observe that the average latency gap between a row buffer conflict and a row buffer hit is 74 CPU cycles. Since this latency gap is large enough to detect, it is possible for user space applications that share the main memory to exploit the row buffer as a covert channel to exchange messages. Our results align with the observations of prior works [70].

#### 3.2. Existing Main Memory Attack Primitives

Main memory timing attacks are powerful as they can be used to gather information on applications that share main memory and establish covert channels to exchange messages between different processes. However, these covert-channel attacks are limited in throughput in traditional architectures for two main reasons: (i) accessing a memory location in main memory requires expensive cache bypassing techniques due to frequently accessed data being cached to improve performance, and (ii) even when bypassing the cache hierarchy, deep cache hierarchies employed in modern processors incur an additional high lookup latency on memory requests that are eventually sent to main memory.

There are several ways to bypass the cache hierarchy in traditional systems by using one or more of four attack primitives: (i) using specialized instructions to flush a cache line (e.g., clflush), (ii) using cache eviction sets (i.e., by creating many conflicting memory requests to replace the cache line with newly-fetched cache lines), (iii) memory access requests generated by direct memory access (DMA) and remote direct memory access (R-DMA) engines, and (iv) non-temporal memory hints (e.g., movnti). However, when used in a main memory-based timing covert channel attack, these methods do *not* provide fast and reliable communication.

Effectiveness Low Latency No Cache Timing Difference ISA No Excessive Memory Accesses Detectability Guarantees Lookup Specialized Х / Instructions Eviction Sets DMA/R-DMA Х N/A

/

1

х

Table 1: Efficiency and Effectiveness of Attack Primitives

We identify four properties of an efficient (i.e., low-latency) and effective attack primitive: 1) avoiding cache lookup overhead, 2) avoiding high-latency memory accesses, 3) creating an easily detectable timing difference, and 4) reliable functionality (e.g., guaranteed to work by the ISA). Table 1 shows a comprehensive comparison of these four attack primitives in terms of these properties.

First, specialized cache line flush instructions have two main disadvantages that hurt the efficiency and effectiveness of attacks that use them: 1) they put the latency of writing back a cache line to the main memory on the critical path to access a memory location, and 2) in some modern systems, these instructions are privileged and cannot be used by user space applications.

Second, eviction sets require a large number of load requests proportional to the number of ways in the caches, which scales with modern designs. Therefore, the attacks that use them have limited throughput. While the ISA guarantees the instructions used to create the eviction sets, the eviction set is not guaranteed to evict the target cache line (due to cache characteristics such

Non-temporal

Memory Hints

PiM Operations

Х

as cache replacement policy, cache prefetchers etc.).

Third, DMA and R-DMA engines incur high overheads due to deep software stacks. As a result, attacks using this primitive need to utilize states with larger timing differences to be distinguishable. An example attack using this primitive [103] showcases a covert channel attack based on memory contention. However, the basis of this type of covert channel is not as finegrained as row buffer-based timing differences. Therefore, the communication throughput these covert channels provide is limited (in the order of Kb/s).

Fourth, the implementation of non-temporal memory hints varies across systems, as system designers are not bound to a specific approach. Consequently, the ISA does not guarantee that memory accesses related to non-temporal hints will consistently bypass caches.

In contrast, PiM architectures provide fast and reliable direct memory access to user space applications that can be used to establish a covert-channel attack.

### 3.3. High Throughput Main Memory-based Covert Channels

To demonstrate the impact of the latencies induced by deep cache hierarchies (i.e., cache access and cache eviction latencies) on communication throughput, we simulate a realistic system (described in Section 5.1) that establishes a state-of-the-art covert channel [70].

Attack Scenarios. We simulate two attacks. First, we evaluate a *baseline attack* that relies on cache bypassing using cache eviction sets. To transmit a bit through the row buffer, the baseline attack first evicts the corresponding cache line and then, it fetches the target row into the row buffer using an additional memory request. The baseline attack accomplishes cache line eviction by issuing N memory requests to the target cache set in an N-way cache. Note that the actual eviction latency can be much higher due to a larger number of memory accesses required to bypass more complex replacement policies employed in today's systems or due to address translation overheads. Second, we evaluate a *direct memory access attack* that can directly access the main memory. The direct memory access attack issues a memory request to fetch the data to the row buffer and does not need any cache access or eviction steps.

For both attacks, we measure the time it takes to send a bit through the row buffer including cache access and cache eviction latencies, and with encoding logic-1 values as row buffer hits and logic-0 as row buffer conflicts. We calculate the communication throughput based on the average time needed to propagate bits from the sender to receiver. We analyze the impact of (i) the LLC size, and (ii) the number of LLC ways on communication throughput to show the limitations in current and future systems with different cache designs.

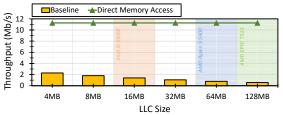

Impact of LLC Size on Communication Throughput. Figure 3 shows the throughput of *baseline* and *direct memory access* attacks. The x-axis shows the cache configuration with increasing last-level cache (LLC) sizes and a fixed number of ways (i.e., 16). To calculate the cache access latency with increasing LLC sizes, we followed the same methodology used in

prior works [104]. To better understand the throughput results, Figure 4 shows the latency of a cache line eviction of caches with corresponding sizes.

Figure 3: Impact of the LLC size on the data leakage throughput of covert channels.

Figure 4: Latency of a cache line eviction in CPU cycles with increasing LLC size.

We make two key observations. First, the communication throughput of the direct memory access attack is 11.27Mb/s across all LLC sizes, which is significantly greater than the throughput of up to 2.29Mb/s achieved by the baseline attack. Second, the baseline attack's throughput decreases with increasing LLC sizes due to increasingly expensive cache access and eviction latencies. We observe that with increasing LLC size, the eviction latency grows significantly due to the increase in access latency. We conclude that with increasing LLC sizes, the cache access and eviction latencies grow significantly and significantly hinder the communication throughput of the baseline attack compared to the direct memory access attack which is independent of the LLC size.

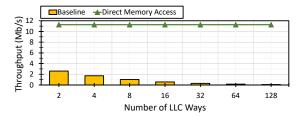

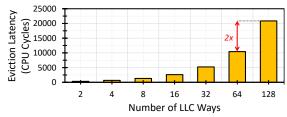

Impact of LLC Associativity on Communication Throughput. Figure 5 shows the communication throughput of *baseline* and *direct memory access* attacks. The x-axis shows the increasing number of LLC ways (from 2 to 128) while the total LLC size is fixed at 16 MB (modern processors typically employ 8 cores and a 2MB LLC slice per core). Increasing the number of LLC ways increases the number of memory requests required to evict a cache line from the cache. To better understand this effect, Figure 6 shows the latency of a cache line eviction across increasing numbers of LLC ways. We observe that the baseline attack's communication throughput decreases significantly with increasing number of LLC ways due to the increased cache eviction latency.

We conclude that attacks that communicate with main memory through caches are greatly limited in throughput due to expensive cache lookup and eviction latencies, which worsen with increasing size and associativity. However, a covert channel based on direct memory access can achieve high throughput independent from cache configurations as it does not require bypassing the cache hierarchy.

Adoption of PiM solutions can fundamentally enable high-

Figure 5: Impact of the number of LLC ways on the data leakage throughput of covert channels.

Figure 6: Latency of evicting a set in CPU cycles with increasing number of LLC ways.

throughput timing attacks through main memory by providing direct access to the main memory to user space applications. Therefore, it is crucial to carefully consider the security implications of PiM architectures and to develop robust security measures to protect against potential attacks. **Our goal** is to develop a set of high-throughput and hard-to-mitigate timing side and covert-channel attacks in PiM architectures. We expect and hope that IMPACT will bring attention to security issues in emerging PiM architectures and result in security awareness in PiM architecture designs.

# 4. IMPACT: A High-Throughput Main Memory Timing Attack

This section introduces IMPACT, a set of high-throughput main memory timing attacks that takes advantage of the direct memory access enabled by the emerging processing-in-memory paradigm. IMPACT (i) operates independently of specialized instructions that flush data from the cache hierarchy and (ii) avoids the resource-intensive cache eviction steps typically required for main memory and cache-based timing attacks, achieving higher data leakage throughput than previous memory-based attacks. In this work, we present (1) two variants of IMPACT covert channel attack and (2) an IMPACT side-channel attack on DNA read mapping applications enabled by *processing-near-memory* (PnM) and *processing-using-memory* (PuM) solutions. We evaluate the communication throughput of IMPACT covert channels in Section 5.3 and the leakage throughput of IMPACT side channel in Section 5.4.

#### 4.1. IMPACT Covert-Channel Attacks

#### 4.1.1. PnM-based Covert-Channel Attack.

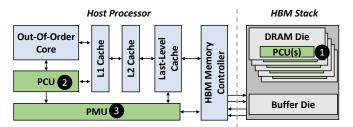

**Baseline PnM Architecture.** In IMPACT-PnM, we consider PiM-Enabled Instructions (PEI) [48] as the baseline PnM architecture. PEI expands the instruction set architecture (ISA) of the host processor with PIM-enabled instructions (PEIs), while keeping the existing programming model intact. A PEI is an instruction that can be executed either on the host processor or

on the in-memory computation logic which is integrated near each DRAM bank of an HBM stack. PEI can also easily be adopted in other memory technologies since its design does not rely on specific features of the memory technology. We chose PEI as the baseline PnM architecture as it introduces a simple and effective model (i.e., offloading computation at the instruction granularity) for PnM, and our attack vector can be generalized for other PnM architectures with similar design components (e.g., FIMDRAM [46]).

Figure 7 depicts the organization of PEI. PEI architecture consists of two key components. First, PEI integrates a PEI Computation Unit (PCU) near each DRAM bank 1 and inside the CPU **2**. In-memory PCUs are shared among all the cores of the host processor and are responsible for executing PEIs near the respective DRAM bank. Second, PEI adds a PEI Management Unit (PMU) 3 integrated with the last-level cache of the host system to (i) monitor the data locality of application regions and (ii) map each region to host-side or memory-side PCUs based on their data locality. This way a PEI can be selectively executed on the host processor PCU (instead of the in-memory PCU) when large on-chip caches are beneficial for its execution. As mentioned in [105], if a locality monitor entry is allocated by a PIM operation, it is often too aggressive to consider it as having high locality on its first hit in the locality monitor. Therefore, they propose adding an ignore flag per entry to ignore the first hit to an entry allocated by a PIM operation. Such a design allows us to easily bypass the locality monitor even with a small virtual address range in our disposal.

Figure 7: Overview of PEI's architecture.

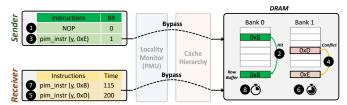

Attack Overview. The PnM-based covert channel (IMPACT-PnM) leverages the direct memory access provided by PiMenabled instructions, which bypasses the cache hierarchy. IMPACT-PnM exploits the timing difference between the latency of a DRAM row buffer hit and a conflict to exchange messages between the sender and the receiver. The sender transmits bits of the message to the receiver in multiple batches of M bits, where the value of each bit is encoded as interference (i.e., row buffer hits or conflicts) in the row buffer of a DRAM bank. We assume the sender and the receiver co-locate data in the same DRAM banks. In this attack, we encode logic-1 as interference in the DRAM bank, and logic-0 as no interference.

Figure 8 and Listing 1 show the end-to-end flow of IMPACT-PnM and all the steps involved in establishing the covert channel

<sup>&</sup>lt;sup>1</sup>If PiM is the main memory, then the sender can co-locate its data with the receiver process's data by using memory massaging techniques, as used in many prior works [70, 90, 106, 107]. Two processes can share data itself in various cases, such as databases and websites running on browsers.

between the sender and the receiver.

**Step 1.** The receiver issues PEI operations to initialize each DRAM bank by activating a predetermined row (Line 18). It is necessary that the cache lines of the activated row are not used before in order to bypass the locality monitor (PMU) that is employed in PEI-based systems. Then, the sender and the receiver synchronize on a barrier (Lines 5&20) which ensures that they start the communication turn at the same time.

Step 2. The sender starts the communication turn by issuing PEI instructions to activate a row in each DRAM bank (Lines 7-12) or not based on the bit value that will be transmitted. To transmit a 0, as shown in Fig. 8 (1) the sender does not activate any row in the corresponding DRAM bank to avoid causing interference in the row buffer (e.g., Row 0xB remains activated in the row buffer 2). To transmit a 1, as shown in Fig. 8 (3) the sender activates a row that is different from the one activated by the receiver to cause interference in the corresponding DRAM bank (i.e., a row buffer conflict between Row 0xD and Row 0xE 4). At the end of the communication turn (after transmitting M bits), the sender first executes a memory fence (Line 14) to ensure that all the PEI instructions have been executed before the receiver starts probing the DRAM banks and then signals the receiver to start probing the DRAM banks (Line 15).

Step 3. The receiver starts probing the DRAM banks by issuing PEI instructions to activate the same row as the one activated during initialization (Line 25). Then, the receiver measures the time it takes to complete the request (Line 27). If the latency of executing the PEI exceeds a predetermined hit threshold, the receiver senses the interference in the row buffer and decodes the bit as a 1 (Lines 28-29 5,6). Otherwise, the access is considered a row buffer hit and the receiver decodes the bit as a 0 (Lines 30-31 7,8). The sender and the receiver repeat the same steps for each batch until the entire message is transmitted.

**Sender-Receiver Synchronization.** The sender and the receiver synchronize in order to ensure that the sender's and receiver's actions (i) are accurately aligned so that they do not interfere with each other and fail to communicate the message and (ii) to overlap the sender and receiver operations to increase the throughput of the attack. To achieve this, the sender and the receiver communicate using semaphores. The value of the semaphore indicates the number of batches that the sender has completed transmitting but the receiver has not yet completed probing. When the sender completes the transmission of a batch of bits, they increment the semaphore to signal the receiver to start probing the DRAM banks. This way, the sender overlaps the transmission of multiple batches of bits with the receiver's probing operations without the need to wait for the receiver to complete the probing of the DRAM banks. Doing so, the sender can freely proceed to future batches without relying on synchronizing with the receiver. The receiver blocks on the semaphore until the sender increments it. When the semaphore is incremented, the receiver decrements it and starts probing the DRAM banks. When the receiver completes the probing of the DRAM banks, they read the semaphore again and the process repeats until the entire message is transmitted. In our

```

Sender:

2

message = [0: N-1]; //N banks and N-bit message

3

batch_size = M; //M-bits per batch where M<N

4

init semaphore(0):

5

barrier(); // synchronize with receiver

6

bank=0:

7

for every batch:

8

for each bit in batch_size;

9

if message[bank] == 1:

10

pim_add(row[bank]);

11

else:

12

NOP();

13

bank++;

14

// signal receiver

memory fence():

15

increment_semaphore(); // to start probing

16

17

Receiver:

18

init_row = initialize_DRAM_rows_with_PEIs();

19

bank = 0;

20

barrier(); // synchronize with sender

21

for every batch:

22

block_on_semaphore();//if semaphore==0, wait

23

for each bit in batch_size;

24

timer(start);

25

pim_add(init_row[bank]);

26

timer(end):

27

latency = end - start;

28

if latency > threshold:

29

result =

30

else:

31

result =

32

bank++;

```

Listing 1: Pseudocode of PnM-based Covert-Channel Attack.

Figure 8: Flow of the PnM-based Covert Channel Attack.

attack implementation (see §5.1) we use POSIX semaphores to implement the sender-receiver synchronization and use a batch size of 4 bits.

#### 4.1.2. PuM-based Covert Channel.

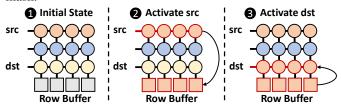

**Baseline PuM Architecture.** We assume a PuM architecture that provides user applications with RowClone [55] that enables bulk data movement operations (e.g., bulk data copy and initialization) within DRAM's subarray boundaries by exploiting the internal operations of DRAM.<sup>2</sup> For our attack, we focus on the *Fast Parallel Mode* in RowClone, which copies the data of a row to another row within a DRAM subarray.

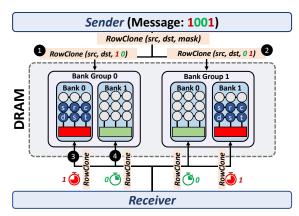

Figure 9 demonstrates how the content of the source row, i.e., *src*, is copied to the destination row, i.e., *dst* using RowClone's Fast Parallel Mode. Initially, the rows and the row buffer are closed (1). RowClone operation consists of two key steps.

<sup>&</sup>lt;sup>2</sup>There could be near-memory RowClone variants that move data without using operational principles of DRAM as well. However, in this attack, we assume a PuM-based RowClone operation.

First, the *src* is activated to store the entire row's data in the row buffer (2). Second, the *dst* is activated, which leads to copying the contents of the row buffer in the *dst* (3). RowClone significantly reduces the latency and energy consumption of the bulk data copy operation from one row to another as it enables data movement without transferring data between the DRAM and the processing units. To execute RowClone, we assume that the user space application specifies a source and a destination virtual address range and the corresponding mask to copy only specific parts of the source to the destination. This way, the memory controller receives one RowClone request and breaks it into parallel RowClone requests, one for each set bit of the mask.

Figure 9: Overview of RowClone's Fast Parallel Mode.

Attack Overview. PuM-based covert channel attack (IMPACT-PuM) exploits in-DRAM bulk copy operations to establish a covert channel between a sender and a receiver. The sender transmits a message by executing a RowClone operation with three operands: (i) a source address range, (ii) a destination address range, and (iii) a mask to select which parts of the ranges will be copied. Source and address ranges correspond to physical pages spanning across all DRAM banks and by using the mask, the sender can encode the transmitted message by causing contention only in selected DRAM banks. The receiver repeatedly issues RowClone operations and measures the time it takes to complete these operations. This way, it can detect contention in a DRAM bank when another process accesses a different row in the same DRAM bank. If the sender issues a RowClone operation to a DRAM bank, it induces contention and the receiver detects a higher latency for its RowClone operation. This latency indicates that the corresponding bit is a logic-1. Otherwise, if the sender does not induce contention to a DRAM bank, the receiver detects a lower latency for the RowClone operation, indicating that the corresponding bit is a logic-0.

Figure 10 and Listing 2 show the end-to-end flow of IMPACT-PuM and all the steps involved to establish the covert channel between the sender and the receiver.

**Step 1.** First, the receiver initializes all DRAM banks by issuing a RowClone operation to copy the contents of a source row to a destination row (Line 16). Then, the sender and the receiver synchronize on a barrier (Lines 10&17) which ensures that they start the communication turn at the same time.

**Step 2.** The sender uses a single RowClone operation to transmit in parallel an N-bit message (where N is the number of banks) to the receiver and encodes the message in the mask operand of the RowClone operation (Lines 11-12). The sender encodes the message by setting the corresponding bits in the

Figure 10: End-to-End Flow of the Processing-using-Memory Covert Channel Attack.

mask operand to 1 or 0 (1,2). Doing so, the sender causes contention in the corresponding DRAM banks and activates a different row in the row buffer. To send a 1, the sender triggers RowClone in the corresponding DRAM bank and induces contention by altering the activated row in the row buffer (3). To send a 0, the sender does not trigger RowClone in the corresponding DRAM bank and does not induce contention (4). The sender synchronizes with the receiver using a barrier operation (Lines 13&18).

```

1

Memory Controller:

2

row_clone(src, dst, mask):

3

for each DRAM bank do:

4

if mask[bank] == 1 then:

5

row_clone(bank, src, dst);

6

else:

7

NOP();

8

9

Sender:

10

barrier_1();

11

mask = init(message);

12

row_clone(src, dst, mask);

13

barrier_2();

14

15

Receiver:

16

init_DRAM_rows_with_RowClone();

17

barrier_1();

18

barrier_2();

19

for each DRAM bank do:

20

mask = 1 << bank;

21

timer(start);

22

row_clone(src. dst. mask):

23

timer(end):

24

latency = end - start;

25

if latency > threshold:

result = '1';

26

27

28

result = '0';

```

Listing 2: Pseudocode of PuM-based Covert-Channel Attack.

**Step 3.** The receiver in IMPACT-PuM detects contention in DRAM banks by issuing RowClone operations and measuring their latency. The receiver continuously issues one RowClone operation for each DRAM bank (in contrast to the sender who issues only a single RowClone operation), to the initial virtual

address range (i.e., rows initialized in Step 1) and measures the latency of each operation (2), Line 24). If the sender induces contention to a DRAM bank, the receiver high latency for the RowClone operation which indicates that the corresponding bit in the message is set to 1 (3), Lines 25-26). Otherwise, the receiver detects a fast RowClone operation which indicates that the bit is set to 0 (4), Lines 27-28).

Advantages over PnM-based Covert Channel. IMPACT-PuM improves upon the PnM-based covert-channel attack in a major way. Using a single RowClone operation, the sender can transmit in parallel an N-bit message to the receiver, where N is the number of DRAM banks which requires less computational resources to transmit the same amount of information compared to the PnM-based covert-channel attack. For example, using a single thread, the sender can activate all N DRAM banks and transmit N bits of information in parallel while in the PnM-based covert-channel attack, the sender needs to separately execute a PEI instruction to activate each DRAM bank.

# **4.2. PnM-based Side-Channel Attack on DNA Read Mapping**

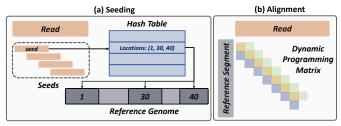

**DNA Read Mapping.** DNA is one of the most unique identifiers of an individual, such that even a small fraction of DNA can include sufficient information for linking to the owner's identity [108]. Therefore, preserving DNA privacy carries importance. DNA sequencing of a biological sample produces short DNA fragments called *reads*. Read mapping is a fundamental operation to find the matching locations of reads in the reference genome that acts as a template genome to construct the complete genome of the sample.

Figure 11 shows a high-level overview of a DNA read mapping (DNA-RM) workflow. DNA-RM has two major key steps: (i) seeding and (ii) alignment. During the seeding step, we identify the possible locations of the reads on the reference genome based on sequence similarities between the reads and the reference genome. Seeding involves hashing small segments of the DNA sequences (i.e., seeds) and probing a hash table that is built from the reference genome. After seeding, we align the reads with their candidate regions on the reference (i.e., potential reference segments) using dynamic programming-based methods to find each read's best matching location among all possible locations in the alignment step.

Figure 11: A simple overview of DNA read mapping workflow: (a) seeding and (b) alignment

DNA-RM requires a large amount of data movement to access different parts of the hash table and then corresponding regions on the reference genome. Hence, several prior works aim to improve the performance of DNA-RM by offloading seed-

ing and alignment to PiM-enabled systems to reduce the data movement overheads [33, 109–115]. In this work, we demonstrate that IMPACT can be used to launch a high-throughput side-channel attack against DNA-RM and quickly leak a large amount of information about the sample genome.

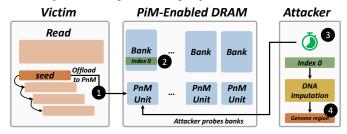

Attack Overview. We assume that the victim is running a DNA-RM application on a PiM-enabled system and the attacker is able to run a malicious application on the same system. The attacker and the victim are using the same read mapping tool (e.g., minimap2 [116]), and the hash table is shared between the attacker and the victim.<sup>3</sup> The attacker's goal is to leak information about the test genome by observing the DNA-RM application's memory access patterns.

Figure 12 shows the high-level overview of the attack. The victim application hashes each seed of the test genome and offloads the corresponding seeding and alignment step to the PiM-enabled system ①. During the seeding step, the corresponding DRAM row gets activated (i.e., Index 0-5 of the hash table) ②. The attacker continuously uses PnM instructions to probe the shared hash table in an attempt to identify if the victim application is accessing a specific index of the hash table ③. If the attacker observes that the victim application is accessing a specific index, it retrieves partial or exact information about the potential locations of the test genome in the reference genome. As shown in previous works on DNA imputation [117,118], the attacker can use the leaked information to infer properties about some regions of the private sample genome ④.

Figure 12: High-level overview of IMPACT attack model on PiMenabled DNA-RM

#### 5. Evaluation

#### 5.1. Methodology

Covert Channel Threat Model. Our threat model for the covert-channel attack envisions a scenario where a sender and a receiver operate on the same PiM-enabled system to exchange information. PiM instructions are available to user space programs without any restrictions and are not privileged instructions. The receiver is assumed to have access to cpuid and rdtscp instructions, enabling high-precision measurement of memory access times. For IMPACT-PnM, the sender and the receiver need to colocate data in the same DRAM banks. For IMPACT-PuM, (i) the sender allocates two virtual address ranges whose corresponding physical pages span across all DRAM banks, and (ii) RowClone guarantees atomicity - when

<sup>&</sup>lt;sup>3</sup>The hash table that contains information about the location of seeds in the reference genome is created once (acts as a database), and each user (attacker and victim in our case) of minimap2 probes it with queries.

the sender issues a RowClone operations that span across multiple banks, all individual bank-level RowClone operations need to be completed before another process accesses DRAM.

Side Channel Threat Model. Our threat model for the side-channel attack envisions a scenario where an attacker process operates on the same PiM-enabled system as a victim process and leaks information about the victim process. We use a DNA-RM implementation based on minimap2 [116] and we modify the implementation to offload the seeding and alignment step to the PiM-enabled system. We assume that the alignment step includes chaining. We use the human genome as the reference and compare it against synthetic sample genomes. We assume that the hash table is distributed across each bank (i.e., DRAM employs a page interleaving mapping). We experiment with multiple different seed sizes, and we report the best-performing selection.

**Proof-of-Concept.** We construct a proof-of-concept of all IM-PACT variants using the Sniper Multicore Simulator [119]. We choose to construct the PoC using Sniper for two reasons. First, it is validated against modern Intel processors [120]. Second, there is no commercially available system that follows a similar architecture as PEI or any modern system that enables end-to-end RowClone operations. We extend Sniper to (i) accurately model all internal DRAM operations, (ii) emulate and simulate the PiM interface and PiM operations, and (iii) emulate the functionality of the cpuid and the rdtscp instructions in order to measure execution cycles from the user space.

Table 2 shows the configuration our simulation setup. Before launching the attack, the sender and the receiver threads warm up by executing both attacks in order to avoid compulsory DRAM accesses for instructions or page table walks (i.e., after an L2 TLB miss, the page table walker might issue requests to DRAM) and reduce the noise of the attack. For IMPACT-PnM, we assume that both the attacker and the receiver use PEIs to perform an addition operation that takes  $\sim 3$  cycles to execute (in addition to the actual DRAM access).

**Comparison Points for Covert-Channel Attacks.** To showcase the effectiveness of IMPACT, we evaluate the leakage throughput of five different covert-channel attacks.

- (i) **DRAMA-clflush:** The main memory covert-channel attack proposed in [70] which uses clflush instructions to send memory requests directly to main memory. clflush only probes the LLC to flush the cache line.

- (ii) **DRAMA-Eviction:** The main memory covert channel attack proposed in [70] which uses cache eviction sets to send memory requests directly to main memory. In both DRAMA attacks, the sender creates contention in the DRAM banks by causing row buffer conflicts and the receiver detects the contention to decode the message.

- (iii) **Streamline:** A state-of-the-art cache covert channel proposed in [121] which enables a flush-less collusion between the sender and the receiver.

- (iv) **DMA Engine:** A main memory attack that uses the DMA engine to bypass the caches and send memory requests directly to main memory. In this scenario, we assume a powerful at-

tacker can infer the DRAM access time directly from the user space by disregarding context switch and OS-related latencies. (v) **PnM-OffChip:** A PnM-based attack that probes the locality monitor and a state-of-the-art off-chip predictor [122] before offloading PEI instructions to compute units near DRAM banks. If the off-chip predictor predicts that data experience high locality, the computation is performed by the CPU instead of the PnM, leading to reduced throughput.

- (iv) **IMPACT-PnM:** Our proposed attack that bypasses the locality monitor and offloads PEI instructions directly to compute units near DRAM banks in order to establish a covert channel between the sender and the receiver.

- (v) **IMPACT-PuM:** Our proposed attack that makes use of RowClone to offload bulk-copy operations directly to main memory and establish a covert channel between the sender and the receiver.

For a fair comparison against DRAMA and Streamline, we showcase the upper bound of the communication throughput achieved by each attack. To evaluate the throughput of the DRAMA and Streamline-based attacks, we use our simulation infrastructure to extract parameters such as the LLC hit latency, average LLC miss latency, cache lookup latency, cache hit/miss ratio, and feed them in an analytical model that calculates the maximum throughput of the attack. We validated the analytical model against the throughput achieved by DRAMA and Streamline in a real system. For example, in Streamline, the authors report a maximum communication throughput of 1.8M Mb/s and our model estimates that the upper bound of the throughput is 2.7 Mb/s for the smallest LLC size.

Noise Sources in Simulation Setup and Error Rate. There are two main microarchitectural structures that generate noise in the simulated system: 1) hardware prefetchers and 2) page table walkers. To observe the impact of application-induced noise on the throughput of IMPACT attacks, we run applications from GraphBIG [123] benchmark suites concurrently with attacker and victim (or sender and receiver) processes. We measure the throughput of each attack by incorporating the error rate in the measurement: we measure the throughput only based on successful leakage.

**Table 2: Simulation Configurations**

| CPU         | 4-core, 4-way, OoO x86 core, 2.6GHz                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MMU         | L1 I-TLB: 128-entry, L1 DTLB (4KB): 64-entry, 4-way assoc, 1-cycle access, L1 DTLB (2MB): 32-entry, 4-way assoc, 1-cycle access, L2 TLB: 1536-entry, 12-way assoc, 12-cycle access, 3 Split PWCs: 32-entry, 2-cycle access |

| L1 Cache    | I-cache: 32 KB; L1D Cache: 32 KB, 8-way assoc, 4-cycle access latency, LRU, IP-stride prefetcher [124]                                                                                                                     |

| L2 Cache    | 1 MB, 16-way assoc, 12-cycle latency, SRRIP [125], Streamer [126]                                                                                                                                                          |

| L3 Cache    | 2 MB/core, 16-way assoc, 32-cycle latency, SRRIP [125]                                                                                                                                                                     |

| Main Memory | DDR4-2400, 16 Banks, 4 Ranks, 1 Channel, Row size = 8192 bytes, $t_{RCD}$ = 13.5 ns, $t_{RP}$ = 13.5 ns , $t_{RC}$ = 13.5 ns, Open Row policy, Row Timeout = 100 ns                                                        |

#### 5.2. Validation of Proof-of-Concept

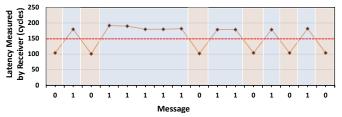

We first demonstrate the PoC results and how we successfully mount the attack in the simulated system. Figures 13 and 14

show the latency (in cycles) measured by the receiver after executing a PiM instruction, one for each of the 16 banks (we assume that the message is 16-bits large), in IMPACT-PnM and IMPACT-PuM, respectively. As we observe, the receiver is able to successfully distinguish whether the sender causes contention in the bank in both IMPACT-PnM and IMPACT-PuM. As shown in the figure, given a latency threshold of 150 cycles, the receiver can decode the complete message: if the latency is less than 150 cycles (i.e., row buffer hit), the receiver decodes the message as a logic-0, otherwise (i.e., row buffer conflict) it decodes the message as a logic-1.

Figure 13: Measured latency (in cycles) by the receiver to execute a PEI instruction for each one of the 16 banks in order to decode a 16-bit message.

Figure 14: Measured latency (in cycles) by the receiver to execute a RowClone instruction for each one of the 16 banks in order to decode a 16-bit message.

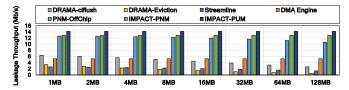

# **5.3.** Throughput Analysis of IMPACT Covert-Channel Attacks

We examine the throughput of all different attacks to understand the potential of IMPACT in establishing a high throughput covert channel between the sender and the receiver. Figure 15 shows the throughput achieved by all different attacks when one sender and one receiver thread run concurrently across systems with increasing LLC sizes. We make four key observations. First, IMPACT-PnM and IMPACT-PuM achieve significantly higher throughput than all other attack vectors. For example, IMPACT-PnM achieves a throughput of 12.87 Mb/s irrespective of the cache size, which is  $2.29 \times$  (up to  $4.91 \times$  with an LLC size of 128MB) higher than the throughput achieved by the secondbest performing attack, DRAMA-clflush. Second, DRAMA and Streamline achieve decreasingly lower throughput as the LLC size increases. This is because the larger the LLC size, the higher the latency it takes to access the LLC. Third, IMPACT-PuM achieves 10% higher throughput than IMPACT-PnM since the sender can issue all RowClone requests in parallel, whereas in IMPACT-PnM the sender has to send the PiM instructions in a sequential manner. Fourth, the DMA engine attack achieves a throughput of 5.27 Mb/s irrespective of the cache size, but is almost 2.4x slower than the PnM-based one due to the OS-related

overheads associated with it (e.g., context switch overhead, OS instructions, etc.). Fifth, the PnM-OffChip attack leads to high throughput, up to 12.64 Mb/s, but the throughput gets reduced down to 10.64 Mb/s as the cache size increases since the off-chip predictor consults more in favor of caching data when the LLC is large, essentially reducing the attack throughput. We conclude that IMPACT-based attacks can achieve significantly higher throughput than the existing state-of-the-art cache covert channels.

Figure 15: Communication throughput comparison across increasing LLC sizes.

Breakdown of Throughput Improvements. The impact of the fundamental difference between PiM architectures and traditional architectures can be seen as the difference between PnM-OffChip and DRAMA-clflush attack throughputs in Fig. 15. The impact of bypassing the locality monitor can be seen as the difference between IMPACT-PnM and PnM-OffChip attack throughputs. Finally, the impact of the parallelism provided by RowClone can be seen as the difference between IMPACT-PuM and IMPACT-PnM attack throughputs.

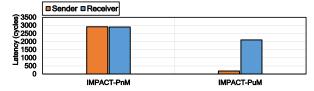

To better understand why IMPACT-PuM achieves higher throughput than IMPACT-PnM, we evaluate the time it takes for the sender and the receiver to perform their respective operations in both attacks. Figure 16 shows the time (in cycles) it takes for the sender to send the message and for the receiver to read the message in IMPACT-PnM and IMPACT-PuM. As we observe, in IMPACT-PuM, the sender can send the message  $14 \times$  faster than the sender in IMPACT-PuM since it can issue all RowClone requests in parallel. In IMPACT-PnM, even though the sender is significantly slower than the sender of IMPACT-PuM, the sender and the receiver overlap, at the cost of synchronization, in order to hide the latency of the sender. This is why IMPACT-PnM achieves only 10% lower throughput than IMPACT-PuM.

Figure 16: Time (in cycles) it takes (i) for the sender to send the message and (ii) for the receiver to read the message in IMPACT-PnM and IMPACT-PuM.

## **5.4. Throughput Analysis of IMPACT Side-Channel** Attack

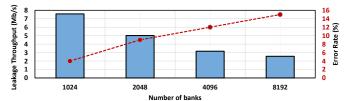

Figure 17 shows the throughput (taking into account only correct identification of activated hash table entries), left y-axis, and the error rate (i.e., wrong identification of activated hash table entries), right y-axis, of the side-channel attack against DNA-RM across different number of DRAM banks. We make

two key observations with respect to the throughput of the attack. First, when using a PiM-enabled DRAM device with 1024 banks, the attacker is able to leak information about the sample genome at a throughput of 7.57 Mb/s. Second, as the number of banks increases, even though the throughput of the attack decreases down to 2.56 Mb/s (since the attacker has to probe more banks and the error rate also increases), the leaked information provides more exact information about the sample genome since the amount of hash table data per bank decreases, reducing the number of potential locations of the reads in the reference genome.

We make two key observations with respect to the error rate of the attack. First, for the 1024 bank configuration, the error rate of the attack is less than 5%. Second, we observe that the error rate of the attack is less than 15% across all different DRAM bank configurations. As the number of banks increases, the error rate of the attack increases since the attacker has to probe more banks, which makes the attack more prone to noise and reduces its bandwidth(i.e., DRAM command delay, memory controller scheduling, etc.).

Even though the error rate of the attack increases as the number of banks increases, the attacker is able to leak information about the test genome with higher accuracy. For example, when using a PiM-enabled DRAM device with 1024 banks, the victim activates a row with 16 hash table entries, and the attacker is able to identify if the sample read is present in any of the locations pointed by the 20 hash table entries with an accuracy of 96%. When using a PiM-enabled DRAM device with 2048 banks, the victim activates a row with 8 hash table entries, and the attacker is able to identify if the sample read is present in any of the locations pointed by the 8 hash table entries with an accuracy of 91%. The exact end-to-end accuracy of identifying the properties of the sample genome depends on the chaining mechanism and the imputation algorithm [117, 118] used by the attacker, and it is out of the scope of this work.

Figure 17: Leakage throughput and error rate of the side-channel attack against DNA-RM across different numbers of DRAM banks.

#### 6. Mitigations for IMPACT

This section discusses the effectiveness of three different techniques to mitigate IMPACT: (i) An address mapping scheme that partitions memory banks across different processes, (ii) a memory controller policy that enforces closing the row buffer after every memory access, and (iii) a memory controller policy that enforces constant-time DRAM accesses to hide the timing differences from the attackers.

Memory Partitioning (MPR). Memory bank partitioning can serve as an effective countermeasure against main-memory-

based covert channel attacks. By dividing the memory into separate banks, each with its own dedicated resources and access control, memory bank partitioning restricts the interactions between different memory regions. This partitioning prevents unauthorized communication channels from crossing the boundaries of the designated banks. In the context of a IMPACT, memory bank partitioning limits the sender's ability to transmit information across different memory banks and the receiver's ability to observe contention in different memory banks. By segregating the memory into distinct banks, the covert channel's ability to exploit timing differences is significantly constrained. However, statically partitioning DRAM resources across applications disables data sharing, which can significantly (i) increase data duplication, (ii) increase memory underutilization, and (iii) lead to frequent swapping from the disk when the memory space is full.

Closed Row Policy (CRP). Enforcing a memory controller policy that closes a DRAM row after each operation can be an effective measure to mitigate and eventually stop timing covert channel attacks. By closing the DRAM row after each operation, the memory controller ensures that subsequent memory accesses, whether legitimate or covert, cannot access the same row without incurring the overhead of row activation. In the context of IMPACT, which heavily relies on the difference in memory access latency to transmit information, closing the DRAM row after each operation disrupts the timing patterns exploited by the attacker. However, as we show in Section 6, enforcing a closed row policy leads to significant performance overheads, even for workloads with low data locality, as every DRAM access will lead to a DRAM row buffer miss.

Constant-Time DRAM Accesses (CTD). One way to mitigate main-memory-based covert channel attacks is to enforce a constant-time DRAM access policy. When a memory access is issued, the memory controller waits for a fixed amount of time before returning the data to the processor. This fixed amount of time is equal to the worst-case DRAM access latency. By enforcing a constant-time DRAM access policy, the memory controller ensures that all memory accesses take the same amount of time, regardless of the accessed memory location. In the context of IMPACT, where the communication relies on the timing or side effects of memory accesses, enforcing a constant-time DRAM access policy obfuscates the timing patterns exploited by the attacker. However, as we show in Section 6, enforcing a constant-time DRAM access policy leads to significant performance overheads as every DRAM access costs the worst-case DRAM access latency.

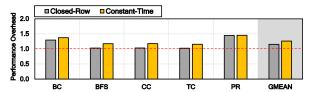

**Performance Evaluation.** To better understand the effectiveness of the countermeasures, we evaluate the performance of CRP and CTD compared to the baseline open-row policy for 5 multi-programmed graph applications which (i) use and share the input graph (i.e., accesses to the same DRAM bank) and (ii) experience a mix of low and high data locality, i.e., the number of last-level cache misses per kilo instructions. We use a 2-core system where each core runs a different instance of the same application (e.g., core 0 runs an instance of PageRank and core

1 the same instance of PageRank using the same input). We evaluate five workloads from GraphBIG benchmark suite [123]: Betweenness Centrality (BC; Data set size: 7.8 GB; LLC MPKI: 0.57), Breadth-First search (BFS; 7.6 GB; 38.59), Connected components (CC; 7.9 GB; 45.2), Triangle counting (TC; 8.2 GB; 5.08), PageRank (PR; 7.0 GB; 1.86).

Figure 18 shows the performance overhead of CRP and CTD compared to the open-row policy for all 5 workloads. We make two key observations. First, CTD leads to the highest performance degration, 26% on average, compared to the open row policy. Especially, in workloads like PR and BC, CTD leads to a performance degradation of 37% and 45% respectively. Second, CRP leads to a performance degradation of 15% on average compared to the open row policy but leads to low performance overheads in workloads that do not benefit from the open row policy like TC, CC and BFS. We conclude that existing countermeasures lead to high performance overheads and there is a dire need to come up with techniques that improve security with low performance overheads.

Figure 18: Performance overhead of Closed-Row policy and Constant-Time policy compared to Open-Row policy.

#### 7. Related Work

To the best of our knowledge, this is the first work that evaluates the implications of PiM on timing attacks.

Security Implications of PiM Systems. A set of prior works [127–129] discuss specific security vulnerabilities in PiM systems. Arafin et al. [127] survey and theoretically analyze security vulnerabilities in PiM systems, with a focus on five specific attack scenarios. In this work, we quantitatively and qualitatively analyze and evaluate main memory-based covert and side channels in detail. Wang et al. [129] extracts neural network architectural information from an RRAM accelerator using power side channels. Similarly, Ensan et al. [128] proposes an attack revealing implemented intellectual property in RRAM-based PiM architectures using power/timing side channels. In contrast, in this work, we demonstrate how to establish high-throughput timing covert channels using PiM operations through software.

**Timing Attacks.** A significant body of work has focused on exploring timing attacks [130, 131]. These attacks involve exploiting variations in the execution time of memory and processor core operations to infer sensitive information. Researchers have investigated various timing attack techniques, such as cache-based attacks [121, 132–139] to uncover vulnerabilities in traditional systems. There is an extensive body of research related to traditional covert-channel attacks, including Flush+Reload [136], where the sender flushes a shared cache line and monitors the access time by the receiver to in-

fer transmitted data. Flush+Flush [135] utilizes cache flush operations to probe for the presence of specific data patterns. Prime+Probe [140] exploits cache set conflicts to communicate information between sender and receiver. Streamline [121] is a flush-less cache covert channel attack that enables asynchronous communication. We compare IMPACT to Streamline in Section 5.3 and show that IMPACT achieves significantly higher throughput.

Other Main Memory-based Timing Attack Mitigations. We already extensively discuss and evaluate mitigations that fundamentally eliminate the timing channel in Section 6. We also discuss practical solutions that restrict access to the timing channel through cache management methods and show that they are not applicable to PiM-based attacks. Another mitigation method is to restrict the usage of fine-grained timers to prevent attackers from exploiting the timing channel. A set of modern processors limits access to fine-grained timers such as Apple M1 cores [141]. Fine-grained timers are used in a wide range of user space applications, such as performance and power consumption monitoring, multithreading, synchronization and locking, optimizations on protocols such as TCP. Restricting access to fine-grained timers can also disable these applications or degrade their effects.

DAGguise [142] is a defense mechanism against memory timing side-channel attacks. DAGguise utilizes a memory access pattern representation obtained through offline profiling and shapes an application's memory access pattern to eliminate information leakage. However, DAGguise does not mitigate row buffer-based timing channels as is and requires the memory controller to employ a closed row policy (evaluated in §6).

Enhancing System Security using PiM. A set of prior works proposes leveraging PIM to enhance the security of modern computing systems. SecNDP [143] proposes an encryption and verification mechanism for untrusted PiM devices that enables computation over encrypted data. SecNDP only focuses on protecting confidentiality and does not consider or analyze potential timing channels in contrast to IMPACT. Nelson et al. [144] propose offloading security critical tasks to near-memory compute units to avoid storing sensitive information in caches and eliminate cache-based side-channel attacks leaking them. In contrast, in this work, we demonstrate and evaluate the implications of PiM on main memory-based timing attacks. InvisiMem. [145] and ObfusMem [146] propose leveraging 3D-stacked memory to design secure processors that provide oblivious RAM equivalent guarantees.

#### 8. Conclusion

The adoption of processing-in-memory (PiM) architectures has gained significant attention due to their ability to provide high performance and low energy consumption by reducing data movement bottlenecks. In this work, we introduce IMPACT, a new high-throughput main memory timing attack that takes advantage of the direct memory access provided by PiM architectures. IMPACT exploits the shared DRAM row buffer to 1) establish covert channels to communicate with other processes at high throughput and 2) leak security-critical information of

victim processes based on their memory accesses. IMPACT covert channels leverage parallelism and eliminate cache bypassing steps, resulting in increased throughput compared to existing main memory-based covert channels. IMPACT side-channel attack targets a genomics application (i.e., DNA read mapping) and leaks the private characteristics of a user's sample genome by leveraging PiM operations. The proposed countermeasures for IMPACT and the discussion on secure and robust PiM architecture designs highlight the need for addressing security concerns in PiM systems.

#### References

- [1] Onur Mutlu. Memory Scaling: A Systems Architecture Perspective. In IMW, 2013.

- [2] Onur Mutlu and Lavanya Subramanian. Research Problems and Opportunities in Memory Systems. SUPERFRI, 2014.

- [3] Jeffrey Dean and Luiz André Barroso. The Tail at Scale. CACM, 2013.

- [4] Svilen Kanev, Juan Pablo Darago, Kim Hazelwood, Parthasarathy Ranganathan, Tipp Moseley, Gu-Yeon Wei, and David Brooks. Profiling a Warehouse-Scale Computer. In ISCA, 2015.

- [5] Michael Ferdman, Almutaz Adileh, Onur Kocberber, Stavros Volos, Mohammad Alisafaee, Djordje Jevdjic, Cansu Kaynak, Adrian Daniel Popescu, Anastasia Ailamaki, and Babak Falsafi. Clearing the Clouds: A Study of Emerging Scale-Out Workloads on Modern Hardware. In ASPLOS, 2012.

- [6] Lei Wang, Jianfeng Zhan, Chunjie Luo, Yuqing Zhu, Qiang Yang, Yongqiang He, Wanling Gao, Zhen Jia, Yingjie Shi, Shujie Zhang, Chen Zheng, Gang Lu, Kent Zhan, Xiaona Li, and Bizhu Qiu. BigDataBench: A Big Data Benchmark Suite from Internet Services. In HPCA, 2014.

- [7] Onur Mutlu, Saugata Ghose, Juan Gómez-Luna, and Rachata Ausavarungnirun. Enabling Practical Processing in and Near Memory for Data-Intensive Computing. In DAC, 2019.

- [8] Onur Mutlu, Saugata Ghose, Juan Gómez-Luna, and Rachata Ausavarungnirun. Processing Data Where It Makes Sense: Enabling In-Memory Computation. MicPro, 2010

- [9] Onur Mutlu. Intelligent Architectures for Intelligent Machines. In VLSI-DAT, 2020.

- [10] Onur Mutlu, Saugata Ghose, Juan Gómez-Luna, and Rachata Ausavarungnirun. A Modern Primer on Processing in Memory. In Emerging Computing: From Devices to Systems — Looking Beyond Moore and Von Neumann. Springer, 2021.

- [11] Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, et al. Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks. In ASPLOS, 2018.

- [12] Shibo Wang and Engin Ipek. Reducing Data Movement Energy via Online Data Clustering and Encoding. In MICRO, 2016.

- [13] Dhinakaran Pandiyan and Carole-Jean Wu. Quantifying the Energy Cost of Data Movement for Emerging Smart Phone Workloads on Mobile Platforms. In IISWC, 2014

- [14] Skanda Koppula, Lois Orosa, A Giray Yağlıkçı, Roknoddin Azizi, Taha Shahroodi, Konstantinos Kanellopoulos, and Onur Mutlu. EDEN: Enabling Energy-Efficient, High-Performance Deep Neural Network Inference Using Approximate DRAM. In MICRO, 2019

- [15] Uksong Kang, Hak-Soo Yu, Churoo Park, Hongzhong Zheng, John Halbert, Kuljit Bains, S Jang, and Joo Sun Choi. Co-Architecting Controllers and DRAM to Enhance DRAM Process Scaling. In *The Memory Forum*, 2014.

- [16] Sally A McKee. Reflections on the Memory Wall. In *CF*, 2004.

- [17] Maurice V Wilkes. The Memory Gap and the Future of High Performance Memories. CAN, 2001.

- [18] Yoongu Kim, Vivek Seshadri, Donghyuk Lee, Jamie Liu, and Onur Mutlu. A Case for Exploiting Subarray-Level Parallelism (SALP) in DRAM. In ISCA, 2012.

- [19] Wm A Wulf and Sally A McKee. Hitting the Memory Wall: Implications of the Obvious. CAN, 1995.

- [20] Junwhan Ahn, Sungpack Hong, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi. A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing. In ISCA, 2015.

- [21] Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W Keckler. Transparent Offloading and Mapping (TOM) Enabling Programmer-Transparent Near-Data Processing in GPU Systems. In ISCA, 2016.

- [22] Yaohua Wang, Lois Orosa, Xiangjun Peng, Yang Guo, Saugata Ghose, Minesh Patel, Jeremie S Kim, Juan Gómez Luna, Mohammad Sadrosadati, Nika Mansouri Ghiasi, et al. FIGARO: Improving System Performance via Fine-Grained In-DRAM Data Relocation and Caching. In MICRO, 2020.

- [23] Svilen Kanev, Juan Pablo Darago, Kim Hazelwood, Parthasarathy Ranganathan, Tipp Moseley, Gu-Yeon Wei, and David Brooks. Profiling a Warehouse-Scale Computer. In ISCA, 2015.

- [24] Indrani Paul, Wei Huang, Manish Arora, and Sudhakar Yalamanchili. Harmonia: Balancing Compute and Memory Power in High-Performance GPUs. In ISCA, 2015.

- [25] Malcolm Ware, Karthick Rajamani, Michael Floyd, Bishop Brock, Juan C Rubio,

- Freeman Rawson, and John B Carter. Architecting for Power Management: The IBM® Power $^{7\text{IM}}$  Approach. In HPCA, 2010.

- [26] Charles Lefurgy, Karthick Rajamani, Freeman Rawson, Wes Felter, Michael Kistler, and Tom W Keller. Energy Management for Commercial Servers. In Computer, 2003

- [27] Thomas Vogelsang. Understanding the Energy Consumption of Dynamic Random Access Memories. In MICRO, 2010.

- [28] Geraldo F Oliveira, Juan Gómez-Luna, Lois Orosa, Saugata Ghose, Nandita Vijayku-mar, Ivan Fernandez, Mohammad Sadrosadati, and Onur Mutlu. DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks. IEEE Access. 2021.