# Low-overhead General-purpose Near-Data Processing in CXL Memory Expanders

Hyungkyu Ham<sup>†\*</sup>, Jeongmin Hong<sup>†\*</sup>, Geonwoo Park<sup>†</sup>, Yunseon Shin<sup>†</sup>, Okkyun Woo<sup>†</sup>, Wonhyuk Yang<sup>‡</sup>, Jinhoon Bae<sup>†</sup>, Eunhyeok Park<sup>†‡</sup>, Hyojin Sung<sup>§</sup>, Euicheol Lim<sup>||</sup>, Gwangsun Kim<sup>†</sup>

†POSTECH

Department of Computer

Science and Engineering

<sup>‡</sup>POSTECH Graduate School of Artificial Intelligence

§Seoul National University Graduate School of Data Science SK hynix

Abstract—Emerging Compute Express Link (CXL) enables cost-efficient memory expansion beyond the local DRAM of processors. While its CXL.mem protocol provides minimal latency overhead through an optimized protocol stack, frequent CXL memory accesses can result in significant slowdowns for memory-bound applications whether they are latency-sensitive or bandwidth-intensive. The near-data processing (NDP) in the CXL controller promises to overcome such limitations of passive CXL memory. However, prior work on NDP in CXL memory proposes application-specific units that are not suitable for practical CXL memory-based systems that should support various applications. On the other hand, existing CPU or GPU cores are not costeffective for NDP because they are not optimized for memorybound applications. In addition, the communication between the host processor and CXL controller for NDP offloading should achieve low latency, but existing CXL.io/PCIe-based mechanisms incur  $\mu$ s-scale latency and are not suitable for fine-grained NDP.

To achieve high-performance NDP end-to-end, we propose a low-overhead general-purpose NDP architecture for CXL memory referred to as *Memory-Mapped NDP* ( $M^2NDP$ ), which comprises *memory-mapped functions* ( $M^2func$ ) and *memory-mapped µthreading* ( $M^2\mu thread$ ).  $M^2func$  is a CXL.mem-compatible low-overhead communication mechanism between the host processor and NDP controller in CXL memory.  $M^2\mu$ thread enables low-cost, general-purpose NDP unit design by introducing lightweight  $\mu threads$  that support highly concurrent execution of kernels with minimal resource wastage. Combining them,  $M^2$ NDP achieves significant speedups for various workloads by up to 128x (14.5x overall) and reduces energy by up to 87.9% (80.3% overall) compared to baseline CPU/GPU hosts with passive CXL memory. The  $M^2$ NDP simulator is publicly available at https://github.com/PSAL-POSTECH/M2NDP-public.

Index Terms—Near-data processing, CXL, Memory expander

# I. INTRODUCTION

The Compute Express Link (CXL) [19] interconnect standard is being widely adopted for communication between processors, accelerators, and memory expanders. In particular, its *memory-semantic* CXL.mem protocol enables low-latency remote memory access with load/store instructions. The latency of CXL.mem is known to be significantly lower than

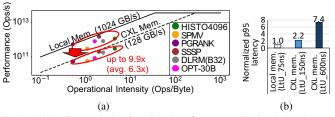

Fig. 1. (a) Roofline analysis of workload performance with data in local memory vs. CXL memory. (b) Impact of Load-to-Use (LtU) latencies of local and CXL memories on the 95th percentile (P95) latency of key-value store (KVS\_A). CXL memory latency can vary depending on the implementation [93], [108], [129]. Evaluation methodology is described in §IV-A.

that of PCIe and is comparable to cross-socket NUMA latency, providing load-to-use latency as low as 150-175 ns [61], [93], [120], [129]. Thus, the host's memory capacity can be cost-effectively increased beyond the local DRAM, benefiting workloads with huge memory footprints, including in-memory online analytic processing (OLAP), key-value store (KVStore), large language model (LLM) [32], recommendation model (e.g., DLRM [104]), and graph analytics [4].

However, the CXL link bandwidth (BW) can become a bottleneck for BW-intensive applications because it is substantially lower than the internal memory BW of CXL memories [58], [122]. As a result, placing the data of applications that require both large memory capacity and high memory BW in CXL memory can substantially degrade performance by up to 9.9× (Fig. 1a). CXL latency can also be significant for latency-sensitive applications that could exploit CXL memory to meet high memory capacity requirements (e.g., key-value stores) (Fig. 1b) [93], [101], [129]. To address these limitations of passive CXL memory, several prior works propose accelerating memory-bound workloads with near-data processing (NDP) in CXL memory [58], [69], [73].

Unfortunately, these prior works propose domain-specific NDP HW logic in CXL memory, limiting their target work-loads. Moreover, adding a wide variety of special-purpose NDP HW for different NDP targets in CXL memory may not be a practical approach due to the high total area and

<sup>\*</sup> These authors contributed equally to this work.

NRE costs [100]. While FPGAs can adapt to target workloads [22], they pose considerable programmability challenges [30]. Meanwhile, for memory-bound workloads with little data reuse, general-purpose NDP can achieve performance similar to specialized logic as long as the memory bandwidth is saturated. However, existing CPU or GPU cores, when used as NDP units [31], [44], [48], [81], [113], [132], [142], do not provide sufficient performance per cost based on our evaluation, because they are not optimized for memory-bound workloads.

Furthermore, conventional ring buffer and MMIO-based NDP offloading using CXL.io/PCIe [58], [69], [73], [122] can incur high latency due to the complexity of the scheme, the CXL.io protocol stack overhead, and costly kernel mode switching on the host, which wastes CPU cycles. While CXL.mem has low latency and can be used within user space, it only supports basic memory reads/writes. Therefore, for latency-sensitive fine-grained NDP, low-overhead offloading mechanism is necessary.

To this end, we propose a novel *Memory-Mapped NDP* ( $M^2NDP$ ) architecture to realize low-overhead, general-purpose NDP in CXL memory.  $M^2NDP$  is based on two key components we propose: *Memory-Mapped function* ( $M^2func$ ) for low-overhead communication between the host and NDP-enabled CXL memory, and *Memory-Mapped µthreading* ( $M^2\mu thread$ ) for efficient NDP kernel execution.

The M<sup>2</sup>func selectively repurposes CXL.mem packets for efficient host-device communication in NDP. By encapsulating NDP management commands (i.e., function calls) in CXL.mem requests to pre-determined addresses, we can avoid the high latency overhead of conventional offloading using CXL.io/PCIe. A key enabler for the M<sup>2</sup>func is a packet filter placed at the input port of the CXL memory. It checks if an incoming request's memory address matches the pre-allocated memory range dedicated for each host process. Then, for matching requests, different NDP management functions are triggered depending on the address. Thus, NDP management function calls (e.g., kernel registration, launch, and status poll) can be done simply by issuing memory accesses from the host. As a result, M<sup>2</sup>func minimizes the latency of NDP offloading, especially benefiting fine-grained NDP. Additionally, we do not require any modification to the CXL.mem standard for best compatibility with host CPUs. Consequently, M<sup>2</sup>func avoids the complexity of managing a ring buffer-based shared task queue between the host and CXL/PCIe-attached devices by providing a clean function call abstraction.

Furthermore, we propose  $M^2\mu$ thread for the intuitive abstraction of NDP and cost-effective kernel execution. Memorybound workloads tend to use fewer registers than compute-bound workloads. Thus, we propose a  $\mu$ thread, which is a lightweight thread with a subset of the architectural registers, as a unit of execution. By reducing register usage, the NDP unit can concurrently execute many  $\mu$ threads with fine-grained multithreading (FGMT) to hide DRAM access latency without excessive physical register file cost.

In addition, memory-bound data-parallel workloads are typ-

ically implemented such that each thread is associated with specific data to be processed. In conventional programming environments such as CUDA, the association between a thread and memory location is expressed indirectly via code (e.g., calculating the index of the array element for a thread using threadblock ID, block dimension, and thread ID in CUDA). In contrast, with our  $M^2\mu$ thread, each  $\mu$ thread is created in direct association with a particular memory location – i.e., the  $\mu$ threads are memory-mapped, thereby reducing the code needed for address calculation. The mapping is done at a smaller granularity (e.g., 32 B) compared to CUDA, which typically maps 128 B of data to a warp, in order to mitigate the impact of intra-warp divergence. Furthermore, to avoid the redundant address calculation in SIMT-only GPUs [57]. scalar instructions are supported. Our NDP unit adopts a modified RISC-V ISA with vector extension (RVV) [9] to leverage SIMD units and fully utilize the DRAM BW within CXL memory cost-effectively. The  $\mu$ threads are spawned individually, unlike thread block spawning in GPUs, which can waste resources due to inter-warp divergence. Our on-chip scratchpad memory with a broader scope than that of GPUs also reduces memory traffic and synchronization.

Overall, our proposed M<sup>2</sup>NDP architecture enables lowoverhead, general-purpose NDP in CXL memory. We show the effectiveness of our design for various workloads, including inmemory OLAP, KVStore, LLM, DLRM, and graph analytics.

To summarize, our contributions include the following:

- We propose M<sup>2</sup>NDP (memory-mapped NDP) to enable general-purpose NDP in CXL memory. Our architecture is based on the unmodified CXL.mem protocol and, thus, does not require any modifications to the host processor hardware. M<sup>2</sup>NDP consists of M<sup>2</sup>func (memory-mapped function) and M<sup>2</sup>μthread (memory-mapped μthreading).

- The M²func supports low-overhead NDP offloading and management from the host processor through CXL.mem, overcoming the high overhead of conventional CXL.io/PCIe-based schemes for fine-grained NDP offloading while retaining standard-compatibility. As a result, it achieves speedups of up to 2.38× (16.8% overall) compared to NDP offloading with conventional approaches.

- The M<sup>2</sup> μthread with lightweight FGMT based on a modified RISC-V with vector extension can cost-efficiently execute NDP kernels. Compared to GPU cores, it reduces waste of on-chip resources and memory bandwidth due to redundant address calculation, inter/intra-warp divergence, and limited on-chip scratchpad memory scope.

- M<sup>2</sup>NDP can achieve high speedups of up to 128× (14.5× overall) for various workloads, compared to the baseline system with passive CXL memory, while reducing energy consumption by up to 87.9% (80.3% overall).

### II. BACKGROUND AND MOTIVATION

# A. Considerations in Architecting NDP in CXL Memory

While passive CXL memory can degrade the performance of latency- and BW-sensitive workloads [129], [144], NDP in

TABLE I High-level comparison of GPU and CXL memory with NDP.

|                       | GPU           | CXL memory with NDP |

|-----------------------|---------------|---------------------|

| Memory capacity       | Low           | High                |

| Cost (area and power) | High          | Low                 |

| FLOPS per memory BW   | High          | Low                 |

| Key target workloads  | Compute-bound | Memory-bound        |

CXL memory presents a substantial opportunity to effectively address this challenge. Although NDP in CXL memory offloads host computation similar to GPUs, they are introduced with very different *primary* objectives (i.e., memory expansion vs. compute acceleration) and, thus, have fundamentally different requirements for memory capacity, cost, and compute throughput (Table I). In particular, CXL memory cannot have 100s of SMs as in high-cost GPUs [36]. The NDP also specifically targets memory-bound workloads with low arithmetic intensity and large memory footprints that do not fit in on-chip caches; other workloads (compute-bound or small working set) can be executed more efficiently on the host or GPUs.

### B. Compute Express Link Interconnect

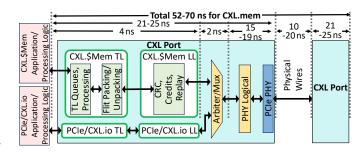

CXL [19] uses PCIe's PHY layer and defines three protocols: CXL.io (equivalent to PCIe) for device management; CXL.cache for cache coherence between the host and device; CXL.mem for memory expansion through CXL. In particular, CXL.mem enables processors to access CXL memory data by simply issuing load/store instructions while providing lower latency compared to CXL.io/PCIe [61], [101], [120]. The loadto-use latency for CXL memory can be as low as  $\sim$ 150 ns, which includes *round-trip* latencies through the host cache, CXL protocol stack, physical off-chip wires, and DRAM [40], [93], [120]. A round-trip latency through the CXL protocol stack and physical wires can be done in  $\sim$ 70 ns (Fig. 2). When a CXL switch is used, the CXL memory access latency can approach 300 ns [93]. In contrast, CXL.io/PCIe takes  $\sim 1 \mu s$ or higher latency for communication (§II-C). The CXL.io is required for all CXL devices for device management.

The host manages the CXL memory, referred to as Host-managed Device Memory (HDM), which can be accessed using a Host Physical Address (HPA). The HDM can use either HDM-H (host-only coherent) or HDM-DB (device coherent using back-invalidation) model. The HDM-H is for passive memory expanders that do not manipulate the memory exposed to the host [19]. In contrast, HDM-DB supports a device coherence agent (DCOH) and a snoop filter in CXL memory to track the host's caching of HDM, so it can back-invalidate (BI) the host cache using BI channels of CXL memory with NDP capability, and we use it for M<sup>2</sup>NDP. The host can also flush HDM data from its cache using HW support [17], [71], [85].

The CXL 3.0 also supports direct peer-to-peer (P2P) access, allowing a CXL device to directly access the HDM of another CXL device through a CXL switch [20]. It can be useful for scalable NDP across multiple CXL memories. However,

Fig. 2. CXL implementation and measured *round-trip* latencies for CXL.mem (figure and numbers adapted from D. D. Sharma [120]). CXL.\$Mem refers to both CXL.cache and CXL.mem (TL: transaction layer, LL: link layer).

accessing host memory from a CXL device is not supported by CXL.mem. To access its own memory, a CXL device can use the Address Translation Services (ATS) [13] defined in PCIe to request a translation by the host, but it can incur a  $\mu$ s-scale latency due to protocol overhead and page table walks on the host [130]. To reduce the overhead, the device can have an Address Translation Cache (ATC) to keep recently used translation information. When necessary, the host can invalidate the device's ATC to prevent incorrect translations.

### C. Communication Overhead with CXL.io/PCIe

Computation offloading with CXL.io/PCIe involves several SW and HW steps with significant overhead in terms of latency and host processor usage, especially for fine-grained offloading. A common method used for GPUs and IO devices is based on a ring buffer shared and manipulated by both the host driver and a PCIe device [47]. For example, to launch a GPU kernel, the host runtime first writes the kernel launch command in the user buffer and the driver pushes a packet that points to the GPU command into the ring buffer in the kernel space. The host then updates the write (or tail) pointer of the ring buffer to notify the GPU of the new command [96], [133], which incurs additional latency through PCIe and triggers two DMA operations from the GPU to fetch the GPU command. Overall, the complex manipulation of the ring buffer shared between the host and GPU can incur two and a half CXL.io round-trips for a kernel launch [47], resulting in high latency of  $\sim 3-6\mu s$  [43], [98] (§III-C). To check kernel completion, polling or interrupt is done, but polling over PCIe can require 2-3 $\mu$ s [70], and interrupt has similar or higher overhead [60], [63], [140]. DMA over PCIe also incurs at least  $\sim 1 \mu s$  latency [61]. Thus, the latencies of kernel launch and completion check can be significant, especially for latencysensitive, fine-grained NDP.

Alternatively, to avoid such overhead, a pair of device-side registers can be directly accessed through MMIO over PCIe to send a request and check the result [45], [58], [122]. However, it cannot support multiple concurrent requests, resulting in limited throughput. In addition, since the memory-mapped registers are physical resources, they cannot be safely shared among multiple user processes and require a context switch to kernel space for every access.

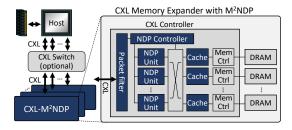

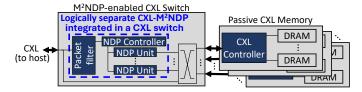

Fig. 3. Overview of the proposed system with M<sup>2</sup>NDP-enabled CXL memory.

### III. MEMORY-MAPPED NEAR-DATA PROCESSING

# A. Overview

To overcome the limited flexibility and cost-efficiency of prior NDP approaches while avoiding the high latency overhead in the offloading procedure (§II-C) for NDP in CXL memory, we propose *Memory-Mapped Near-Data Processing* ( $M^2NDP$ ) in CXL memory, called CXL- $M^2NDP$  (Fig. 3). The  $M^2NDP$  comprises two mechanisms – 1) *Memory-Mapped functions* ( $M^2func$ ) for low-overhead NDP management and offloading based on unmodified standard CXL.mem and 2) *Memory-Mapped µthreading* ( $M^2\mu thread$ ) for cost-effective general-purpose NDP microarchitecture. They are combined to holistically improve end-to-end NDP performance including both offloading procedures and kernel execution. They are implemented in the CXL controller chip which also supports the basic read/write CXL.mem transactions.

### B. Memory-mapped NDP Management Function ( $M^2$ func)

To exploit NDP for fine-grained computation offloading as well as coarse-grained offloading, the communication latency between the host and CXL-M<sup>2</sup>NDP needs to be minimized. While the CXL.mem protocol provides low latency, the standard only defines packet types for normal CXL memory accesses and cannot be directly used for other communication. To extend CXL.mem to support custom packet types, the host processor HW should be modified to support the special usage of the reserved bits. Thus, commodity processors that only support the standard protocol cannot utilize it. Furthermore, to send special packets, special instructions would need to be introduced in the host's ISA as in prior works [67], [81], [111]. Such propriety extension of the standard protocol or host's ISA would hinder widespread adoption. In contrast to CXL.mem, the conventional PCIe/CXL.io-based ring buffer scheme supports arbitrary communication, but incurs higher latency from the protocol stack, ring buffer management, and context switch to the OS for privileged IO device communication (§II-C).

Thus, to enable low-overhead and flexible communication with CXL- $M^2$ NDP from the host using unmodified CXL.mem, we propose  $M^2$ func. The basic idea is to reserve some physical memory space of the CXL memory, referred to as the  $M^2$ func region, for host communication. To distinguish between the two different usages of CXL.mem, we introduce a packet filter placed at CXL memory's input port to examine all packets and determine if the packet should be interpreted as normal reads/writes or  $M^2$ func call based on the packet's

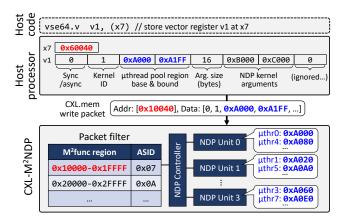

Fig. 4. Example NDP kernel launch using  $M^2$  func with VectorAdd NDP kernel that computes C=A+B. Vectors A, B, and C are placed at 0xA000, 0xB000, and 0xC000, respectively. It is assumed that the virtual address 0x60040 is translated into physical address 0x10040. Each  $\mu$ thread computes a 32B (8x4B) partial vector output. Other datapath components are not shown.

address. M<sup>2</sup>func can be used to provide various functionalities, including NDP kernel registration/unregistration and launch. Different functions can be called by using corresponding offsets from the base of the M<sup>2</sup>func region for the CXL.mem packet (Table II). M<sup>2</sup>func calls are handled by the NDP controller (Fig. 3), which is implemented similarly to the microcontrollers in GPUs [15].

For the initialization of M<sup>2</sup>func, a host's user process can request the M<sup>2</sup>NDP driver to allocate an uncacheable M<sup>2</sup>func region in CXL memory and insert its physical address range into the packet filter using the CXL.io scheme. Once initialized, CXL.io is not needed anymore for NDP and CXL.mem can be used for both normal reads/writes and M<sup>2</sup>func.

The packet filter entry requires little storage of only 18 B per host process (64-bit base, 64-bit bound, and 16-bit ASID), so a small packet filter can support many processes (e.g., 18 KB for 1024 processes) and can also be easily replicated in multiported CXL memory [19].

For an M<sup>2</sup> func call, we use a write request format to include arguments in the write data portion of the request. To send it, the host executes a store instruction with a register that holds the arguments (Fig. 4), which will bypass the host cache as the M<sup>2</sup>func region is uncacheable. Vector registers [9], [21], [124] can be used to send multiple arguments up to the vector register's size. However, the response to the write request cannot include any return value data from the NDP controller using the CXL.mem. Thus, we use a subsequent read request to the same address to access the return value of the latest call of the function by the current process. Because the return value will be accessed with a normal memory access, the NDP controller can simply store the function's return value at the corresponding memory address and serve the read request as normal access. For proper ordering, the host process code should have a fence instruction between the requests.

Table II lists the NDP management functions for different address offsets from the base of an M<sup>2</sup>func region. To support

TABLE II PROPOSED USER-LEVEL LIBRARY API FOR  $M^2NDP$ . ERR IS A NEGATIVE VALUE REPRESENTING AN ERROR.

| API Function         | Arguments                                                                                        | Return Value              | Privileged | Offset |

|----------------------|--------------------------------------------------------------------------------------------------|---------------------------|------------|--------|

| ndpRegisterKernel    | codeLoc, scratchpadMemSize, numIntRegs, numFloatRegs, numVectorRegs                              | ndpKernelID or ERR        | No         | 0      |

| ndpUnregisterKernel  | ndpKernelID                                                                                      | 0 (success) or ERR        | No         | 1 ≪ 5  |

| ndpLaunchKernel      | synchronicity, ndpKernelID, $\mu$ threadPoolRegion (base, bound), kernelArgSize, kernelArguments | kernelInstanceID or ERR   | No         | 2 ≪ 5  |

| ndpPollKernelStatus  | ndpKernelInstanceID                                                                              | 0 (finished), 1 (running) | No         | 3 ≪ 5  |

|                      |                                                                                                  | 2 (pending), or ERR       |            |        |

| ndpShootdownTlbEntry | ASID, virtualPageNumber                                                                          | 0 (success) or ERR        | Yes        | 4 ≪ 5  |

sufficient sizes for function arguments and return values, the offsets can be strided (by  $1 \ll 5$  or 32 B in this example). Thus, multiple arguments and return values can be communicated. For example, to register (unregister) an NDP kernel, assuming the base address is 0x00FF0000, a write request to  $0x00FF0000 (0x00FF0020 \text{ or } 0x00FF0000+(1 \le 5)) \text{ can be used.}$ Since different kernels can require varying amounts of register and scratchpad memory (§III-G), they are given as arguments for registration. In addition, the kernel argument size should be specified so that the arguments can be properly extracted from a kernel launch packet. The metadata of registered kernels are stored in the M<sup>2</sup>func region for the current host process, beginning at a pre-determined location beyond the offsets used in Table II for ease of accesses by the host. As the M<sup>2</sup>func region is allocated by each process, it is protected from other processes by the host.

### C. NDP Kernel Launch

The  $M^2$ func facilitates efficient NDP kernel launch with minimal overhead (Fig. 5a). To launch a kernel, a host process can invoke the  $M^2$ func at offset  $2\ll 5$  (Table II) by issuing a write request with kernel launch arguments. Note the difference between  $M^2$ func arguments for kernel launch function (which determines how a kernel is launched) and NDP *kernel* arguments (which will be directly used in the NDP kernel code). Large kernel inputs (e.g., arrays) can be stored in a separate memory location in CXL memory and their pointer can be passed as an argument. Each kernel instance is associated with a virtual memory region for an input or output data array called  $\mu thread$  pool region provided in a kernel launch call for our  $M^2\mu th$ read mechanism (§III-D). After a kernel launch, the NDP controller sends back an acknowledgment packet immediately.

Afterward, the host can have a memory fence and a load instruction to fetch the return value for the kernel launch function at the same M²func offset 2≪5. The difference is that this time, a read request will be sent. Its response with the return value can be sent back differently based on the Synchronicity argument given for kernel launch: for a synchronous launch, it will return after kernel termination, and for an asynchronous launch, it will return immediately (dotted arrow in Fig. 5a). The asynchronous launch enables overlapping an NDP kernel with subsequent NDP kernels launched from the same host process or other host-side computation. Concurrent kernels can also be launched from multiple host threads, similar to the multi-process service (MPS) of

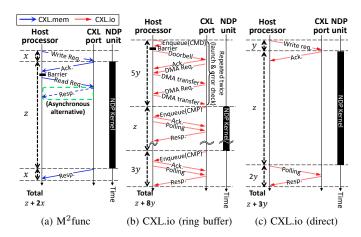

Fig. 5. Example timelines with different NDP offloading schemes. One-way latencies of CXL.mem, CXL.io, and kernel execution are parameterized as x, y, and z, respectively. Their known minimal values are  $x = \sim 75$  ns from 150 ns load-to-use latency for CXL memory [93], [120],  $y = \sim 500$  ns from  $\sim 1~\mu s$  DMA [61]. An example value for z is 6.4  $\mu s$  NDP kernel runtime from DLRM(SLS) –B32 (§IV-C). For M² func, we assume a synchronous launch while also showing the arrow for an alternative asynchronous launch. For the ring buffer, CMD and CMP refer to command and completion messages enqueued into the ring buffers, respectively. Two pairs of CMD and CMP are needed for kernel launch and error checks [24]. While the barrier for M² func overlaps with the kernel, the one needed for ring buffer is in the critical path.

GPUs [106]. The host can then later use the kernel status poll function (i.e., ndpPollKernelStatus) to check its completion.

When the NDP unit's available resource is insufficient due to other kernels running, the kernel launch request will be buffered and served after prior kernels are completed. If the buffer is full, the kernel launch will return an error code.

Comparison with traditional approaches. With the traditional ring buffer scheme used by PCIe/CXL.io devices, an NDP kernel launch can require multiple link round-trips to update the write pointer (i.e., doorbell), and transfer the pointer to the command from the ring buffer and then the command itself to the device similar to GPU kernel launches [96], [133] (Fig. 5b). Subsequently, to check if the launch is done without an error, the procedure should be repeated [24]. This approach incurs high latency but allows concurrent execution of multiple NDP kernels. On the other hand, a simpler approach of directly manipulating dedicated device registers through MMIO [45] takes a shorter latency (Fig. 5c) but can execute only one kernel at a time as the registers should not be overwritten.

In contrast to these approaches, M<sup>2</sup>func reduces the kernel launch latency by exploiting the faster CXL.mem protocol and avoiding kernel mode transition. In addition to the protocol-

level advantage, M<sup>2</sup>func requires fewer round-trips compared to the ring buffer scheme while enabling concurrent execution of multiple kernels. As a result, for the example latencies in Fig. 5, M<sup>2</sup>func reduces the communication overhead and end-to-end runtime by 33-75% and 17-37%, respectively, compared to the traditional schemes.

Note that while we reduce the NDP offloading overhead with CXL.mem, we do not preclude the use of CXL.io/PCIe for NDP management in systems where CXL.mem is not available. For long kernels, CXL.io overhead can be well-amortized over the runtime. The CXL-M<sup>2</sup>NDP can be configured to use either the conventional CXL.io/PCIe mechanism or M<sup>2</sup>func with CXL.mem when the device is initialized by the OS and driver, as using both at the same time is unnecessary.

API for Host-side Programming. For host codes, we propose an API for NDP that exposes high-level functions defined in the first three columns of Table II, similar to the APIs of existing accelerators (e.g., CUDA). Thus, users do not need to understand the low-level implementation with M<sup>2</sup>func – e.g., how an API call's return value is fetched with a subsequent CXL.mem read request or the offset value for each function. Using the ndpPollKernelStatus function, kernel status checks and exception handling can be done using the return value. Note that while this API demonstrates a minimal example, it can be easily extended to include a richer set of API functions.

# D. Memory-mapped $\mu$ threading ( $M^2\mu$ thread)

To maximize the NDP kernel's memory bandwidth utilization, a large number of memory accesses need to be done concurrently to hide memory latency. While out-of-order cores can perform multiple memory accesses simultaneously, it is not suitable for cost-efficient NDP due to high control logic overhead. Fine-grained multithreading (FGMT), especially with a large number of threads as in GPUs, can efficiently provide high concurrency. However, GPU SM's SIMT-only execution can be inefficient when its threads perform redundant computation within a warp due to a lack of scalar operations (e.g., loop variable management, and address calculation) [57].

Thus, to efficiently support both scalar and SIMD operations, we adopt RISC-V ISA with vector extension (RVV) and modify it to support highly concurrent FGMT-based  $M^2\mu$ thread (Table III). Particularly, for CPUs, the OS creates and manages threads, but the overhead can be tremendous for a large number of threads, especially if they are shortlived [138], due to  $\mu$ s-scale thread management delays [11], [92]. In addition, a CPU thread requires the entire ISA-defined register set, so the physical register file can grow linearly with the HW thread count. However, memory-bound workloads tend to use fewer registers than compute-bound workloads due to lower arithmetic intensity. Thus, we use GPU-style HWmanaged threads without the conventional OS for CPUs and provision the number of registers for each thread as specified by SW (i.e., compiler) during kernel registration (Table II) to reduce register file cost. For example, if 5 integer and 3 vector registers are needed, only registers x0-x4 and v0-v2 are used in the kernel. We refer to this type of thread as  $\mu$ thread

TABLE III ARCHITECTURAL DIFFERENCES BETWEEN THE CPU, GPU, AND  $M^2NDP$ .

|                      | CPU            | GPU              | M <sup>2</sup> NDP    |

|----------------------|----------------|------------------|-----------------------|

| Thread creation      | Each thread    | Threadblock      | Each $\mu$ thread     |

| granularity          | (fine-grained) | (corase-grained) | (fine-grained)        |

| Flynn's taxonomy     | SISD + SIMD    | SIMD (SIMT) only | SISD + SIMD           |

| Per-thread registers | Fixed by ISA   | By usage         | By usage              |

| Thread creation      | By OS          | By HW            | By HW                 |

| Thread scheduling    | ST/SMT/        | FGMT             | FGMT                  |

|                      | FGMT/CGMT      |                  | FGMI                  |

| Out-of-order exec.   | Yes or No      | No               | No                    |

| Scratchpad           | N/A            | Threadblock      | All $\mu$ threads run |

| memory scope         | IVA            | Tilleadblock     | on an NDP unit        |

| Thread               | Process ID     | (Threadblock ID, | Mapped μthread        |

| Identification       | 1 locess ID    | thread ID)       | pool address          |

due to its low resource usage. Creating a  $\mu$ thread can be done quickly as in GPUs. To maximize the concurrency of  $\mu$ threads, they execute in a bulk synchronous parallel manner without any ordering guarantee, similar to GPU threads. The  $\mu$ threads can also use on-chip scratchpad memory for communication. Thus, the NDP kernel should be written accordingly. Despite similarities, our  $\mu$ threads differ from GPU threads in several ways besides the ISA differences and provide the following key  $\underline{\mathbf{A}}$ dvantages (A1-A4).

(A1)  $\rm M^2\mu$ thread reduces the overhead of address calculation in an NDP kernel compared to GPUs. Whereas a GPU thread is identified by multidimensional threadblock and thread indices,  $\mu$ threads are identified by the address it is mapped to in a  $\mu$ thread pool region. The address and offset from the base of the pool region are provided in the first two non-zero-valued scalar registers (i.e., x1 and x2) when a  $\mu$ thread is spawned. Then, the offset can also be used to access other data with different bases. By using one of the input data arrays as a  $\mu$ thread pool region (Fig. 4), the  $\mu$ thread can reduce address calculation overhead. As memory-bound NDP kernels tend to have fewer instructions than compute-bound kernels, the static instruction count is reduced by 3.28-17.6% for our evaluated workloads as a result, compared to calculating addresses from multi-dimensional threadblock/thread dimension and indices.

In addition, we avoid the overhead of redundant address calculation in SIMT-only GPUs by using scalar instructions and improve performance by up to 20.2% (§IV-D). Avoiding the redundancy also reduces the register file size requirement and the number of ALUs per NDP unit, resulting in smaller NDP unit area. Combined with the goal of optimizing for memory-bound workloads, our NDP unit uses 81% smaller register file and 69% less area for ALUs (§IV-F). As a result, compared to GPU SMs, more NDP units can be implemented in given area to sustain higher concurrency in memory accesses.

(A2) Second, whereas GPU threads are created in a coarse threadblock granularity,  $\mu$ threads are created in fine, individual thread granularity. The coarse-grained thread creation can result in resource fragmentation and underutilization due to inter-warp divergence – i.e., resource unused by finished warps of a threadblock will remain unused until the entire thread-

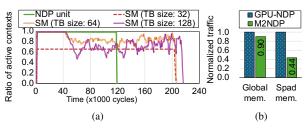

Fig. 6. (a) Ratio of active contexts (i.e., warps for GPU SMs and  $\mu$ threads for  $M^2\mu$ thread) executed on an SM or NDP unit over time for a main kernel of PGRANK [34] with configuration in §IV-A. Maximum threadblock count per SM limits the active warp ratio for the threadblock (TB) size of 32. (b) Reduction of global and scratchpad memory traffic by our NDP unit for HISTO. For GPU-NDP, "Iso-Area" configuration (§IV-A) was used here.

block they belong to is finished and its resource is released for the next threadblock [139]. In contrast, with  $M^2\mu$ thread, resources for a finished  $\mu$ thread are released immediately for the next  $\mu$ thread, improving resource utilization and performance/cost for irregular workloads. For example, Fig. 6a shows that, for PGRANK, NDP unit increases the ratio of active contexts by 50.9-15.9% compared to GPU SM using different threadblock sizes. While using smaller threadblock can improve resource utilization in some cases, it can make it more difficult to effectively use the CUDA shared memory because different threadblocks cannot share data through shared memory. As a result, global memory traffic can be increased. By removing the threadblock hierarchy,  $M^2\mu$ thread also eliminates the need for optimizing the threadblock dimension, which can significantly affect performance [102].

(A3) Moreover, the scope of the on-chip scratchpad memory in NDP unit is larger for μthreads than in CUDA. Whereas CUDA shared memory is not shared across threadblocks even if they are executed on the same SM, all μthreads executed on the same NDP unit can share data through the scratchpad memory. As a result, our NDP unit can significantly reduce traffic for global memory and on-chip scratchpad memory compared to GPUs – e.g., 10% and 56%, respectively (Fig. 6b). Initializing the shared memory in each threadblock also requires additional intra-block synchronization. While NVIDIA's Hopper GPU [23] introduces distributed shared memory that allows different threadblocks in a threadblock cluster to share data in shared memory, it requires that the threadblocks be scheduled in the even coarser cluster granularity and can aggravate SM resource underutilization (Fig. 6a).

(A4) To achieve high utilization of the vector ALUs while avoiding bottleneck, the size of the data associated with a  $\mu$ thread is matched with the memory access granularity of the DRAM (e.g., 64 B for DDR5 and 32 B for LPDDR5). In contrast, GPU tends to process a larger amount of data in a warp (e.g., 128 B per warp with 32 threads processing FP32 data). As a result, for irregular workloads, there can be significant intra-warp divergence, lowering compute resource utilization. As a result, for the (irregular) graph workloads we evaluated, the proportion of active lanes in the SIMD units was  $1.39-2.27\times$  higher in our NDP unit compared to the GPU SM.

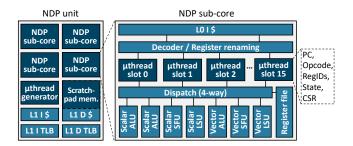

Fig. 7. Proposed NDP unit microarchitecture.

### E. NDP Unit Microarchitecture

The NDP unit is designed at low cost while supporting general-purpose computation (Fig. 7). When an NDP kernel is launched, the NDP controller commands the  $\mu$ thread generator to spawn  $\mu$ threads by allocating  $\mu$ thread slots and register file resources across the sub-cores of the NDP unit. Having multiple sub-cores instead of a monolithic core simplifies the dispatch unit. A  $\mu$ thread slot consist of a PC (program counter), CSR (configure and status register) of RISC-V, opcode and register IDs of the current instruction decoded, and base IDs for INT/FP/vector registers. The base register IDs are assigned when a  $\mu$ thread is created and allocated the required registers. Logical registers are renamed to physical registers simply by adding a logical ID to the base ID.

To load-balance NDP units,  $\mu$ threads are scheduled on NDP units in an interleaved manner with the memory-access granularity. Otherwise, there can be a significant load-imbalance among NDP units for fine-grained NDP kernels (e.g., one NDP unit could have 64 active  $\mu$ threads while the others are idle). After a  $\mu$ thread is allocated a slot, its PC is initialized with the kernel code location to begin execution.

A load/store unit for the scratchpad memory with atomic operations capability [12] is also provided to manipulate shared data in an NDP unit (e.g., for reduction by multiple μthreads). Global memory atomics are done at the memoryside L2 cache to avoid coherence issues (§III-F). Address translation is done using the on-chip TLBs, DRAM-TLB, and ATS (§III-H). The NDP unit can access any memory location in CXL memories in the system through on-chip and off-chip interconnects. The on-chip crossbar provides high BW for all-to-all communication between the NDP units and the memory controllers. On-chip wires and BW are abundant [39], and our crossbar is significantly smaller than that of GPUs [5].

Instructions from a  $\mu$ thread are executed serially while different  $\mu$ threads independently issue instructions with FGMT, avoiding the overhead of complex dependency checks between instructions or data forwarding logic. With sufficient  $\mu$ thread slots (e.g., 64 per NDP unit), the CXL memory bandwidth can be highly utilized. When a  $\mu$ thread is finished, another  $\mu$ thread in the  $\mu$ thread pool is spawned in the idle slot.

# F. Caches Hierarchy

To avoid the complexity of cache coherence, we adopt the cache hierarchy of the GPU [131], using write-through policy

for L1 data cache of NDP units and placing the L2 cache in front of the memory controller (Fig. 3). L1 data cache's capacity is also configurable between normal L1 data cache and scratchpad memory to meet varying requirements of different workloads. The L2 cache supports global memory atomic operations for data from DRAM. The NDP unit employs a small instruction cache because data-parallel, memory-bound workloads have relatively smaller instruction footprint than compute-bound workloads. To prevent access to stale code, the instruction caches are flushed when an NDP kernel is unregistered (§III-B). However, it would be done infrequently and have negligible performance impact.

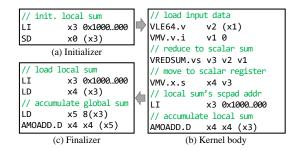

### G. Programming Model for NDP Kernels

To support various use cases, an NDP kernel consists of an initializer, kernel body, and finalizer. The initializer (Fig. 8a) is executed only once when an NDP kernel is launched for initialization of scratchpad memory (if needed) and any required pre-computation before the main computation. For the initializer, one  $\mu$ thread is spawned in each  $\mu$ thread slot with a unique ID in the x2 (or offset) register (§III-E). When they are finished, the  $\mu$ thread generator starts spawning  $\mu$ threads from the  $\mu$ thread pool region to execute the kernel body (Fig. 8b). There can be multiple kernel bodies such that when a kernel body is finished for all  $\mu$ threads, all  $\mu$ threads are generated again for the next kernel body. It can be useful for synchronization of  $\mu$ threads across different phases of a kernel. After all kernel bodies finish, the finalizer (Fig. 8c) is executed, similar to the initializer, but for post-processing and storing the result to DRAM if needed.

When a kernel is launched, the kernel arguments are placed in the on-chip scratchpad memory of each NDP unit to efficiently share them among  $\mu$ threads. The scratchpad memory is mapped to the unused region in the virtual memory layout [51] and can be accessed using normal loads/stores.

$\rm M^2\mu$ thread provides a very flexible execution environment with few restrictions. Depending on the HW support, the compiler can use any instruction in RV64IMAFDV extension or its subset, except for instructions that require operating system (e.g., ECALL). In addition, kernels can access any memory location in HDM, including that of peer CXL.mem devices, either directly or indirectly. Thus, pointer chasing can be done for irregular workloads (e.g., graph analytics). While host-side memory cannot be directly accessed from an NDP kernel using CXL.mem due to the lack of support by the protocol, it is possible to adopt page-fault handling support from GPUs with PCIe and host driver/runtime.

While mapping each  $\mu$ thread to a memory location simplifies the kernel code (§III-D), it is not necessary to strictly adhere to this approach. It is even possible to map  $\mu$ threads to unallocated dummy memory locations as long as they are not actually accessed by loads/stores. In such a case, the offset in the  $\times 2$  register can be used as a thread ID.

To generate kernel code, RISC-V compilers with RVV support [10] can be adapted for M<sup>2</sup>NDP. For basic functionality, the compiler should assume that, for each  $\mu$ thread, the  $\mu$ thread

Fig. 8. NDP kernel example for reduction of a large data. It is assumed that the scratchpad memory is mapped to 0x10000000 and the final result will be stored at the location given in scratchpad memory at 0x10000008. The AMOADD instruction performs an atomic add operation on a memory location.

generator will initialize the x1 and x2 registers with mapped address and offset, respectively (§III-E). It is also possible to adopt high-level programming model for SIMD units in CPUs (e.g., Intel's ISPC [7], [112] and DPC++/SYCL [3] for x86 AVX) for M<sup>2</sup>NDP. Similar to CUDA, ISPC enables the SPMD programming model for vector/SIMD units and has been used in production and state-of-the-art graphics frameworks [6], [89], [135], [145]. Additionally, similar to how cuDNN and cuBLAS from NVIDIA are developed and optimized in assembly [59], [80], hand-tuned M<sup>2</sup>NDP libraries can be developed to achieve high performance for common high-level operations. Unfortunately, since RISC-V has a shorter history, its software ecosystem has not yet matured enough and lacks such open-source compilers and libraries. We leave designing such compilers for future work.

### H. Virtual Memory Support

Our  $M^2NDP$  can efficiently support virtual memory. As the host uses physical addresses for normal CXL.mem requests, address translation is not needed in a passive CXL memory without NDP. However, with NDP, virtual addresses are used for the  $\mu$ thread pool region and load/store instructions. Our NDP unit employs on-chip TLBs, but it may be insufficient for kernels that process large data in CXL memory, and the ATS (§II-B) can also incur high latency. Thus, we adopt DRAM-TLB [72], [115] to cost-effectively improve the TLB reach of NDP units and minimize the miss penalty of on-chip TLBs.

Each DRAM-TLB entry uses 16 bytes to store the ASID, tag, physical page number, and other attributes (e.g., permission bits). The location of a DRAM-TLB entry is computed based on the hash of the virtual page number and ASID as well as base address per CXL memory, ensuring that all NDP units within the same CXL memory can share them.

The DRAM-TLB has low overhead since even with 4 KB pages, the DRAM-TLB entry has only 16 B/4 KB=0.4% overhead, and for 2 MB pages, the overhead is negligible. If the DRAM-TLB region is sufficiently allocated for the given capacity of CXL memory, there will be few DRAM-TLB misses with the hashed location calculation, after DRAM-TLB warms up.

Fig. 9. CXL switch with integrated M<sup>2</sup>NDP logic that can process data from passive CXL memories.

The on-chip and DRAM-TLBs of CXL-M<sup>2</sup>NDP can also keep translations for addresses in other CXL memories if they exist. A TLB shootdown needs to be done for all CXL-M<sup>2</sup>NDPs if a page's mapping changes, but it can rarely occur for in-memory data we assume (i.e., no swapping to disks).

# I. Scaling with Multiple CXL-M<sup>2</sup>NDPs

Using direct P2P accesses between CXL devices through a CXL switch (§II-B), NDP kernels can access data from other CXL-M<sup>2</sup>NDPs to process huge data. However, the CXL interface bandwidth can become a bottleneck for frequent P2P accesses, so localizing data across multiple CXL memories needs to be done carefully. Because different workloads exhibit varying memory access patterns, data partitioning schemes are typically specialized for target workloads [121]. For best performance, current multi-GPU systems also require the userlevel SW to partition the data across GPUs and launch separate kernels. Thus, we similarly assume that the data are placed by SW across CXL memories and an NDP kernel is launched in each CXL-M<sup>2</sup>NDP for multi-device scaling, and leave the exploration of automatic scaling for future work. However, the data localization does not have to be perfect since NDP units can directly access other CXL memories for reads and atomic operations similar to GPUs.

# *J. Scaling CXL Memory Capacity Independently of NDP Units with an M*<sup>2</sup>*NDP-enabled CXL Switch*

Using multiple CXL-M<sup>2</sup>NDPs increases total NDP throughput proportionally with the total CXL memory capacity, which can be desirable in many cases. However, some workloads may have low throughput/capacity ratios and need to increase capacity independently of NDP throughput. For such scenarios, CXL-M<sup>2</sup>NDP can be integrated in a CXL switch to perform NDP with data from different peer, (third-party) passive CXL memories (Fig. 9). For M<sup>2</sup>func region (§III-A), a small SRAM within the switch can be used. To avoid coherence issues with host, it is desirable to use it for workloads that do not need concurrent shared data manipulation between the host and NDP (e.g., serving ML models).

# IV. EVALUATION

### A. Methodology

We faithfully modeled the functional and timing aspects of CXL-M<sup>2</sup>NDP with an in-house cycle-level simulator based on Ramulator [84]. Baseline CPU and GPU with passive CXL

TABLE IV

SIMULATOR CONFIGURATION. WHEN MULTIPLE VALUES ARE GIVEN, THE

DEFAULT IS INDICATED IN BOLDFACE.

|                      | GPU                                                           |  |  |  |

|----------------------|---------------------------------------------------------------|--|--|--|

| Parameter            | Value                                                         |  |  |  |

| SM count and freq.   | 82 SMs @ 1695 MHz                                             |  |  |  |

|                      | Max. 32 threadblocks, Max. 1536 threads, 256 KB reg. file,    |  |  |  |

| SM organization      | 4 SP units, 4 DP units, 4 SFU units, 4 INT units,             |  |  |  |

| Ü                    | 4 INT units, 4 TC (tensor core) units                         |  |  |  |

| L1 D-cache           | 128 KB per SM, 128 B line, 32 B sector @ 1695 MHz             |  |  |  |

| L2 cache             | 6 MB per GPU, 128 B line, 32 B sector @ 1695 MHz              |  |  |  |

| NoC                  | 82x48 crossbar (32B flit)                                     |  |  |  |

| DRAM (HBM2)          | 32 channels, 4 bankgroups/channel,                            |  |  |  |

| organization and     | 4 banks/bankgroup, tRC=48, tRCDR=14, tRCDR=10,                |  |  |  |

| timing param. in clk | tCL=14, tRP=15, tCCDs=1, tCCDl=2, Freq=1000 MHz               |  |  |  |

|                      | CPU                                                           |  |  |  |

| Parameter            | Value                                                         |  |  |  |

| Cores                | 64 OoO cores @ 3.2 GHz                                        |  |  |  |

|                      | 64 KB L1 (8-way, 4-cycle; 64 B line, LRU),                    |  |  |  |

| Caches               | 1 MB L2 (8-way, 12-cycle, 64 B line, LRU),                    |  |  |  |

|                      | 96 MB L3 (16-way, 74-cycle, 64 B line, LRU)                   |  |  |  |

| DRAM (timing         | DDR5-6400 with 409.6 GB/s (8 channels)                        |  |  |  |

| parameters in clk)   | tRC=149, tRCD=46, tCL=46, tRP=46                              |  |  |  |

|                      | CXL Memory Expander                                           |  |  |  |

| Parameter            | Value                                                         |  |  |  |

| CXL                  | 64 GB/s (in each dir.) from CXL 3.0 (PCIe 6.0) x8, 256 B flit |  |  |  |

|                      | Load-to-use latency: 150 ns, 300 ns, 600 ns                   |  |  |  |

| NoC                  | Four 32x32 crossbars (32B flit)                               |  |  |  |

| Memory-side          | 4 MB (128 KB per memory channel,                              |  |  |  |

| L2 cache             | 16-way, 7-cycle, 128 B line, 32 B sector, LRU)                |  |  |  |

| DRAM (timing         | 32-channel LPDDR5 with 409.6 GB/s and 256 GB capacity         |  |  |  |

| parameters in clk)   | elk) per device [109], tRC=48, tRCD=15, tCL=20, tRP=15        |  |  |  |

| NDP in CXL Memory    |                                                               |  |  |  |

| Type                 | Configuration                                                 |  |  |  |

|                      | 32 NDP units @ 2 GHz, 4 SCs per NDP unit,                     |  |  |  |

|                      | 48 KB register file, 512 B L0 I-cache per SC,                 |  |  |  |

| _                    | 2 KB L1 I-cache, 128 KB scratchpad/L1D cache                  |  |  |  |

| $M^2NDP$             |                                                               |  |  |  |

| (SC: sub-core)       |                                                               |  |  |  |

|                      | Scalar units: 2 ALUs, 1 SFU, and 1 LSU per SC,                |  |  |  |

|                      | 256-bit vector units: 1 vALU, 1 vSFU, and 1 vLSU per SC,      |  |  |  |

|                      | 16 $\mu$ thread slots per SC, Max. concurrent kernels: 48     |  |  |  |

|                      | Iso-FLOPS(8SMs), 4×FLOPS(32SMs), 16×FLOPS(128SMs),            |  |  |  |

|                      |                                                               |  |  |  |

memory are modeled using modified ZSim [117] and Accel-Sim [80]; while CPUs are typically used as hosts, for data-parallel GPU workloads, we assume GPU as the host processor because GPUs integrated with CPU cores can function as a host [79]. Table IV gives the simulator configurations. The baseline GPU has similar throughput and memory bandwidth to the NVIDIA GeForce RTX 3090 GPU [18]. In addition, we provide comparisons with high-end CPU [16] and GPU cores [18] used for NDP within CXL memory, referred to as CPU-NDP and GPU-NDP, respectively. They represent prior approaches for general-purpose NDP.

Iso-Area(16.2SMs) @2 GHz.

SM organization: same as the above GPU SM without TC

GPU-NDP

For CPU-NDP evaluation for OLAP workload, we measure the performance on a real dual-socket system with high-end AMD EPYC 75F3 CPUs (2.3 GHz) [16] that has the same total memory bandwidth as the CXL memory that we model (i.e., 409.6 GB/s). The evaluation was done using multiple copies of Apache Arrow processes and memory allocation was done locally to avoid the NUMA effect. We used 32 CPU cores in total (i.e., 16 cores per socket) to match the 32 NDP units we assume for M<sup>2</sup>NDP. Note that M<sup>2</sup>NDP has substantially lower cost than this CPU with OoO pipeline and large caches.

The GPU-NDP (ISO-FLOPS) uses eight Ampere GA102 SMs that provide equivalent peak FLOPS as the 32 NDP units in CXL-M<sup>2</sup>NDP. GPU-NDP (4×FLOPS) and GPU-NDP (16×FLOPS) are also evaluated to show the impact of 4x and 16x higher SM counts (i.e., 32 and 128 SMs). For GPU-NDP (Iso-Area), we estimate the GPU SM's area using the same methodology as NDP unit (§IV-F) to obtain GPU-NDP with 16.2 SMs that has similar area as M<sup>2</sup>NDP. We used 16 SMs and increased the SM's frequency to account for the remaining 0.2 SMs. We also model prior work on GPU-like generalpurpose NDP [81] which requires the host to translate and generate all memory addresses for NDP (NSU). All configurations except for M<sup>2</sup>NDP use CXL.io for kernel launch. The direct MMIO scheme (Fig. 5c), which uses dedicated device registers with a 1.5  $\mu$ s latency overhead, is the default for CXL.io and is indicated with the DR suffix. The RB suffix indicates the ring buffer scheme with a 4  $\mu$ s latency overhead (Fig. 5b). The M<sup>2</sup>NDP configuration uses CXL.mem-based M<sup>2</sup>func for kernel launches with CXL.mem latency according to Table IV. All results include the communication overhead through CXL.io/CXL.mem-based mechanisms. Unless otherwise mentioned, we evaluate performance for running a single instance of each workload at a time, but for throughput measurements with DRLM and KVStore (§IV-B), multiple kernel instances are executed concurrently.

In the CXL memory, we assume fine-grained 256 B-granularity hashed interleaving across memory channels [114]. For multiple CXL memories, we assume each page (2 MB) is mapped to a single CXL memory as in current NUMA or multi-GPU systems [116]. We assume locality-aware page placement by the user for regular workloads in our evaluation. We assume the DRAM-TLB is warmed up for the CXL memory-resident data.

The CPU energy is modeled with McPAT [94] and for GPU and NDP units, we use AccelWattch [76], CACTI 6.5 [2], [103] for SRAM, DSENT [126] for NoC, and 8 pJ/bit CXL link energy [38]. During NDP, the idle host's energy is included.

### B. Workloads

We focus on important workloads, including in-memory OLAP, NoSQL, graph analytics, and deep learning that exhibit large memory footprint and little cache locality (Table V). We assume that the host does not have dirty cachelines for the NDP kernel data by default, but show dirty host cache's impact in §IV-D. Since the compiler for M<sup>2</sup>NDP is not available yet, the kernels were implemented with assembly.

**In-memory OLAP.** Filtering operations are commonly used in OLAP, but executing them from the host processor can cause a bottleneck in the CXL link. Thus, using NDP, we offload the memory-intensive Evaluate phase of the filtering operation, which sweeps column data to check the filtering condition and generates a boolean mask in the CXL memory. For baseline, we use Polars [8], a high-performance columnar in-memory query engine based on Apache Arrow [1]. A subsequent Filter phase (creating a resulting filtered column)

$TABLE\ V \\ Workloads\ used\ for\ evaluation\ (B:\ Baseline)$

| В           | Workload         | Input problem                                                   | Data in CXL mem.                   |

|-------------|------------------|-----------------------------------------------------------------|------------------------------------|

| C<br>P<br>U | OLAP [14], [107] | TPC-H (Q6, Q14),<br>SSB (Q1.1, Q1.2, Q1.3)                      | Arrow columnar format table        |

|             | KVStore [33]     | 24B key, 64B value,<br>10M KV items                             | Hash table with key-value pairs    |

| G           | HISTO [105]      | 16M INT32 elem.,<br>256 or 4096 bins                            | Input array                        |

|             | SPMV [56]        | 28924 nodes, 1036208 edges                                      | Sparse CSR matrix,<br>dense vector |

| P           | PGRANK [34]      | 299067 nodes, 1955352 edges                                     | CSR format graph                   |

| U           | SSSP [34]        | 264346 nodes, 733846 edges                                      | CSR format graph                   |

|             | DLRM [104]       | 1M 256-dim. vectors, 256 req.                                   | Embedding table                    |

|             | OPT [83]         | OPT-30B, OPT-2.7B, Generation phase with context length of 1024 | Model weight,<br>activation        |

and other parts of query execution (e.g., query planning) can be efficiently executed on the host due to small memory footprints. We select queries from TPC-H [14] and SSB (Star Schema Benchmark) [107] that spend non-negligible time on filtering operations. To filter multiple columns, multiple NDP kernels are launched. The address range of the column data is used as the  $\mu$ thread pool region.

KVStore. For large KVStores, the CXL memory can store hash tables and key-value pairs [33], [46], [129]. Serving a KVStore request in such systems can require memory access through the CXL link for hash table lookup, key comparison, and linked list traversal (for hash collisions). Thus, the tail response latency can be increased for the baseline, but NDP can minimize data movement over CXL by offloading hash table lookup, reducing tail latency. We model a simplified Redis and offload GET/SET operations with NDP after compute-intensive hash function on the host. Request traces are obtained using YCSB [37] and have 10K requests for varying GET:SET ratios (G50:S50 for KVS\_A and G95:S5 for KVS\_B).

**Graph analytics.** Large graph analytics require high memory capacity [4] and can exploit CXL memory. As for the  $\mu$ thread pool region, we use the address range of the row pointers from the graph's CSR format. Each NDP kernel corresponds to a kernel in CUDA benchmarks [35], [56], [125].

**DLRM.** Recommendation models can account for over 79% of inference cycles in datacenters [55]. The CXL memory can be used to cost-effectively store their TB-scale embedding tables [137]. However, the CXL link can be a bottleneck when the host accesses the embedding tables for the Sparse Length Sum (SLS) operations, which can account for up to 80% of runtime [104]. Thus, we offload it with NDP, using the output vector of SLS as  $\mu$ thread pool region. We use Criteo Dataset [42] for input with 80 embedding lookup operations per request [77] and use batch sizes of 4, 32, and 128.

**LLM inference.** Generative LLMs require large memory capacity from weight matrices and the key-value cache that grows linearly with the context length during the generation phase [110]. In addition, as GPUs are not efficiently utilized during the long generation phase [75], recent work proposed running this phase separately on GPUs with lower cost [110]. Thus, we evaluate NDP for a token generation with Meta's OPT-2.7B and OPT-30B models [143] assuming a batch size

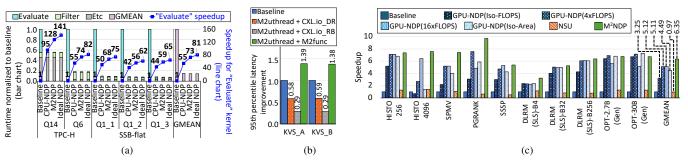

Fig. 10. Speedup of different NDP approaches over the baseline CPU/GPU with passive CXL memory for (a) OLAP, (b) KVStore, and (c) GPU workloads.

of 1 and KV cache of 1024 tokens. For the GPU baseline, we use the highly optimized inference kernels from vLLM [86], and NDP kernels are implemented similarly.

### C. Performance

CPU workloads. Compared to the CPU baseline, for the Evaluate phase of OLAP,  $M^2NDP$  achieved significant speedups of up to  $128\times (73.4\times$  on average) with a high 90.7% CXL memory's internal DRAM BW utilization on average (Fig. 10a).  $M^2NDP$  even approached within 10.3% of the performance of the Ideal NDP that uses 100% of DRAM BW. Our NDP units also outperformed the CPU-NDP with 32 high-end CPU cores with large caches [16] by 34.2% on average. For KVStore, compared to the baseline,  $M^2\mu$ thread with CXL.io-based offloading resulted in significant 1.70-3.46× increase in end-to-end P95 latency due to  $\mu$ s-scale CXL.io latencies, which was significantly longer than  $0.77\mu$ s P95 kernel runtime (Fig. 10b). In contrast,  $M^2$ func effectively improved the end-to-end P95 latency through NDP by 38.2% and  $4.79\times$  on average over baseline and CXL.io(RB), respectively.

GPU workloads. M<sup>2</sup>NDP achieved significant speedups of up to  $9.71 \times (6.35 \times \text{ on average})$  compared to the baseline GPU by avoiding the CXL link BW bottleneck (Fig. 10c). By better utilizing resources and reducing host communication overhead, our 32 NDP units (M<sup>2</sup>NDP) even outperformed 128-SM GPU-NDP (16×FLOPS) by 24%. In addition, M<sup>2</sup>NDP significantly outperformed GPU-NDP (Iso-Area) by up to  $5.48 \times$  and  $1.41 \times$  on average. For hist4096, the limited threadblock-wide scope of GPU's shared memory resulted in high global and shared memory traffic and frequent intra-block synchronization. By addressing them, M<sup>2</sup>NDP outperformed GPU-NDP (Iso-Area) by  $5.48\times$ . The relative performance for graph workloads depended on the characteristics of the graph data/algorithm. While our NDP unit used four separate 256-bit SIMD units, a GPU SM issued instructions in 32-thread warp granularity, which was equivalent to 1024-bit SIMD width for 32-bit data. Thus, for the irregular graph workloads, the SMs suffered more from memory divergence depending on the graph structure. For DLRM with small batch size of 4 that has short kernel runtime, M<sup>2</sup>NDP achieved a 37.8% speedup over GPU-NDP (Iso-Area) by reducing kernel launch overhead. For large-batch DLRM and OPTs, both GPU-NDP (Iso-Area) and M<sup>2</sup>NDP similarly outperformed the baseline by avoiding the

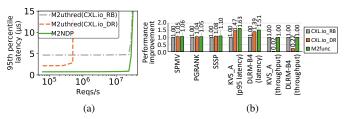

Fig. 11. (a) P95 latency-throughput curves of  $KVS\_A$  with latency assumptions in  $\S IV-A$ . (b) Impact of  $M^2$  func when CXL.io and CXL.mem have the same 600 ns latency.

CXL link BW bottleneck. GPU-NDP (16×FLOPS) did not perform well for them due to reduced DRAM row buffer locality caused by excessive traffic from too many SMs. NSU performed worse than the baseline on average, because the CXL link became the bottleneck due to all addresses translated and sent from the host. In contrast,  $M^2NDP$  did not have such a bottleneck, outperforming NSU by  $6.52\times$ .

**Impact of M**<sup>2</sup>**func.** By using low-overhead M<sup>2</sup>func for host communication, M<sup>2</sup>NDP achieved an additional speedup of up to 2.41× (23.8% overall) for GPU workloads over M<sup>2</sup>μthread with CXL.io(RB). It was particularly effective for fine-grained NDP kernels. In addition, compared to CXL.io(DR) that cannot support concurrent NDP kernels (§III-C), M<sup>2</sup>func improved throughput by 47.3× for KVStore (Fig. 11a). Even if CXL.mem was assumed to have the same latency as CXL.io, M<sup>2</sup>func improved latency by up to 63% (12.1% overall) over CXL.io(RB) by reducing CXL round-trips (Fig. 11b), and increased throughput by 47.3× and 4.58× for KVS\_A and DLRM-B4, respectively, over CXL.io(DR), by supporting concurrent NDP kernels.

### D. Scalability and Sensitivity Study

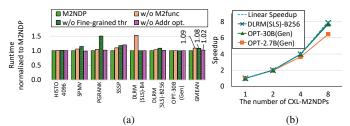

Ablation study. To evaluate the benefit of different components of  $M^2NDP$ , we compare its performance with alternative design choices (Fig. 12a). Disabling  $M^2$ func and using CXL.io(RB) increased runtime by up to 141%. In addition, using coarse-grained  $\mu$ thread scheduling that spawns all 16  $\mu$ threads in a sub-core at a time increased runtime by up to 50.6%. Avoiding the redundant address calculation of SIMT-only GPU by using scalar units had an impact of up to 20.2%. Scalability. To evaluate the scalability of  $M^2NDP$  for OPT and DLRM, we partition the weight matrix or embedding table across different CXL- $M^2NDPs$  using model parallelism [121].

Fig. 12. (a) Ablation study. (b) Scalability of CXL-M<sup>2</sup>NDP.

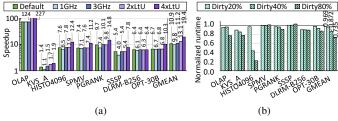

Fig. 13. (a) Speedup over the baselines by CXL- $\rm M^2NDP$  across different NDP unit frequencies and Load-to-Use (LtU) CXL memory latencies (2xLtU=300 ns, 4xLtU=600 ns). (b) Normalized runtime with dirty cacheline ratios over clean host cache. OLAP (Eval) is the average from all queries' Evaluate part. For KVStore (KVS\_A), we show p95 latency improvement.

As shown in Fig. 12b, we achieved near-linear speedups of 7.84× (7.69×) for DLRM (OPT-30B) with eight CXL-M<sup>2</sup>NDPs. OPT-2.7B scaled less well with 6.45× speedup for 8 devices because all-reduce took a longer portion for smaller models. **Sensitivity study.** Reducing the frequency of NDP units from 2 GHz to 1 GHz degraded performance by 10.0% overall (Fig. 13a), but using 3 GHz improved performance by only 2.5% due to the memory BW bottleneck. When load-to-use latency for CXL memory (from the host) was increased by 2-4× (2xLtU and 4xLtU), the speedups by M<sup>2</sup>NDP further increased to 13.1× and 19.4× on average, respectively, because the baseline suffered even more from the longer latency whereas M<sup>2</sup>NDP kernels do not use the CXL link during execution and are unaffected by its latency.

In addition, when the host cache had a significant amount of dirty cachelines for 20-80% of the NDP kernel's data, M²NDP was affected by only by 3.1-26.5% overall (Fig. 13b). Note that these scenarios are very unlikely as the host is not supposed to update the kernel data (e.g., LLM weights and DLRM embedding table during inference), and the kernel data are significantly larger than the host's cache, but we show them as a limit study. The performance impact was not significant, since BI from a  $\mu$ thread overlapped with execution of other  $\mu$ threads, hiding the latency. In addition, when CXL memory BW is saturated, fetching some data from the host through CXL port can provide additional BW for moderate dirty cacheline ratios, countering the BI latency impact.

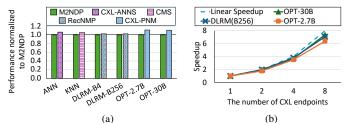

Comparison to domain-specific NDP. Compared to using processing elements (PEs) from prior domain-specific NDP works,  $M^2NDP$ 's performance was within 6.5% of their performance on average (Fig. 14a). For the memory-bound workloads,  $M^2NDP$  was able to nearly saturate the memory BW by  $\sim 81.6\%$  even with the general-purpose design, although

Fig. 14. (a) Performance of domain-specific CXL-NDP using PEs from prior works (CXL-ANNS [74], CMS [122], RecNMP [77], and CXL-PNM [109]). For ANN and KNN (from CMS [122]), we assumed top-K algorithm is executed on the host, overlapping with NDP [74]. We assumed a sufficient number of PEs to saturate the memory BW. (b) Scalability with M<sup>2</sup>NDP-enabled CXL switch with varying number of passive CXL memories.

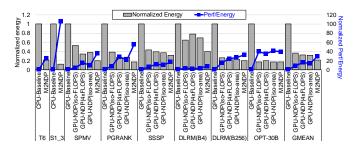

Fig. 15. Energy and performance per energy normalized to baseline CPU and GPU for OLAP and GPU workloads respectively. T6 and S1\_3 denote TPC-H Q6 and SSB Q1.3. GMEAN is calculated for GPU workloads only.

domain-specific PEs sometimes exhibited higher row buffer locality and utilized memory BW slightly better.

**Scalability of M<sup>2</sup>NDP-enabled CXL switch.** Even if M<sup>2</sup>NDP were implemented in a CXL switch (§III-J), the performance scaled well with the number of passive CXL memories, achieving 6.39-7.38× speedups with 8 CXL memories by using multiple CXL ports of the switch (Fig. 14b).

### E. Energy

Compared to the baselines,  $M^2NDP$  significantly improved the performance per energy by up to  $106\times$  and  $32.0\times$  on average (Fig. 15). For OLAP,  $M^2NDP$  substantially reduced energy consumption by up to 87.9% (83.9% on average) compared to the CPU baseline without NDP by reducing data movement over the CXL link and static/constant energy with lower runtime. Similarly, for GPU workloads,  $M^2NDP$  also significantly reduced energy compared to the baseline by 78.2% on average. Compared to the GPU-NDP (Iso-Area), we reduced energy by up to 76.3% (31.4% on average).

# F. Hardware Cost

We estimated the areas of caches and TLBs in the NDP unit using CACTI 6.5 and scaled them to 7 nm with node-scaling factor from [64]. The area of register files (integer, float, and vector) is estimated to be  $0.25~mm^2$ . Each NDP unit has a unified L1 and scratchpad memory of  $0.45~mm^2$ . With each  $\mu$ thread slot occupying  $0.002~mm^2$ , a single NDP unit with compute units from [99] occupies  $0.83~mm^2$ . Thus, the 32 NDP units that we assumed in the evaluation are estimated to incur an area overhead of only  $26.4~mm^2$ .

### V. RELATED WORK

# A. CXL Memory Expander

Several works studied the performance impact of CXL memory on cloud workloads and proposed memory placement schemes [82], [101], [129] as well as memory pooling [52], [93]. DirectCXL [53] also demonstrated the performance benefits of CXL.mem over RDMA. D. D. Sharma [119], [120] analyzed the CXL architecture and its performance.

# B. Near-Data Processing and Processing-In-Memory

**NDP** in memory expanders. Several recent works proposed application-specific NDP in a memory expander or disaggregated memory for genome analysis [69], recommendation model [58], [87], [88], nearest neighbor [73], [122], and DNN parameter server [136]. In contrast, we propose a general-purpose NDP architecture for CXL memory to overcome their limited flexibility.

PIM. Recent DRAM-PIM designs implemented PIM units in DRAM to exploit the high DRAM-internal BW across all banks, targeting DNNs [62], [90], [91] or other dataparallel workloads [41]. They have different trade-offs, including memory bandwidth available, flexibility (e.g., instructions supported), communication between PIM units, and virtual memory support within PIM kernel. However, PIM reduces memory capacity [62] and may not be suitable for workloads with huge memory footprints [4], [14], [32], [137]. PIM can also be combined with NDP in the same CXL memory for computation that cannot be localized in a single DRAM chip. NDP in SSD. Several works explored NDP in SSD using CPU cores [54], [134], [141] or FPGA [95], [123], [128], [134] to exploit the high bandwidth and low latency available internally. However, there are significant gaps between DRAM and flash in terms of BW (e.g., 10 GB/s within SSD vs. 100s GB/s in CXL memory) and latency (10s of  $\mu$ s for flash vs. 10s of ns for DRAM). Still, for workloads with low BW demand (e.g., cold KV stores), NDP in SSD can be useful. Since our NDP units are memory device-agnostic and can saturate DRAM BW while being more cost-effective than CPU or GPU cores, they can be employed in the SSD for efficient general-purpose NDP. If CXL is used for the SSD's interface, our M<sup>2</sup>func can also enable low-overhead kernel offloading. The speedup by NDP in SSD would be largely determined by its internal BW.

Other NDP approaches. Application-specific NDP in HMCs has been proposed for DNNs [50], [66], [97], linked-lists [65], [68], and graph workloads [25]. For programmable NDP, FPGA/CGRA has been proposed [29], [45], [49], [77], [78], [118], but they pose programmability challenges of mapping application algorithms to HW logic. Several works proposed placing simple NDP logic for very fine-grained NDP [26], [67], [81], but they do not effectively support coarse-grained NDP and are not suitable for data-intensive NDP because the large number of offload command packets required can create a link BW bottleneck. Furthermore, they require modifying the memory protocol. These approaches also cannot work independently of the host CPU/GPU and are tightly coupled with the thread on the host – e.g., they require the host to send

input data for each NDP thread. Some prior works introduced CPU or GPU cores in HMCs [44], [97], [113], [142], but our proposed  $M^2\mu$ thread can achieve higher efficiency with lightweight  $\mu$ threads and flexible utilization resources (§III-D and IV-C). Several works explored offloading NDP operations to buffer chips of DIMMs [27], [28], [127], [146]. They are orthogonal to  $M^2$ NDP and can be used in the DIMMs of CXL memory.

### VI. CONCLUSION

In this work, we propose memory-mapped NDP (M<sup>2</sup>NDP) which enables a cost-effective, general-purpose NDP in CXL memory expanders by combining memory-mapped function (M<sup>2</sup>func) and memory-mapped  $\mu$ threading (M<sup>2</sup> $\mu$ thread). M<sup>2</sup>func leverages the unmodified CXL.mem protocol for lightweight communication between the host and CXL device. It facilitates efficient NDP kernel launch and management, avoiding the high overhead of traditional PCIe/CXL.io-based schemes.  $M^2\mu$ thread introduces  $\mu$ thread, a lightweight thread with minimal register allocation, allowing a sufficient number of  $\mu$ threads to be concurrently executed on a low-cost NDP unit. Allocation/deallocation of NDP unit's resources including  $\mu$ thread slots are also done more flexibly compared to GPU SMs, achieving higher resource utilization. Directly mapping  $\mu$ threads to memory and providing scalar units also address the overhead of SIMT-only GPU warps. Compared to the baseline host processor with a passive CXL memory expander, M<sup>2</sup>NDP can achieve significant speedups (up to 128×) while reducing energy (by up to 87.9%) for various applications that require large memory capacity, including in-memory OLAP, KVStore, LLM, DLRM, and graph analytics.

### ACKNOWLEDGMENT

This work supported in part by the MSIT (Ministry of Science and ICT), Korea, under the ITRC (Information Technology Research Center) support program (IITP\_2024-RS-2024-00437866) supervised by the IITP (Institute of Information & communications Technology Planning & evaluation), IITP grants (No. RS-2021-II210871, No. RS-2021-II210310, and No. RS-2019-II191906), and National Research Foundation of Korea (NRF) grants (No. RS-2023-00277080 and No. RS-2024-00415602). This work was also partially supported by SK hynix. We would like to thank the anonymous reviewers for their insightful comments. Gwangsun Kim is the corresponding author.

#### REFERENCES

- [1] "Apache Arrow." [Online]. Available: https://arrow.apache.org/docs/

- [2] "Cacti: An integrated cache and memory access time, cycle time, area, leakage, and dynamic power model." [Online]. Available: https://www.hpl.hp.com/research/cacti/

- [3] Data parallel c++: the oneapi implementation of sycl. Intel Corp. [Online]. Available: https://www.intel.com/content/www/us/en/ developer/tools/oneapi/data-parallel-c-plus-plus.html

- [4] "Graph500 Benchmark specification." [Online]. Available: https://graph500.org/?page\_id=12

- [5] "Inside the nvidia ampere architecture," NVIDIA GTC 2020.[Online]. Available: https://developer.download.nvidia.com/video/gputechconf/gtc/2020/presentations/s21730-inside-the-nvidia-ampere-architecture.pdf

- [6] Intel® embree overview. [Online]. Available: https://github.com/ RenderKit/embree

- Intel® implicit spmd program compiler (intel® ispc). [Online]. Available: https://github.com/ispc/isp

- "Polars: Lightning-fast DataFrame library for Rust and Python." [Online]. Available: https://www.pola.rs/

"RISC-V "V" Vector Extension." [Online]. Available: https://github.

- com/riscv/riscv-v-spec/blob/master/v-spec.adoc

- [10] Risc-v vector intrinsic document. [Online]. Available: https://github. com/riscv-non-isa/rvv-intrinsic-doc

- [11] "Thread management," Threading Programming Guide, Apple. Available: https://developer.apple.com/library/archive/ documentation/Cocoa/Conceptual/Multithreading/CreatingThreads/ CreatingThreads.html

- [12] "Vector amo extension," RISC-V Vector extension specification, May. [Online]. Available: https://github.com/riscv/riscv-v-spec/blob/master/ v-amo.adoc

- [13] "Address translation services revision 1.1." Peripheral Component Interconnect Special Interest Group (PCI-SIG)., 2009. [Online]. Available: https://www.pcisig.com/specifications/iov/ats/