# Compilation for Dynamically Field-Programmable Qubit Arrays with Efficient and Provably Near-Optimal Scheduling

Daniel Bochen Tan University of California, Los Angeles bochentan@ucla.edu Wan-Hsuan Lin University of California, Los Angeles wanhsuanlin@ucla.edu Jason Cong University of California, Los Angeles cong@cs.ucla.edu

Abstract—Dynamically field-programmable qubit arrays based on neutral atoms have high fidelity and highly parallel gates for quantum computing. However, it is challenging for compilers to fully leverage the novel flexibility offered by such hardware while respecting its various constraints. In this study, we break down the compilation for this architecture into three tasks: scheduling, placement, and routing. We formulate these three problems and present efficient solutions to them. Notably, our scheduling based on graph edge coloring is provably near-optimal in terms of two-qubit gate stage count (at most one more than the optimum), the fidelity bottleneck of this platform. As a result, our compiler, Enola, produces higher fidelity results compared to existing works, e.g., 3.7X stage reduction and 5.9X fidelity improvement on the benchmark set used by OLSQ-DPQA, the current state of the art. Additionally, Enola is highly scalable, e.g., within 30 minutes, it can compile circuits with 10,000 qubits, a scale sufficient for the current era of quantum computing. Enola is open source at https://github.com/UCLA-VAST/Enola.

#### I. INTRODUCTION

In recent years, quantum computing based on neutral atoms has advanced quickly in scale, quality, and adoption. The largest experiment so far captured 6,100 qubits [1], greater than other quantum computing platforms. One-qubit gates with 99.97% fidelity and two-qubit gates with 99.5% fidelity have been demonstrated [2], [3] to be competitive among the platforms. As a result, in addition to intensifying academic efforts, multiple startup companies [4], [5], [6], [7], [8] have been established to pursue this route of quantum computing.

A particular advantage of neutral atoms is the ability to move the qubits. Via these movements, the coupling among qubits can be field-programmable dynamically in different stages of the quantum circuit execution. This allows for a lot more flexibility to apply two-qubit entangling gates that are essential to quantum computing. Thus, researchers were able to run some of the most advanced quantum circuits requiring non-local connectivity on the *dynamically field-programmable qubit arrays* (DPQA) architecture [2], [9].

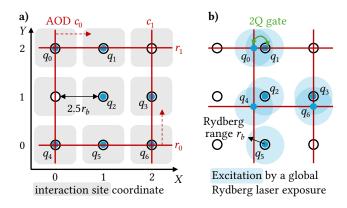

In DPQA, qubits are captured in two kinds of traps. A spatial light modulator (SLM) generates an array of *static* traps, as indicated by the 3-by-3 circles in Fig. 1. Seven of these traps are occupied by qubits. A 2D acousto-optic deflector (AOD) generates *mobile* traps that can travel in the plane. The AOD traps are intersections of a set of rows and columns. In our example, there are two rows ( $r_0$  and  $r_1$ )

Fig. 1. Dynamically field-programmable qubit arrays (DPQA). a) Qubits (blue dots) can transfer between SLM traps (circles) and AOD traps (intersections of red lines). AOD rows and columns can move while preserving their relative order. b) A global Rydberg laser excites all qubits. A two-qubit gate is applied if two qubits are within the Rydberg range.

and two columns ( $c_0$  and  $c_1$ ). When we align the AOD traps with SLM traps and ramp up the AOD intensity, qubits are *transferred* from the SLM to the AOD. In Fig. 1a, three qubits ( $q_0$ ,  $q_4$ , and  $q_6$ ) get transferred to the AOD. Then, the AOD row  $r_0$  shifts upward while the AOD column  $c_0$  shifts to the right, so that the qubits in the AOD move along with them. This movement yields the new configuration shown in Fig. 1b. At this point, if we reverse the movement and wind down the AOD, the three qubits would be transferred back to the SLM. A major constraint of the movements is that the order of AOD columns cannot change, e.g.,  $c_0$  cannot move past  $c_1$  to the right side, nor can the order of rows. An order violation may cause the qubits in the AOD to collide and be lost.

A global Rydberg laser, which *excites all qubits* to potentially entangle with each other, induces the two-qubit operation in DPQA. The range of this interaction is named the *Rydberg range*,  $r_b$ , illustrated by the half-transparent blue spheres in Fig. 1b. If two qubits are within  $r_b$  of each other, a twoqubit gate is applied. In our example, three gates are applied:  $(q_0, q_1), (q_2, q_4),$  and  $(q_3, q_6)$ . We call these parallel gates induced by the Rydberg laser a Rydberg *stage* in the circuit execution. Across the stages, qubits can be rearranged to different *interaction sites* to interact with different qubits.

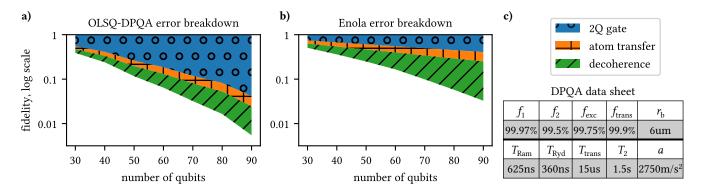

Fig. 2. OLSQ-DPQA and Enola error breakdown. The benchmarks are 3-regular MaxCut QAOA circuits used in Ref. [10]. For the 90-qubit circuits, Elona reduces two-qubit gate stages by 3.7X and improves the overall fidelity by 5.9X.

These sites are represented by the gray regions in Fig. 1a. They center at integer points in the coordinate system and are separated sufficiently by  $2.5r_b$  so that two-qubit interactions can only happen between qubits at the same site. Note that, even if a qubit is alone during a Rydberg stage so that it does not go through a gate, such as  $q_5$  in Fig. 1b, it still gets excited by the Rydberg laser and accumulates error. Therefore, we should minimize the number of stages to reduce these side effect errors.

The compilation for DPQA involves a few tasks: scheduling which assigns two-qubit gates to Rydberg stages, placement which maps the qubits to sites initially, and routing which transfers and moves qubits between stages. The qubit mapping [11], [12], [13], [14], [15], [16], [17], [18] or quantum layout synthesis (QLS) problem [19], [20], [21], [22], [23], [24] ties these tasks together. OLSQ-DPQA [25], [10] is the first work to investigate QLS for DPQA with an effort to find the optimal QLS solution. Subsequent works Q-Pilot [26] and Atomique [27] aim to develop scalable heuristic solutions to support solving large-scale QLS problems for DPQA. However, we find opportunities for improvement both in quality and scalability. Specifically, the formulation of OLSQ-DPQA hinders the exploration of multiple rearrangement steps between Rydberg stages, resulting in more stages than the theoretical lower bound. Through a fidelity estimation detailed later, we find the two-qubit gates (including the side effect errors) to be the dominating error source in their results, as seen in Fig. 2a. In terms of scalability, OLSQ-DPQA can only handle circuits with up to 90 qubits in a day because it depends on solving satisfiability modulo theories (SMT) problems, which are NP-complete.

In this work, we formulate the three tasks in QLS individually and present efficient solutions for them. As a result, our compiler Enola (efficient and near-optimal layout synthesizer for atom arrays) has both higher quality and scalability than OLSQ-DPQA. The quality improvements of Enola are mainly due to the reduction of Rydberg stages, as indicated by the suppression of the two-qubit gate portion in Fig. 2b compared to Fig. 2a. Specifically, we can model two-qubit gates as edges in a graph so assigning gates to stages becomes coloring the edges in the graph. Suppose the optimal number of Rydberg stages is  $S_{opt}$ . Leveraging an efficient and provably near-optimal edge-coloring algorithm [28], Enola manages to schedule the gates to  $S_{opt}$  or  $S_{opt} + 1$  stages. The placement problem is solved by simulated annealing to reduce the qubit traveling distance, and the routing solution is generated by solving independent sets to avoid AOD order violations. For the 90-qubit QAOA 3-regular MaxCut benchmarks [10], Enola produces 3.7X fewer stages and improves the overall fidelity by 5.9X. Furthermore, Enola can handle much larger circuits because it consists of scalable algorithms. We demonstrate compiling circuits with up to 10,000 qubits in 30 minutes, compared to OLSQ-DPQA's 90 qubits in a day.

The paper is organized as follows. Sec. II motivates the paper by analyzing the OLSQ-DPQA results with a detailed fidelity model. The following three sections (III, IV, and V) provide our solutions of scheduling, placement, and routing. Next, Sec. VI presents the evaluations. Then, Sec. VII introduces related works. Finally, we conclude the paper and suggest future directions in Sec. VIII. Additionally, we attach an appendix on the NP-hardness of optimal routing.

# II. MOTIVATION: FIDELITY ANALYSIS

In OLSQ-DPQA, the SMT model only gives a high-level description: the interaction site where each qubit is at for each Rydberg stage. Given this SMT solution, a software module called CodeGen derives the other details like when and where to turn on or off the AOD. These details are enclosed in the generated DPQA code file consisting of a small set of DPQA instructions: initialization, Rydberg laser exposure, turning on/off the AOD, and AOD movements. Ref. [10] mainly reports the number of Rydberg stages, but with the CodeGen infrastructure, we can examine their compiled results with a more careful fidelity model.

We model three error sources: imperfect gates, atom transfers, and qubit decoherence. The parameters follows leading experiments [2], [9] and are summarized in Fig. 2c. Singlequbit gates have the fidelity  $f_1 = 99.97\%$  and the duration  $T_{\text{Ram}} = 625$ ns. These gates can be individually addressed to corresponding qubits [29], so there is no side effect errors on other qubits. In this work, we make the same assumption as Ref. [10] that the single-qubit gates are first removed so that the compiler only handles the two-qubit gates. Then, the single-qubit gates are inserted back to the compiled results. Two-qubit gates have the fidelity  $f_2 = 99.5\%$  and the duration  $T_{\rm Ryd} = 360$ ns. The other qubits also excited by the Rydberg laser, e.g.,  $q_5$  in Fig. 1a, each has the fidelity  $f_{\text{exc}} = 99.75\%$ . Atom transfers have the fidelity  $f_{\text{trans}} = 99.9\%$  and the duration  $T_{\text{trans}} = 15$ us. Note that multiple transfers can be simultaneous, e.g., the three transfers in Fig. 1a will take 15us. The coherence time of qubits is  $T_2 = 1.5$ s. The decoherence effect of a qubit q is modelled by a multiplicative factor  $1 - T_q/T_2$  where  $T_q$  is its idling time, i.e., the total duration of the procedure carried out on DPQA minus any time spent on gates or transfers. The majority of  $T_q$  is spent on AOD movements. The move distance, d, and time, t, follow the relation  $d/t^2 = a = 2750$  m/s<sup>2</sup> [2], e.g., if d = 110 um, then t = 200us.

The overall fidelity is computed by

$$f = (f_1)^{g_1} \cdot \overbrace{(f_2)^{g_2} \cdot (f_{\text{exc}})^{|Q|S-2g_2}}^{\text{two-qubit gate}} \cdot \overbrace{(f_{\text{trans}})^{N_{\text{trans}}}}^{\text{atom transfer}} \cdot \underbrace{\prod_{q \in Q} (1 - T_q/T_2)}_{\text{decoherence}}, \qquad (1)$$

where  $g_1$  and  $g_2$  are the number of single-qubit and two-qubit gates, respectively, Q is the set of qubits, S is the number of stages,  $|Q|S - 2g_2$  calculates the qubits affected by the Rydberg laser but does not perform a gate, and  $N_{\text{trans}}$  is the total number of atom transfers. Since we only focus on twoqubit gates, the term  $(f_1)^{g_1}$  is a constant and we ignore it from now on. As an example, we calculate the fidelity for the process in Fig. 1. There are 3 two-qubit gates so  $(f_2)^{g_2} =$  $0.9950^3 = 0.9851$ . Only  $q_5$  is excited but does not perform a gate so  $(f_{\rm exc})^{|Q|S-2g_2} = f_{\rm exc}^{7\times 1-2\times 3} = 0.9975$ . Thus, the total two-qubit gate term is  $0.9851 \times 0.9975 = 0.9826$ . Since there are 3 atom transfers in Fig. 1a, the atom transfer term is  $(f_{\text{trans}})^{N_{\text{trans}}} = 0.9990^3 = 0.9970$ . The longest movement belongs to  $q_4$ : it travels a  $\sqrt{2}$  site separation, i.e.,  $\sqrt{2} \times 2.5 r_b =$ 21.21um. Thus, the AOD movement from Fig. 1a to Fig. 1b takes  $t = (21.21 \text{um}/2750 \text{m/s}^2)^{0.5} = 87.82 \text{us}$ . This is the  $T_q$ for the moving qubits  $q_0$ ,  $q_4$ , and  $q_5$ . The other 4 qubits are additionally idling during the atom transfer, so their  $T_q =$ 87.82us +  $T_{\text{trans}} = 102.82$ us. Therefore, the *decoherence term* is  $[1 - 87.82/(1.5 \times 10^6)]^3 \times [1 - 102.82/(1.5 \times 10^6)]^4 =$ 0.9996. Finally, the over all fidelity is  $f = 0.9826 \times 0.9970 \times$ 0.9996 = 97.92%.

In Ref. [10], OLSQ-DPQA compiles a set of QAOA circuits designed for the MaxCut problem on 3-regular graphs [30] with the number of qubits ranging from 30 to 90. The specific circuit is the problem unitary in QAOA,  $U_C$ , consisting of 3 commutable two-qubit gates on each qubit. We evaluate the compiled results with our fidelity model and present the breakdown in Fig. 2a. Note that, to draw the figure, we take the logarithm of the fidelity terms so that they are additive. At 90 qubits, the two-qubit gate fidelity term is 0.0414, the atom

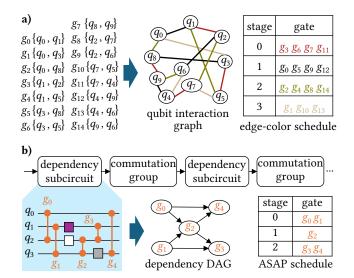

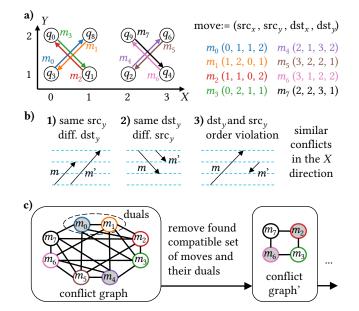

Fig. 3. Scheduling in Enola. a) Scheduling a commutation group of two-qubit gates with edge coloring. b) Generic circuits can be considered as dependency subcircuits and commutation groups. Gates in the former is scheduled ASAP.

transfer term is 0.592, and the decoherence term is 0.223. Thus, the dominating error source are the two-qubit gates, confirming what the authors claim in Ref. [10]. However, there is a gap between the number of stages achieved by OLSQ-DPQA, on average 14.6 for 90 qubits, and the theoretical lower bound, 3, because each qubit is only involved in 3 two-qubit gates. With our compiler, Enola, only 4 stages are produced, pushing the two-qubit fidelity term to 0.406. This effect is evident in the great decrease of the two-qubit gate portion in Fig. 2b compared to Fig. 2a.

#### III. SCHEDULING: EDGE COLORING

The two-qubit gates available on DPQA are controlled rotation in the Z basis, which are known to *commute* [31]. This means a set of these two-qubit gates can be executed in any order. We can solve the scheduling of a *commutation group*, i.e., a set of commutable two-qubit gates, with graph theoretic tools.

For a graph G = (V, E), an *edge coloring* is a function  $\phi : E \to \mathbb{Z}$  that evaluates different values for two different edges incident on a vertex, i.e., for  $e, e' \in E$  and  $e \neq e'$ , if  $e \cap e' \neq \emptyset$ , then  $\phi(e) \neq \phi(e')$ . Misra&Gries [28] provide an algorithm with runtime  $O(|V| \cdot |E|)$  that gives an edge coloring  $\Phi : E \to \{0, 1, ..., \Delta(G)\}$  where  $\Delta(G)$  is the maximum vertex degree of G. Thus,  $\Phi$  colors the edges with at most  $\Delta(G) + 1$  colors. The minimum number of colors to color the edges is called the *chromatic index* of the graph,  $\chi'(G)$ . Since  $\chi'(G) \ge \Delta(G)$ ,  $\Phi$  colors the edges with at most  $\chi'(G) + 1$  colors. Our compiler leverages these results to schedule commutable two-qubit gates. Its advantage is due to the following theorem.

**Theorem 1.** For a group of commutable two-qubit gates on n qubits, suppose the optimal number of Rydberg stages to schedule these gates on DPQA is  $S_{opt}$ , there is an algorithm

with time complexity  $O(n^3)$  that assigns these gates to at most  $S_{opt} + 1$  Rydberg stages.

*Proof.* A commutation group of two-qubit gates can be represented by a *qubit interaction graph* G = (V, E) where the vertices are qubits and the edges are the two-qubit gates (Fig. 3a). The schedule is a function  $\psi : E \to \mathbb{N}$  such that a qubit can only be involved in one gate at a Rydberg stage, i.e., for  $e, e' \in E$  and  $e \neq e'$ , if  $\psi(e) = \psi(e')$ , then  $e \cap e' = \emptyset$ . This is contrapositive to the definition of an edge coloring, so  $\psi$  is an edge coloring. Thus, the optimal number of Rydberg stages is  $S_{\text{opt}} = \chi'(G)$ , which means the function  $\Phi$  derived by the Misra&Gries algorithm maps the two-qubit gates to at most  $S_{\text{opt}} + 1$  Rydberg stages. Since |E| is  $O(n^2)$  where n is the number of qubits, and the Misra&Gries algorithm is  $O(|V| \cdot |E|)$ , the time complexity of our scheduling is  $O(n^3)$ .

A more generic quantum circuit is specified by a sequence of gates. If two gates act on the same qubit, their relative order dictates a *dependency*. In Fig. 3b, we exhibit an example of of how one derives the dependency DAG for the twoqubit gates in a generic circuit. In this case, the scheduling problem is straightforward: the optimal number of stages is the critical path in the DAG and ASAP scheduling can achieve optimality. Although there is a way to augment the DAG to represent partially commutable circuits [32], supporting this in general requires mixing logic synthesis and layout synthesis. Therefore, we make an assumption similar to Ref. [33] that the whole quantum circuit is sliced into subcircuits that either respect all derived dependencies, as 'dependency subcircuits' shown in Fig. 3b, or are commutation groups. The scheduling for the slices can be performed simultaneously and the results can be stitched together afterwards. This sliced structure is prevalent in quantum computing. An example is the graph state preparation with various applications [34], which has a layer of Hadamard gates in the beginning and then commuting CZ gates. Another example is MaxCut QAOA that has alternating driver unitaries  $U_B$  with dependency and problem unitaries  $U_C$  that are commutation groups of ZZ gates.

# IV. PLACEMENT: SIMULATED ANNEALING

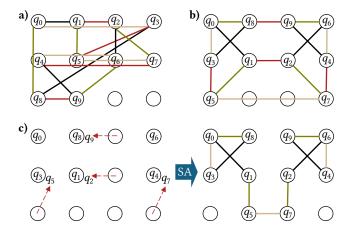

In placement, we map qubits to interaction sites. The twoqubit gates at each Rydberg stage thus correspond to 2-pin nets between the sites. If the nets have a long wire-length, it takes more time to move the qubits, resulting in more decoherence, the second largest error source. As an example, qubits can be placed trivially from left to right and from top to bottom as in Fig. 4a. Then, the total distance of gates in the commutation group in Fig. 3a accumulates to  $25.67 \times 2.5r_b$ . In comparison, an optimized placement displayed in Fig. 4b achieves a total wire-length of  $19.48 \times 2.5r_b$ . To minimize the qubit travelling distances, our cost function is defined as

$$\sum_{g(q,q')\in G} w_g \cdot \operatorname{dist}(m(q), m(q')), \tag{2}$$

where  $w_g$  is the weight for gate g, m is the placement function from qubits to interaction sites, and 'dist' is the Euclidean distance.

Fig. 4. Placement in Enola. a) Trivial placement from left to right, from top to bottom. b) Placement with gate distance optimized by simulated annealing. c) Dynamic placement: after a Rydberg stage (red) is executed (left), run simulated annealing on moved qubits for a new placement (right).

We apply a simulated annealing algorithm, Fast-SA [35], to optimize this cost due to its effectiveness in solving discrete optimization problems. To enhance exploration efficiency, we confine qubits to a specific region, thus reducing the search space. Assuming the number of qubits to place is n, and the interaction sites have column indices  $\{0, 1, ..., x_{max}\}$  and row indices  $\{0, 1, ..., y_{max}\}$ , we define the chip region for exploration as  $x \in [0, \max(\lfloor \sqrt{n} \rfloor + 4, x_{\max})]$  and  $y \in$  $[0, \max(\lfloor \sqrt{n} \rfloor + 4, y_{\max})]$ . In Fig. 4,  $x_{\max} = 3$  and  $y_{\max} = 2$ . Fast-SA has a three-stage annealing schedule to facilitate state space exploration. At the first stage, the temperature is high. In other words, we have higher probability to accept an inferior solution. This stage mimics a random search to explore a large solution space. Then, the second stage performs the pseudogreedy local search with low temperature. The last stage is the hill-climbing search stage where the temperature increases again to escape from local minima. The state in the annealing process is a placement which we initialize randomly. Then, state transitions can be made by either reassigning a qubit to an empty site or exchanging the locations of two qubits. The annealing process will terminate if the temperature is lower than a threshold or the number of iterations exceed a predefined limit, so the placement algorithm has a constant runtime.

The configuration after the first Rydberg stage (red) is on the left of Fig. 4c. The arrows indicate AOD movements from 4b to this configuration. At this point, we can always reverse the movements to return to Fig. 4b, and then find out the movements for the next stage (black). In this case, the placement is static for all the Rydberg stages so we set all the gate weights to 1 in the cost function.

However, one can also consider dynamically changing the placement for the next stage. On the right of Fig. 4c, we display a new placement where the gate between  $q_5$  and  $q_7$  is shorter compared to Fig. 4b. If the placement is dynamic, gates earlier in the schedule should contribute more to the cost function. Thus, we set  $w_g = \max(0.1, 1 - 0.1s_g)$ , where

$s_g$  is the number of stages preceding the stage that the gate g belongs to, e.g., the gates in stages 0 to 3 will have the weights of 1, 0.9, 0.8, and 0.7, respectively. During the simulated annealing for intermediate placement, only the set of qubits necessitating relocation to vacant sites can be moved, while the remaining qubits must stay where they are. In our example, the new placement is restricted, from qubits  $q_2$ ,  $q_5$ ,  $q_7$ , and  $q_9$  to the 6 empty sites. Placement of the other qubits are inherited from the previous placement. In our evaluations detailed later, dynamic placement slightly outperforms static placement. In a commutation group, there are at most O(n) stages, so our placement runtime is O(n), given that each placement spends a constant time.

### V. ROUTING: INDEPENDENT SET

Not all AOD movements from one Rydberg stage to another can be performed simultaneously. The reason lies in the fundamental constraints of AOD: the order of its columns cannot change, nor can the order of rows. We consider the movements of the second stage consisting of gates  $(q_0, q_1)$ ,  $(q_3, q_8), (q_2, q_6), \text{ and } (q_4, q_9), \text{ in Fig. 5a. We define a move}$ to be a 4-tuple: x and y of the source, and x and y of the destination. Since each gate has a choice of which of its two qubits to move, there are two tuples corresponding to each gate. For example,  $m_0 = (0, 1, 1, 2)$  and  $m_1 = (1, 2, 0, 1)$ are both for gate  $(q_0, q_1)$ . We call them to be each other's dual. The AOD constraints are enforced by forbidding conflicts illustrated in Fig. 5b. If the sources of two moves m and m'have the same y, i.e.,  $\operatorname{src}_{y}(m) = \operatorname{src}_{y}(m')$ , the two qubits are picked up by the same AOD row. Then,  $dst_u(m) = dst_u(m')$ because that AOD row can only terminate at one vertical location post-movement. Similarly, if  $dst_u(m) = dst_u(m')$ , then  $\operatorname{src}_{u}(m) = \operatorname{src}_{u}(m')$ . If the qubits are picked up by different rows, their relative order must be maintained, e.g., if  $\operatorname{src}_{u}(m) > \operatorname{src}_{u}(m')$ , then  $\operatorname{dst}_{u}(m) > \operatorname{dst}_{u}(m')$ . In the X direction, there are similar three types of conflicts.

These conflicts are pairwise, which means they can be encoded as edges in a graph where the vertices are the moves. We present this *conflict graph* in Fig. 5c. A set of compatible moves constitutes an independent set (IS) of vertices. One can utilize a maximum independent set (MIS) solver for compatible moves, but MIS is NP-hard.<sup>1</sup> In practice, we find maximal independent sets are sufficient, which can be derived by 1) putting all vertices in a list, 2) adding the first vertex to the IS, 3) removing all its neighbors from the list, and continuing 2-3). In the first box in Fig. 5c, assuming the list of vertices is sorted by indices,  $m_0$  is added to the IS first, so its neighbors  $m_1, m_2, m_3, m_5$ , and  $m_7$  are removed from the list. Next,  $m_4$  is added to the IS and invalidates all the rest of vertices. So the maximal IS is  $\{m_0, m_4\}$  corresponding to gates  $(q_3, q_8)$  and  $(q_2, q_6)$ . Next,  $m_0$  and  $m_4$ , along with their duals  $m_1$  and  $m_5$  are deleted from the conflict graph, resulting

Fig. 5. Routing in Enola. a) Definition of a move as a 4-tuple. b) Conflicts between two moves. c) Compatible moves are independent sets (IS) in the conflict graph (filled vertices). After finding an IS, delete the moves and their duals from the graph. The process continues until no moves are left.

the the second box in Fig. 5c. In the updated graph, we find the second maximal IS,  $\{m_2, m_6\}$ . By now, all moves are deleted and the routing terminates.

The runtime of maximal IS is O(|V| + |E|) where |V|is the number of moves, which is less or equal than the number of qubits, n. To construct the graph, we need to check conflicts for all pairs of vertices, which requires  $O(n^2)$  time. The longest move in each compatible set determines the AOD movement time for this set. Thus, in our compiler, the list of moves is sorted by their distance. This sorting takes  $O(n \log n)$ time. Then, the maximal IS takes  $O(n^2)$  time. In summary, finding a compatible set takes  $O(n^2)$  time. In the worst case, each compatible set includes only one gate. Then, we run O(n)times the procedure above until all gates in one Rydberg stage are handled, resulting in  $O(n^3)$  time. In total, there can be O(n) Rydberg stages for a commutable group, so the total routing time is  $O(n^4)$ . We refer to this routing approach as *sortIS*.

To improve the scaling of sortIS, we can introduce a fixed length window when scanning the list of vertices. Instead of constructing the whole conflict graph, we only construct a graph on the first K vertices in the list where K is the constant window size. These vertices are the K longest moves. Thus, both checking the conflicts between vertices and solving the maximal IS only take  $O(K^2)$  time. Thus, the windowed routing takes  $O(n^2 \log n + n^2 K^2)$  time. We refer to this routing approach as windowIS.

For each compatible set of moves, the qubits need to be picked up by the AOD and dropped off to their destination interaction sites. Turning on the AOD rows and columns and ramping up the intensity for atom transfers also take time. To minimize this time, we need to consider the product structure

<sup>&</sup>lt;sup>1</sup>One can also imagine formulating the routing problem as a vertex coloring to find all compatible sets together, but this involves increasing the size of the graph and solving NP-hard coloring problems. Thus, we do not explore this possibility in this paper.

of AOD, which is a research topic on its own [29]. Actually, we can prove that optimal routing is NP-hard from the complexity of optimizing the AOD pick-up time. In practice, we do not observe this optimality to be critical to the overall fidelity, so we defer these details to the appendix. In Enola, we apply a simple approach implemented by CodeGen in OLSQ-DPQA where the qubits are picked up row by row. The columns may shift horizontally before picking up the next row. The CodeGen just involves scanning over all the qubits to pick up, so the runtime is less than finding the compatible sets.

## VI. EVALUATION

We implemented our proposed algorithm in Python. We employed KaMIS (v2.1) [36] for solving the maximum independent set problems. All experiments were conducted on an AMD EPYC 7V13 64-Core Processor at 2450 MHz and 128 GB of RAM. Each fidelity data point in the figures on QAOA is an average of results corresponding to 10 randomly generated graphs of the same size.

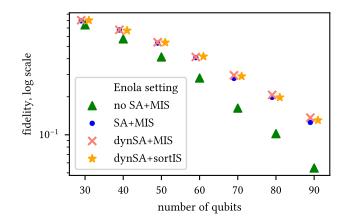

# A. Impact of Different Settings in Enola

Fig. 6 provides the comparison of different settings in Enola on the MaxCut QAOA benchmarks. Since the scheduling is the same for all settings, the two-qubit gate fidelity term is the same. Additionally, in every setting, we use 4 atom transfers for each gate: picking up a qubit and dropping it off to the qubit it interacts with at this Rydberg stage, and the pick-up and drop-off on the way back. This means the atom transfer fidelity term is also the same for all settings. Thus, the comparison is on the decoherence term. A major improvement comes from optimizing placement, as evident by the gap between trivial placement (green triangles) and the other series. Dynamic placement (dynSA+MIS, pink cross) is slightly better than static placement (SA+MIS, blue dot). In routing, sortIS is slightly worse than MIS, as in the comparison of dynSA+sortIS (yellow star) and dynSA+MIS (pink cross). Thus, sortIS proves to be a viable replacement for MIS which is NP-hard. The windowIS method is theoretically worse than sortIS because of the limited window size. We set this size to be 1,000, larger than the scale of benchmarks in Fig. 6. In the evaluations with larger benchmarks up to 10,000 qubits, we observe a similar number of compatible move sets and an average movement distance compared to sortIS, which means windowIS is a good heuristic to speed up the compilation.

### B. Quality Comparison with Previous Works

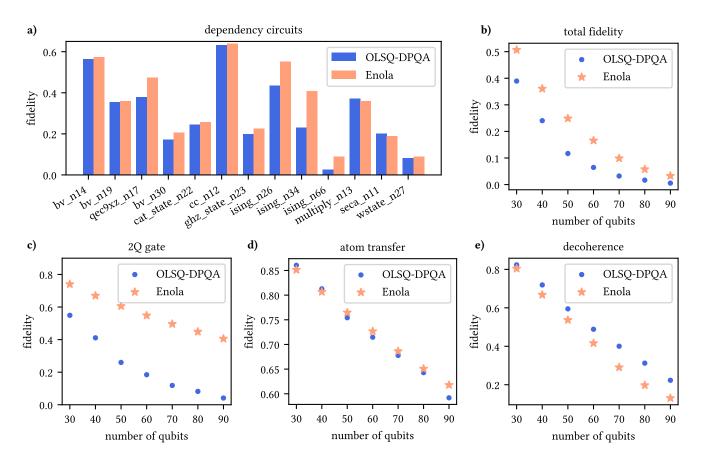

In Fig. 7, we compare Enola with OLSQ-DPQA [10] using the same set of benchmarks in that study. For dependency circuits, OLSQ-DPQA tries to execute as many gates as possible in the current front layer of the DAG, which often results in the same number of Rydberg stages as our ASAP scheduling. In some cases like the three 'ising' benchmarks, OLSQ-DPQA suffers from elongating the critical path because its formulation cannot explore more than one rearrangement steps between Rydberg stages, which results in a notably worse fidelity compared to Enola. In some other cases like

Fig. 6. Decoherence fidelity term of different settings in Enola on 3regular MaxCut QAOA circuits. 'no SA' means trivial placement. 'SA' means static placement. 'dynSA' means dynamic placement. 'MIS' means maximum independent using a solver. For these benchmarks, windowIS is the same with sortIS since the window size (1,000) is larger than the number of vertices in graph where we search for an IS.

'multiply\_n13' and 'seca\_n11', it appears one rearrangement step is sufficient, so the two methods produce the same number of stages. Under this scenario, OLSQ-DPQA can potentially outperform Enola because the routing in Enola is heuristic after all and may not find the optimal compatible sets of moves.

On the QAOA benchmarks, Enola clearly outperforms OLSQ-DPQA because it is able to leverage the near-optimal scheduling. We depict the comparison of overall fidelity in Fig. 7b and the three terms in Fig. 7c-e. In the two-qubit gate term, there is a significant gap between the two approaches. At 90 qubits, OLSQ-DPQA uses 14.6 stages on average whereas Enola only employs 4, a 3.7X reduction. In the atom transfer term, two approaches are similar, but Enola starts gaining advantage on larger benchmarks. It should be noted that in OLSQ-DPQA, atom transfers are not penalized in the SMT formulation. Examining its results with human eyes, there appears to be unnecessary transfers and movements. In Enola, we have explicit control over the transfers and movements. In the decoherence term, Enola is worse than OLSQ-DPQA. This is inevitable because we choose to prioritize the number of Rydberg stages, necessitating more AOD movements. Overall, Enola improves the fidelity by 5.9X compared to OLSQ-DPQA at 90 qubits.

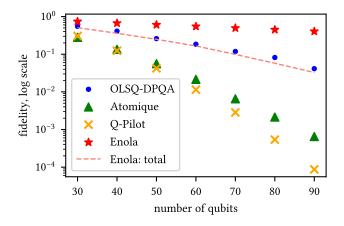

The fidelity gain of Enola is even larger when compared to heuristic methods. Q-Pilot [26] is a DPQA router that utilizes AOD only for ancilla qubits to mediate two-qubit gates between SLM qubits. It does not include a nontrivial placement solution. Atomique [27] focuses on the placement and routes the qubits with SWAP gates. In Fig. 8, we compare the two-qubit gate fidelity terms of all the approaches. Q-Pilot and Atomique result in more Rydberg stages than OLSQ-DPQA and Enola because the generation and recycling of the ancillas and the SWAPs require additional stages. At 90 qubits, Enola reduces the number of stages by 8.7X compared to Atomique and 10.5X compared to Q-Pilot. As a result,

Fig. 7. Comparison of result fidelity between Enola and OLSQ-DPQA. a) Comparison on dependency circuits. b) Comparison of total fidelity on 3-regular MaxCut QAOA circuits. c-e) Comparisons of different fidelity terms on the QAOA circuits.

Fig. 8. Comparison of two-qubit gate fidelity term (scattered points) on 3regular MaxCut QAOA circuits. The total fidelity of Enola is also drawn for reference (dashes).

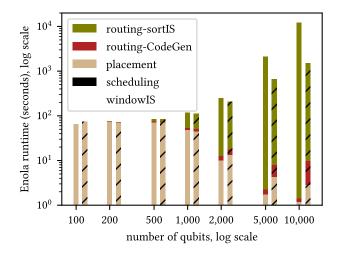

Fig. 9. Enola runtime scaling on 3-regular MaxCut QAOA circuits. Two nearby bars correspond to the same number of qubits. The hatched bars are windowIS data (with a window size of 1,000) and the other bars are sortIS data.

the two-qubit fidelity term of Enola (red star) is 779X higher than Atomique (green triangle) and 5806X higher than Q-Pilot (yellow cross). The total fidelity of Enola (dashes), including atom transfers and decoherence, is still higher than the twoqubit fidelity term of the two heuristics.

#### C. Runtime Scaling of Enola

Since the steps in Enola all have polynomial runtime, it is much more scalable than OLSQ-DPQA. For 3-regular MaxCut QAOA, OLSQ-DPQA can compile 90-qubit benchmarks in one day, whereas Enola compiles 100 qubit circuits with higher fidelity in a minute.

Fig. 9 exhibits the runtime of Enola with sortIS and windowIS on larger benchmarks, up to 10,000 qubits. Note that this is a log-log plot. Different colors inside each bar provides the portion of time spent on different tasks. The scheduling is extremely fast, invisible in the plot. For benchmarks smaller than 1,000 qubits, the runtime is dominated by the placement. Although the placement scales in O(n), the constant factor is large because we would like the simulated annealing to return high-quality results. Later on, the routing portion becomes dominant due to a higher asymptotics: sortIS takes  $O(n^4)$ time and windowIS takes  $O(n^2 \log n)$  time with a constant window size. At 10,000 qubits, the sortIS approach took 1.22e4 seconds, i.e., about 3.4 hours; the windowIS approach took 1.50e3 seconds, i.e., about 25 minutes. From the data, the runtime scaling of windowIS roughly follows  $O(n^2 \log n)$ : increasing the number qubits by 10X from 1,000 to 10,000, the runtime increases by 55X from 18.8 seconds to 1.04e3 seconds.

### VII. RELATED WORK

We have introduced the three existing works that can be directly compared with Enola: OLSQ-DPQA [25], [10], Q-Pilot [26], and Atomique [27]. In this section, we discuss other related works.

A key hardware assumption of ours is that the Rydberg laser globally excites all qubits. An individually addressed Rydberg laser has also been demonstrated, but the two-qubit gate fidelity so far at 92.5% [37] is much lower than the global approach. With individual addressability, the qubits can be routed logically with SWAP gates like quantum computing platforms with a fixed coupling graph such as superconducting circuits. Baker et al. [38] covered the layout synthesis under such a hardware setting. Li et al. [39] further considered the detailed durations for different gates in the scheduling. Patel et al. [40] proposed a method of logic resynthesis to leverage three-qubit gates available on neutral atoms. The SWAPs for routing qubits can sometimes become 'free lunch' after the resynthesis.

Some works also utilizes the movement capabilities on neutral atoms. Brandhofer et al. [41] targeted an architecture with a more restricted kind of movement, '1D displacement'. Nottingham et al. [42] and Schmid et al. [43] proposed to combine the SWAP and AOD movement capabilities for routing qubits. However, these works still rely on individual addressability.

## VIII. CONCLUSION AND FUTURE DIRECTION

In this paper, we formulated three tasks in the compilation for DPQA: scheduling, placement, and routing. We presented efficient solutions to all of them and integrated these solutions in our compiler, Enola. Most notably, because the scheduling is based on the Misra&Gries edge coloring algorithm, Enola generates provably near-optimal number of two-qubit gate stages. Our placement based on simulated annealing and routing based on independent set also proves effective. This paper leads to a few promising directions.

1) Synergy between the three tasks. For example, the edge coloring only assigns two-qubit gates to stages without explicitly ordering these stages. Exploring this ordering resembles placement-driven scheduling [44] and may further decrease the total movement time. Further improvement is also possible via routability-based placement [45] because the current placement only reduces the Euclidean distance of two-qubit gates without considering whether the moves corresponding to these gates are compatible.

2) More detailed formulation of the routing problem. For example, the current notion of compatibility considers the entirety of movements. However, a move may not entirely be compatible with another move but becomes compatible after it progresses past a certain portion. Exploring these opportunities may also require innovation in the lower level instruction set. Separately, the NP-hardness of routing justifies further exploration in solver-based methods. Although these methods cannot solve large-scale problems, it is still valuable to pursue optimal solutions for critical and frequent subroutines or a coarsened solution in a multilevel flow.

3) Application-specific compilation. This work achieves the highest improvement over previous state of the art on commutation groups of two-qubit gates. However, there are commutation relations on higher level structures like Pauli string unitaries in quantum simulation applications [46] that lies out of the scope of this paper. Another example is the decoding circuits for quantum error correction codes [47]. Although they are not commutation groups directly, there is flexibility in the ordering of two-qubit gates.

4) Adaptation to hardware capabilities and co-design. DPQA with separate storage and entanglement zones have been demonstrated [9] where the Rydberg laser only illuminates the entanglement zone. This work is still useful to handle what happens inside the entanglement zone, but a higher level framework of shuttling qubits between the zones should be developed. An efficient and near-optimal compilation such as Enola also aids in the co-design of the hardware, e.g., exploring the impact of more AODs in DPQA.

#### ACKNOWLEDGMENT

This work is funded by NSF grant 442511-CJ-22291. The authors would like to thank Dolev Bluvstein and Harry Hengyun Zhou for valuable discussions.

# APPENDIX: NP-HARDNESS RESULT OF THE DPQA ROUTING PROBLEM

In the DPQA routing problem, we are given a set of pairwise disjoint two-qubit gates and the qubit placement, i.e., a map from qubits to interaction sites. The goal is to generate compatible sets of moves to realize all the two-qubit gates. By our assumption, each move concerns one and only one gate, so the number of atom transfers is fixed regardless the routing strategy. Thus, different routing strategies have the same two-qubit gate fidelity and atom transfer fidelity, but may have different decoherence fidelity due to different time spent. An optimal routing solution should minimize both the time of AOD movements and that of atom transfers. In the main text, we focus on the former. To minimize the atom transfer time, we need to consider which qubits can be picked up in parallel. To discuss this problem, we need to introduce some terminology first.

For a binary matrix  $M \in \mathbb{B}^{m \times n}$ , a combinatorial *rectangle* is the elements  $M_{ij}$  where  $i \in X \subseteq [m]$  and  $j \in Y \subseteq [n]$ , i.e., elements at the intersections of some rows and columns. If all the elements in a rectangle are 1's, we call it a *1-monochromatic rectangle* or a rank-1 submatrix. An example is provided in Fig. 10a where different markers indicate different 1-monochromatic rectangles. The *rectangular partitioning* problem asks for the minimum number of 1-monochromatic rectangles to partition all the 1's in the matrix. This problem being NP-hard is because its decision version is equivalent to the normal set basis problem which is NP-complete [29], [48].

Because of the product structure of the AOD, it can transfer qubits locating at a rectangle of SLM traps, e.g., in Fig. 1a, it aligns with 2-by-2 traps and picks up 3 qubits. If more qubits need to be collected, we can slightly shift the existing AOD rows and columns, and ramp up some other rows and columns which, again, will pick up qubits in a rectangle of SLM traps. For example, in Fig. 10a, 1's like  $M_{00}$  means the qubit is to be collected, whereas 0's like  $M_{13}$  means the qubit should not be collected. The 5 rectangles to partition the matrix incur 5 parallel pick-ups. Since each parallel pick-up takes a constant time  $T_{\text{trans}}$ , we would like to minimize the number of rectangles. Below, we prove that the rectangular partitioning problem is reducible to the DPQA routing problem. The idea is that in the reduced routing problem, there is only one compatible set of moves, so an optimal routing solution collects qubits with a minimum number of parallel pick-ups, i.e., rectangles.

# Theorem 2. The DPQA routing problem is NP-hard.

*Proof.* Given a matrix  $M \in \mathbb{B}^{m \times n}$ , e.g., Fig. 10a, we construct the set of two-qubit gates to route: if and only if  $M_{ij} = 1$ , there is a gate between  $q_{2(ni+j)}$  and  $q_{2(ni+j)+1}$ . The qubit placement is from left to right and from top to bottom. Each row contains 2n qubits as illustrated in Fig. 10b. The black dots are the qubits with even indices whereas the gray dots are the qubits with odd indices. Given this qubit placement, the movements for all the gates can be performed

| <b>a)</b> $M_{00}$ $M_{13}$               | <b>b)</b> $q_1  M$         | $_{ij}$ =1 $\leftrightarrow$ gate or  | $q_{2(ni+j)}$ and | $d q_{2(ni+j)+1}$          |

|-------------------------------------------|----------------------------|---------------------------------------|-------------------|----------------------------|

|                                           |                            | • • • • •                             |                   |                            |

| 0 1 1 0 0                                 |                            | • • • • •                             |                   |                            |

| M = 1 0 0 1 1                             | <b>●</b> <u>1</u> <b>●</b> | $\bullet 0 \bullet \bullet 0 \bullet$ | ●-1▶●             | <b>●</b> <u>1</u> <b>●</b> |

|                                           | ● <u>1</u> >● ●            | • 1• • 0 •                            | • 0 •             | • 0 •                      |

| $\overline{0}$ $\overline{0}$ $1$ $1$ $0$ | $\bullet 0 \bullet$        | • 0 • • <b>1</b> ••                   | ●-1▶●             | • 0 •                      |

Fig. 10. NP-hardness of routing. a) A rectangular partitioning problem. b) A DPQA routing problem reduced from a).

simultaneously by shifting all the black dots at the beginning of all the arrows to the right by one unit. Thus, the optimal routing solution provides the minimum number of parallel pick-ups to collect qubits corresponding to the 1's in M, which is the rectangular partitioning number of M. Thus, we reduce an NP-hard problem, rectangular partitioning, to a DPQA routing problem, which means the DPQA routing problem is NP-hard.

#### REFERENCES

- H. J. Manetsch, G. Nomura, E. Bataille, K. H. Leung, X. Lv, and M. Endres, "A tweezer array with 6100 highly coherent atomic qubits", 2024. [Online]. Available: https://arxiv.org/abs/2403.12021

- [2] D. Bluvstein, H. Levine, G. Semeghini, T. T. Wang, S. Ebadi, M. Kalinowski, A. Keesling, N. Maskara, H. Pichler, M. Greiner, V. Vuletić, and M. D. Lukin, "A quantum processor based on coherent transport of entangled atom arrays," *Nature*, vol. 604, no. 7906, pp. 451–456, 2022, DOI: 10.1038/s41586-022-04592-6.

- [3] S. J. Evered, D. Bluvstein, M. Kalinowski, S. Ebadi, T. Manovitz, H. Zhou, S. H. Li, A. A. Geim, T. T. Wang, N. Maskara, H. Levine, G. Semeghini, M. Greiner, V. Vuletić, and M. D. Lukin, "High-fidelity parallel entangling gates on a neutral-atom quantum computer," *Nature*, vol. 622, no. 7982, p. 268–272, 2023, DOI: 10.1038/s41586-023-06481-

- [4] QuEra. [Online]. Available: https://www.quera.com/

- [5] Infleqtion. [Online]. Available: https://www.infleqtion.com/

- [6] Pasqal. [Online]. Available: https://www.pasqal.com/

- [7] plangc. [Online]. Available: https://www.plangc.eu/

- [8] Atom Computing. [Online]. Available: https://atom-computing.com/

- [9] D. Bluvstein, H. Levine, G. Semeghini, T. T. Wang, S. Ebadi, M. Kalinowski, A. Keesling, N. Maskara, H. Pichler, M. Greiner, V. Vuletić, and M. D. Lukin, "Logical quantum processor based on reconfigurable atom arrays," *Nature*, vol. 626, no. 7997, pp. 58–65, 2024, DOI: 10.1038/s41586-023-06927-3.

- [10] D. B. Tan, D. Bluvstein, D. M. Lukin, and J. Cong, "Compiling quantum circuits for dynamically field-programmable neutral atoms array processors," *Quantum*, vol. 8, p. 1281, 2024, DOI: 10.22331/q-2024-03-14-1281.

- [11] G. Li, Y. Ding, and Y. Xie, "Tackling the qubit mapping problem for NISQ-era quantum devices," in *Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems*, Providence, RI, USA, 2019, pp. 1001–1014, DOI: 10.1145/3297858.3304023.

- [12] C.-Y. Huang, C.-H. Lien, and W.-K. Mak, "Reinforcement learning and DEAR framework for solving the qubit mapping problem," in *Proceedings of the 41st IEEE/ACM International Conference* on Computer-Aided Design, New York, NY, USA, 2022, DOI: 10.1145/3508352.3549472.

- [13] S. Li, K. D. Nguyen, Z. Clare, and Y. Feng, "Single-qubit gates matter for optimising quantum circuit depth in qubit mapping," in *Proceedings* of the 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD), 2023, DOI: 10.1109/ICCAD57390.2023.10323863.

- [14] S. Park, D. Kim, M. Kweon, J.-Y. Sim, and S. Kang, "A fast and scalable qubit-mapping method for noisy intermediate-scale quantum computers," in *Proceedings of the 59th ACM/IEEE Design Automation Conference*, New York, NY, USA, 2022, p. 13–18, DOI: 10.1145/3489517.3530402.

- [15] R. Wille, L. Burgholzer, and A. Zulehner, "Mapping quantum circuits to IBM QX architectures using the minimal number of SWAP and H operations," in *Proceedings of the 56th Annual Design Automation Conference* 2019, Las Vegas, NV, USA, 2019, DOI: 10.1145/3316781.3317859.

- [16] C. Zhang, A. B. Hayes, L. Qiu, Y. Jin, Y. Chen, and E. Z. Zhang, "Time-optimal qubit mapping," in *Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems*, Virtual USA, 2021, pp. 360–374, DOI: 10.1145/3445814.3446706.

- [17] A. Molavi, A. Xu, M. Diges, L. Pick, S. Tannu, and A. Albarghouthi, "Qubit mapping and routing via MaxSAT," in *Proceedings of the 2022* 55th IEEE/ACM International Symposium on Microarchitecture (MI-CRO), 2022, pp. 1078–1091, DOI: 10.1109/MICRO56248.2022.00077.

- [18] B. Tan and J. Cong, "Optimal qubit mapping with simultaneous gate absorption," in *Proceedings of the 40th IEEE/ACM International Conference on Computer-Aided Design*, Munich, Germany, 2021, DOI: 10.1109/ICCAD51958.2021.9643554.

- [19] B. Tan and J. Cong, "Optimality study of existing quantum computing layout synthesis tools," *IEEE Transactions on Computers*, vol. 70, no. 9, pp. 1363–1373, 2021, DOI: 10.1109/TC.2020.3009140.

- [20] B. Tan and J. Cong, "Optimal layout synthesis for quantum computing," in *Proceedings of the 39th IEEE/ACM International Conference on Computer-Aided Design*, Virtual Event, USA, 2020, DOI: 10.1145/3400302.3415620.

- [21] W.-H. Lin, J. Kimko, B. Tan, N. Bjørner, and J. Cong, "Scalable optimal layout synthesis for NISQ quantum processors," in 2023 60th ACM/IEEE Design Automation Conference (DAC), 2023, DOI: 10.1109/DAC56929.2023.10247760.

- [22] T.-A. Wu, Y.-J. Jiang, and S.-Y. Fang, "A robust quantum layout synthesis algorithm with a qubit mapping checker," in *Proceedings of the* 41st IEEE/ACM International Conference on Computer-Aided Design, New York, NY, USA, 2022, DOI: 10.1145/3508352.3549394.

- [23] H. Fan, C. Guo, and W. Luk, "Optimizing quantum circuit placement via machine learning," in *Proceedings of the 59th ACM/IEEE Design Automation Conference*, New York, NY, USA, 2022, p. 19–24, DOI: 10.1145/3489517.3530403.

- [24] I. Shaik and J. van de Pol, "Optimal layout synthesis for quantum circuits as classical planning," in *Proceedings of the 42th IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, San Diego, California, USA, 2023, DOI: 10.1145/3400302.3415620.

- [25] B. Tan, D. Bluvstein, M. D. Lukin, and J. Cong, "Qubit mapping for reconfigurable atom arrays," in *Proceedings of the 41th IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, San Diego, California, 2022, DOI: 10.1145/3508352.3549331.

- [26] H. Wang, B. Tan, P. Liu, Y. Liu, J. Gu, J. Cong, and S. Han, "Q-Pilot: Field programmable quantum array compilation with flying ancillas", 2024. [Online]. Available: https://arxiv.org/abs/2311.16190

- [27] H. Wang, P. Liu, D. B. Tan, Y. Liu, J. Gu, D. Z. Pan, J. Cong, U. A. Acar, and S. Han, "Atomique: A quantum compiler for reconfigurable neutral atom arrays", 2024. [Online]. Available: https://arxiv.org/abs/2311.15123

- [28] J. Misra and D. Gries, "A constructive proof of Vizing's theorem," *Information Processing Letters*, vol. 41, no. 3, pp. 131–133, Mar. 1992, DOI: 10.1016/0020-0190(92)90041-S.

- [29] D. B. Tan, S. Ping, and J. Cong, "Depth-optimal addressing of 2D qubit array with 1D controls based on exact binary matrix factorization", 2024. [Online]. Available: http://arxiv.org/abs/2401.13807

- [30] E. Farhi, J. Goldstone, and S. Gutmann, "A quantum approximate optimization algorithm", Nov. 2014. [Online]. Available: https: //arxiv.org/abs/1411.4028

- [31] H. Levine, A. Keesling, G. Semeghini, A. Omran, T. T. Wang, S. Ebadi, H. Bernien, M. Greiner, V. Vuletić, H. Pichler, and M. D. Lukin, "Parallel implementation of high-fidelity multi-qubit gates with neutral atoms," *Physical Review Letters*, vol. 123, no. 17, p. 170503, 2019, DOI: 10.1103/PhysRevLett.123.170503.

- [32] R. Iten, R. Moyard, T. Metger, D. Sutter, and S. Woerner, "Exact and practical pattern matching for quantum circuit optimization," ACM *Transactions on Quantum Computing*, vol. 3, no. 1, 2022, DOI: 10.1145/3498325.

- [33] Y. Shi, N. Leung, P. Gokhale, Z. Rossi, D. I. Schuster, H. Hoffmann, and F. T. Chong, "Optimized compilation of aggregated instructions for realistic quantum computers," in *Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems*, New York, NY, USA, 2019, p. 1031–1044, DOI: 10.1145/3297858.3304018.

- [34] M. Hein, W. Dür, J. Eisert, R. Raussendorf, M. Van den Nest, and H.-J. Briegel, "Entanglement in graph states and its applications," in *Quantum Computers, Algorithms and Chaos*, ser. Proceedings of the International School of Physics "Enrico Fermi", vol. 162. Varenna, Italy: IOP Press, 2006, pp. 115–218, DOI: 10.3254/978-1-61499-018-5-115.

- [35] T.-C. Chen and Y.-W. Chang, "Modern floorplanning based on b/sup \*/-tree and fast simulated annealing," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 25, no. 4, pp. 637–650, 2006, DOI: 10.1109/TCAD.2006.870076.

- [36] D. Hespe, C. Schulz, and D. Strash, "Scalable kernelization for maximum independent sets," ACM Journal of Experimental Algorithmics, vol. 24, no. 1, 2019, DOI: 10.1145/3355502.

- [37] T. M. Graham, Y. Song, J. Scott, C. Poole, L. Phuttitarn, K. Jooya, P. Eichler, X. Jiang, A. Marra, B. Grinkemeyer, M. Kwon, M. Ebert, J. Cherek, M. T. Lichtman, M. Gillette, J. Gilbert, D. Bowman, T. Ballance, C. Campbell, E. D. Dahl, O. Crawford, N. S. Blunt, B. Rogers, T. Noel, and M. Saffman, "Multi-qubit entanglement and algorithms on a neutral-atom quantum computer," *Nature*, vol. 604, no. 7906, pp. 457–462, 2022, DOI: 10.1038/s41586-022-04603-6.

- [38] J. M. Baker, A. Litteken, C. Duckering, H. Hoffman, H. Bernien, and F. T. Chong, "Exploiting long-distance interactions and tolerating atom loss in neutral atom quantum architectures," in *Proceedings of the* 48th Annual International Symposium on Computer Architecture, Virtual Event, 2021, p. 818–831, DOI: 10.1109/ISCA52012.2021.00069.

- [39] Y. Li, Y. Zhang, M. Chen, X. Li, and P. Xu, "Timing-aware qubit mapping and gate scheduling adapted to neutral atom quantum computing," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 11, pp. 3768–3780, 2023, DOI: 10.1109/TCAD.2023.3261244.

- [40] T. Patel, D. Silver, and D. Tiwari, "Geyser: A compilation framework for quantum computing with neutral atoms," in *Proceedings of the 49th Annual International Symposium on Computer Architecture*, New York, NY, USA, 2022, p. 383–395, DOI: 10.1145/3470496.3527428.

- [41] S. Brandhofer, H. P. Büchler, and I. Polian, "Optimal mapping for near-term quantum architectures based on Rydberg atoms," in *Proceedings of the 40th IEEE/ACM International Conference on Computer-Aided Design*, Munich, Germany, 2021, DOI: 10.1109/IC-CAD51958.2021.9643490.

- [42] N. Nottingham, M. A. Perlin, R. White, H. Bernien, F. T. Chong, and J. M. Baker, "Decomposing and routing quantum circuits under constraints for neutral atom architectures", 2023. [Online]. Available: http://arxiv.org/abs/2307.14996

- [43] L. Schmid, S. Park, S. Kang, and R. Wille, "Hybrid circuit mapping: Leveraging the full spectrum of computational capabilities of neutral atom quantum computers", 2023. [Online]. Available: https://arxiv.org/abs/2311.14164

- [44] L. Guo, Y. Chi, J. Wang, J. Lau, W. Qiao, E. Ustun, Z. Zhang, and J. Cong, "Autobridge: Coupling coarse-grained floorplanning and pipelining for high-frequency HLS design on multi-die FPGAs," in *The* 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, 2021, pp. 81–92, DOI: 10.1145/3431920.3439289.

- [45] C. Li, M. Xie, C.-K. Koh, J. Cong, and P. H. Madden, "Routabilitydriven placement and white space allocation," *IEEE Transactions on Computer-aided design of Integrated Circuits and Systems*, vol. 26, no. 5, pp. 858–871, 2007, DOI: 10.1109/TCAD.2007.8361580.

- [46] G. Li, A. Wu, Y. Shi, A. Javadi-Abhari, Y. Ding, and Y. Xie, "Paulihedral: a generalized block-wise compiler optimization framework for quantum simulation kernels," in *Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems*, New York, NY, USA, 2022, p. 554–569, DOI: 10.1145/3503222.3507715.

- [47] Q. Xu, J. P. Bonilla Ataides, C. A. Pattison, N. Raveendran, D. Bluvstein, J. Wurtz, B. Vasić, M. D. Lukin, L. Jiang, and H. Zhou, "Constantoverhead fault-tolerant quantum computation with reconfigurable atom arrays," *Nature Physics*, 2024, DOI: 10.1038/s41567-024-02479-z.

- [48] T. Jiang and B. Ravikumar, "Minimal NFA problems are hard," SIAM Journal on Computing, vol. 22, no. 6, pp. 1117–1141, 1993, DOI: 10.1137/0222067.