作者:Zhang Zhaofu

以下是我阅读文献、结合自己的经验做的一些关于半导体异质结能带对齐的总结介绍,如果有任何不对,欢迎及时联系我做修改。希望转载注明源出处:http://blog.sciencenet.cn/blog-2686986-1172373.html

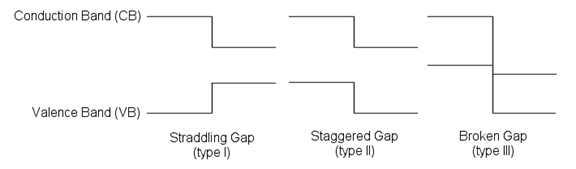

当半导体/半导体,或者绝缘体/半导体接触形成界面结构时,因为禁带宽度不同,在两侧材料的导带底和价带顶处会形成不连续的台阶,即能带台阶(band offset),其中导带底处的能带台阶被称为导带台阶(conduction band offset, CBO),价带顶处的能带台阶被称为价带台阶(valence band offset, VBO)。视能带对其情况不同,半导体异质结被分为三类:type-I, type-II,和type-III,其能带图如图1[1]:

图1 The three types of semiconductor heterojunctions organized by band alignment.

半导体能带对齐有重要意义。比如,对于电子器件来说,常用的为type-I band alignment,要求CBO/VBO大于1eV才能更有效的束缚电子/空穴,减小漏电[2]。type-II异质结在异质结光催化分解水领域,可以有效减小电子空穴对符合,提高光催化效率[3]。

界面两侧的能带对齐(band alignment)依赖于两侧材料的电荷转移。当异质结两侧无电荷转移时候,CBO是由异质结两侧材料的电子亲和势(electron affinity, EA)决定,被称为electron affinity model,又称为Anderson's rule[4]。在这个模型中,认为两侧真空能级持平,根据两侧材料的EA不同,得到两侧材料的CB位置,即CBO。根据材料的禁带宽度Eg数值,即可得到价带的相对关系,即VBO。另外的办法是采用一个外来的参考能级做参考标准,比如采取过渡金属杂质的高度局域化的d轨道能级来做参考标准[5],或者采用材料中H的(+/-)能级来做参考标准[6]。

实际的界面中,通常存在电荷转移,形成界面dipole。界面dipole会调整band alignment,使得band alignment不再遵循electron affinity model。描述有电荷转移的异质结

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3326

3326