# TECHNIQUES FOR FAST, ENERGY EFFICIENT ON-DIE GLOBAL COMMUNICATION

by

**Shomit Das**

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

August 2017

Copyright © Shomit Das 2017

All Rights Reserved

# The University of Utah Graduate School

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                                                  | Shomit Das |                           |  |

|----------------------------------------------------------------------|------------|---------------------------|--|

| has been approved by the following supervisory committee members:    |            |                           |  |

| Kenneth S. Stevens                                                   | , Chair    | 07/10/2015  Date Approved |  |

| Alan L. Davis                                                        | , Member   | 07/10/2015                |  |

|                                                                      | <u> </u>   | Date Approved             |  |

| Cynthia Furse                                                        | , Member   | 07/10/2015  Date Approved |  |

| Roberto Suaya                                                        | , Member   | Date Approved             |  |

| Timothy Hollis                                                       | , Member   | Date Approved             |  |

|                                                                      |            | Date Approved             |  |

| and by Gianluca Lazzi                                                |            | _ , Chair/Dean of         |  |

| the Department/College/School of Electrical and Computer Engineering |            |                           |  |

| and by David B. Kieda, Dean of The Graduate School.                  |            |                           |  |

## **ABSTRACT**

Communication surpasses computation as the power and performance bottleneck in forthcoming exascale processors. Scaling has made transistors cheap, but on-chip wires have grown more expensive, both in terms of latency as well as energy. Therefore, the need for low energy, high performance interconnects is highly pronounced, especially for long distance communication. In this work, we examine two aspects of the global signaling problem. The first part of the thesis focuses on a high bandwidth asynchronous signaling protocol for long distance communication. Asynchrony among intellectual property (IP) cores on a chip has become necessary in a System on Chip (SoC) environment. Traditional asynchronous handshaking protocol suffers from loss of throughput due to the added latency of sending the acknowledge signal back to the sender. We demonstrate a method that supports end-to-end communication across links with arbitrarily large latency, without limiting the bandwidth, so long as line variation can be reliably controlled. We also evaluate the energy and latency improvements as a result of the design choices made available by this protocol. The use of transmission lines as a physical interconnect medium shows promise for deep submicron technologies. In our evaluations, we notice a lower energy footprint, as well as vastly reduced wire latency for transmission line interconnects. We approach this problem from two sides. Using field solvers, we investigate the physical design choices to determine the optimal way to implement these lines for a given back-end-of-line (BEOL) stack. We also approach the problem from a system designer's viewpoint, looking at ways to optimize the lines for different performance targets. This work analyzes the advantages and pitfalls of implementing asynchronous channel protocols for communication over long distances. Finally, the innovations resulting from this work are applied to a network-on-chip design example and the resulting power-performance benefits are reported.

To the insane bard, the deranged artist, the unhinged maestro, and to the scientist, who is the maddest of them all.

# **CONTENTS**

| AB  | STRACT                                                                                                                                                                  | iii                  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LIS | T OF FIGURES                                                                                                                                                            | vii                  |

| LIS | T OF TABLES                                                                                                                                                             | ix                   |

| AC  | KNOWLEDGEMENTS                                                                                                                                                          | X                    |

| СН  | APTERS                                                                                                                                                                  |                      |

| 1.  | INTRODUCTION                                                                                                                                                            | 1                    |

|     | 1.1 Exascale Computing          1.2 Interconnect Challenges          1.3 System Design          1.4 Thesis Statement and Contributions          1.5 Thesis Organization | 2<br>4<br>5          |

| 2.  | BACKGROUND AND RELATED WORK                                                                                                                                             | 9                    |

|     | 2.1 Transmission Line Interconnect         2.2 Multifrequency Asynchronous Design         2.3 Networks-on-Chip         2.4 Summary                                      | 12<br>15             |

| 3.  | SOURCE ASYNCHRONOUS SIGNALING                                                                                                                                           | 20                   |

|     | 3.1 Introduction 3.2 Background 3.3 Source Asynchronous Signaling 3.4 SAS Models 3.5 Evaluation 3.6 Conclusion                                                          | 21<br>24<br>27<br>30 |

| 4.  | CHARACTERIZATION OF ON-CHIP TRANSMISSION LINES                                                                                                                          | 36                   |

|     | 4.1 Background 4.2 Simulation Setup 4.3 Design Choices 4.4 Circuit Design 4.5 Evaluation 4.6 Summary                                                                    | 38<br>38<br>39<br>41 |

| <b>5.</b> | CO  | MPARISON OF CHANNEL PROTOCOLS | 53 |

|-----------|-----|-------------------------------|----|

|           |     | Motivation                    |    |

|           |     | Models                        |    |

|           |     | Comparisons                   |    |

|           |     | Summary                       |    |

| 6.        | AN  | ETWORK-ON-CHIP EXAMPLE        | 73 |

|           | 6.1 | Introduction                  | 73 |

|           |     | Related Work                  |    |

|           |     | NoC Architecture and Circuits |    |

|           | 6.4 | NoC Simulator                 | 77 |

|           | 6.5 | Evaluation                    | 79 |

|           | 6.6 | Conclusion                    | 80 |

| 7.        | CO  | NCLUSION                      | 89 |

|           | 7.1 | Inferences                    | 89 |

|           |     | Future Work                   |    |

| REI       | ER1 | ENCES                         | 92 |

# LIST OF FIGURES

| 1.1 | The exascale challenge                                                   | 7  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Communication costs                                                      | 7  |

| 1.3 | Communication fabric choices                                             | 8  |

| 1.4 | Clocked and asynchronous methods                                         | 8  |

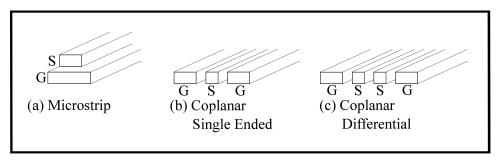

| 2.1 | On-chip TL configurations                                                | 17 |

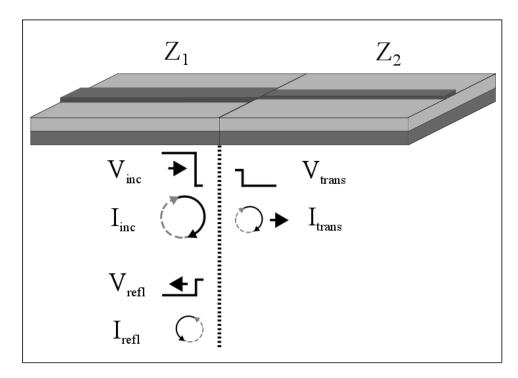

| 2.2 | Reflection in transmission lines                                         | 18 |

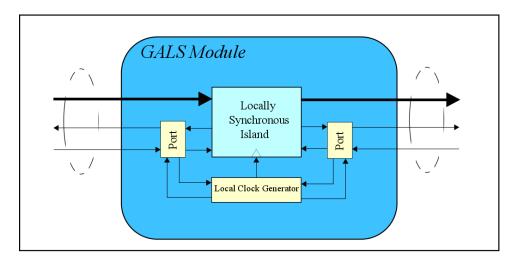

| 2.3 | GALS module                                                              | 18 |

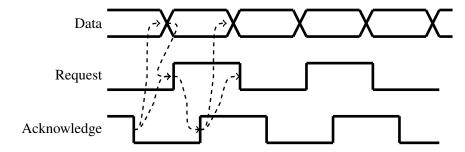

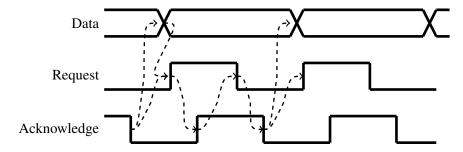

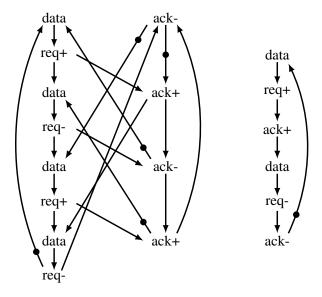

| 2.4 | 2-phase protocol                                                         | 18 |

| 2.5 | 4-phase protocol                                                         | 19 |

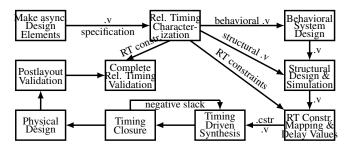

| 2.6 | Simplified relative timing design flow                                   | 19 |

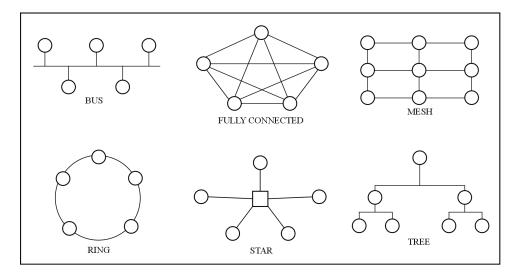

| 2.7 | Regular network topologies                                               | 19 |

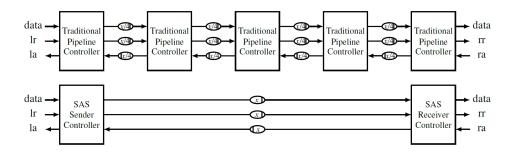

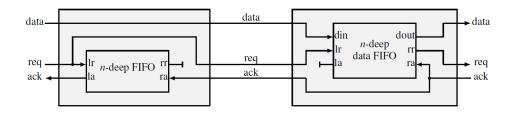

| 3.1 | Traditional and SAS communication pipelines with large wire delay of $x$ | 33 |

| 3.2 | NRZ SAS $n = 2$ vs traditional channel protocol                          | 33 |

| 3.3 | SAS two-phase handshaking protocol $n = 2$                               | 34 |

| 3.4 | SAS sender block                                                         | 34 |

| 3.5 | SAS receiver block                                                       | 34 |

| 3.6 | Complete SAS channel                                                     | 34 |

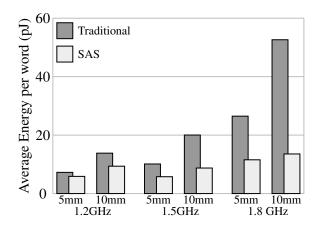

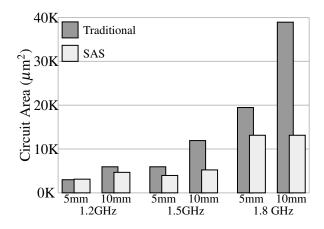

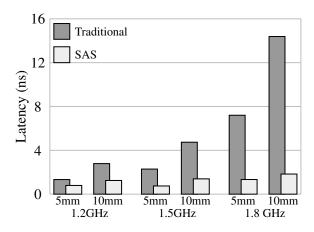

| 3.7 | Energy comparison: traditional vs SAS links                              | 35 |

| 3.8 | Area comparison                                                          | 35 |

| 3.9 | Latency comparison                                                       | 35 |

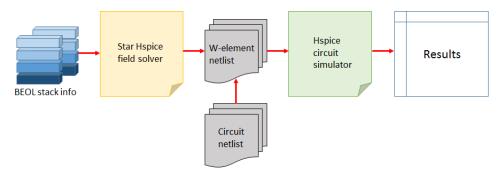

| 4.1 | Characterization process flow                                            | 43 |

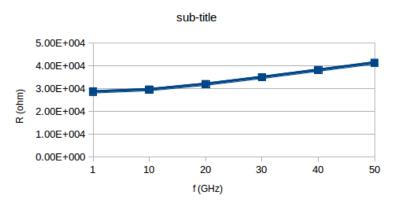

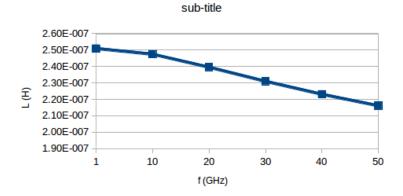

| 4.2 | Proximity effect at high frequencies                                     | 43 |

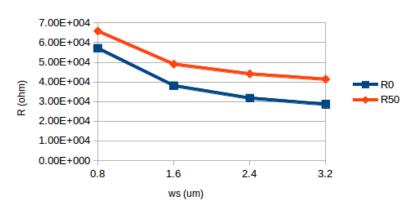

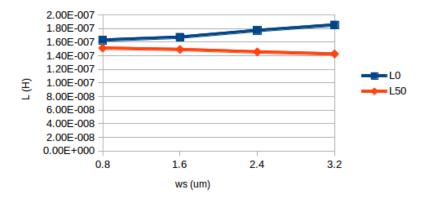

| 4.3 | Effect of conductor width                                                | 44 |

| 4.4 | Capacitance limitation of increasing conductor width                     | 45 |

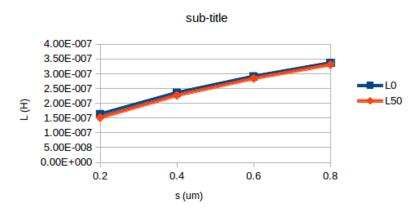

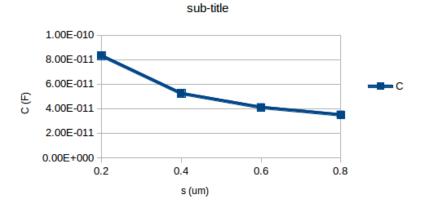

| 4.5 | Implications of increasing the spacing                                   | 46 |

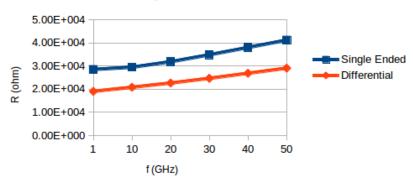

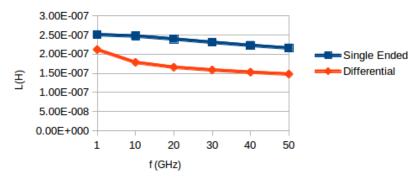

| 4.6 | Differential vs single ended lines                                       | 47 |

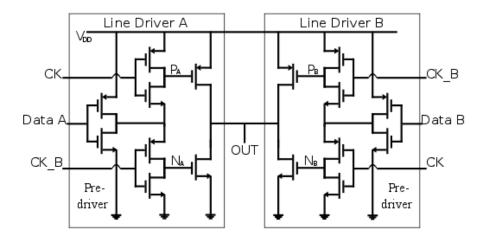

| 4.7 | Voltage mode driver                                                      | 48 |

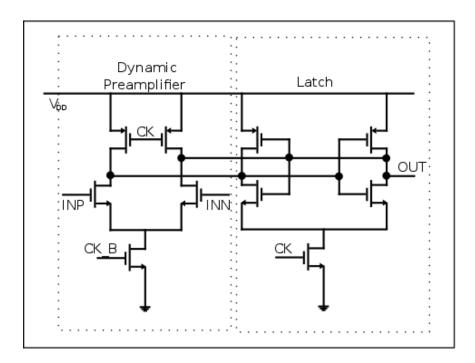

| 4.8 | Comparator receiver                                                      | 48 |

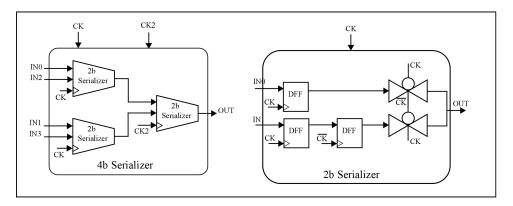

| 4.9  | Serializer                                                 | 49 |

|------|------------------------------------------------------------|----|

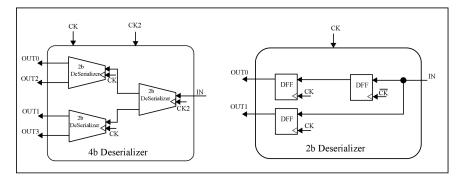

| 4.10 | Deserializer                                               | 49 |

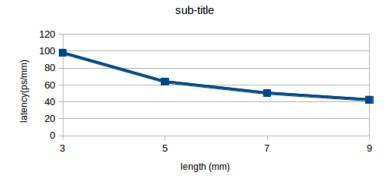

| 4.11 | Latency of a TL link                                       | 50 |

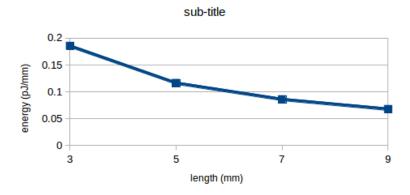

| 4.12 | Energy of a TL link                                        | 51 |

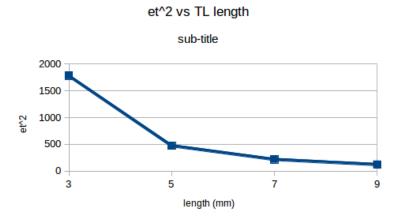

| 4.13 | Energy-delay squared product of a TL link                  | 51 |

| 4.14 | Comparing RC and TL                                        | 52 |

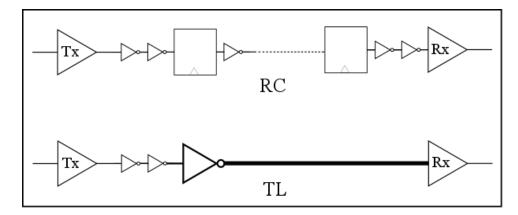

| 5.1  | No repeaters in TL channels                                | 63 |

| 5.2  | Synchronous and asynchronous topologies                    | 63 |

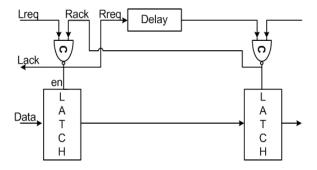

| 5.3  | Simulated implementation for bundled data 4-phase protocol | 64 |

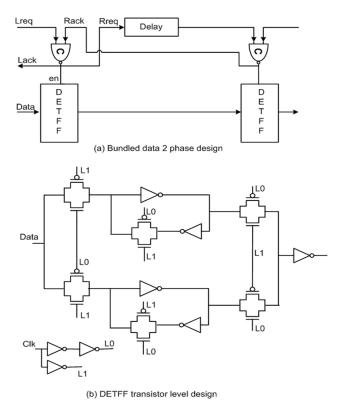

| 5.4  | Simulated implementation for bundled data 2-phase protocol | 64 |

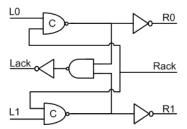

| 5.5  | Simulated DI 1-of-2 protocol implementation                | 64 |

| 5.6  | Cycle time for various protocols                           | 65 |

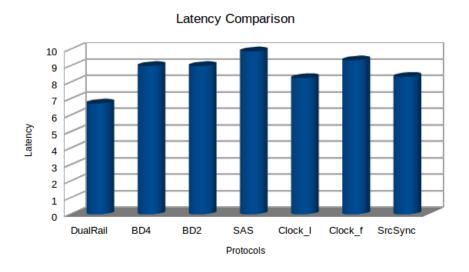

| 5.7  | Latency for various protocols                              | 65 |

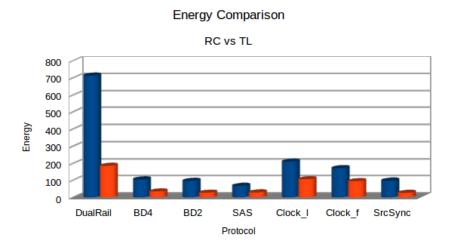

| 5.8  | Energy for various protocols                               | 66 |

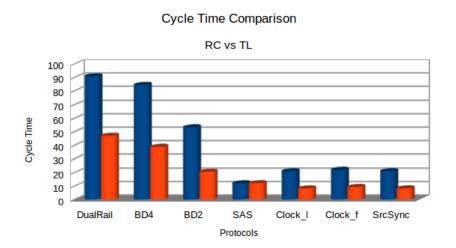

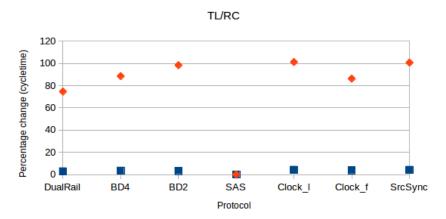

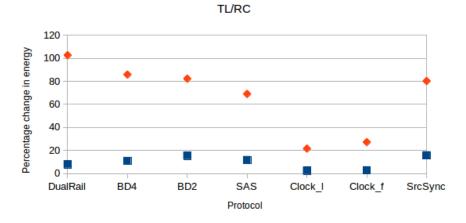

| 5.9  | Cycle time RC vs TL                                        | 66 |

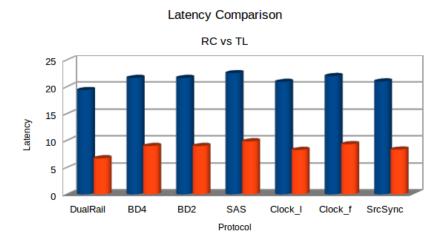

| 5.10 | Latency RC vs TL                                           | 67 |

| 5.11 | Energy RC vs TL                                            | 67 |

| 5.12 | Wirelength effect on cycle time                            | 68 |

| 5.13 | Contribution of wire delay to cycle time (RC)              | 68 |

| 5.14 | Contribution of wire delay to cycle time (TL)              | 69 |

| 5.15 | Wirelength effect on energy                                | 69 |

| 6.1  | Mesh based routing examples                                | 81 |

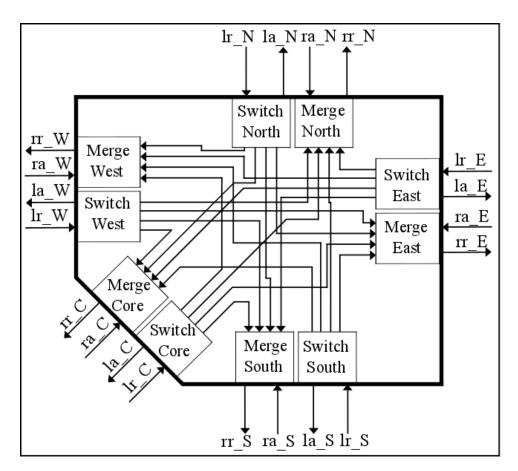

| 6.2  | Router architecture                                        | 82 |

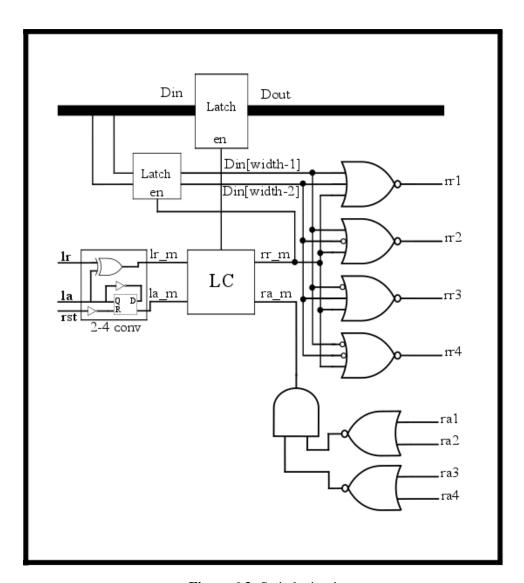

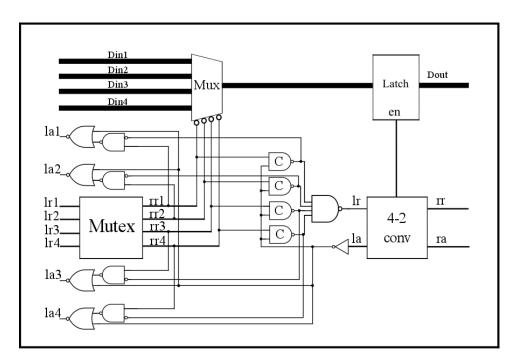

| 6.3  | Switch circuit                                             | 83 |

| 6.4  | Merge circuit                                              | 84 |

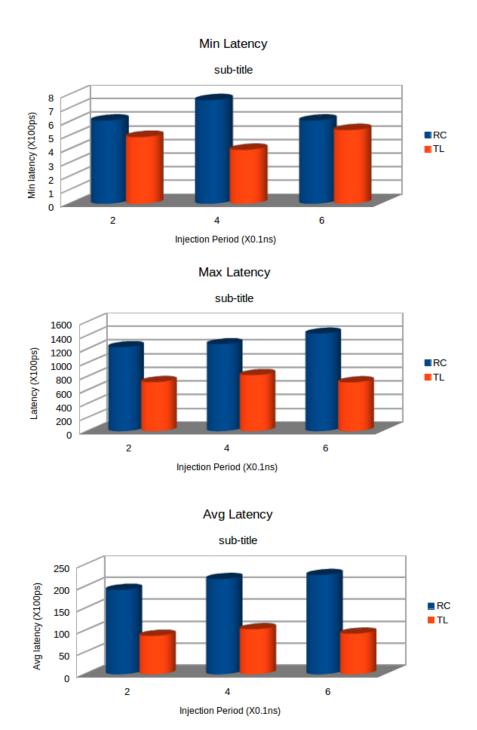

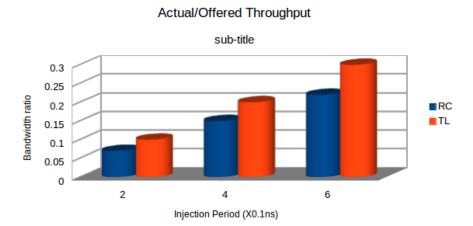

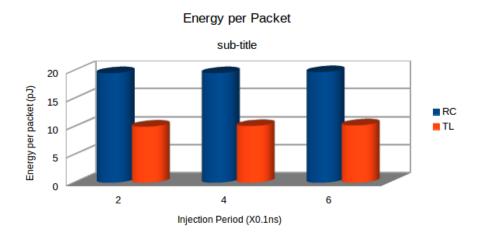

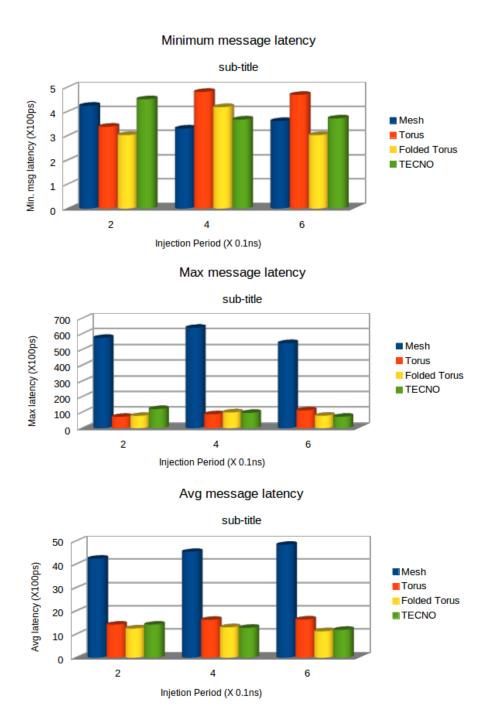

| 6.5  | Latency of RC and TL mesh networks                         | 85 |

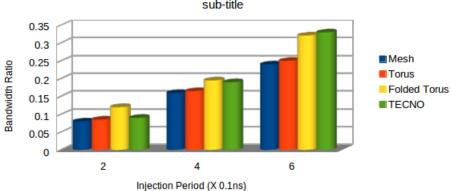

| 6.6  | Throughput and energy of RC and TL mesh networks           | 86 |

| 6.7  | Latency of RC and TL mesh networks                         | 87 |

| 6.8  | Throughput and energy of RC and TL mesh networks           | 88 |

# LIST OF TABLES

| 3.1 | Bandwidth and energy comparison                                                       | 34 |

|-----|---------------------------------------------------------------------------------------|----|

| 5.1 | Parameter variables and derivatives                                                   | 70 |

| 5.2 | Operating parameters                                                                  | 70 |

| 5.3 | Asynchronous control parameters from 65nm SPICE simulations of the designs $\ \ldots$ | 71 |

| 5.4 | Cycle time equations measured in FO4 delays.                                          | 71 |

| 5.5 | Latency per stage measured in FO4 delays.                                             | 71 |

| 5.6 | Models for average energy per transaction per pipe stage                              | 72 |

| 6.1 | TL evaluation                                                                         | 81 |

| 6.2 | Repeated RC evaluation                                                                | 81 |

## **ACKNOWLEDGEMENTS**

This document, six years in the making, has several primary contributors. First and foremost, my advisor Ken Stevens whose almost boyish enthusiasm over all things technical was a constant source of inspiration. He provided clever insights to seemingly insurmountable problems, offered counsel during times of negative energy, and displayed pride at the eventual success of my endeavor. I look forward to a long, fruitful collaboration with him. Roberto was my mentor during excellent summers in Grenoble, even letting me use his home during my internship with Mentor Graphics. I cannot thank him enough for going above and beyond normal mentor duties in order to enable me to work with him in France. Tim, Cindy, and Al carefully monitored my progress over several years so I could get to this point without any major hiccups. They were always quick to respond to even trivial questions that I had, despite their incredibly busy schedules. Georgios Manetas was my electromagnetic guru during and beyond my intern days. I will always appreciate his professional and personal help during some tough transition times in Grenoble. A big shout-out to the Greek gang of Grenoble as well as Zohaib for enhancing my time spent in Europe. Apart from the three internships with Mentor Graphics, I was also very fortunate to have worked with Ram Krishnamurthy's group at Intel's Circuit Research Labs. Greg, Himanshu, Mark, and others helped me shape my understanding of physical interconnect design. Salt Lake City is one of the best places I have ever lived in. My time as a grad student would not have been the same without the help and support of DK, Para, Sanket, Rashmi, Push, Raj, Rahul, NP, Preethi, Aadi, Rungta, and other members of the JLT Gang. I will always cherish our friendship. I have had the fortune of working along side some incredible minds at the U. My sincere thanks to Eliyah, Dan, Junbok, Vikas, Krishnaji, Willy, Dipanjan, Jotham, Tannu, Mac, and Dheeraj for their help and camaraderie during my time at the lab. Julie has been a source of tremendous support during the final third of grad life. I look forward to many adventures in the coming days. My extended family of aunts, uncles, and cousins have always boosted my self-confidence and provided unwavering love all my life. I am very grateful for that. Lastly, nothing in my life would have been possible without my parents, Meeta and Nirban Das. I owe everything to them, including this dissertation.

# **CHAPTER 1**

#### INTRODUCTION

This chapter sets up the motivation for the problem tackled in this dissertation. A summary of proposed solutions is provided, as well as the outline for the remaining manuscript.

# 1.1 Exascale Computing

As big data analytics becomes the cornerstone of contemporary commercial organizations, high performance computing is making the transition from a niche market to an everyday one. The next major milestone in the journey to shape future supercomputers is to achieve one billion billion floating point operations per second (1 exaflops). Such mammoth computing machines are dubbed *exascale computers*. Apart from predictive analytics for businesses, there are several potential scientific applications for exascale computing including:

- Mapping the human brain

- Modeling regional climate changes and severe weather patterns

- Simulation of the motion of every atom in a biochemical system

- Design of advanced materials and renewable energy sources

- Modeling fusion and fission reactions

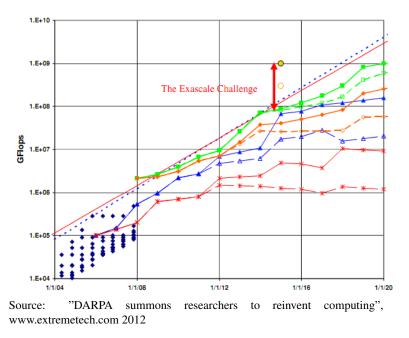

Microprocessor clock speeds are expected to remain fairly constant in the 1 to 2 GHz range due to the linear dependence of power consumption to operating frequency. Therefore, the required performance boost has to be facilitated by a substantial increase in on-chip parallelism. This will include hardware parallelism along with supporting software framework. It is estimated that the degree of parallelism on a single chip will compare to the number of discrete nodes of massively parallel supercomputers from the 1980s [1]. However, exascale computing is not merely about assembling a large number of nodes on a die. It requires a complete reimagination of the way we compute, how we communicate among nodes, and also how we design our applications. Figure 1.1 shows the gap between exascale requirements and current state-of-the-art. Some of the assumptions that need to be updated are as follows:

- Power has to replace maximum clock frequency as the principal design objective

- Communication overheads have to outweigh computation costs in keeping with the motto of flops are free, wires are expensive

- Heterogeneity introduced by the rising inclusion of graphics processing units (GPUs) and accelerators in modern architectures needs to replace the prevailing ideology of adding more uniform cores to a supercomputer.

- The growth in concurrency introduced by the increased parallelism demands a migration from the the clocked to an asynchronous regime

Power is the primary roadblock to exascale systems. The apex position in the Top 500 supercomputers list is currently held by the Tianhe-2 system at the National Super Computer Center in Guangzhou, China [2]. Using 3.12 million cores, it achieves 33.86 petaflops while burning a massive 17.8 MW. If we simply scale the performance for our desired 1 exaflops, it results in a power requirement of 534 MW, which is higher than the power output of the Fort Calhoun nuclear power plant in Nebraska, U.S.A. Obviously, this is a preposterous demand; future exascale supercomputers will need to achieve their performance at more or less the same order of magnitude as current power budgets.

Similarly, connecting thousands of processing elements on a chip so that they communicate reliably among themselves is a difficult problem. To do so with a limited power budget is a daunting task.

# **1.2** Interconnect Challenges

This work investigates the matter of high bandwidth, low latency, energy efficient on-chip data communication. There are multiple approaches to tackling this issue. In this section, we first outline the problem, and appraise the various existing solutions. Finally, we justify the choice of path we take to approach the challenges.

#### 1.2.1 The Cost of Moving Data

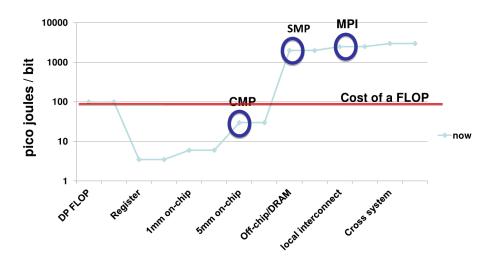

While computation energy costs are reducing, communicating data on a chip has become absurdly expensive. In a 35nm process node, energy expenditures necessary to propagate a 64b signal 2mm are approximately equal to performing a 64b floating point operation [3]. The bandwidth of a conventional diffusive wire varies inversely as the square of the wire length. Higher throughputs are possible by increasing the drive voltage, but this comes at the price of increased energy consumption. Repeaters are included in long wires to boost the signal and maintain a linear power-distance relationship; however, adding these extra active devices also increases the power consumed by

the chip. Decreasing feature sizes in modern processes increases the per unit resistance of the copper wires, which leads to two deleterious effects. Not only does the wire draw more power while moving data bits, it also performs this movement more slowly due to the increased RC constant. This means higher bandwidth imposes a higher premium on the power cost, while also keeping the throughput localized due to the power-distance correlation. It is clear that realizing exascale computing will require a redesign of the communication methodology. This dissertation examines alternative techniques for on-chip data movement. Figure 1.2 shows the energy cost of data movement at different interconnect levels relative to a floating point operation [4].

#### 1.2.2 Existing Techniques

The interconnect problem can be dealt with using process technology to obtain more suitable dielectric materials, such as low-k and air-gap dielectrics [5]. New wiring materials such as carbon nanotubes [6] and graphene nanoribbons [7] have also been proposed. While these solutions have potential, we look at using design techniques for existing materials to solve the problem.

Power consumption is proportional to the squared value of the signal voltage. Therefore, low voltage swing signaling using differential wires has tremendous potential for power savings. However, such an apparatus is highly susceptible to noise induced by variation, coupling, reflections, and other sources. Also, sense amplifiers used in such techniques are often found to be power hungry. Another solution to offset the effects of long wires is to avoid them by vertically stacking thinned die on top of each other in a **3D** configuration [8]. The long wires are then replaced by through silicon vias (TSV) that pass through chip substrates, but reduce global wire length considerably. However, this technology is plagued by yield issues and also requires complicated design and computer aided design (CAD) tool support. Researchers have also studied the feasibility of augmenting on-chip networks with single hop, long range wireless links [9]. Wireless point-to-point links help overcome the shortcomings of lossy metallized global interconnects while also mitigating routing congestion. These links require additional complex circuitry such as on-chip antennae and suffer from reliability issues arising from manufacturing. **Optical interconnects** provide low latency, high bandwidth data transfer using light for signal propagation and dense wave division multiplexing (DWDM) [10], [11]. Wavelength selective ring resonators are used to distinguish different signals sent as waves with different wavelengths on a single channel. This facilitates a substantially large throughput per unit wiring area as compared to conventional electrical links. However, the ring resonators need to be constantly heated, in a process called trimming so as to be tuned to their desired wavelengths. This results in a large static power overhead. Optical-electrical interfaces and laser drivers also amplify the power requirements of this signaling scheme. There is also a large cost associated with

fabricating the necessary optical devices, such as laser sources and photo detectors on silicon. In this dissertation, we explore the use of on-chip transmission lines as a suitable replacement for diffusive wires on long links.

#### 1.2.3 Our Approach

RLC transmission lines (TL) are fundamentally different from diffusive RC wires. Signals on a transmission line propagate as electromagnetic waves on the dielectric surrounding the lines. This means that very low latency of signal propagation is possible with this technique. Additionally, since the transmission lines essentially act as waveguides, data bits can travel farther distances as compared to RC lines, without making use of repeaters, resulting in much lower energy requirements. Transmission lines are implemented as full swing communication links in regular back-end-of-line (BEOL) metal stack without the need for exotic TSV structures or complicated circuitry like antennae and lasers, among others. However, a number of design constraints need to hold for proper on-chip deployment of RLC interconnects. These consist of ensuring precise dimensions, topologies, and aspect ratios for the lines. Transmission lines are susceptible to reflections caused by impedance mismatches at discontinuities along the line. They are also vulnerable to crosstalk induced by coupling. Therefore, care must be taken at every stage of the TL link design, from circuit design to layout, to accurately implement these long links on a chip.

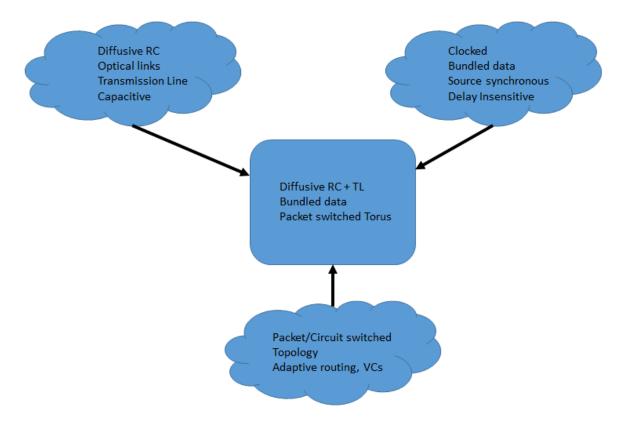

# 1.3 System Design

The choice of signaling technique used for data transport is just one parameter in the overall implementation of the communication fabric. This work also appraises other design choices available to the system architect, such as signaling protocols and network-on-chip designs. Figure 1.3 shows an example of the communication fabric chosen for implementation from the alternatives available.

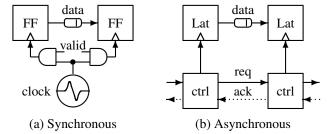

#### 1.3.1 Signaling Protocols

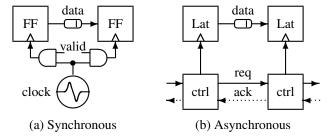

Several clocked and self-timed pipeline methodologies are available for reliable communication across a channel. In synchronous schemes, data is transmitted every clock cycle between latches or flip-flops. On the other hand, asynchronous signaling utilizes handshaking for data transfer. Bundled data protocols use the same datapath as clocked techniques, but use an *ack* signal to enforce data validity. In contrast, synchronous protocols restrict data changes via setup and hold timing constraints. Figure 1.4 shows the inherent differences between clocked and bundled data asynchronous configurations. Another self-timed protocol uses 1-of-N codes to encode data validity within data wires. Handshaking signals add an overhead to the throughput and energy properties of a communication system. Naturally, clocked pipeline protocols are expected to perform better for

purely data transfer purposes. However, sometimes it becomes useful, and often times necessary, to avoid a shared global clock in a system. In this dissertation, we evaluate an asynchronous channel protocol that emulates the properties of synchronous signaling protocols, while retaining its self-timed properties and associated capabilities. We also compare the performance and power characteristics of these protocols when applied to transmission line global channels.

# 1.3.2 Network-on-Chip

As the spotlight moves from computation to communication in modern-day systems-on-chip, a majority of the design effort goes towards constructing an efficient, reliable, low power communication fabric [12]. A good on-chip network must transmit large amounts of data with low latency, consume almost no static power and little dynamic power, route packets with negligible error, manage congestion, and perform well even at heavy workloads, and for different applications. It must perform these tasks while connecting hundreds of nodes. It is nearly impossible to achieve all these goals with a single design; therefore, engineers settle for Pareto optimality. There are many design choices while implementing a NoC, including choice of topology, routing scheme, router architecture, flow control, etc. There are trade-offs associated with each of these options. Experts agree that network power consumption is one of the primary concerns in future exascale trends. In this dissertation, we evaluate the use of reactive, self-timed routers and signaling schemes for achieving low power NoC operation. We also explore the use of low latency, low energy, high bandwidth transmission lines as global interconnects for these NoCs.

#### 1.4 Thesis Statement and Contributions

Given the immediate and rising demand for energy efficient, high performance, long range interconnects, this work provides solutions using three main approaches. Low latency transmission lines are designed and characterized for high frequency, low power operation. Various pipeline protocols are examined for communication over long links and a novel method is presented to duplicate the benefits of clocked signaling in an asynchronous handshaking method. Finally, a network-on-chip design is presented that incorporates the modularity of multi-frequency asynchronous operation and the signaling properties of RLC interconnects to demonstrate the efficacy of our proposed methods at the system level.

This thesis makes several contributions towards advancing our understanding of the challenges and opportunities related to building long range on-chip communication links. The contributions range from applying very low level electromagnetic principles to design better interconnects to understanding software constructs to build accurate simulators. Specifically, some of them are:

- A method to enable full communication bandwidth on wires with arbitrary delay when employing handshake communication. This method supports end-to-end communication across links with arbitrarily large but finite latency without limiting the bandwidth, so long as line variation can be reliably controlled. This technique decouples wire latency and wire lengths in an unconventional manner that is very useful in modern chips.

- Characterization of RLC interconnects for use as long haul NoC links. The effects of design choices on link performance are studied. Various circuit elements that comprise the transmission line transceiver system are compared and contrasted. Guidelines for efficient transmission line operation are provided for designers.

- A comparative study of synchronous and asynchronous pipeline protocols applied to communication over a transmission line channel. Various metrics are evaluated and the most efficient signaling protocols are identified. Detailed communication models are presented and verified with circuit simulations.

- A transmission line enabled asynchronous NoC is designed and simulated. An accurate Verilog based NoC simulator is built to appraise the effect of including transmission lines in NoC topologies. Deadlock avoidance in circular asynchronous routing topologies is studied and solutions are proposed.

# 1.5 Thesis Organization

This thesis is organized as follows:

- Chapter 2 provides some background information pertaining to the major themes used in this thesis. These include concepts in transmission line signaling, asynchronous circuit design, and networks-on-chip.

- A new channel protocol for high bandwidth communication, called source asynchronous signaling is introduced in Chapter 3. Various conditions to ensure correct operation are derived. The protocol is then evaluated against traditional asynchronous channel protocol.

- On-chip transmission lines are designed and characterized in Chapter 4. The simulation process and circuits used are described. Trade-offs of choosing one line over another in terms of channel performance are discussed.

- Chapter 5 compares numerous synchronous and asynchronous protocols for use over long range transmission lines. First order models are derived for cycle-time, latency, and energy.

- A network-on-chip design is presented in **Chapter 6** that incorporates the techniques from the preceding chapters to evaluate their effects on system performance. This design is then compared against traditional approaches.

• Chapter 7 provides concluding remarks and ideas for future work that will hopefully spawn more focused research in this field.

Figure 1.1: The exascale challenge

Source: "Exascale Computing Technology Challenges [1]"

Figure 1.2: Communication costs

Figure 1.3: Communication fabric choices

Figure 1.4: Clocked and asynchronous methods

# **CHAPTER 2**

### BACKGROUND AND RELATED WORK

Overcoming design challenges in modern high performance VLSI design requires a cross-disciplinary approach. Low level circuit designers need to be aware of system implications of their design choices, while system architects need to understand the complex tweaks done at the transistor level that can affect power and performance. Mixed signal design is gaining traction as variation and other analog effects manifest themselves in deep submicron regimes. Engineering teams can no longer live in the vacua of their domains. This thesis delves into three major keystones of the communication fabric – the transmission line physical medium, the asynchronous signaling protocols, and the high level network design. In this chapter, some background in each of these spheres is presented, along with examples of previous work relevant to our approach.

# 2.1 Transmission Line Interconnect

By definition, transmission lines (TL) are quite simply a pair of conductors (signal and return) with nonzero length [13]. They possess some electrical and magnetic properties that are native only to them. Although classified as a passive element, TL behavior is very removed from other passive elements such as resistance (R), capacitance (C), and inductance (L). A lossless ideal transmission line can propagate electromagnetic waves at the speed of light in the dielectric medium surrounding the conductor pair. In practice, however, many factors determine the signal carrying capabilities of a transmission line as we see in the following sections.

## 2.1.1 Signal Propagation

A signal propagating along a transmission line uses both the signal and return paths. Close coupling between these two conductors results in superior channel performance. Therefore, if the cross-section of the transmission line remains fairly constant along its entire length, the line carries the signal better. Such lines are called uniform, or controlled impedance transmission lines. This should be the design goal of the physical designer implementing on-chip TLs. Depending on the relative arrangement of the signal and return paths, on-chip transmission lines are classified as

coplanar or microstrip as shown in Figure 2.1. The difference between single ended and differential TLs will be covered in a later chapter. Depending on the geometry, and metal and dielectric properties, transmission lines propagate electromagnetic (EM) waves in the following modes:

- TE: In the *Transverse Electric* mode, only the magnetic field waves oscillate in the direction of signal propagation

- TM: Conversely, in the *Transverse Magnetic* mode, only the electric field waves oscillate in the direction of signal propagation

- TEM: *Transverse Electromagnetic* mode dictates that both electric and magnetic field lines are normal to the direction of EM wave propagation. Due to its nondispersive nature, TEM is the preferred mode of operation for transmission lines. However, this mode imposes many unreasonable conditions on the material properties of the TL, such as infinite conductor conductivity and lossless, uniform dielectric.

- Quasi-TEM: In a non-ideal, hybrid environment such as silicon die consisting of multiple boundary regions, a *quasi TEM* mode exists where most, but not all of the EM waves are normal to the direction of signal propagation.

#### 2.1.2 Definitions

As a passive, lossy element, a transmission line offers impedance to the signal propagating across it. At each time step, the ratio of the signal voltage to the current flowing through the line is referred to as the instantaneous impedance. If the voltage and the charge injected into the line remain unchanged, the signal encounters a fixed impedance. The only two variables that determine the impedance of the transmission line are the signal speed and per unit line capacitance. The signal speed depends on the dielectric material surrounding the wires, while the capacitance depends on the cross section of the line. It is interesting to note that the impedance does not depend on the length of the line or the signal voltage propagating along it. Therefore, for a uniform transmission line, the signal observes a constant instantaneous impedance at every point in the line. This is the **characteristic impedance** ( $Z_0$ ) of the transmission line. If the line is not uniform, any perturbation in the wire geometry will cause changes in the capacitance. The resulting variation in the instantaneous impedance causes reflections and loss of signal integrity.

Signals propagating along a transmission line decays exponentially with distance. This signal degradation manifests in two ways – attenuation of the signal voltage level, and shift in the signal phase. The **propagation constant** ( $\gamma$ ) metric is used to denote this effect. It consists of a real part, attenuation constant ( $\alpha$ ), and an imaginary part, phase constant ( $\beta$ ).  $\alpha$  represents the signal attenuation and is usually measured by dB/m. The phase of the signal along the line is indicated by  $\beta$  and

has the unit of radian/m.  $Z_0$  and  $\gamma$  are often sufficient to describe the behavior of a transmission line. Other physical and electromagnetic properties as well as 2-port network (S-parameters) behavior are also used to characterize transmission lines.

## 2.1.3 Transmission Line Signal Distortion

Since the transmission line channel does not make use of periodic repeaters to boost the signal, extra care must be given to the matter of signal integrity along the long link. There are three main contributors to signal distortion along an RLC channel. In this section, we discuss these culprits and ways to mitigate their effects.

- Reflection: As mentioned in the previous section, any time a wave encounters a change in instantaneous impedance down a transmission line, part of the wave will be reflected back to the source as seen in Figure 2.2. The reflected wave travels back to the source, and is reflected back again. This back-and-forth continues until the reflected wave attenuates completely. At the ends of the transmission line, these spurious signals cause overshoot and undershoot of the desired signal; this effect is called ringing. Ringing is harmful because it increases power consumption due the added current drawn by the reflected signals. Also, at the receiving end, the extra signal transitions may lead to logic and timing errors, thereby compromising the passivity of the line. Reflections can be avoided, to some degree, by keeping the TL link uniform. However, this may not always be possible due to the presence of vias, bends, forks, and joins in an on-chip wiring topology. Terminating one or both ends of the transmission line with resistive or capacitive elements minimizes reflections in the line. The high resistance of metal wires in modern processes serve as a damping mechanism for reflected signals, thereby providing an intrinsic series resistive termination.

- Attenuation: Signal loss in a transmission line is frequency dependent. Higher frequency signal components get selectively attenuated more than the low frequency components. This uneven frequency domain attenuation causes an increase in the signal rise time, and subsequently, a decrease in signal bandwidth. Also, simple boosting repeaters do not work in this case due to the selective nature of signal loss. Attenuation can be attributed to the losses occurring mainly in the conductor and the dielectric. Coupling to other lines and radiation also contribute to signal loss, albeit insignificantly. The nonlinear frequency response of the channel means that different components of the same signal arrive at the receiver at different times, leading to multipath propagation. This leads to blurring together of successive symbols at the receiving end, known as inter symbol interference (ISI). The intuitive solutions to solving this problem is to either boost the high frequencies at the sending end (preemphasis),

- or to filter out low frequency components at the receiving end (**equalization**). This approach, however, introduces extra circuitry to the TL communication system.

- Crosstalk: Crosstalk is the superposition of a spurious signal from one net to another due to coupling between the two wires. Coupling is caused by the fringe electric and magnetic fields surrounding a conductor. Changing electromagnetic fields from one wire induce current in the adjacent wire. This manifests as distortion in the signal at both near and far ends of the line. The obvious method is to increase the separation between the affected wires and/or introduce guard bands between them. However, this reduces the per unit wiring area throughput of the link. Other engineering solutions include using wide area return planes instead of return lines, decrease the characteristic impedance of the line, increasing the signal rise time, and reducing the coupling length of the wires.

#### 2.1.4 Existing Work

Transmission line signaling is the primary medium of data transfer in off-chip environments. There have been a few attempts at engineering on-chip RLC channels. Beckmann [14] first suggested using transmission lines to reduce the communication latency incurred while accessing L2 caches. In earlier process nodes, using TL links in upper metal layers in lieu of diffusive wires translated to a direct 30× communication speedup. The numbers in current technology are not so optimistic. Suaya outlined the use of transmission lines for clock tree networks [15]. Chang [16] used modulation to up-convert data signals to a carrier wave and transmit over a microstrip TL. However, the added RF mixer circuitry increased the power budget and complexity of the communication link. A current mode logic transceiver was demonstrated by Ito et.al. [17]. This work demonstrated reliable TL signaling on a fabricated die using simple circuitry and differential transmission lines. A complete serial link with SERDES circuits was implemented by Flynn [18]. The architectural advantages of using transmission lines were reported by Carpenter [19]. In this domain, it is clear that we stand on the shoulder of giants.

# 2.2 Multifrequency Asynchronous Design

The complex nature of modern VLSI design has led to the proliferation of *intellectual property* (IP) blocks on a chip. These IP blocks may be designed by different teams and optimized for different goals, resulting in different operating frequencies. The overall System on Chip (SoC) is comprised of these blocks stitched together using a communication fabric. The predicted heterogenous nature of future exascale systems indicates that this organization is here to stay. Clock domain crossing required to communicate between different parts of the same chip is not only expensive

in terms of latency, power, and area, but also impacts the reliability of the system. Asynchronous design, by its very nature is intrinsically suited to adoption in this multi-frequency regime.

# 2.2.1 Globally Asynchronous Locally Synchronous

Globally Asynchronous Locally Synchronous is a design style that allows IP blocks to operate in synchrony with their associated local clocks, yet employs a self-timed communication fabric to facilitate talking among the modules [20]. Clock domain crossing interfaces are wrapped around each block that translate between the asynchronous fabric and the synchronous domain. This enables a kind of 'plug-and-play' modularity in the system. Clocked design is well understood and widely adopted in both industry and academia. GALS allows engineers to make use of highly optimized IP blocks without having to synchronize to a global chip clock. On the other hand, there are several misgivings regarding asynchronous circuit design such as inadequate computer aided design (CAD) tool support, potential races and hazards in the final design, trouble with testability, among others. GALS technique allows circuit designers to remain in their comfort zone while unlocking the advantages of modular, multifrequency system design. However, this comes at a price - each block is driven from a local pausible clock generator to stretch or pause the clock during data transfer, as shown in Figure 2.3. This is usually achieved with the help of ring oscillators. Metastability is a concern in such implementations, and must be accounted for [21]. Other options to realize GALS designs are to use synchronizers to communicate between completely asynchronous or loosely synchronous timing domains.

#### 2.2.2 Basics of Asynchronous Circuit Design

An asynchronous design is not tied to a single clock frequency. Instead, it is reactive and is operational only when valid data presents itself. The role of timing in digital design is essentially to impose sequencing. Using a central timing reference for this purpose is inefficient in terms of power and performance. However, it makes design simpler and lends support to CAD tools that exploit the *lockstep* arrangement imposed on the signals. Self-timed designs enforce sequencing and flow control with simple handshaking. In cases when high performance and low energy are demanded from the system, self-timed designs stand out over traditional clocked design due to their adherence to the average-case performance in contrast to the worst-case performance enforced by the clocked design style. Power constrained designs especially are tailored for asynchronous circuits since they immediately get rid of the power spent in the clock tree. Asynchronous designs also possess intrinsic modularity and concurrency that make them suitable for use in highly parallel architectures.

There are several ways to design asynchronous circuits. The easiest way to differentiate design styles is to consider the type of timing assumptions made regarding the design. **delay insensitive**

(DI) designs are completely agnostic to gate and wire delays. This highly conservative nature of timing means that the resulting circuits are slow and power hungry. One simple relaxation made to the DI assumption, namely that wire forks have the exact delay (isochronic forks), enables the circuits to be much less bulky. This class of circuits are called quasi delay insensitive. If wire delays are assumed to be zero, yet gate delays are arbitrarily large, the design style is called **speed independent**. The fastest, smallest, and most energy efficient self-timed circuits are made possible using timed circuits. In this case, gate delays have predefined upper and lower bounds. Naturally, these extra timing constraints warrant extra effort for timing verification. Each style has its own advantages and disadvantages. For example, while DI designs are bound to be larger than their timed counterparts, they are also more robust against PVT timing variations, and far easier to design. Depending on the number of signal transitions per valid transaction, asynchronous protocols can be classified as 2-phase or 4-phase. The 2-phase or non-return-to-zero (NRZ) protocol consists of two transitions to complete a data transaction. It is also called transition signaling protocol. A pair or transitions, either high-to-low or low-to-high, one each on the request and acknowledge lines indicates a valid data transfer. While this protocol is more efficient as compared to its 4-phase counterpart, circuits for this scheme are usually larger due to the edge detection requirements of the protocol and at the storage level. On the other end of the coin, return-to-zero or level signaling 4-phase protocols use four signal transitions per datum transferred. Consequently, there is a large overhead in acknowledging each transaction, which makes it unwieldy for communication purposes. However, circuits adhering to this formula are smaller and easy to design. Generally speaking, circuits are designed using the 4-phase strategy and converted to 2-phase for transmission over long distances. Figures 2.4 and 2.5 show the waveforms for the two protocols.

#### 2.2.3 Relative Timing

This work uses relative timing (RT) [22] methodology as the sequencing technique for the design of all network components. The RT based design flow allows the designer to specify, characterize, and validate clockless elements using synchronous CAD tools. Instances of these characterized blocks can then be inserted in the regular VLSI CAD flow with some additional timing constraints. An RT constraint consists of a common timing reference called point-of-divergence, or pod, and a pair of events that are ordered in time for correct circuit operation called the point-of-convergence, or poc. A constraint is represented as pod  $\mapsto$  poc<sub>0</sub>+ $m \prec$  poc<sub>1</sub> where poc<sub>0</sub> must occur in time before poc<sub>1</sub> with margin m. Hence, the maximum path delay from pod to poc<sub>0</sub> must be less than the minimum path delay from pod to poc<sub>1</sub>. This is easily represented by two related design constraint equations set\_max\_delay and set\_min\_delay, which perform timing driven synthesis

that enforce the constraints on the logic paths. The complete RT design flow is represented in Figure 2.6

# 2.3 Networks-on-Chip

Traditional bus and point-to-point communication schemes do not scale well for *many-core* systems. To meet the aggressive performance specifications of most present-day applications, it is necessary to design a network that has suitable routing, flow control and topological schemes. On-chip networks differ from macroscale off-chip networks in several ways. On-chip networks are required to be light-weight due to the limited power and area budgets. Most of the communication latency of on-chip networks derives from router delay instead of wire delay since they span shorter distances. Therefore, router design plays an important role in the performance of the network. Also, NoC bandwidth is not limited by pin availability as in the case of off-chip networks. In this section, we discuss the various considerations that are factored in during the design of an on-chip network.

#### 2.3.1 Topology

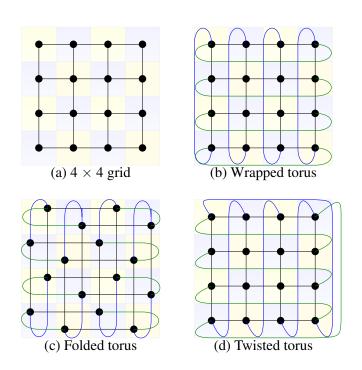

The network topology describes the arrangement and connection of various components of a network such as routers and links [23]. Direct topologies are defined as schemes where each router is connected to a node. Indirect topologies allow cases where intermediate routers are not connected to nodes. A hop is defined as a physical connection between neighboring routers. The topology of a network determines the number of hops required for a packet to travel from source to destination. The network diameter is the maximum number of hops required to traverse from one node to another such that the packet does not loop, backtrack, or detour; and is an important characteristic of the topology. Another important feature of the network is the path diversity, which is a count of the number of unique paths that exist between a pair of nodes. This is a key consideration when traffic load distribution and fault tolerance of a network are important. The network topology is decided based on these factors. Some examples of network topologies are shown in Figure 2.7.

## **2.3.2** Routing

The routing algorithm determines the path taken by the packet to travel from source to destination. If the path is fixed at the source, it is called *source routing*. *Destination routing* is when intermediate routers resolve the path based on the destination address. If multiple paths are available, routing algorithms choose the route based on optimizing a target metric, which can be hop count, latency, bandwidth, etc. Adaptive routing algorithms can change the paths for different packets traveling between a source-destination pair to balance load traffic, or to avoid deadlock. While employing adaptive routing, care must be taken that out-of-order packet arrival is accounted

for. In contrast, a deterministic route always uses the same link to go from a source to a destination. Care must be taken in this method to avoid deadlocks. Deadlock occurs when packets cannot progress further down the NoC due to a cyclic dependency of the shared resources (buffers and channels). In most topologies, deadlock can be avoided by restricting certain turns that can create cycles. X-Y dimension ordered routing is one such example.

#### 2.3.3 Flow Control

There are choices for the flow control as well. Circuit switching first sends out a probe to reserve channels along a path for a communication flow. After the sender receives word (ack) that the route is ready, it streams data freely without having to worry about contention or deadlock. After the entire message is transmitted, another signal is sent from the source to free the reserved links. This overhead of reservation and de-reservation is justified only when a large amount of data is transmitted. In **packet switching**, the packets are injected directly into the NoC and link allocation is performed on a hop-by-hop basis at the routers. In store-and-forward flow control, a router stores all flits of a packet before forwarding it to the next router. This increases the required buffer capacity of the router FIFO to accommodate the entire packet. In the virtual cut-through technique, storage and bandwidth requirements of the router remain the same, however flits can be forwarded before the entire packet has been received. Wormhole reduces the buffering capacity of input ports at the router to the flit granularity level. While this greatly reduces the size of the routers, wormhole flow control is susceptible to head-of-line blocking where a flit blocked at the head of the FIFO queue due to congestion also blocks the flits behind it, even when the routes associated with the blocked flits are not congested. If different flows have separate queues at the router, the head-of-line blocking can be avoided. This is called the virtual channel flow control, because separate channels appear to each flow, although only one physical channel exists.

#### 2.3.4 Simulators

Early forms of on-chip network simulators were usually single-threaded, which meant that their turn-around time was high. Unfortunately, this high run-time scales very poorly with the rising number of nodes in future exascale networks. The introduction of transaction level modeling (TLM) introduced the concept of function calls to model communication. Recent efforts have been focused on parallelizing NoC simulations using a multithreaded approach on highly parallel GPU architectures. One problem with these programs is the high synchronization cost incurred. Other efforts, based on workload decomposition have been proposed [24]. Full-system simulations provide a high degree of accuracy at the cost of higher run-time, by evaluating the correlation between the NoC and the applications. Sampling based approaches have been investigated where

a small sample is used to represent the entire application [25]. NoC simulators also need to take into account various choices in network design, such as topology, flow control, fault tolerance, etc. [26] Also, with use of unconventional links such as wireless, optical interconnect, and transmission lines, low level link accuracy gains further importance. Evidently, the problem of fast, reliable, accurate on-chip network simulators that can accommodate hundreds of nodes is a critical unsolved problem.

# 2.4 Summary

In this section, some background has been provided that will help in understanding the following chapters. It is highly recommended that the reader consult the references provided for the further understanding of some of the salient points in this chapter.

Figure 2.1: On-chip TL configurations

Figure 2.2: Reflection in transmission lines

Figure 2.3: GALS module

Figure 2.4: 2-phase protocol.

Figure 2.5: 4-phase protocol.

Figure 2.6: Simplified relative timing design flow

Figure 2.7: Regular network topologies

# **CHAPTER 3**

#### SOURCE ASYNCHRONOUS SIGNALING

In the absence of a universal timing scheme in clockless paradigms, the choice of the communication protocol carries high importance for functional correctness as well as performance. This chapter introduces a novel handshaking protocol that imparts the desirable throughput characteristics of a clocked scheme while maintaining the modularity of an asynchronous method.

## 3.1 Introduction

Latency down a communication link on an integrated circuit is dependent upon the resistance, capacitance, and current carrying capabilities of the wires. Each new process generation scales the technology down by reducing the cross sections of the wires while simultaneously placing them closer together. This increases the number of communication links in a fixed millimeter squared area of an integrated circuit. However it also modifies the signal carrying properties of the wire. In a scaled wire, capacitance remains about the same but resistance substantially increases due to the reduced cross sectional area. The increased resistance produces a relative increase in the communication latency down a fixed length of wire [27]. Increasing delay and energy properties on interconnect pose design challenges, particularly with global wires or network-on-chip interconnect.

Communication employing asynchronous handshake protocols is accomplished by sending data accompanied with validity information down a communication channel. Flow control is established by acknowledging the receipt of the data, thereby enabling the transmission of new data. The handshake signals are generated using pipelined control logic that implements the protocol and synchronize two adjacent channels. The frequency of communication is determined by the delay of the control logic plus the latency down the communication wires. Maximum operating frequency for any specific controller design is established when the pipelined controllers are physically adjacent to each other, as in a first-in first-out buffer (FIFO). Increasing distance between pipeline stages increases wire delay, and decreases the operating frequency of the system.

The direct consequence of wire latency is easily observed when employing asynchronous request acknowledge handshake-based communication. Every additional picosecond of wire delay

due to controllers being placed farther apart directly results in at least two picoseconds of degradation in the cycle time (1ps each for request and acknowledge). As the communication distance between control elements increases, the communication overhead increases, with a commensurate decrease in operating frequency and communication bandwidth. At some wire length, the communication delay eventually exceeds the desired performance target.

Traditional solutions to this problem reduce the impact of wire overhead. This is accomplished by employing two-cycle communication, which reduces the number of transient communications down the channel in half compared to four cycle protocols, and placing pipeline stages closer together, which reduces communication latency [28, 29, 30].

A new protocol called source asynchronous signaling (SAS) is provided for asynchronous handshake based communication. Rather than mitigate the wire overhead, this protocol is completely independent of wire delays. Thus the SAS link can achieve the same bandwidth as a traditional pipelined link shown in Figure 3.1. The SAS protocol therefore allows for high throughput asynchronous communication for channels with large wire latency. A method of implementing SAS is provided, and results are evaluated and compared against traditional protocols.

The SAS protocol decouples the request and acknowledge handshaking signals in such a way that multiple request operations may occur without an acknowledgment operation, and multiple acknowledgment operations may occur without an intervening request operation. Such communication by definition can not be delay insensitive as handshake events are not directly acknowledged. This results in a necessary set of relative timing constraints that must hold for the circuit to be functional as well as to perform at the desired bandwidth without stalling [22].

# 3.2 Background

This work builds on existing handshaking based communication protocols for data transfer. This section compares existing techniques and demonstrates the bridge to this work.

#### 3.2.1 Related Work

This work is similar to clocked "source synchronous" signaling [31]. We are aware of unpublished work as far back as the mid-1980s when Hewlett Packard began transmitting the clock along-with data between memory chips and microprocessor chips. This solved the problem of distributing low skew clocks in systems where data is transmitted over long distances. Similar properties exist today on a single die due to increasing wire delays and transistor counts. Thus, source synchronous signaling is relevant for today's system-on-chip and network-on-chip designs [32, 33, 34].

Clocked source synchronous signaling is challenging for two reasons: it creates timing relationships between the sender and receiver nodes, and it necessitates detailed evaluation of the signal carrying properties of the wires. Applying source synchronous concepts to asynchronous handshake protocols is no different; timing relationships and signal integrity become central issues. This work defines all timing constraints necessary for the SAS protocol as applied to the design presented in this work.

The topic of signal integrity is largely left as related work. However, due to its fundamental importance we briefly touch on key aspects related to SAS. A robust method of repeater deployment on long wires must be used to maintain linear wire delay, reduce variation, and maintain signal fidelity. The critical repeater distance is the maximum distance between line drivers that must be maintained to ensure linear delay and signal fidelity. In several 65nm technologies this distance is approximately 555  $\mu$ m. First order equations for communication latency and variation have been developed and validated against SPICE showing approximately 15% maximum error [30]. These models can be used to quickly estimate long communication link robustness to variation, energy, and latencies for any particular physical design configuration.

Since the SAS protocol is independent of wire delay, one can theoretically set channel frequencies to arbitrarily high values. Wave pipelining can result for very long wires and/or very high frequencies. In such cases multiple signals are concurrently in flight down a communication channel. Wave pipelining requires more care in physical design of the communication channel. However, multiple researchers have shown that high speed wave pipelined signaling is possible with proper engineering [35, 36, 37].

In order to put wave pipelining and signal integrity issues in perspective, consider our highest frequency network-on-chip design operating at 2.6 GHz in a 65nm process [38]. The delay in picoseconds of well managed interconnect for this process is modeled with the linear regression equation len/10 + 16, were len is the wire length in microns [39, 40]. This equates in the the network-on-chip router to the time-of-flight down a 3.69mm link. At that distance a skew of 150ps (a 39% variation) in either a delay-insensitive or bundled data protocol on a SAS channel still provides a very robust margin of 85ps.

Previous work defining a method for asynchronous handshake-based source synchronous signaling has been performed [41]. That work contains two channels, one for forward communication and one for backward communication, each with a FIFO. The design from [41] requires interface logic in order to connect traditional handshake protocols to the dual-channel internal protocol. The specifics of the internal channel protocol are not defined. In contrast, this work only contains a single channel, and no interface logic is required. The SAS channel protocol is formally defined.

One FIFO is placed at each end of the channel. FIFO sizes can be reduced to zero when cycle times are sufficiently large or wire delays sufficiently small. In such a condition the SAS protocol and provided implementation becomes equivalent to a traditional handshake channel. This base case is directly represented in our timing models when no SAS buffers are required.

## 3.2.2 Channel Properties

A channel consists of data, validity information identifying when the data are stable and may be sampled, backward flow control, and the controllers that implement the communication. Traditional handshake communication performance depends on the wire delays in the communication channel and the performance of the pipelined controllers. Data validity is provided by a separate req signal for bundled data channels or encoded in the data for delay insensitive channels. Backward flow control is normally provided with an ack signal. Handshake communication channels are characterized by (i) the channel protocol, (ii) the data encoding employed by the channel, (iii) how and when data are stored, (iv) the amount of concurrency implemented between adjacent channels, (v) the design of the controller that implements concurrency between channels, and clocking of the local storage elements.

Asynchronous channel protocols are very simple. Delay-insensitive channels forever repeat the sequence of a valid data encoding, ack, null data encoding, ack. Bundled data channels consist of a forever repeating req and ack events with the associated data relationship [42]. Channel protocols can take the form of a "return-to-zero" (RZ) or "four-phase" communication, or reduce the number of transitions by using "non-return-to-zero" (NRZ) or "two-phase" communication. There are many examples of different pipelined communication channels and their associated controllers in the literature. Any such controller that can be used to build FIFOs is a candidate and thus can be used in this design.

The SAS protocol introduces a new channel protocol, but otherwise supports all data encodings, data and control relationships, and concurrency between channels. The general design of the controller which interfaces between SAS channels and traditional handshake channels is provided herein. The design is based on FIFO structures with specific signal integrity and timing relationships that must hold. This paper demonstrates the SAS protocol using bundled data encoding. This encoding requires w+1 wires to encode w bits of data as well as a communication wire labeled ack to engineer the acknowledge handshaking. The SAS channel is described in this section using a two phase protocol.

#### 3.2.3 Channel bandwidth

Equations 3.1 to 3.3 represent the maximum communication bandwidth for clocked and traditional asynchronous handshake protocols. Variable w is the width of the data-path in terms of the number of data bits it carries, and delays are converted into frequencies by putting them in the denominator. The maximum bandwidth of a clocked design  $B_{clk}$  is proportional to the wire latency down a communication channel ( $L_c$ ) plus the setup time to the flip-flop (SU).  $B_2$  is the maximum bandwidth of a two phase communication protocol. It is proportional to the sum of  $C_{Or}$ , the request to acknowledgment responds time of the output channel, plus twice  $L_c$ . This is because in the two phase protocol, there is one transition each on the req and ack handshake signals. The maximum bandwidth of the four phase protocol  $B_4$  is proportional to twice the response time of the output channel  $C_{Or}$  plus four times the channel latency  $L_c$  due to the four required transitions on the handshake control signals.

$$B_{clk} = w/(L_c + SU) \tag{3.1}$$

$$B_2 = w/(2 \times L_c + C_{Or}) \tag{3.2}$$

$$B_4 = w/(4 \times L_c + 2 \times C_{Or}) \tag{3.3}$$

$$B_{SAS} = w/C_I \tag{3.4}$$

Assume delays  $L_c \gg (SU \approx C_{Or})$ , so that  $L_c$  is the dominant delay in the above equations, and that the clocked and asynchronous overheads (SU and  $C_{Or}$ ) are effectively identical. In such a case, the clocked design has approximately twice the maximum bandwidth of a two-cycle asynchronous design, and the two-cycle asynchronous design has approximately twice the bandwidth of a four-cycle asynchronous design. This two to four penalty factor for handshake communication can seriously hamper competitiveness in terms of performance, area, or power. SAS bandwidth (Equation 3.4) is only dependent on the input channel frequency and number of data bits. Now if  $C_I \approx L_c$  then the SAS channel operates at the same frequency as the clocked design. Thus the SAS protocol overcomes the communication disadvantage, but comes at the cost of adding timing constraints to the design.

# 3.3 Source Asynchronous Signaling

This section provides details on the novel SAS protocol.

#### 3.3.1 Protocol Specification

Figure 3.2 shows the formal representations of a bundled data NRZ SAS channel protocol with a buffer depth of two (n = 2) and a traditional bundled data NRZ handshake channel protocol. Each

protocol is represented as a petri-net and can be used as a specification for the traditional and SAS communication channels.

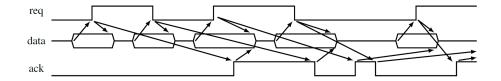

Figure 3.3 shows an example simulation of a two phase NRZ SAS communication channel where n=2. Rather than requiring that acknowledgment signal arrives before the next request signal, data transfer stalling is delayed by three ack transactions. This allows up to n+1 request transactions to occur before an acknowledgment transaction. As a result, the third data value becomes valid and the third req signal asserts indicating data validity, but flow control of the SAS Channel Protocol requires that the data remain valid and the third data transfer transaction does not complete until after the first acknowledge transaction (ack) occurs. Thus for the SAS channel communication protocol, the acknowledge flow control is shifted based on the number of data items n that can be buffered in the SAS sender and SAS receiver elements.

#### 3.3.2 Implementation of SAS Channel and Interfaces

SAS sender controllers interface a traditional channel protocol to the SAS Channel Protocol; SAS receiver controllers perform the dual operation. One can write a petri-net specification to synchronize a SAS channel and a traditional channel protocol in order to build SAS sender and receiver controllers. Our experiments synthesizing such specifications resulted in complex and slow designs. We then realized that the concurrency between the channels very closely mimics the behavior of a FIFO.

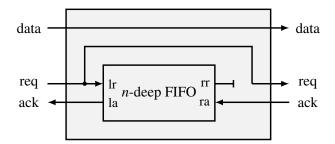

Figure 3.4 shows the block diagram representation of the bundled data SAS sender controller. The controller consists of an *n*-deep first-in first out (FIFO) that interfaces between a traditional handshake communication channel as an input and a SAS communication channel as the output. SAS controllers may use bundled data or delay-insensitive channels; however, this design does not work for GasP or single track communication.

The function of the FIFO is to record how many data transfers have occurred, and to not complete any transactions on the input channel that would exceed n transactions on the SAS communication channel. This is accomplished by implementing an n-deep FIFO to communicate between the traditional and the SAS communication channels. If n = 2, then two complete request acknowledge transactions can occur unimpeded on the input channel, and the corresponding data are sent down the SAS output channel. A third transaction may begin and the data transfer down the SAS communication channel would be initiated. However, the transaction would not complete until an acknowledge transaction occurs on the SAS communication channel. Since the depth of the FIFO is two, and two tokens have been placed in the FIFO, the third request transaction on the input port will not be acknowledged until an acknowledgment is received on the SAS channel.

Note that the data and the data validity information (req) on the traditional input channel are the same as the data and data validity information on the SAS communication channel. Other logic may be placed on these signals for various reasons such as to improve signal fidelity, delay the timing reference, change the data and timing encoding, or other standard modifications. The output request (rr) from the FIFO is left unconnected. This results in timing assumptions that must hold for the circuit to operate correctly. All transitions on the rr output of FIFO must occur before an associated response occurs on the acknowledge signal on the SAS channel that connects to the ra signal on the FIFO. This requires that the delay between edges on the ack signal is greater than the response time of FIFO.

The SAS sender element is not limited to bundled data protocols. Dual-rail, m-of-n, LEDR, or any other data encoding may be used in the channels and FIFOs. Likewise any type of asynchronous handshake controller that can implement a FIFO may be used so long as the design meets the SAS timing requirements imposed upon the design.

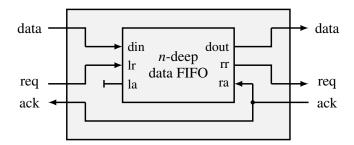

The SAS receiver controller is represented in Figure 3.5. This circuit is in many ways the dual of the SAS sender controller. This element contains a data FIFO that interfaces an input SAS communication channel with a traditional output asynchronous handshake channel. The input SAS channel and traditional output channel may use any data encoding, data transfer protocol, or protocol concurrency.

The function of the FIFO is to buffer and output the data received on the input SAS channel to the output channel. The size of the FIFO will be n, and this will be the same depth as the sender FIFO.

The acknowledge signal (ack) on the output handshake channel and the SAS communication channel are the same signal. The input acknowledgment (la) from the FIFO is left unconnected. This results in timing assumptions that must hold for the circuit to operate correctly. All transitions on the acknowledge signal la on the FIFO input must occur before the next transition on the req signal from the SAS communication channel. This requires that the delay between edges on the SAS Channel req signal is greater than the response time of the FIFO.

Figure 3.6 shows the block diagram of a complete SAS communication system with interfaces to traditional communication channels. The wires across the SAS Channel may be very long with substantial delay. Both the request and acknowledge timing signals across this channel are not directly acknowledged. Therefore, care must be taken to ensure that the fidelity of the signals and the relationship between the data and the timing signals hold across this channel. Repeaters will be inserted on the wires if they are longer than the critical repeater distance to ensure signal fidelity. Wave pipelining may occur on the SAS channel.

## 3.4 SAS Models

For a correctly designed SAS communication system, the maximum bandwidth  $B_{SAS}$  is expressed in Equation 3.4 where  $C_I$  is the cycle time of the channel. Note that this equation is strictly dependent upon the target data frequency to be sent down the channel, not upon wire delays as is the case with traditional communication channels as defined by Equations 3.2 and 3.3. Thus, the SAS channel provided can achieve wire overhead free communication down a long communication channel. However, for the SAS communication system to operate properly, a number of constraints must hold, which are now defined.

The forward and backward latency (Equations 3.7–3.10) of all FIFO designs are a function of the depth n of the FIFO. For linear FIFOs, the latency is n times the latency of each stage in the FIFO. Many designs exist that reduce the forward and backward latencies, such as parallel, tree and square configurations [43]. In these designs the latency is not calculated as n times latency per stage; rather there is a more complicated function to determine latency. For example, in an asynchronous tree FIFO, the latency is to the first order  $\log_2 n$  times the latency per stage [44]. For the latency values used in this document, the forward and backward latency values  $L_{bs}(n)$ ,  $L_{fR}(n)$ , and  $L_{bR}(n)$  for each FIFO calculate the first order approximation of the latency based on the FIFO design and structure which is a function of n.

| $L_{SAS}$    | Latency of a repeated wire down SAS Channel            | (3.5)  |

|--------------|--------------------------------------------------------|--------|

| n            | Depth of sender/receiver FIFOs                         | (3.6)  |

| $L_{f_S}(n)$ | Forward latency of sender FIFO as a function of $n$    | (3.7)  |

| $L_{b_S}(n)$ | Backward latency of sender FIFO as a function of $n$   | (3.8)  |

| $L_{f_R}(n)$ | Forward latency of receiver FIFO as a function of $n$  | (3.9)  |

| $L_{b_R}(n)$ | Backward latency of receiver FIFO as a function of $n$ | (3.10) |

| $C_I$        | Minimum cycle time of the input channel                | (3.11) |

| $C_O$        | Minimum cycle time of the output channel               | (3.12) |

| $C_{Or}$     | Output channel req-to-ack response time                | (3.13) |

| $C_{Sf}$     | Maximum cycle time of SAS sender FIFO                  | (3.14) |

| $C_{Rf}$     | Maximum cycle time of SAS receiver FIFO                | (3.15) |

Overhead free communication only occurs when the channel operates at frequency  $1/C_I$  without stalling. A few fundamental conditions must hold for this to be the case based on the above variables.

$$C_I \ge C_O \ge C_{Sf}, C_{Rf} \tag{3.16}$$