## A Framework for Automated HW/SW Co-Verification of SystemC Designs using Timed Automata

vorgelegt von

Diplom-Ingenieur

Paula Herber

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

### **Promotionsausschuss:**

Vorsitzender: Prof. Dr. Ben Juurlink

Berichtende: Prof. Dr. Sabine Glesner

Berichtender: Prof. Dr. Rolf Drechsler

**Tag der wissenschaftlichen Aussprache:** 25. Februar 2010

Berlin 2010

### **Abstract**

Embedded systems are usually composed of deeply integrated hardware and software components. They are often used in domains where a failure results in high financial losses or even in serious injury or death. As a consequence, it is indispensable to ensure the correctness of the digital components that control these systems with systematic and comprehensive verification techniques. To model and simulate complex HW/SW systems, the system level design language SystemC is widely used. However, the co-verification techniques used for SystemC are mostly ad-hoc and non-systematic. With that, it is either very expensive to verify a given design, or the results are not reliable.

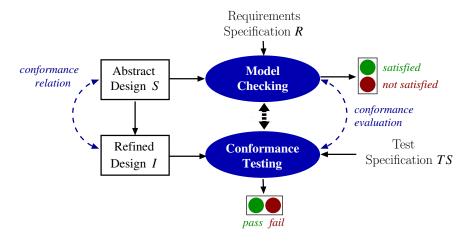

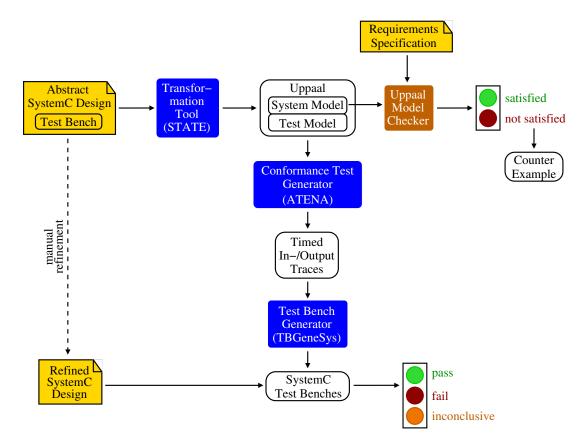

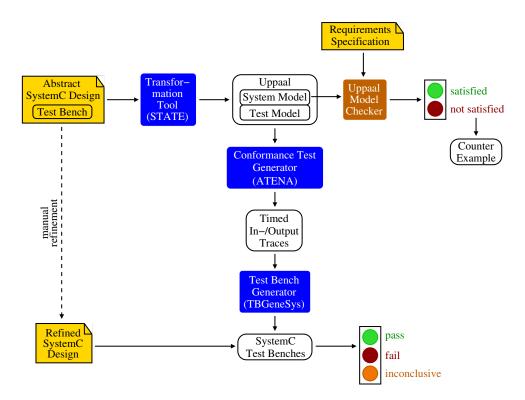

In this thesis, we present an approach to overcome this problem by a systematic, comprehensive, and formally founded quality assurance process, which allows automated co-verification of digital HW/SW systems that are modeled in SystemC. The main idea is to apply model checking to verify that an abstract design meets a requirements specification and to generate conformance tests to check whether refined designs conform to this abstract design. With that, we obtain guarantees about the abstract design, which serves as a specification, and we can ensure the consistency of each refined design to that. The result is a HW/SW co-verification flow that supports the HW/SW co-development process continuously from abstract design down to the final implementation.

To establish a formal basis for our HW/SW co-verification approach, we define a formal semantics for SystemC. To this end, we present a mapping from SystemC to UPPAAL timed automata, which have a formally well-defined semantics. Using this mapping, we can automatically transform a given SystemC design into a semantically equivalent UPPAAL model. Furthermore, the resulting UPPAAL model allows the application of the UPPAAL model checker. With that, we can verify important properties of a SystemC design fully automatically, for example, liveness, safety, or the compliance with timing constraints. These properties are guaranteed for all possible input scenarios.

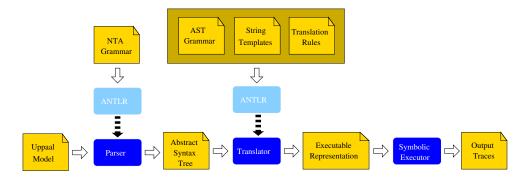

In addition to the formal semantics that allows model checking, we present a novel test algorithm for SystemC. The algorithm uses the UPPAAL model of a given high-level SystemC design to generate conformance tests for lower abstraction levels. Existing algorithms for the generation of conformance tests from timed automata models either support only deterministic subclasses of timed automata or compute expected results *online* during the test execution. The first is inacceptable because SystemC designs are inherently non-deterministic. The latter makes it impossible to reuse the conformance tests in multiple refinement steps. The algorithm presented in this thesis generates conformance tests offline and it can cope with non-deterministic systems. The result is a set of SystemC test benches that can be used to check automatically whether a refined design conforms to a given abstract design.

Together with our model checking approach for abstract SystemC designs, we obtain a framework for the automated HW/SW co-Verification of SystemC designs using Timed Automata (VeriSTA). The framework is fully automatically applicable and continuously supports the whole HW/SW co-design process. We implemented the complete VeriSTA framework and demonstrate its performance and its error detecting capability with experimental results.

### Zusammenfassung

Eingebettete Systeme sind in der heutigen Welt allgegenwärtig. Sie werden zunehmend auch in Bereichen eingesetzt, in denen ein Fehler zu hohen finanziellen Verlusten oder sogar zu Verletzungen und Todesfällen führen kann, zum Beispiel im Automobilbereich. Als Folge davon wird es immer wichtiger, die Korrektheit eingebetteter Systeme mit systematischen und umfassenden Verifikationstechniken sicher zu stellen. Eine besondere Herausforderung ist dabei, dass in eingebetteten Systemen Hardware- und Software-Anteile eng miteinander verflochten sind. Um solche heterogenen Systeme zu modellieren und zu simulieren wird häufig die Systembeschreibungssprache SystemC eingesetzt. Die Verifikationstechniken, die für SystemC eingesetzt werden, sind jedoch überwiegend ad hoc und unsystematisch. Die Verifikation ist daher entweder sehr teuer oder die Ergebnisse sind nicht zuverlässig.

In dieser Arbeit stellen wir einen Ansatz zur Lösung dieses Problems vor. Wir präsentieren einen systematischen, umfassenden und formal fundierten Qualitätssicherungsprozess, der die HW/SW Co-Verifikation durchgängig über den gesamten Entwurfsprozess ermöglicht. Die übergeordnete Idee ist, eine Kombination von Model Checking und Konformitätstesten anzuwenden. Model Checking verwenden wir um zu zeigen, dass ein abstrakter Entwurf eine gegebene Anforderungsspezifikation erfüllt. Anschließend erzeugen wir Konformitätstests um zu prüfen, ob ein verfeinerter Entwurf konform zu diesem abstrakten Entwurf ist. Mit diesem Ansatz erhalten wir Garantien über bestimmte Eigenschaften des abstrakten Entwurfs und stellen gleichzeitig die Konsistenz verfeinerter Entwürfe über den Entwurfsablauf hinweg sicher. Das Ergebnis ist ein Qualitätssicherungsprozess, der den Entwicklungsprozess von der abstrakten Spezifikation bis zur finalen Implementierung unterstützt.

Um eine formale Basis für unseren Ansatz zu etablieren, definieren wir eine formale Semantik für SystemC. Zu diesem Zweck bilden wir die informell definierte Semantik von SystemC auf die formal wohl-definierte Semantik von UPPAAL Timed Automata ab. Basierend auf dieser Abbildung können wir einen gegebenen SystemC Entwurf automatisch in ein semantisch äquivalentes UPPAAL Modell transformieren. Dies ermöglicht auch die Anwendung des UPPAAL Model Checkers. Damit können wir wichtige Eigenschaften, zum Beispiel Lebendigkeit, Sicherheit oder die Einhaltung von Zeitschranken, vollautomatisch verifizieren. Neben dem Model Checking bildet die von uns definierte formale Semantik für SystemC auch eine Basis für Konformitätstests. stellen einen Algorithmus vor, der aus einem abstrakten Modell alle möglichen (zeitbehafteten) Ausgaben berechnet und aus diesen automatisch SystemC Test Benches erzeugt. Diese können einen beliebigen verfeinerten Entwurf ausführen und automatisch prüfen, ob die Ausgaben dieses Entwurfs in der Spezifikation erlaubt sind oder nicht, also ob der verfeinerte Entwurf konform zum abstrakten Enwturf ist.

Mit der Kombination aus Model Checking und Konformitätstesten erhalten wir ein Framework für die automatisierte HW/SW Co-Verifikation von SystemC Entwürfen mit Hilfe von Timed Automata (VeriSTA). Das Framework ist voll-automatisch anwendbar und unterstützt den gesamten HW/SW Co-Design Prozess. Wir haben das VeriSTA Framework vollständig umgesetzt und demonstrieren seine Leistungsfähigkeit mit experimentellen Ergebnissen.

### **Danksagung**

Die vorliegende Arbeit entstand während meiner Tätigkeit als wissenschaftliche Mitarbeiterin im Fachgebiet "Programmierung eingebetteter Systeme" unter der Leitung von Prof. Dr. Sabine Glesner. Bei ihr möchte ich mich ganz besonders bedanken. Sie hat mich immer aus vollem Herzen unterstützt und mir sehr viel beigebracht. Ohne sie wäre die Arbeit so nicht zustande gekommen. Ebenfalls sehr dankbar bin ich meinem Zweitgutachter Prof. Dr. Rolf Drechsler für seine freundliche Unterstützung, seine oft auch sehr kurzfristige Hilfe und seine wertvollen Anmerkungen.

Neben den Gutachtern gibt es noch zwei Personen, die ganz besonders zum Gelingen dieser Arbeit beigetragen haben: meine Kollegen und Freunde Lars Alvincz und Thomas Göthel. Ich danke euch sehr für all die inhaltlichen Diskussionen, wiederholtes Korrekturlesen und dass ihr immer für mich da wart. Ganz herzlich danke ich auch meinen Diplomanden Joachim Fellmuth, Florian Friedemann und Marcel Pockrandt danken, die sehr viel zur Umsetzung der Arbeit beigetragen haben. Allen meinen Kollegen möchte ich danken für viele hilfreiche Diskussionen und für die angenehme Atmosphäre in unserer Gruppe, in der man einfach gern zur Arbeit kommt und für alles einen Ansprechpartner findet.

Zuletzt möchte ich meiner Familie, all meinen Freunden und den Hausmädels für ihre Unterstützung danken, insbesondere meinem Freund Kaspar Scholemann und meinen Eltern, Hille Herber und Norbert Thiery-Herber. Es hat mir sehr geholfen dass ihr mir immer zugehört und mir immer wieder gute Laune gemacht habt.

### **Contents**

| 1 | Intr | oductio | on                               | 13 |

|---|------|---------|----------------------------------|----|

|   | 1.1  | Proble  | em                               | 13 |

|   | 1.2  | Objec   | tives                            | 14 |

|   | 1.3  | Propo   | sed Solution                     | 15 |

|   | 1.4  | Motiv   | ation                            | 17 |

|   | 1.5  | Resear  | rch Area                         | 18 |

|   | 1.6  | Main    | Contributions                    | 18 |

|   | 1.7  | Outlin  | ne                               | 19 |

| 2 | Bac  | kgroun  | ıd                               | 21 |

|   | 2.1  | HW/S    | SW Co-Design                     | 21 |

|   |      | 2.1.1   | Design Flow                      | 22 |

|   |      | 2.1.2   | Transaction Level Modeling       | 24 |

|   | 2.2  | HW/S    | W Co-Verification                |    |

|   |      | 2.2.1   | Input Selection                  | 27 |

|   |      | 2.2.2   | Co-Simulation                    | 29 |

|   |      | 2.2.3   | Evaluation of Simulation Results | 29 |

|   | 2.3  | Verific | cation and Validation Techniques | 30 |

|   |      | 2.3.1   | Preliminaries                    | 31 |

|   |      | 2.3.2   | Model Checking                   | 32 |

|   |      | 2.3.3   | Conformance Testing              | 35 |

|   | 2.4  | Syster  | mC                               | 36 |

|   |      | 2.4.1   | Structural Modeling              | 38 |

|   |      | 2.4.2   | Behavioral Modeling              | 42 |

|   |      | 2.4.3   | Simulation Semantics             | 44 |

10 Contents

|   | 2.5  | UPPAAL Timed Automata                       | 45  |

|---|------|---------------------------------------------|-----|

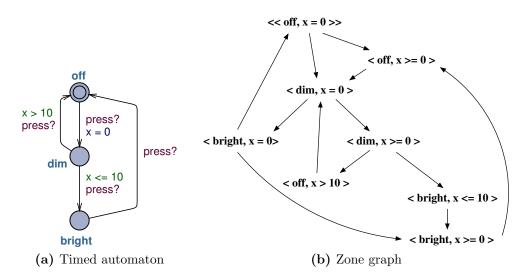

|   |      | 2.5.1 Timed Automata                        | 46  |

|   |      | 2.5.2 Networks of Timed Automata            | 48  |

|   |      | 2.5.3 Symbolic Semantics of Timed Automata  | 48  |

|   |      | 2.5.4 Difference Bound Matrices             | 51  |

|   |      | 2.5.5 Uppaal                                | 52  |

|   | 2.6  | Summary                                     | 55  |

| 3 | Rela | ted Work                                    | 57  |

|   | 3.1  | Formal Verification of SystemC Designs      | 57  |

|   | 3.2  | Test Generation for SystemC Designs         | 60  |

|   | 3.3  | Conformance Testing using Timed Automata    | 61  |

|   | 3.4  | Summary                                     | 62  |

| 4 | Qua  | lity Assurance Approach                     | 63  |

|   | 4.1  | Combining Model Checking and Testing        | 63  |

|   | 4.2  | HW/SW Co-Verification Framework VeriSTA     | 66  |

| 5 | Fori | nal Semantics for SystemC                   | 69  |

|   | 5.1  | Assumptions                                 | 70  |

|   | 5.2  | Representation of SystemC Designs in UPPAAL | 70  |

|   | 5.3  | Design Transformation                       | 71  |

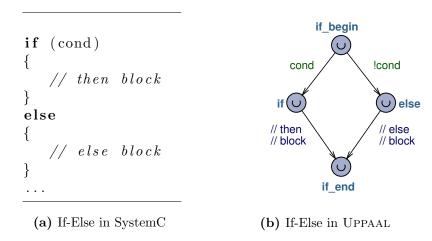

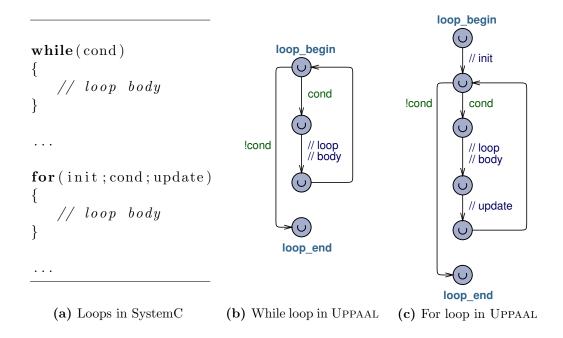

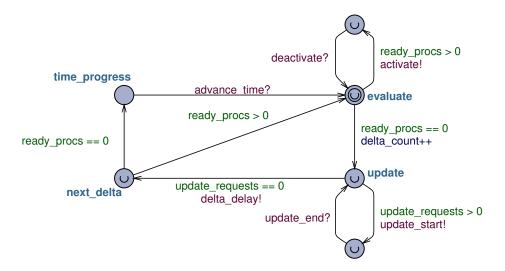

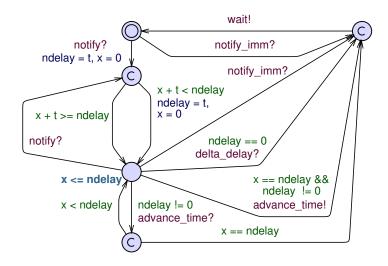

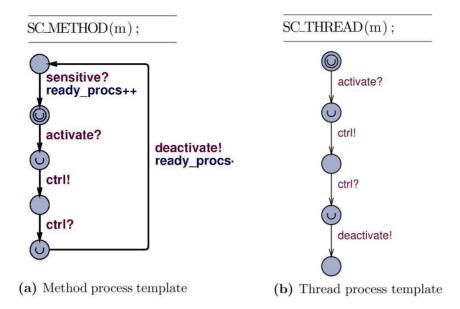

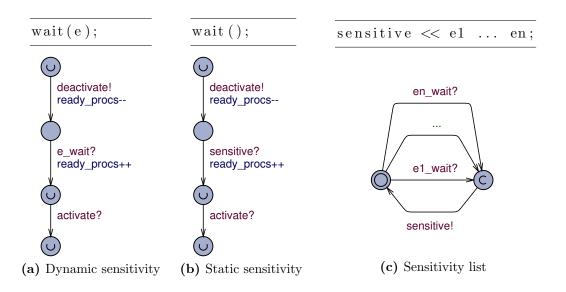

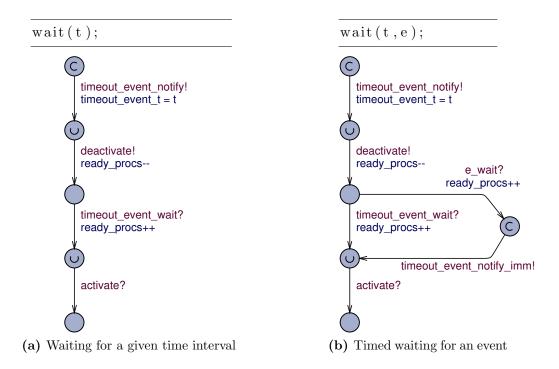

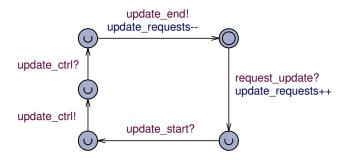

|   |      | 5.3.1 Method Transformation                 | 72  |

|   |      | 5.3.2 Concurrency and Communication         | 77  |

|   |      | 5.3.3 Channels and Modules                  | 82  |

|   |      | 5.3.4 Instantiation and Binding             | 83  |

|   | 5.4  | Model Checking SystemC Designs              | 84  |

| 6 | Con  | formance Testing                            | 85  |

|   | 6.1  | Test Setting                                | 86  |

|   | 6.2  | Symbolic Semantics of Uppaal Timed Automata | 87  |

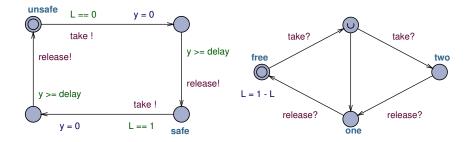

|   | 6.3  | Conformance Relation                        | 90  |

|   | 6.4  | Conformance Test Generation                 | 93  |

|   |      | 6.4.1 Basic Algorithm                       | 93  |

|   |      | 6.4.2 Computation of Successor States       | 95  |

|   |      | 6.4.3 Optimizations                         |     |

|   | 6.5  | Test Bench Generation                       | 102 |

|   | 6.6  | Automated Conformance Evaluation            | 104 |

Contents 11

| 7   | lmp   | lementation 1                               | .07 |

|-----|-------|---------------------------------------------|-----|

|     | 7.1   | STATE                                       | 108 |

|     | 7.2   | ATENA                                       | 111 |

|     | 7.3   | TBGeneSys                                   | 113 |

| 8   | Ехр   | erimental Results 1                         | 15  |

|     | 8.1   | Case Studies                                | 115 |

|     | 8.2   | Performance Evaluation                      | 118 |

|     |       | 8.2.1 Transformation from SystemC to UPPAAL | 118 |

|     |       | 8.2.2 Model Checking                        | 118 |

|     |       | 8.2.3 Conformance Test Generation           | 121 |

|     | 8.3   | Error Detecting Capability                  | 123 |

|     | 8.4   | Summary                                     | 124 |

| 9   | Con   | nclusion 1                                  | 27  |

|     | 9.1   | Results                                     | 127 |

|     | 9.2   | Discussion                                  | 129 |

|     | 9.3   | Outlook                                     | 130 |

| Lis | st of | Figures 1                                   | 33  |

| Lis | st of | Listings 1                                  | 36  |

| Lis | st of | Tables 1                                    | 37  |

| Bi  | bliog | raphy 1                                     | 39  |

## 1 Introduction

Embedded systems are usually composed of deeply integrated hardware and software components, and they are developed under severe resource limitations and high quality requirements. In connection with the steadily increasing demands on multi-functioning and flexibility, the analog control components are more and more replaced by complex digital HW/SW systems. To meet the high quality standards and to satisfy the rising quantitative demands, the automatization of quality assurance processes for such systems is gaining more and more importance. A major challenge is to develop *automated* quality assurance techniques that can be used for the integrated verification of complex digital HW/SW systems.

### 1.1 Problem

SystemC [IEE05] is a system level design language that supports design space exploration and performance evaluation efficiently throughout the whole design process even for large and complex HW/SW systems, and thus it is widely used in HW/SW co-design. SystemC allows the description of both hardware and software, and the designs are executable on different levels of abstraction. As a consequence, co-simulation, i.e., the simultaneous execution of hardware and software, can be used for validation and verification throughout the whole design process. For quality assurance, however, simulation is necessary but not sufficient. This has three reasons: First, simulation is incomplete. It can neither be applied to all possible input scenarios (in particular for real-time and non-terminating systems), nor can it be assured that all possible executions are covered in the case of non-deterministic systems. Second, although HW/SW co-designs are developed in a refinement process where an abstract design is stepwise refined to the final implementation, it is very difficult to ensure consistency between different abstraction levels, or to reuse verification results in later development stages. Third, simulation alone is not sufficient for a systematic and comprehensive quality assurance approach because the degree of automation is limited. The evaluation of simulation results has to be done manually by the designer, e.g., by inserting assertions about the expected behavior all over the design.

14 Introduction

### 1.2 Objectives

The aim of this thesis is to establish a framework for the automated HW/SW co-verification of SystemC designs. We require the framework to fulfill the following criteria:

- 1. The proposed co-verification techniques must be suitable for both hardware and software parts of a given digital control system, and they have to be able to cope with the main co-design concepts, namely concurrency, time, reactivity, hierarchical modeling and abstract communication. Due to the implementation of concurrency in the SystemC scheduler, this includes the requirement to support non-deterministic system designs.

- 2. The quality assurance process should be comprehensive and *continuous*, i. e., it should support the complete system design flow from an abstract design down to the final implementation. In particular, we want to ensure consistency between different abstraction levels in a refinement process and to reuse verification results from high abstraction levels on lower abstraction levels.

- 3. We require the co-verification techniques used in the proposed framework to be automatically applicable and efficient. To give evidence for that, the framework should be completely implemented. It should be applied to case studies that demonstrate its efficiency in terms of performance and of error detecting capability.

A vital precondition for automated verification techniques is a formal semantics for SystemC. This is due to the fact that automated verification techniques require a clear and unique understanding of how to interpret a given design or model. Unfortunately, the semantics of SystemC is only defined *informally* in [IEE05]. As a consequence, we derive as a subgoal that we have to address the problem of defining a formal semantics for SystemC. We require our formal semantics to fulfill the following criteria:

- (i) The behavioral semantics of SystemC informally defined in [IEE05] must be completely preserved.

- (ii) To maintain comprehensibility, the structure of a given SystemC design has to be preserved.

- (iii) We want the formal model of a given SystemC design to be generated automatically.

- (iv) The formal semantics must be suitable for automated verification.

- (v) For debugging purposes, there should be tool support to edit, visualize and simulate the formal model of a given SystemC design.

### 1.3 Proposed Solution

To achieve the objectives defined above, we propose a quality assurance process based on a combination of model checking and conformance testing. We assume that the HW/SW co-design process starts with an abstract design that is stepwise refined down to the final implementation. We propose to use model checking to verify that the abstract design meets its requirements, and to generate conformance tests to verify that refined models or the final implementation conform to the abstract model. This approach yields a formally founded and comprehensive assurance process that

- continuously supports the HW/SW co-design flow throughout the whole design process,

- ensures consistency between different development stages,

- allows reusing verification results and

- has the potential to be fully automatically applicable.

Model checking is an automatic verification technique. With model checking, it can be proven that a model of a finite-state concurrent system (described by a system specification) fulfills certain requirements. In contrast to simulation or testing, model checking is *complete*, i. e., it covers all possible input scenarios and all possible execution paths. With that, it is possible to *guarantee* important properties such as liveness, safety and compliance with timing constraints. The precondition for the application of model checking is a formal model of the specification. In our approach, the specification is given as an abstract SystemC design, whose semantics is only informally defined.

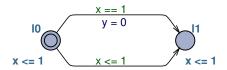

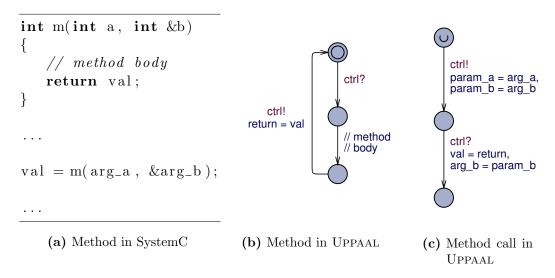

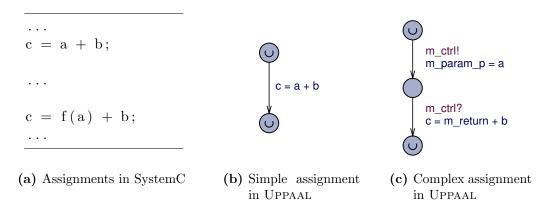

To obtain a formal semantics for SystemC designs, as required for the automatization of verification techniques, we propose to map the semantics of SystemC to the formally well-defined semantics of UPPAAL timed automata [BLL<sup>+</sup>95]. Using this mapping, we present an approach to automatically translate a given SystemC design into a semantically equivalent UPPAAL model. This allows the application of the UPPAAL model checker to verify safety, liveness and timing properties. Furthermore, UPPAAL timed automata have the expressiveness to represent most of the SystemC language constructs and execution semantics. The only exceptions are dynamic process and object creation and the restriction that only bounded integer data variables are used. As we will see, these are minor restrictions. More important is that interactions between parallel processes, including dynamic sensitivity and timing behavior, can be naturally modeled. Compared to other state based modeling languages, UPPAAL is especially well-suited to model and to verify timing behavior. This is vital because system designs often contain synchronous hardware and asynchronous software. In both the SystemC design and the UPPAAL model, systems are regarded as networks of communicating processes. In our transformation approach, we map SystemC processes to UPPAAL processes. The execution of these processes is controlled by a timed automaton that models the SystemC scheduler. We use parameterized timed automata for events and for primitive channels. The timed automata modeling SystemC 16 Introduction

processes, events, channels and the scheduler are synchronized by UPPAAL channels. All automata that are necessary to represent a given design are generated separately and composed into a system using the UPPAAL template mechanism. This makes the generation process highly scalable and the generated UPPAAL model compact, comprehensible, and flexible towards design evolution. To ensure the correctness of the transformation, we first ensure that the transformation of SystemC processes into timed automata processes preserves their informally defined behavior. Second, we ensure that the semantics of interactions between processes is preserved. The resulting transformation from SystemC to UPPAAL preserves the informally defined semantics of SystemC and the structure of a given design, can be applied fully automatically, and yields direct access to the UPPAAL model checker.

The aim of conformance testing is to determine whether an implementation of a system conforms to its specification. To this end, it is necessary to define the notion of *conformance* precisely. In formal testing theory, this is defined by a formal *implementation relation*. Widely used and well-established in the context of model-based testing of labeled transition systems is the *input* output conformance (ioco) relation introduced by Tretmans [Tre96]. Based on the *ioco* relation it is possible to evaluate test results automatically by comparing the outputs of the implementation with those of the specification. If the implementation sends an output that is not foreseen by the specification, the test verdict is fail. If the implementation sends all expected outputs for a given input trace, the test verdict is pass. The automatic generation of conformance tests based on the *ioco* relation consists of the computation of all possible outputs of the specification for a given input trace. The resulting set of expected output traces can then be used as a test oracle. This allows the automated evaluation of test executions by comparing the output traces produced by the implementation with the expected ones.

The main challenge in the generation of conformance tests for SystemC designs is that they are inherently non-deterministic due to the semantics of the SystemC scheduler defined in [IEE05]. Furthermore, SystemC designs are usually developed in several refinement steps. Thus, it is desirable to have test cases that can be applied repeatedly in each refinement step. As a consequence, we require our conformance test generation approach to meet two important requirements: First, it should be applicable to non-deterministic systems, and second, the expected simulation or test results should be computed offline, such that they can be easily reused in later development stages. To generate conformance tests under these requirements, we first use our mapping from SystemC to UPPAAL to translate an abstract SystemC design into a semantically equivalent UPPAAL model. Then, we use the UPPAAL model to statically compute all possible output traces for a given test suite consisting of a set of input traces. When the test suite is executed on a refined design or on the final implementation, we can compare the output traces produced by the refined design with the output traces computed from the UPPAAL model of the abstract design. To decide whether the refined design conforms to the abstract design, we use the relativized timed input/output conformance (rtioco) relation presented by Larsen et al. [LMN05]. Based on that, we can use the 1.4 Motivation 17

output traces from the UPPAAL model as a *test oracle* to test the conformance of the refined designs to the abstract design fully automatically.

### 1.4 Motivation

Embedded systems are ubiquitous in today's everyday life. They help us making breakfast, buying a ticket at the ticket machine, and provide daily entertainment with radios, DVD players, TVs and video games. However, these applications are only the tip of the iceberg. On top of that, we also confide our lives to embedded systems which control our cars, trains and airplanes, traffic lights, and medical equipment. The latter class of embedded systems is a particularly severe challenge for their engineers, as they move between the conflicting priorities of safety, performance, and resource requirements. A field where those conflicting priorities are extremely hard to reconcile is the automotive sector. Automotive systems are safety-critical, as their failure may result in death or serious injury, the resource limitations are rigorous due to large quantities of production and the high cost pressure. At the same time, the quantity of digital hardware and software is heavily increasing, and already accounts for up to 30% of the overall cost of a car [Bro05].

To achieve design solutions with maximal performance at minimal cost, it is indispensable to explore the whole design space. In an application area where hardware and software persistently interact with each other and are to a great extent interchangeable, this requires an integrated design methodology. The demand for such an integrated design methodology has led to the idea of HW/SW co-design. In HW/SW co-design, a detailed high-level description of the complete behavior is made prior to design selection and HW/SW partitioning. This behavioral description then serves as an input to an optimization procedure that uses performance estimations to select the overall design and partitioning. This allows the evaluation of different design alternatives, and at the same time leads to an early consideration of HW/SW interfaces and thereby eases system integration. While co-design techniques have become comparatively mature, not least due to the development of powerful languages for the design of digital HW/SW systems such as SystemC and SystemVerilog, co-verification techniques still lack to keep pace with the advancements. In particular, the degree of automatization of co-verification techniques is limited. Although co-designs have become executable on different abstraction levels, and co-simulation is extensively used in every design stage, simulation results are still evaluated manually or semi-automatically by inserting assertions about the expected behavior all over the design. Although the concept of HW/SW co-design requires a behavioral abstract description of the system that serves as a specification for the following refinement steps, this description is still not used to automatically assure quality and conformance of subsequently developed designs. On top of that, the techniques to ensure the quality of the behavioral description are also premature and insufficiently automated, at least in case of a timed description. Together, this makes HW/SW co-verification an expensive, time-consuming, and error-prone task.

18 Introduction

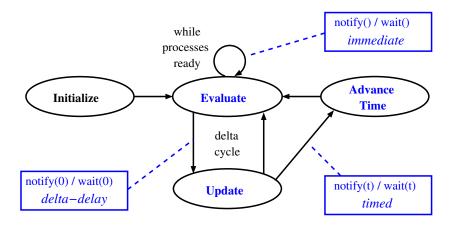

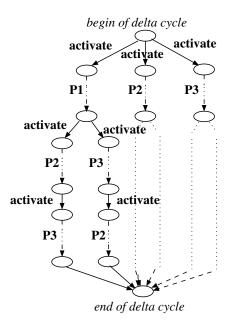

With this thesis, we contribute to this field with a framework for automated HW/SW co-verification of digital SystemC designs. Our approach allows both the automated verification of a given high-level design as well as the automated evaluation of the conformance of refined designs to the abstract design throughout the whole design process. SystemC became our language of choice because it permits to use a single language for specification, architectural analysis, test benches, and behavioral design. SystemC provides all of the substantial concepts of HW/SW co-design languages, such as concurrency simulation based on delta-cycles, time, reactivity, hierarchical modeling and abstract communication. With a solution that can cope with all of this, we are confident that our approach can also be transferred to other co-design languages (such as SystemVerilog).

### 1.5 Research Area

The issue of HW/SW co-verification establishes a point of intersection of many research areas. HW/SW co-design taken by itself is already an interdisciplinary field, which brings together the hardware world and the software world, communication and network experts, mechatronics and control engineers, and many others. HW/SW co-verification adds the dimension of topics connected with quality assurance. Analysis techniques, formal verification, testing and simulation can all be made applicable to co-verification with appropriate adaptations. Furthermore, the very different techniques from the area of hardware verification have to be combined with those from the area of software verification. For this thesis, the main research areas in which it is embedded are HW/SW co-design, formal verification, and testing. With respect to HW/SW co-design, we use current research results from system level design, transaction level modeling, and HW/SW co-simulation. With respect to formal verification, the relevant research fields can be narrowed to model checking, formal specification and semantic-preserving transformations. In the field of testing, our work can be classified as research belonging to the areas of conformance testing, in particular input/output conformance testing, black-box testing, real-time testing, and automated test generation.

### 1.6 Main Contributions

The main contributions of this thesis are:

■ A formally founded and comprehensive HW/SW co-verification process for digital HW/SW systems modeled in SystemC, which continuously supports the HW/SW co-design flow throughout the whole design process. The proposed process is based on a combination of model checking and conformance testing, ensures consistency between different development stages, allows reusing verification results and is fully automatable. We published this approach in [HFG09, Her10].

1.7 Outline 19

■ A formal semantics for SystemC that is defined by a mapping from SystemC to UPPAAL timed automata. This allows the application of the UPPAAL model checker to verify that an abstract SystemC design meets its requirements. In particular, a given SystemC design can be automatically translated into a semantically equivalent UPPAAL timed automata model. This exempts the designer from the time-consuming and error-prone task of developing a formal specification manually. We published this approach for model checking SystemC designs in [HFG08].

- An algorithm for offline conformance test generation for SystemC designs. The algorithm uses a UPPAAL model, which was automatically generated from a high-level SystemC design, to compute all possible output traces. SystemC designs are non-deterministic. We mitigate the state space explosion problem by exploiting specifics of the SystemC semantics to drastically reduce the number of states that have to be kept in memory. From the resulting output traces, we generate SystemC test benches that evaluate the conformance of a given low-level design fully automatically. We published the basic algorithm in [HFG09].

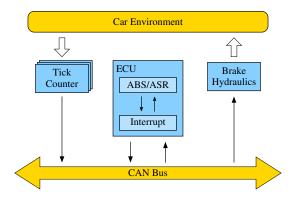

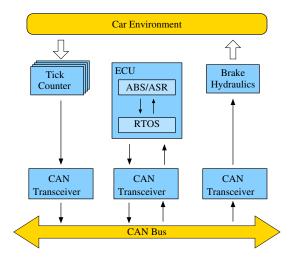

- A Framework for Automated HW/SW Co-Verification of System C designs using Timed Automata (VeriSTA), which shows the applicability of our approach. With an Anti-Slip Regulation and Anti-lock Braking System (ABS/ASR) as case study, we demonstrate that the complete framework can be applied fully automatically to digital HW/SW systems. Using the ABS/ASR example, we furthermore demonstrate both the efficiency and error detecting capability of our framework.

### 1.7 Outline

This thesis is structured as follows: In Chapter 2, we give an introduction to HW/SW co-design and co-verification, to model checking and conformance testing, and to SystemC and UPPAAL. Then, in Chapter 3, we review related work on HW/SW co-verification, in particular approaches that target SystemC, and related work on conformance testing for timed systems, in particular for UPPAAL. In Chapter 4, we present our approach for a comprehensive and continuous quality assurance of digital System C designs. The proposed quality assurance process is based on a combination of model checking and testing. In Chapter 5, we present our approach to transform a given SystemC design into a semantically equivalent UPPAAL model, which can then be verified using the UPPAAL model checker. In Chapter 6, we present our approach for automated conformance test generation and conformance evaluation for SystemC designs. To show the practical applicability of our approach, we have implemented the complete VeriSTA framework and applied it to three case studies. In particular, we use an Anti-Slip Regulation and Anti-lock Braking System to demonstrate both the performance of the framework and its error detecting capability. The main characteristics of the implementation are summarized in Chapter 7. The experimental results are presented in Chapter 8. We conclude in Chapter 9 and give an outlook on further research topics.

In this chapter, we give a brief introduction to the main topics that are connected to this thesis. First, we introduce the concepts of HW/SW co-design. To this end, we describe the HW/SW co-design flow and the idea of transaction level modeling. Second, we identify the main challenges in HW/SW co-verification and review common co-verification practice. Then, we give a general overview over verification and validation techniques and define some important terms we use in this thesis. We also introduce the verification techniques that are most relevant for our approach, namely model checking and conformance testing. Finally, we introduce the two languages that are in the center of our approach for automated HW/SW co-verification, i. e., the system level design language SystemC and the formal modeling language UPPAAL timed automata.

### 2.1 HW/SW Co-Design

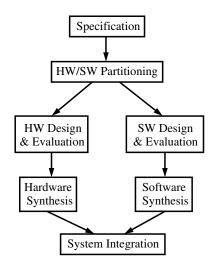

Embedded systems are usually composed of deeply integrated hardware and software components. In some systems the hardware part is fixed, but the increasing demands on performance and quality requires more and more that the hardware fulfills very special requirements and that it is precisely adjusted to the embedded software. As a consequence, it is often no longer sufficient to use prefabricated hardware components. When dedicated hardware has to be developed for an embedded system, the development of the embedded software depends on the progress in hardware development. The classical design flow for such hardware/software systems is shown in Figure 2.1. It starts with an abstract specification, e.g., the algorithm or another functional description of the desired system behavior. The specification is then partitioned into hardware and software modules. The decision which parts of the systems should be implemented in hardware and which in software is often guided by experience. For example, in video processing applications, the transformation of single frames (e.g., redundancy reduction and quantization) must be performed in high-speed and is usually implemented in hardware, while the composition of the frames is usually done in software. After the HW/SW partitioning, the design flow diverges and hardware and software parts of the system are de-

Figure 2.1: Classical Design Flow

veloped separately and independently. The integration of the hardware and software modules is not done until the last development step.

The separation of hardware and software design flows severely increases the system integration effort and makes it difficult and error-prone. For example, if the HW/SW interface definitions show deficits or if the communication between hardware and software designers is insufficient, system integration requires a lot of debugging and re-design. Furthermore, the later defects are revealed, the more expensive is their removal. If they were injected in early development phases, the designers often have to go back through the complete design cycle to detect and to mend them. Besides the cost and quality issues, a major drawback of the separated development of hardware and software is the issue of performance. The early HW/SW partitioning does not allow the evaluation of different design alternatives, and thus sacrifices significant optimization potential. HW/SW co-design is an approach to overcome these problems.

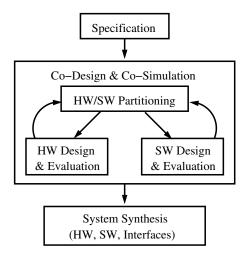

### 2.1.1 Design Flow

The idea of HW/SW co-design came up in the early 1990s [PP92, EHB93, GM93, KL93]. The central point is that hardware and software are developed together in an integrated system design process. The resulting co-design flow is shown in Figure 2.2. As before, it starts with an abstract specification, but now, the HW/SW partitioning is not fixed at the beginning. Instead, it is part of an iterative process, where different design alternatives are evaluated and compared. As a consequence, it is possible to explore the whole design space and to find an optimal HW/SW architecture. Furthermore, it allows an early analysis of HW/SW interfaces and thus reduces the cost of integration and defect removal.

Figure 2.2: HW/SW Co-Design Flow

An essential component of co-design methods is HW/SW co-simulation, which is necessary to evaluate and compare different design alternatives. In a HW/SW co-simulation, hardware and software parts of a system are simulated together. For example, an Instruction Set Simulator (ISS) is executed together with a VHDL (VHSIC<sup>1</sup> Hardware Description Language) module. This provides an integrated way to simulate the interactions between hardware and software. At the same time, it allows performance evaluation if performance parameters like the delay of each module and the timing relations among events are simulated.<sup>2</sup>

The main challenge in HW/SW co-simulation is that hardware and software designers talk in different languages. They use different abstraction levels, different models of computation, different programming languages and different tools. These differences make it complicated to bring the design processes together and to unify them in a single co-simulation framework. To promote unifying frameworks, it is vital to gain insights into the relationship between different models of computations [Lee02]. An important question is how to combine synchronous and parallel hardware modules with asynchronous and sequential software models correctly and efficiently. As the software is finally executed on hardware, a simple approach to maintain correctness is to simulate both hardware and software on the lowest level of abstraction, on register transfer level. This is a feasible solution, but it exhibits the drawback of very slow simulation speed. In particular, if the processor design and the compiler are not part of the optimization target, but merely input parameters, the low-level simulation produces a huge unnecessary overhead. To solve this problem, there exist two (complementary) approaches: multi-level simulation and transaction-level modeling. Multi-level simulation means that modules on different abstraction levels are simulated together. Transaction level modeling

<sup>&</sup>lt;sup>1</sup>VHSIC was a 1980s U.S. government program to develop very-high-speed integrated circuits.

<sup>&</sup>lt;sup>2</sup>Other performance parameters could be for example energy consumption, memory usage, and space requirements.

tries to subsume hardware and software modeling under a common model of computation. At the same time, it provides abstractions that are suitable to speed up simulation without sacrificing correctness. The transaction level modeling design methodology can be easily extended to include multi-level simulations. In the following, we briefly introduce the principles of transaction level modeling.

### 2.1.2 Transaction Level Modeling

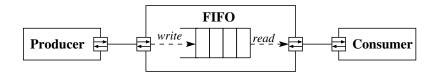

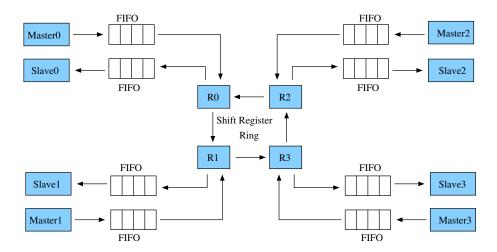

Transaction level modeling (TLM) [Ghe05, Kli05, CG03] was introduced by Synopsis around 2000.<sup>3</sup> The general idea of TLM is the rigorous separation of computation and communication. A system is regarded as a set of communicating processes, which can be structured in modules. The processes model functional processing units, i.e., the computations. The communication architecture is modeled by channels, which interconnect processes and modules. Data exchange is modeled by transactions. The concept of transactions is the heart of the TLM approach. A transaction is an abstraction of any possible information exchange between processes. For example, a transaction could represent the exchange of an abstract data type, but also of a concrete signal on a physical wire. At the same time, the processes can also be modeled on different abstraction levels. As a consequence, the transaction model can be instantiated with different models of computation. For example, a data flow model could be instantiated by using purely functional processes and FIFO (first in first out) channels for the exchange of abstract data types. At the lowest level, a register transfer level (RTL) model could be instantiated by modeling combinational circuits as processes and data exchange with registers.

To obtain a systematic design methodology, TLM defines a set of abstraction levels, which guide the way through the stepwise refinement process from an abstract behavioral specification down to the final implementation. The abstraction levels can be classified according to their modeling accuracy. The dimensions of modeling accuracy can in turn be divided into functional accuracy and timing accuracy.

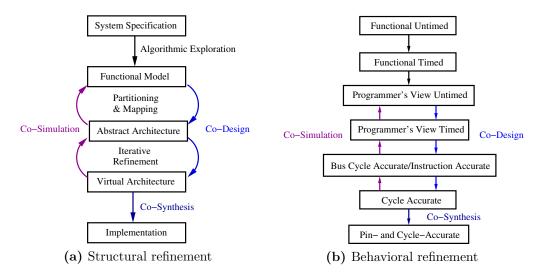

The TLM design flow used in HW/SW co-design is depicted in Figure 2.3. Figure 2.3(a) illustrates the structural view, where emphasis is put on the architecture definition, Figure 2.3(b) illustrates the behavioral view, where emphasis is on the behavioral refinement, e.g., data and time refinements. Both views are conceptually different, but complementary in the design process, as a structural refinement always refines the behavior and vice versa.

Both from a structural and a behavioral view, the first step is to derive a functional model from the system specification. To this end, algorithms and functions are selected that are suitable to implement the purpose of the system. This model is used to define and to validate the functionality of the system. As

<sup>&</sup>lt;sup>3</sup>The term transaction *level* modeling is a little bit misleading because TLM is not a single *level*, but a modeling technique covering different levels of abstraction.

Figure 2.3: TLM Refinement Flow

time plays an important role in nearly all kinds of embedded systems, the first step after defining and validating the functionality of a system is usually to add approximate timing information to processes and channels. This yields a first impression about the timing behavior. To that end, from a behavioral view, an *untimed functional* and a *timed functional* model are distinguished. In this early design phase, time is usually over-approximated because an important goal is to assess the feasibility of the design and to get preliminary performance estimations. The resulting timing constraints on processes and channels can be regarded as time budgets for later design phases because they constitute the upper bounds that must be obeyed to meet the system timing requirements.

When the functional model of the design is validated and the preliminary performance estimation turns out to be satisfactory, the next step is to map it to an abstract architecture. To this end, the functional model is partitioned and mapped to abstract hardware and software components. From a behavioral view, this mapping is the transition to the programmer's view. Now it is possible to add more realistic timing information, depending on the HW/SW partitioning. Still, the timing information is over-approximated, such that timing constraints can be interpreted as time budgets for later design phases.

In the next design phase, the abstract architecture is mapped to a virtual architecture. To this end, each partition (or component) is either refined manually or existing modules (Intellectual Properties, IPs) are used as implementation. The manual refinement includes refinement of the data granularity and timing behavior. On the software side, the modules are implemented in a high-level programming language, and real-time operating system functionality is added where necessary. The compilation of the software components yields an instruction accurate model. On the hardware side, communication channels and protocols are chosen, and hardware data types are defined. This yields a bus cycle accurate model (e. g., a VHDL design). From the bus cycle/instruc-

tion accurate model, a cycle-accurate model can be derived. The result of the iterative refinement phase is a cycle-accurate, synthesizable system design.

In the last step, the final *implementation* is synthesized, which is *pin- and cycle-accurate*. This is usually done automatically by *electronic design automation* (EDA) tools.

### 2.2 HW/SW Co-Verification

In the last decade, embedded systems have become omnipresent in everyday lives. At the same time, they are increasingly used in cost-critical and lifecritical applications, for example in the automotive sector or in the medical sector. This has led to a drastically heightened significance of design correctness of these systems. Unfortunately, conventional verification and validation techniques are difficult to use for quality assurance of embedded systems. Harris [Har05] attributes this to the high complexity of these systems, which stems from their size and their heterogenity. The considered systems are timed and have to meet strict real-time requirements. They often consist of a large set of concurrent or parallel processes exhibiting non-deterministic behavior. A particular problem is the composition of synchronous and asynchronous subsystems. Last but not least, verification techniques are usually designed either for hardware or for software, and conveying them to the other is not trivial. Nonetheless, several co-verification techniques evolved over the last few years.

In general, one can distinguish between formal co-verification as a static and complete technique, and simulation and testing as dynamic and incomplete techniques. Formal co-verification approaches either use abstract formal specifications which are suited for the description of both hardware and software parts of a system, such as finite state-machines (e.g., [BCG<sup>+</sup>97, Lee03]), or they try to combine formal verification methods for hardware and software, e.g., bounded model checking and inductive proofs [GKD06]. Most of these approaches focus on functional verification and do not consider non-functional properties such as real-time behavior. However, exactly those properties gain more and more importance in recent developments, in particular in the embedded system domain. Naturally, non-functional properties such as the abidance of real-time constraints and dependability are vital in safety-critical embedded systems. As it is difficult to formally verify non-functional properties, simulation and testing are more popular in the HW/SW co-design and co-verification community. Following Harris [Har05], simulation and testing for HW/SW coverification involves three major steps:

- (i) input selection

- (ii) co-simulation or test execution

- (iii) evaluation of simulation or test results

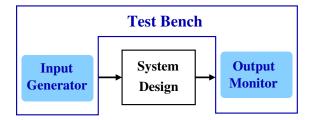

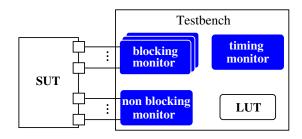

The co-simulation or test execution involves the common execution of hardware and software components and their interactions. Typically, a test bench

Figure 2.4: Structure of a Test Bench

is used to provide the system with inputs and to observe its outputs. To this end, it usually consists of an *input generator* and an *output monitor* as shown in Figure 2.4. The aim of automatic test generation techniques for HW/SW cosimulation is the automatic construction of test benches, i. e., the construction of input generators and output monitors. Ideally, the output monitor does not only observe the outputs, but also evaluates their validity. In the following, we discuss input selection, co-simulation and the evaluation of simulation results in more detail.

### 2.2.1 Input Selection

An important task to make co-simulation systematic and to allow automatization is *input selection*. The term *input selection* denotes the selection of inputs from the set of possible inputs. This includes the selection of input events, the determination of points in time where they should be sent to the design under test, and test data generation. Together, these constitute an input trace. In case of embedded systems, the real inputs are later provided by a technical environment. In general, the number of possibilities to provide an embedded system with inputs is infinite. This has several reasons: first, as these systems are often non-terminating, the length of an input trace is generally infinite. Second, as these systems are timed, and time is real-valued, their exists an infinite set of possibilities at which points of time inputs could be send. Third, also the input data may be real-valued and thus infinite. The infinity of input scenarios makes *exhaustive* or *complete* simulation and testing generally impossible. Thus, *input selection* is a vital task for simulation and testing of embedded systems.

In the co-simulation setting, the environment is replaced by a test bench, which provides inputs and observes outputs. In our context, the test bench can be regarded as an *environment model*. In this terminology, one can distinguish open environments, which may provide arbitrary inputs at arbitrary times (e. g., randomized), and restricted environments, which only provide inputs at certain times, orders and ranges. It is important to note that knowledge about the environment can be used to limit the number of test scenarios, and to concentrate on possible or likely inputs. Of course, for robustness or fault tolerance testing, an open environment model is preferable.

Regardless of whether a test bench corresponds to an open or to a closed environment, there exist different strategies to select simulation or test inputs from the infinite set of possible inputs. The basis for assessing the quality of a given set of inputs (i.e., a test suite), and thus for the selection of a "good" test suite, is a fault model. A fault model allows the concise representation of the set of all possible design errors of a given system. With that, the coverage of a test suite with respect to a given design can be evaluated. For example, a popular fault model in the software domain is statement coverage, where a potential fault is associated with each line of code. Using this fault model, the coverage of a given test suite with respect to a given design can be evaluated by computing the ratio of statements executed by the test suite to all the statements in the design. Other typical fault models from the software domain are control- and data flow based like branch coverage, path coverage or domain coverage. In the HW/SW co-design domain, state machine based fault models like state coverage or transition coverage are widely used. In the hardware domain, the most popular fault models are stuck-at coverage and toggle coverage. In general, one can distinguish randomized, coverage-directed, and fault-directed input selection.

For randomized input selection, test inputs are chosen randomly. At arbitrary times, a random event is taken from the set of input events, and test data is generated randomly. It is also possible to define probability distributions for input events and test data. To determine the delays between input events, it is reasonable to use exponential distributions. Randomized input selection allows the fast generation of large test suites, but no conclusions about how much of the design is tested can be drawn.

For coverage-directed input selection, the test generation technique heuristically modifies an existing test suite and evaluates fault coverage to decide whether the modification yields an advantage. A popular technique for coverage-directed input selection is the use of genetic algorithms together with a cost function which is used to evaluate new test sequences. It is also possible to use randomized input selection together with a cost function to achieve a certain coverage. Coverage-directed input selection is potentially less time-consuming than fault-directed techniques because efficient heuristics may be used to modify the test suite. However, the quality of the resulting test suite depends on the used heuristics.

For fault-directed input selection, the test generation technique targets a specific fault and constructs a test sequence to detect that fault, e.g., using path conditions. The resulting fault coverage is evaluated to decide whether the test generation process should be terminated. Popular techniques for fault-directed input selection are constraint solving at constraint and data flow graph (CDFG) level for software, and BDD based techniques such as satisfiability (SAT) solving for hardware. Fault-directed input selection allows the systematic derivation of minimal test suites with maximal coverage, but can be very costly in terms of computation time.

### 2.2.2 Co-Simulation

In HW/SW co-simulation, the design under test, including hardware and software components, is executed in a simulator. Conventionally, there is a gap between the simulation techniques used for hardware and those used for software. Typically, hardware is simulated by event-driven simulators with picosecond accuracy, e.g., on register-transfer level or on gate level. Opposed to that, software 'simulation' is usually performed by simply executing the code, possibly together with a real-time operating system (RTOS), on any processor which supports the RTOS and the interpreter of the language [Har05]. Co-simulation techniques often bridge the gap between hardware and software simulation by explicitly modeling the target processor, by compiling the software for it, and by simulating the execution of the software on the processor model together with the hardware components. An alternative to that is the approach of executable system-level design languages such as SystemC or SystemVerilog. There, hardware and software tasks are modeled in a common language and run concurrently in the simulation. The expressiveness of these languages also allows the explicit modeling of hardware/software interfaces and interactions.

The challenge of co-simulation is to be efficient and accurate at the same time. These goals contradict each other. In general, a higher accuracy always leads to lower performance. Thus, it is vital for co-simulation techniques to choose the appropriate abstraction level. As we have seen in Section 2.1, the TLM refinement flow defines a set of abstraction levels with ascending accuracy. On the functional level, no data or timing details are modeled. As a consequence, functional models can be executed with very high simulation speed. At the further end, pin- and cycle-accurate models contain all data and timing details needed for hardware and software synthesis. These models can only be executed with very low simulation speed. The models in between, e.g., bus-cycle and instruction accurate models, are often referred to as transaction level models. They are part of the TLM design paradigm, i.e., details of communication among computation components are separated from the details of computation components. For co-simulation, it is important that unnecessary details of communication and computation are hidden in a transaction level model and may be added later. As a consequence, transaction level models speed up simulation drastically opposed to commonly used hardware models such as RTL models. At the same time, they allow the evaluation and validation of design alternatives in HW/SW co-design at a high level of abstraction.

#### 2.2.3 Evaluation of Simulation Results

The aim of the evaluation of simulation or test results is to inspect simulation or test traces in order to decide whether the system behaved correctly for a specific input trace, or whether a defect was detected. One possibility to achieve this is to inspect simulation or test traces manually. In most cases, this is not only error-prone but also unacceptably time-consuming. A prerequisite for the automated evaluation of simulation results is a machine-readable description of

the expected or correct system behavior. To that end, it is necessary to formalize the expected behavior somehow. For that, there exist two complementary approaches: assertion-based and specification-based techniques.

Assertion-based techniques require the definition of a set of assertions, which are dynamically checked during simulation or test execution. Assertion-based techniques are particularly well-suited for validation purposes, because system requirements can often be directly formalized as a set of assertions. In addition, assertions are generally well-suited to formalize plausibility checks, e. g., on variables representing physical data. A great advantage of assertion-based techniques is that they can be directly derived from the requirements, and no formal model of the system is required. A major drawback is that the assertions that can be derived from the requirements are usually coarse-grained. Manual effort is necessary to translate them into machine-checkable assertions that are related to the concrete signals of the final implementation. Furthermore, the assertions have to be inserted manually.

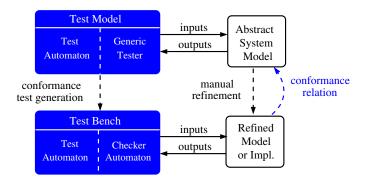

Specification-based techniques are based on a formal model, which is used as specification of the expected or correct system behavior. The evaluation of simulation results is done by comparing the behavior of the system implementation with the behavior of the formal specification. A specification-based technique which is broadly elaborated in the literature is conformance testing, introduced by Tretmans [Tre96]. There, a conformance relation is used to decide whether the implementation conforms to the specification. There are two major advantages of conformance testing: first, if an executable formal specification is available, conformance testing can be applied fully automatically. Second, conformance testing is especially well-suited to ensure consistency when a design is refined from specification to implementation, as it is for example the case in model-driven development processes or in the typical HW/SW co-design flow.

Overall, assertion-based and specification-based techniques for the evaluation of simulation or test results are complementary and should be used together. Assertion-based testing is especially well-suited to check whether a system fulfills the requirements, specification-based testing is better suited to ensure consistency between different models in a model-centric design flow. As conformance testing plays a major role in this thesis, we give a more detailed introduction to that in Section 2.3.3.

### 2.3 Verification and Validation Techniques

Verification and validation (V&V) techniques are used to check whether a system conforms to the requirements and whether it satisfies its intended use. Verification and validation techniques are used in all kinds of domains. However, the interpretation of notions and central concepts varies in different communities. In this section, we first give a brief introduction to some basic ideas and review the main characteristics of important V&V techniques. Then, we

introduce the techniques that are most relevant for the approach of this thesis, namely model checking and conformance testing.

### 2.3.1 Preliminaries

For software validation and verification, there exists an IEEE standard [IEE04], which gives the following definitions:

- Validation: The process of evaluating a system or component during or at the end of the development process to determine whether it satisfies specified requirements. (Are we building the right thing?)

- Verification: The process of evaluating a system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase. (Are we building the thing rightly?)

Unfortunately, the IEEE classification of Validation and Verification is not always in compliance to the use of the terms in different communities. For example, an alternative interpretation that is wide-spread in software engineering communities is to take the term verification literally. Then, it corresponds to formal proof techniques that aim at yielding absolute guarantees about the correctness of a given system, in contrast to falsification techniques such as simulation and testing. In the HW/SW co-design community, the differentiation between verification and validation is often abandoned, and the term HW/SW co-verification is used for all kinds of V&V techniques. To simplify things and to stay out of the debate, we follow this and use the term coverification for all kinds of V&V techniques applied to the HW/SW co-design domain.

In general, one can distinguish static and dynamic V&V techniques. Static V&V techniques are static analyses and formal verification, the most popular dynamic V&V techniques are simulation and testing. In this thesis, we use formal verification, simulation and testing. Formal verification provides a formal proof that a formal specification satisfies a given property expressed as logic formula, using formal methods or mathematics. The result is *complete* and guarantees that the property is satisfied for all possible input scenarios. Important formal verification techniques are model checking and theorem proving. In simulation and testing, experiments are performed before deploying the system in the field. In *simulation*, the experiments are performed on a model or abstraction of the system. Testing is similar to simulation, apart from that the experiments are performed with the real implementation. The border between simulation and testing becomes blurred in mixed HW/SW systems because very often parts of the system are simulated while for others the implementation is executed. Common examples are Hardware in the Loop simulations, where the real hardware is executed in a simulated environment, and Software in the Loop simulations, where the software is executed on simulated hardware. The main advantage of simulation and testing techniques is that they do not require any prerequisites like a formal system model or formal

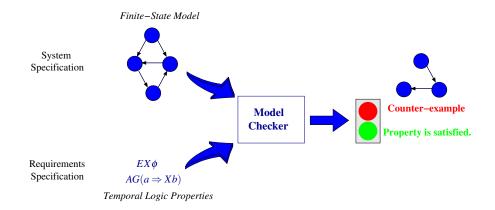

Figure 2.5: Model Checking

requirement specifications, and that the effort is considerably lower than for formal verification. The disadvantage is that the results are *incomplete*, yielding only propositions with respect to the executed input scenarios. In other words, simulation and testing can be used to show the presence of bugs, but never their absence (Dijkstra [DHD72]). Note that all V&V techniques can be used for both verification or validation. With formal verification, one can prove that a system fulfills a given requirements specification or that a refined formal model conforms to an abstract specification. Regarding simulation and testing, one can check certain assertions during test execution, which are derived from the requirements specification (assertion-based testing), or one can compare the outputs of an implementation with the outputs of a specification (specification-based testing). Checking whether the implementation conforms to the specification is a special case of specification-based testing also termed conformance testing.

### 2.3.2 Model Checking

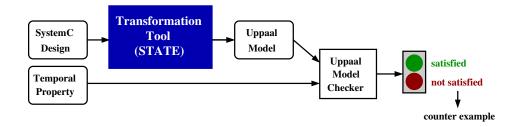

The aim of model checking is to check whether a model of a finite-state concurrent system (system specification) fulfills certain logical properties (requirement specification). A model checker is a tool that automatically checks whether the properties are satisfied, and yields counter-examples if not (see Figure 2.5). The counter-examples are given as traces of the system that violate the postulated property. The following section gives a brief introduction to model checking based on Clarke et al. [CGP99].

Formally, model checking is used to check whether a model  $\mathcal{M}$  satisfies a property  $\phi$ :

The model  $\mathcal{M}$  of the system is usually specified as a labeled transition system (LTS), which can be represented as a *Kripke structure*. A Kripke structure is a labeled transition graph, where the nodes represent the reachable states of the system and the edges transitions from one state to another. Paths in the graph model possible executions of the system. To model properties of the system, a function is used that labels each state with a set of atomic propositions that are true in this state. Formally, a Kripke structure  $\mathcal{M}$  can be defined as follows:

**Definition 1** (Kripke Structure). Let AP be a set of atomic propositions. A Kripke structure  $\mathcal{M}$  over AP is a four tuple  $\mathcal{M} = (S, S_0, R, L)$  where

- $\blacksquare$  S is a finite set of states,

- $S_0 \subseteq S$  is the set of initial states,

- $R \subseteq S \times S$  is a transition relation that must be total, i. e., for every state  $s \in S$  there is state  $s' \in S$  such that R(s,s'),

- $L: S \to 2^{AP}$  is a function that labels each state with the set of atomic propositions true in that state.

A path in  $\mathcal{M}$  is an infinite sequence of states  $\pi = s_0 s_1 s_2 ...$  such that  $R(s_i, s_{i+1})$  for all  $i \geq 0$ .

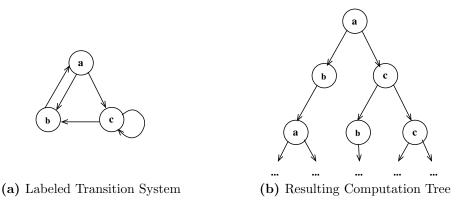

For the specification of logical properties of both hardware and software systems, temporal logics have proved to be useful. With temporal properties, it is possible to describe the ordering of events in time without introducing time explicitly. Temporal logics use atomic propositions and boolean operations to describe properties of states (such as "situation is critical"), and temporal operators such as eventually or never to describe properties beyond states (such as "a critical situation never arises"). A logic for specifying properties of the state transition systems is the computation tree logic CTL\*, which is used to describe properties of computation trees. A computation tree can be derived from a labeled transition system by taking the initial state as root, and then appending all possible successor states of the system. To those, again the successor states are appended until all (infinite) paths of the system are unfolded. An example is shown in Figure 2.6. From the initial node a, possible successor states are b and c. From state b, one can only go back to a, from state c to b or c, and so on.

CTL\* formulae are composed of a *state formula*, which describe properties of a state, *temporal operators*, which describe properties of a path, and *path quantifiers*, which describe whether a property holds on all path or on some path. There are two path quantifiers and five basic temporal operators in CTL\*:

- Path quantifiers:

- **A**: for all paths (**A**lways)

- E: for some path (Exists)

- Temporal operators:

Figure 2.6: Computation Tree

- $\mathbf{X} \phi$ : property  $\phi$  holds in the next state (neXt)

- $\mathbf{F} \phi$ : property  $\phi$  will hold at some state in the future (Future)

- **G**  $\phi$ : property  $\phi$  holds at every state (**G**lobally)

- $\phi_1$  U  $\phi_2$ : property  $\phi_1$  holds in all states until property  $\phi_2$  holds (Until), and  $\phi_2$  holds eventually at some state

- $\phi_1$  **R**  $\phi_2$ : property  $\phi_2$  holds in all states until property  $\phi_1$  holds, or  $\phi_2$  holds never (Release)

In CTL\*, these operators can be freely combined. The most important subsets of CTL\* are the *linear-time logic* LTL and the *computation tree logic* CTL. LTL is based on the assumption that time is linear and thus only a single path is considered. As a consequence, no path quantifiers are used in LTL.<sup>4</sup> In this thesis, we focus on CTL because the UPPAAL requirements language is a subset of CTL.<sup>5</sup> In CTL, it is assumed that there are branches in the computation tree, and temporal operators must be immediately preceded by a path quantifier. This leads to the following rules for the structure of CTL formulae:

- if  $p \in AP$ , then p is a state formula

- if  $\phi_1$ ,  $\phi_2$  are state formulae, then  $\neg \phi_1, \phi_1 \land \phi_2$  and  $\phi_1 \lor \phi_2$  are state formulae

- if  $\phi_1$ ,  $\phi_2$  are state formulae, then  $\mathbf{X}$   $\phi_1$ ,  $\mathbf{F}$   $\phi_1$ ,  $\mathbf{G}$   $\phi_1$ ,  $\phi_1$   $\mathbf{U}$   $\phi_2$ , and  $\phi_1$   $\mathbf{R}$   $\phi_2$  are path formulae

- lacktriangledown if  $\phi$  is a path formula, then  $\mathbf{E}$   $\phi$  and  $\mathbf{A}$   $\phi$  are state formulae

Using CTL it is possible to specify important properties, in particular *safety* properties (something bad will never happen), and *liveness properties* (something good will eventually happen).

The simplest model checking algorithm is to construct an explicit representation of a Kripke structure  $\mathcal{M} = (S, R, L)$  as a labeled, directed graph, and

<sup>&</sup>lt;sup>4</sup>LTL can nevertheless be applied to computation trees. Then, an implicit **A**lways is assumed and the given property must hold on all paths.

<sup>&</sup>lt;sup>5</sup>In UPPAAL, nesting of path formulae is not allowed. As a consequence, complex properties such as confluence cannot be verified.

then to check which states in S satisfy a CTL formula  $\phi$ . The problem is that the explicit representation of the Kripke structure yields an exponential increase in the number of states, which is also referred to as the *state space explosion* problem. Several techniques exist to face this problem, e.g., binary decision diagrams, symbolic model checking, partial order reduction, and abstraction techniques. However, to elaborate these techniques is not in the scope of this thesis. We refer the interested reader to Clarke et al. [CGP99].

### 2.3.3 Conformance Testing

The aim of conformance testing is to determine whether an implementation of a system conforms to its specification. To this end, it is a necessary prerequisite to define a formal *implementation relation*. Widely used and well-established in the context of model-based testing of labeled transition systems is the *input output conformance* (ioco) relation introduced by Tretmans [Tre96]. In this section, we briefly review the *ioco*-theory. For more detail, we refer to Schmaltz et al. [ST08] and Tretmans [Tre08].

An implementation relation relates an implementation to its specification. Whereas a specification is a formal object taken from a formal domain SPEC, the implementation is usually a real physical object. To relate such an implementation to a formal specification is possible by assuming that any real implementation can be modeled by some formal object  $i \in MOD$ , where MOD is the universe of all possible implementation models. This assumption is usually referred to as the test assumption. Based on the test assumption, a formal implementation relation can be defined as  $imp \in MOD \times SPEC$ . An implementation i is than said to be correct with respect to a specification s if i imp s.

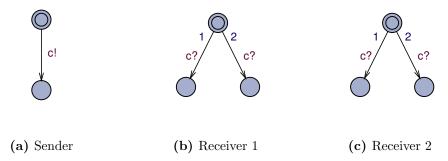

The implementation relation ioco is based on the assumption that both the specification and the implementation can be described by labeled transition systems (LTS) with inputs and outputs. The ioco relation defines that an implementation i conforms to its specification s if any experiment derived from s and executed on i leads to an output of i that is foreseen by s.

**Definition 2** (Input-output conformance (ioco)). An implementation i conforms to a specification s if for all input traces  $\sigma$  that can be derived from s the set of output traces of i is contained in the set of all possible output traces of s:

```

i ioco s iff \forall \sigma \in traces(s) : out(i after \sigma) \subseteq out(s after \sigma)

```

The domains of i and s, and also the semantics of traces(s) and  $out(s, \sigma)$  are defined by the type and interpretation of the labeled transition system used for modeling implementation and specification. For now, we deliberately abstract away from any specific semantics. In Chapter 6, we describe a more specific conformance relation for UPPAAL timed automata.

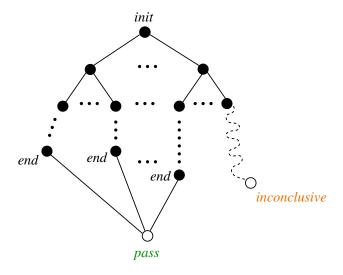

Based on the *ioco* relation it is possible to evaluate test results by comparing the outputs of the implementation with those predicted by the specification. If

the implementation sends an output not foreseen by the specification, the test verdict is *fail*. If the implementation sends only expected outputs for a given input trace, the test verdict is *pass*. A peculiar aspect of the *ioco* relation is that the absence of outputs is also considered as an observable event, which is called *quiescence*. This allows the definition of a timeout if the implementation does not send any outputs for a certain time interval, after which the test verdict is *fail*.

From the *ioco* relation, a general approach for the generation of conformance tests can be derived. First, one has to compute all possible output traces of the specification for a given input trace. Second, the implementation is executed for the same input trace. The previously computed output traces can then be used as a *test oracle* to check the correctness of the outputs of the specification using the relation  $out(i \text{ after } \sigma) \subseteq out(s \text{ after } \sigma)$ . This can be done fully automatically. Tretmans [Tre08] showed that the generated tests are sound, i. e., any failing implementation is indeed non-conforming and no false detections of errors can be made.

### 2.4 SystemC

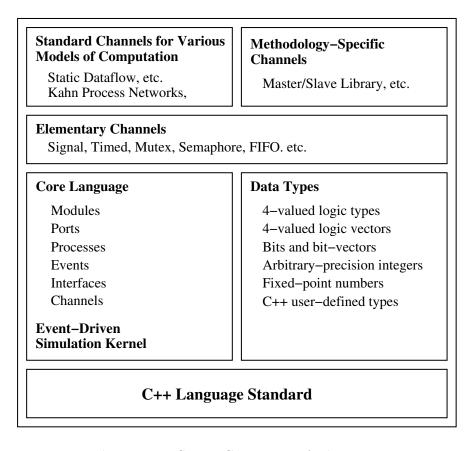

SystemC [IEE05] was introduced by the Open SystemC Initiative (OSCI) in 1999<sup>6</sup>. The aim of the Open SystemC Initiative was to develop an open industry standard for system-level modeling, design and verification. SystemC can be seen as both a system level design language and a framework for HW/SW co-simulation. It allows the modeling and execution of system level designs on various levels of abstraction, including classical register transfer level hardware modeling and transaction-based design. This allows system-level design from abstract concept down to implementation in a unified framework. Note that SystemC without extensions can only be used for digital HW/SW Systems. There also exists an extension for analog and mixed-signal components, namely SystemC-AMS, but this is not in the scope of this thesis.

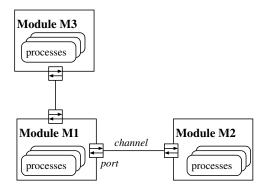

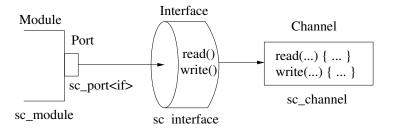

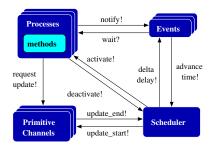

SystemC is implemented as a C++ class library, which provides the language elements and an event-driven simulation kernel. The language comprises constructs for modularization and structuring, for hardware, software and communication modeling, and for synchronization and coordination of concurrent processes. From a structural point of view, a SystemC design is a set of modules, connected by channels. The structure strictly separates between computation and communication units (i. e., modules and channels) and is highly flexible due to a communication concept that allows transaction level modeling and communication refinement. The event-driven simulation kernel regards the SystemC design as a set of concurrent processes that are synchronized and coordinated by events and communicate through channels.

<sup>&</sup>lt;sup>6</sup>Corporate OSCI members are amongst others: ARM, Intel, Cadence, CoWare, NXP, Synopsis, Mentor Graphics, and STMicroelectronics.

Figure 2.7: SystemC Language Architecture