0 calificaciones0% encontró este documento útil (0 votos)

Detector de Código BCD Simulado en Quartus 13.0

Detector de Código BCD Simulado en Quartus 13.0

Cargado por

Kevin ArteagaEl sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Descargar como pdf o txt

Detector de Código BCD Simulado en Quartus 13.0

Detector de Código BCD Simulado en Quartus 13.0

Cargado por

Kevin Arteaga0 calificaciones0% encontró este documento útil (0 votos)

El sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Título original

Detector de código BCD simulado en Quartus 13.0

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

El sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Descargar como pdf o txt

0 calificaciones0% encontró este documento útil (0 votos)

Detector de Código BCD Simulado en Quartus 13.0

Detector de Código BCD Simulado en Quartus 13.0

Cargado por

Kevin ArteagaEl sistema digital determina si el número ingresado corresponde un BCD. En caso de no serlo activa la señal error.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Descargar como pdf o txt

Está en la página 1/ 13

ESCUELA SUPERIOR POLITCNICA DEL LITORAL

FACULTAD DE INGENIERA EN ELECTRICIDAD Y COMPUTACION

LABORATORIO DE SISTEMAS DIGITALES

Proyecto de primer parcial

DETECTOR BCD

Presentado por:

KEVIN ARTEAGA YELA

XAVIER AGUAYO MURILLO

Profesor a cargo:

ING. RONALD PONGUILLO

Guayaquil Ecuador

2014

2

CONTENIDO

1. ESPECIFICACIN ......................................................................................................... 3

DETECTOR DE CODIGO BCD ................................................................................. 3

2. DIAGRAMA DE BLOQUES ............................................................................................ 4

3. DIAGRAMA ASM ........................................................................................................... 5

4. DIAGRAMA DE TIEMPO ............................................................................................... 6

Salida BCD activada .................................................................................................. 6

Salida ERROR activada ............................................................................................ 7

5. DIAGRAMA ESQUEMATICO ......................................................................................... 7

6. DESCRIPCION VHDL.................................................................................................... 9

7. REPORTE SOBRE APROVECHAMIENTO ................................................................. 11

8. CONCLUSIONES ........................................................................................................ 12

9. RECOMENDACIONES ................................................................................................ 12

10. BIBLIOGRAFA ........................................................................................................ 13

3

1. ESPECIFICACIN

DETECTOR DE CODIGO BCD

Disear y construir un circuito DETECTOR DE CODIGO BCD. El circuito tiene una

entrada serial de DATOS, la entrada START y la entrada MOSTRAR representadas

por botoneras y dos salidas (BCD y ERROR) indicadas con dos diodos LED.

Adicionalmente se agregaron dos entradas: la entrada INGRESAR y la entrada

STOP.

Al presionar y soltar la botonera START, el circuito habilitar la entrada de DATOS

siempre que presionemos la entrada INGRESAR, asumiendo que el primer bit que

se ingresa es el LSB. Despus de haber ingresado los datos presionaremos el

botn STOP para detener el ingreso de datos.

Si el cdigo ingresado corresponde a un cdigo BCD, el circuito regresa al estado

inicial generando la seal de salida BCD.

Pero, si el cdigo ingresado no corresponde a un cdigo BCD, el circuito genera la

seal de salida ERROR y luego regresa al estado inicial.

Los diodos LED que indican las salidas BCD y ERROR permanecen prendidos hasta

que se activa la entrada START para empezar el ingreso de un nuevo dato.

Si la seal BCD ha sido activada y se presiona el botn MOSTRAR entonces el

numero BCD ingresado es mostrado en un display de siete segmentos.

4

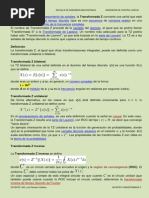

2. DIAGRAMA DE BLOQUES

En esta seccin mostraremos un esquema general de nuestro sistema digital

DETECTOR BCD, indicando las entradas, salidas y una breve descripcin de la

funcin de cada una. El diagrama de bloques est formado por los siguientes

componentes.

Controlador

Almacenador de datos

Detector BCD

Display

El controlador dirige las acciones del usuario y de la maquina de estados, las

entradas y salidas se muestran en la figura 1. Las entradas del controlador se

encuentran en la parte izquierda del bloque y las salidas a la derecha.

El almacenador de datos guarda los cuatro bits (0 - 1) que el usuario ingrese, el

ingreso de cada bit es habilitado por la entrada en_guarda. La salida del bloque

almacenador de datos es un nmero de cuatro bits.

El detector BCD comprueba si el dato mostrado es un nmero BCD y su salida

SiEsBCD se conecta al controlador para que el tome la decisin de mostrarle al

usuario si es BCD o ERROR.

El bloque Display tiene la funcin de mostrar el nmero BCD.

Figura 1.- Diagrama de bloques del sistema digital detector BCD

3. DIAGRAMA ASM

Figura2.- Diagrama ASM del sistema DETECTOR BCD

El diagrama ASM mostrado en la figura 2 es el diagrama de flujo del bloque

controlador mostrado en la figura 1. Existen 7 estados, etiquetados como Ta, Tb, Tc,

Td, Te, Tf, Tg, Th. El primer estado Ta encera el registro y el contador de cuatro bits.

Una vez que se presiona START pasamos al siguiente estado Tb; si dejamos de

presionar avanzamos al estado Tc.

En el estado Tc, si presionamos STOP nos vamos al siguiente estado Td; sino s,

presionamos ingresar habilitamos en contador (EnC) y el registro (EnR1) para cargar

un bit. Y as se cargaran bits y aumentara el contador hasta que el usuario presione

STOP.

6

Cuando estamos en el estado Td, analizamos si el dato ingresado es un nmero

BCD. Entonces, primero preguntamos si el nmero se ingreso ms de cuatro veces

(4) y si esto es verdadero vamos al estado Te y mostramos ERROR. Si es falso,

preguntamos si el nmero es mayor que nueve (Data>9), si es verdadero

nuevamente nos vamos al estado Te y mostramos ERROR; pero, si es falso nos

dirigimos al estado Tf y activamos la salida BCD, que indica que el nmero

ingresado es BCD.

En el estado de ERROR y en el estado BCD, pasa salir de este estado y regresar al

estado inicial hay que presionar y soltar el botn START.

4. DIAGRAMA DE TIEMPO

Salida BCD activada

Figura 3.- Diagrama de tiempo mostrando la salida error

Las seales internas contador y registro mostrados en la figura 3 nos ayudaran a

saber el nmero de veces que ingreso el dato y el dato de cuatro bits cargado. Una

vez ingresado el dato, el sistema analiza el dato siempre y cuando el usuario

presione STOP. El usuario ingreso exactamente cuatro bits y el nmero cargado es

tres en binario 0011. El controlador muestra la salida BCD que indica que el

nmero es un BCD. Data_out es la salida de 7 bits del decodificador de 7

segmentos.

La figura 4 muestra la salida de ERROR activada. Vemos que despus de presionar

el botn stop, el nmero cargado es 11 en binario 1011. El nmero 11 no

representa un nmero BCD, y por lo tanto muestra la salida ERROR.

7

Salida ERROR activada

Figura 4.- Diagrama de tiempo mostrando la salida BCD

5. DIAGRAMA ESQUEMATICO

La figura muestra el diagrama esquemtico con todas las interconexiones y sus

respectivos nombres. Los componentes utilizados son los siguientes

Controlador

Divisor de Frecuencia

Antirebote

Decodificador de 7 segmentos

Comparadores

Display de 7 segmentos

Puertas lgicas

Descripcin de las terminales ms importantes

EnC.- Habilita al Contador para que cuente el nmero de bit ingresado

EnR1.- Habilita el registro para que se cargue un bit y realice el desplazamiento

DATO.- Bit a ingresar para formar el nmero BCD

BCD.- Salida de un bit que indica si el nmero ingresado es BCD.

ERROR.- Salida de un bit que indica si el nmero ingresado es no es BCD.

DATA[3..0].- Seal interna utilizada para mostrar el valor cargado en el registro de

desplazamiento.

COUNT[3..0].- Seal interna utilizada para mostrar el nmero de datos bits ingresado

por el usuario.

DiferDe4.- Seal que indica si ingreso ms de cuatro bits o menos de cuatro bits

DataMay9.- Seal que indica si el numero ingresado en mayor que nueve

8

6. DESCRIPCION VHDL

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity DetectorCodigoBCD is

port( clock, resetn: in std_logic;

start, DATOS, mostrar, ingresar, stop: in std_logic;

activ_disp: out std_logic;

error,bcd: out std_logic;

data_out: out std_logic_vector(0 to 6));

end detectorCodigoBCD;

architecture comportamiento of DetectorCodigoBCD is

--*****COMPONENTES*****--

component ANTIREBOTE

port(PB_N, CLOCK_100Hz : IN STD_LOGIC;

PB_SIN_REBOTE : OUT STD_LOGIC);

END component;

component clock_div

port

(CLOCK_50MHz :IN STD_LOGIC;

CLOCK_1MHz :OUT STD_LOGIC;

CLOCK_100KHz :OUT STD_LOGIC;

CLOCK_10KHz :OUT STD_LOGIC;

CLOCK_1KHz :OUT STD_LOGIC;

CLOCK_100Hz :OUT STD_LOGIC;

CLOCK_10Hz :OUT STD_LOGIC;

CLOCK_1Hz :OUT STD_LOGIC);

end component;

component contador_up

port(clock,resetn,enable: in std_logic; --enable: entrada de habilitacion

Q : out std_logic_vector(3 downto 0));

end component;

component reg_iz_der

port(R,Resetn,Clock, enable: in std_logic;

Q: out std_logic_vector(3 downto 0));

end component;

component DEC_DR_N

port( BCD : in std_logic_vector(3 downto 0);

10

SEG7 : out std_logic_vector(0 to 6));

end component;

type estado is (Ta, Tb, Tc, Td, Te, Tf, Tg, Th);

signal y: estado;

signal Vcc, EnR1, EnC, DiferDe4,dataMay9, prende: std_logic;

signal data,count, nueve, cuatro: std_logic_vector(3 downto 0);

signal start1, datos1, mostrar1, ingresar1, stop1: std_logic; -- salidas de

antirebotes

signal clk1, clk2, clk3, clk4, clk5, clk6, clk7: std_logic; -- salida de reloj

CLOCk_div

--*****CONTROLADOR*****--

begin

mss_transiciones: process(resetn, clk7, ingresar, mostrar)

begin

if resetn='0' then y<=Ta;

elsif (clk1'event and clk1='1') then

case y is

when Ta => if start='0' then y<=Ta; else y<=Tb; end if;

when Tb => if start='1' then y<=Tb; else y<=Tc; end if;

when Tc => if stop='0' then y<=Tc; else y<=Td; end if;

when Td => if diferDe4='1' then y<=Te; elsif dataMay9='1' then

y<=Te; else y<=Tf ; end if;

when Te => if start='0' then y<=Te; else y<=Tg; end if;

when Tg => if start='1' then y<=Tg; else y<=Ta; end if;

when Tf => if start='0' then y<=Tf; else y<=Th; end if;

when Th => if start='1' then y<=Th; else y<=Ta; end if;

end case;

end if;

end process;

mss_salidas: process(y, stop, ingresar, start, mostrar)

begin

EnR1<='0'; EnC<='0'; Error<='0'; BCD<='0'; prende<='0';

case y is

when Ta =>

when Tb =>

when Tc => if stop='0' and ingresar='1' then EnR1<='1'; EnC<='1';

else EnR1<='0'; EnC<='0'; end if;

when Td =>

when Te => Error<='1';

when Tg =>

when Tf => BCD<='1'; if start='0' and mostrar='1' then prende<='1';

end if;

when Th =>

end case;

end process;

11

--*****PROCESADOR DE DATOS*****--

Vcc<='1';

nueve<="1001";

Cuatro<="0100";

RELOJ: clock_div port map (clock, clk1, clk2, clk3, clk4, clk5, clk6, clk7);

reg_id: reg_iz_der port map(Datos, resetn, clk6, EnR1, data);

contador: contador_up port map(clk6, resetn, EnC, count);

decoder: dec_DR_N port map (data, data_out);

DataMay9<='1' when (Data > Nueve) else '0';

DiferDe4<='1' when ((Count > cuatro) or (Count < cuatro)) else '0';

activ_disp<='1' when (prende = Vcc) else '0';

end comportamiento;

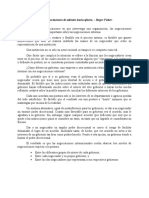

7. REPORTE SOBRE APROVECHAMIENTO

Figura 5.- Captura de pantalla del reporte de compilacin

La figura 5 muestra un reporte general del aprovechamiento de la tarjeta DE0NANO

EP4CE22. Se utilizaron 17 pines de los 154 existentes. Memoria total ocupada en

bits: 5248 (menos del 1%)

12

8. CONCLUSIONES

En resumen, el proyecto DETECTOR BCD se realiz utilizando una

herramienta importante para simular sistemas digitales. Esta herramienta es

Quartus 13.0, por medio de la cual pudimos describir nuestro proyecto de

forma ESTRUCTURAL; en pocas palabras, se escribi todo el proyecto en

lneas de cdigo.

Pudimos darnos cuenta de la dificultad de realizar el proyecto realizando

descripcin estructural, comparado con la construccin de bloques utilizando

el diagrama esquemtico. La dificultad de la descripcin estructural reside en

la interconexin de las terminales de cada componente con otros, lo que no

sucede en la construccin de bloques.

Finalmente, pudimos terminar con xito este proyecto, realizando su anlisis,

la programacin y la implementacin del mismo. Para la implementacin

fsica, se utiliz la tarjeta De0 NANO EP4CE22F17. Cabe destacar que

afianzamos los conocimientos aprendidos en las clases tericas de Sistemas

digitales I y II.

9. RECOMENDACIONES

Fijar el bus de datos nos ayudar a que no existan desconexiones o falsos

contactos; adems, es importante utilizar el cable adecuado para la conexin

de pines del cable de bus de datos con el protoboard. As que si preferimos

utilizar cables rgidos, tomar en cuenta que estos puedes romperse y

producir grandes retrasos a la hora de encontrar el fallo.

Cabe destacar la importancia de conocer las especificaciones de

funcionamiento de los elementos electrnicos a utilizar en nuestro proyecto.

Tales como diodos, pulsadores, resistencia y sus cdigos de colores,

switches y sobre todo el display de 7 segmentos.

Al utilizar la tarjeta DE0 NANO debemos ser cuidadosos con la misma, las

cargas estticas presentes en nuestro cuerpo pueden averiar o daar los

chips y circuitos integrados. Estos dispositivos son sensibles a las cargas

estticas.

13

10. BIBLIOGRAFA

Sistemas digitales, A. Lloris y A. Prieto y L. Parrilla, McGraw Hill,

Madrid 2003.

Fundamentos de sistemas digitales, (7 edicin), Floyd T. L., Prentice

Hall, Madrid 2003.

Principios de Diseo Digital, D.D. Gajski, Prentice Internacional INC.,

1997.

Diseo Digital. Principios y Prcticas, J. F. Wakerly, Prentice

Internacional INC., 2001.

Fundamentos fsicos y tecnolgicos de la informtica, P. Gmez, V.

Nieto, A. lvarez y R. Martnez, Pearson Prentice Hall, Madrid 2006.

También podría gustarte

- Circuitos Combinacionales en El Control de Procesos.100% (1)Circuitos Combinacionales en El Control de Procesos.27 páginas

- Plan de Trabajo Exp Carretera Aconsya Crushuasa100% (1)Plan de Trabajo Exp Carretera Aconsya Crushuasa16 páginas

- Manejo Puerto Paralelo en LabviewAún no hay calificacionesManejo Puerto Paralelo en Labview7 páginas

- 3.2 REPRESENTACIÓN DE ESFUERZOS MEDIANTE EL CÍRCULO DE MOHR. DIAGRAMA P-QAún no hay calificaciones3.2 REPRESENTACIÓN DE ESFUERZOS MEDIANTE EL CÍRCULO DE MOHR. DIAGRAMA P-Q18 páginas

- Experimento 4 - Implementacion de Funciones Booleanas - Circuitos DigitalesAún no hay calificacionesExperimento 4 - Implementacion de Funciones Booleanas - Circuitos Digitales10 páginas

- Números Utilizados en Electrónica DigitalAún no hay calificacionesNúmeros Utilizados en Electrónica Digital21 páginas

- Aplificadores de Potencia Tema (5)Aún no hay calificacionesAplificadores de Potencia Tema (5)26 páginas

- Manual de Usuario Péndulo Invertido Control IIAún no hay calificacionesManual de Usuario Péndulo Invertido Control II30 páginas

- PRACTICA #6 de Robles Nolasco Jose Alberto100% (1)PRACTICA #6 de Robles Nolasco Jose Alberto14 páginas

- Realización de Un Multímetro PonceAún no hay calificacionesRealización de Un Multímetro Ponce22 páginas

- Seguidor de Lineas Con 4 SensoresAún no hay calificacionesSeguidor de Lineas Con 4 Sensores11 páginas

- Criterio de Routh Hurwitz Sistemas ContinuosAún no hay calificacionesCriterio de Routh Hurwitz Sistemas Continuos5 páginas

- Simulación de Un Convertidor Digital AnalógicoAún no hay calificacionesSimulación de Un Convertidor Digital Analógico2 páginas

- Aplicaciones Lineales Del Amplificador Operacional0% (1)Aplicaciones Lineales Del Amplificador Operacional4 páginas

- Diseño de Circuitos Neumáticos: Método Paso A PasoAún no hay calificacionesDiseño de Circuitos Neumáticos: Método Paso A Paso14 páginas

- Unidad I - Sistemas y Codigos Numericos PDFAún no hay calificacionesUnidad I - Sistemas y Codigos Numericos PDF35 páginas

- Uc PIC - Conversión Analógico - DigitalAún no hay calificacionesUc PIC - Conversión Analógico - Digital13 páginas

- Amplificadores Operacionales ECUACIONESAún no hay calificacionesAmplificadores Operacionales ECUACIONES3 páginas

- Principios y Aplicaciones de Los Dispositivos Lógicos Programables Como Las Pals y Las GalsAún no hay calificacionesPrincipios y Aplicaciones de Los Dispositivos Lógicos Programables Como Las Pals y Las Gals6 páginas

- Control de Velocidad de Motor DC Usando Labview y Nidaq100% (2)Control de Velocidad de Motor DC Usando Labview y Nidaq8 páginas

- Circuito de Disparo Con AislamientoAún no hay calificacionesCircuito de Disparo Con Aislamiento18 páginas

- Análisis y Simulación en La Frecuencia de Sistemas Lineales Invariantes en El TiempoAún no hay calificacionesAnálisis y Simulación en La Frecuencia de Sistemas Lineales Invariantes en El Tiempo4 páginas

- Convertidor de Código Con Compuertas Básicas100% (1)Convertidor de Código Con Compuertas Básicas23 páginas

- Transgenerador Magnético - AbstractoAún no hay calificacionesTransgenerador Magnético - Abstracto1 página

- Sistemas Numéricos y Códigos. Sistemas Digitales IAún no hay calificacionesSistemas Numéricos y Códigos. Sistemas Digitales I42 páginas

- Autorreporte Condiciones SST Teletrabajo - CIL ONGAún no hay calificacionesAutorreporte Condiciones SST Teletrabajo - CIL ONG5 páginas

- Negociaciones de Adentro Hacia AfueraAún no hay calificacionesNegociaciones de Adentro Hacia Afuera4 páginas

- Clase 10 Ecuaciones e Inecuaciones Parte 1Aún no hay calificacionesClase 10 Ecuaciones e Inecuaciones Parte 1106 páginas

- ACTIVIDAD COMPLEMENTARIA No. 2 FREDY PABONAún no hay calificacionesACTIVIDAD COMPLEMENTARIA No. 2 FREDY PABON19 páginas

- 1aa. Silabo de Manufactura I - 2021-b VirtualAún no hay calificaciones1aa. Silabo de Manufactura I - 2021-b Virtual8 páginas

- Segunda Diapositiva de Recursos HumanosAún no hay calificacionesSegunda Diapositiva de Recursos Humanos56 páginas

- Copia de CURRICULUM ORLANDO GUERRA MALACARAAún no hay calificacionesCopia de CURRICULUM ORLANDO GUERRA MALACARA5 páginas

- Introducción Al Pensamiento Científico - Resumen Catedra MiguelAún no hay calificacionesIntroducción Al Pensamiento Científico - Resumen Catedra Miguel13 páginas

- Practica 3 Ac-Dc Manual de Practicas ResueltoAún no hay calificacionesPractica 3 Ac-Dc Manual de Practicas Resuelto33 páginas

- Clasificación de Macizos Rocosos (Parte I)100% (1)Clasificación de Macizos Rocosos (Parte I)95 páginas

- Preguntas - Ejercicios - Juego de Estudio para MatemáticasAún no hay calificacionesPreguntas - Ejercicios - Juego de Estudio para Matemáticas4 páginas

- Calor Latente y de Evaporacion PDFAún no hay calificacionesCalor Latente y de Evaporacion PDF11 páginas

- Circuitos Combinacionales en El Control de Procesos.Circuitos Combinacionales en El Control de Procesos.

- 3.2 REPRESENTACIÓN DE ESFUERZOS MEDIANTE EL CÍRCULO DE MOHR. DIAGRAMA P-Q3.2 REPRESENTACIÓN DE ESFUERZOS MEDIANTE EL CÍRCULO DE MOHR. DIAGRAMA P-Q

- Experimento 4 - Implementacion de Funciones Booleanas - Circuitos DigitalesExperimento 4 - Implementacion de Funciones Booleanas - Circuitos Digitales

- Aplicaciones Lineales Del Amplificador OperacionalAplicaciones Lineales Del Amplificador Operacional

- Diseño de Circuitos Neumáticos: Método Paso A PasoDiseño de Circuitos Neumáticos: Método Paso A Paso

- Principios y Aplicaciones de Los Dispositivos Lógicos Programables Como Las Pals y Las GalsPrincipios y Aplicaciones de Los Dispositivos Lógicos Programables Como Las Pals y Las Gals

- Control de Velocidad de Motor DC Usando Labview y NidaqControl de Velocidad de Motor DC Usando Labview y Nidaq

- Análisis y Simulación en La Frecuencia de Sistemas Lineales Invariantes en El TiempoAnálisis y Simulación en La Frecuencia de Sistemas Lineales Invariantes en El Tiempo

- Sistemas Numéricos y Códigos. Sistemas Digitales ISistemas Numéricos y Códigos. Sistemas Digitales I

- Autorreporte Condiciones SST Teletrabajo - CIL ONGAutorreporte Condiciones SST Teletrabajo - CIL ONG

- Introducción Al Pensamiento Científico - Resumen Catedra MiguelIntroducción Al Pensamiento Científico - Resumen Catedra Miguel

- Preguntas - Ejercicios - Juego de Estudio para MatemáticasPreguntas - Ejercicios - Juego de Estudio para Matemáticas