Cours Archi 4

Cours Archi 4

Transféré par

Emma DjomoDroits d'auteur :

Formats disponibles

Cours Archi 4

Cours Archi 4

Transféré par

Emma DjomoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Droits d'auteur :

Formats disponibles

Cours Archi 4

Cours Archi 4

Transféré par

Emma DjomoDroits d'auteur :

Formats disponibles

IUP SI - L3 Architecture d’un ordinateur UPS IUP SI - L3 Architecture d’un ordinateur

Architecture des ordinateurs

Processeur :

Plan du cours :

– Unités de calcul :

➽ Architecture d’un ordinateur – Unité Arithmétique et logique (UAL)

➽ Codage des informations – Eventuellement, unité de calcul sur les flottants (FPU)

➽ Unité Arithmétique et Logique – Mémoire interne (registres) : Utilisés pour stocker temporairement des

➽ Chemin de données informations

➽ Exemple d’architecture – Unité de commande : Automate qui envoie les ordres aux registres, aux unit és de

calcul, au bus, a la mémoire et aux système d’entrées/sorties pour exécuter les

➾ Instructions de traitement

instructions d’un programme.

➾ Instructions de transfert – Bus internes : permettent de tranférer les informations entre la mémoire, les

➾ Instructions de branchement unités de calcul et l’unité de commande.

➾ Programmation modulaire

Remarque : Unités de calcul+Registres+Bus=chemin des données

➽ Synthèse de l’unité de commande

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –1– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture d’un ordinateur UPS IUP SI - L3 Architecture d’un ordinateur

Mémoire

Instructions et données sont codées en binaire et stockées en mémoire dans des

Unités fonctionnelles d’un ordinateur : registres de n bits constitués de la concaténation de n bascules.

Processeur Memoire Interfaces E/S Une mémoire est un vecteur de registres, chacun étant repéré par une adresse

(équivalente à l’indice d’un tableau).

bus Adresse

Memoire Donnees

RD

– Processeur (CPU) : coeur de l’ordinateur. C’est lui qui traite les informations. WR

– Mémoire : stocke les instructions et les données des programmes.

On peut y accéder en lecture ou en écriture :

– Entrées/Sorties : Permettent à l’ordinateur de communiquer avec l’extérieur.

– En lecture, le signal RD met, sur le bus de donnéees, le contenu de la mémoire

Les différentes unités sont reliés par des bus de communication.

correspondant à l’adresse présente sur le bus d’adresses.

– En écriture, le signal WR stocke la valeur présente sur le bus de données à

l’emplacement correspondant à l’adresse présente sur le bus d’adresses.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –2– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture d’un ordinateur UPS IUP SI - L3 Architecture d’un ordinateur

Entrées-Sorties

Caractéristiques d’un processeur

– Unités d’entrée : Clavier, souris, scanner, convertisseur analogique/digital, etc...

– Unités de sortie : Ecran, imprimante, convertisseur numérique/analogique, etc... – nombre de bits de l’Unité Arithmétique et Logique

– Unités d’entrée/sortie : Transferts d’information de et vers l’ordinateur. Mémoires – dimension de l’espace adressable

de masse ou secondaires : disquettes, CD-ROM, DVD, clefs USB, etc... – fréquence de fonctionnement (nombre de cycles par seconde)

Unite

– jeu d’instructions

Unite Unite

d’E/S d’E/S d’E/S

– architecture interne

bus peripherique

– puissance en Mips (Millions d’instructions par seconde) et en Mflops (Millions

d’opérations flottantes par seconde)

Interfaces E/S

Types de processeurs

Processeur Memoire

(controleurs)

– processeurs “universels” : Exemples Pentium, Athlon, PowerPC, ...

bus systeme

– micro-contrôleurs : interfaces d’E/S intégrés.

Les unités d’entrée/sortie sont reliées au processeur par l’intermédiaire d’interfaces. – DSP : processeurs spécialisés en traitement du signal

L’accès se fait par des adresses mémoires.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –5– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture d’un ordinateur UPS IUP SI - L3 Architecture d’un ordinateur

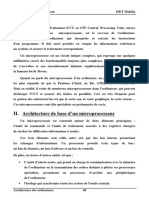

Architecture multi-niveaux

Bus de communication

– Niveau Applications :

Un bus est un ensemble de fils qui assurent la transmission d’informations de

– Niveau 6 : Langages d’applications (Matlab, langage G, mapple, ...)

même type véhiculées en parallèle. On distingue trois types de bus :

– Niveau 5 : Langages évolués (Pascal, Ada, C, ...)

– Bus de données : bidirectionnel. Nombre de lignes égal à la capacité de – Niveau 4 : Langage d’assemblage (assembleur)

traitement de l’UAL. – Niveau Système :

– Bus d’adresses : unidirectionnel. Permet de sélectionner les informations dans un – Niveau 3 : Système d’exploitation (Unix, Windows, ...)

espace mémoire. Pour un bus de m bits, on peut distinguer 2m adresses. – Niveau 2 : Macro-machine (langage machine)

– Bus de commande : assure la synchronisation des flux d’informations sur les bus – Niveau 1 : Micro-machine (micro-instructions)

de données et d’adresses. – Niveau 0 : Machine physique (circuits logiques)

Un bus est une ressource partagée (par les différents boitiers d’E/S notamment). Chaque niveau fait appel aux services du niveau inférieur.

Une fonction de décodage d’adresse permet de sélectionner le boitier pouvant

Machine virtuelle : L’utilisation d’une machine à un niveau donné peut faire

accéder au bus à un instant donné.

abstraction des niveaux inférieurs.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –6– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Codage des informations UPS IUP SI - L3 Codage des informations

Codage des informations Codage des entiers relatifs (signés) sur n bits

– Codage par signe et valeur absolue : le bit le plus à gauche ( bit le plus

– Les informations que peut traiter un ordinateur sont des suites de bits (0 ou 1), un

significatif) représente le signe du nombre (1 : nombre négatif).

codage est donc nécessaire pour passer des données symboliques et

X

n−2

instructions d’un programme à une forme exploitable par l’ordinateur. S(A) = (−1)an−1 ai 2i

– L’objet de taille minimale accessible est un octet (byte en anglais) soit 8 bits. i=0

Le codage de données et d’instructions utilise donc des multiples d’octets. – Codage par complément à 2 : les nombres négatifs sont représentés par leur

– Notation hexadécimale (base 16 :{0,1,...,E,F}) : permet de représenter de complément à 2. Celà revient a donner un poids négatif au bit le plus significatif.

manière plus synthétique un ensemble de bits. 4 bits peuvent être représentés X

n−2

par un seul symbole. Ex : 3EF5h=0011111011110101b Z(A) = −an−1 2n−1 ai 2 i

– Codage des caractères : On utilise essentiellement le codage ASCII qui permet

i=0

– Codage par excédent : Les nombres sont décalés d’une valeur e (en général

de coder 128 caractères en utilisant 7 bits. Les codes 0 à 31 sont des codes de

e = 2n−1 ou e = 2n−1 − 1).

contrôle.

– Codage des nombres : le codage varie suivant qu’il s’agit d’entiers naturels X

n−1

χe (A) = ai 2i − e

(non-signés), d’entiers relatifs ou de réels. i=0

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –9– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Codage des informations UPS IUP SI - L3 Codage des informations

Codage des entiers naturels (non-signés) sur n bits

On utilise une numération positionnelle : chaque symbole du code à un poids qui Codage des réels en virgule fixe

dépend de sa position. Les poids sont croissants de la gauche vers la droite en

Pour un codage sur n bits, on réserve m bits pour coder la partie fractionnaire.

puissance de 2 en binaire (puissance de 10 en décimal et de 16 en hexadécimal)

Soit m le nombre de bits codant la partie fractionnaire du réel :

Soit A = an−1 an−2 ...a1 a0 un code binaire, la valeur décimale N (A) de l’entier X

n−2

Φm (A) = −an−1 2 n−1−m

+ ai 2i−m = 2−m Z(A)

naturel représenté par A peut être calculé par :

i=0

X

n−1

N (A) = ai 2i Exemple : Soit A=3E20h représentant un réel codé sur 16 bits avec m =7:

i=0

Φ7 (A) = 124, 25

Exemple : le code 0101 0111b (en hexadécimal : 57h) représente l’entier 87 codé

sur 8 bits.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –10– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Codage des informations UPS IUP SI - L3 Codage des informations

Codage des réels en virgule flottante

Norme IEEE P754 Codage des caractères. Code ASCII sur 7 bits

En simple précision, le codage se fait sur 32 bits : code 0 1 2 3 4 5 6 7 8 9 A B C D E

0x00 NUL SOH STX ETX EOT ENQ ACK BEL BS HT LF VT NP CR SO

31 30 ... 23 22 ... 0

0x10 DLE DC1 DC2 DC3 DC4 NAK SYN ETB CAN EM SUB ESC FS GS RS

S E F

0x20 SP ! ” # $ % & ’ ( ) * + , - .

– Le bit S code le signe du nombre (1 pour un nombre négatif). 0x30 0 1 2 3 4 5 6 7 8 9 : ; < = >

– La mantisse est recadrée entre 1 et 2 (2 exclu) avant d’être codée. Elle est de la 0x40 @ A B C D E F G H I J K L M N

forme : m = 1, f . Seule la partie fractionnaire f est codée et ceci sur 23 bits 0x50 P Q R S T U V W X Y Z [ \ ] ˆ

0x60 ‘ a b c d e f g h i j k l m n

(Φ23 (F )).

0x70 p q r s t u v w x y z { — } ˜

– L’exposant est codée sur 8 bits par excédent 127.

Les caractères 0 a 31 et 127 sont des caractères de contrôle.

Le code A=S|E|F représente le réel :

Le 8ème bit peut avoir divers usages :

R(A) = (−1)S (1 + Φ23 (F ))2χ127 (E) – contrôle de parité

– définition de caractères étendus (accentués par exemple).

Exemple : le nombre 1 a pour code : 3F800000h

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –13– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Codage des informations UPS IUP SI - L3 Codage des informations

Caractères de contrôle et propriétés du code ascii

Codage des instructions ➯ Les lettres de l’alphabet sont dans l’ordre croissant et se suivent : Un tri

alphabétique se ramène à un tri numérique.

– Types d’instructions :

– Instructions de traitement. ➯ Le passage de minuscule en majuscule et vice-versa se fait simplement en

– Instructions de chargement/rangement. inversant le bit 5 du code (soit + ou - $20)

– Instructions de contrôle d’exécution. ➯ Le passage d’un chiffre à son code ASCII consiste à rajouter $30 à ce chiffre.

– Format : dépend du type d’instruction. Exemples :

Quelques caractères de contrôles :

– traitement :

NUL absence de caractère SOH début d’entète STX début de texte

code opération adresse 1er opérande adresse 2ème opérande adresse résultat

ETX fin de texte EOT fin de transmission ENQ interrogation

– chargement/rangement :

ACQ accusé réception BEL sonnette BS retour arrière

code opération adresse registre adresse mot en mémoire HT tabulation horizontale LF ligne suivante VT tabulation verticale

– contrôle : FF page suivante CR retour chariot NAK reçu avec erreur

code opération code condition adresse de branchement SYN synchronisation CAN annulation SUB substitution

ESC échappement FS séparateur de fichier GS séparateur de groupe

RS séparateur d’article US séparateur d’unité DEL effaçer

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –14– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité Arithmétique et Logique UPS IUP SI - L3 Unité Arithmétique et Logique

Unité Arithmétique et logique

Au coeur du processeur, l’UAL effectue le traitement des informations. Additionneur binaire

E1 E2

– Demi-additionneur 1 bit :

n n

s=a⊕b r = a.b

– Additionneur complet 1 bit :

f

m UAL p ....... si = a i ⊕ b i ⊕ r i ri+1 = ai .bi + ((ai ⊕ bi ).ri )

indicateurs

– Additionneur n bits à propagation de retenue :

n a n−1 bn−1 a 1 b1 a 0 b0

S rn rn−1 r2 r1 r0

add add add

C’est un circuit combinatoire qui produit un résultat (S) sur n bits fonction des

s s1 s0

données présentes sur ses entrées (E1 et E2) et de la fonction à réaliser (f) et met à

jour des indicateurs.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –17– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité Arithmétique et Logique UPS IUP SI - L3 Unité Arithmétique et Logique

Fonctions de l’UAL

L’UAL permet de réaliser différents types d’opérations sur des donnéees de la forme

Addition d’entiers naturels

S=f(E1,E2) :

– Addition d’entiers codés sur n bits :

– Des opérations arithmétiques : additions, soustractions, ...

– Des opérations logiques : ou, et, ou exclusif, ...

N (S) + 2n rn = N (A) + N (B)

– Des décalages et rotations.

Le résultat est exact si rn = 0 (pas de retenue).

Elle met par ailleurs à jour des indicateurs en fonction du résultat de l’opération

Soit le bit C (Carry) du registre de condition égal à 0 (C=rn ).

effectuée :

– Addition d’entiers codés sur k × n bits (précision multiple).

– Z : indicateur mis à 1 si le résultat de l’opération est 0. Séquence de k additions en commençant par les poids faibles et en tenant

– N : indicateur mis à 1 pour un résultat négatif (bit le plus à gauche égal à 1). compte de la retenue (bit C) du niveau précédent.

– C : mis à 1 en cas de retenue ou débordement en contexte non signé.

– V : mis à 1 en cas de débordement en contexte signé.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –18– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité Arithmétique et Logique UPS IUP SI - L3 Unité Arithmétique et Logique

Opérations logiques

Addition d’entiers relatifs Une Unité Arithmétique et Logique permet d’exécuter les fonctions logiques de

– On utilise un codage par complément à 2. base : ET (AND), OU (OR), OU EXCLUSIF (XOR), PAS (NOT). Ces fonctions, pour

Si le mot-code X représente le nombe Z(X), on peut écrire : des mots de n bits sont effectués en parallèle. Elles sont obtenus par juxtaposition

Z(X) = N (X) − 2 xn−1 n

d’opérateurs logiques 1 bit :

– Soit A et B les codes des nombres Z(A) et Z(B) et S le code du résultat tel ai

que Z(S) = Z(A) + Z(B). On montre que le résultat de Z(A) + Z(B) est bi

le même que le résultat de N (A) + N (B) si

V = rn−1 ⊕ rn = 0

– L’addition d’entiers relatifs est donc identique à celle d’entiers naturels. La seule

f 0 1 2 3

chose qui change, c’est l’indicateur qui permet de savoir si le r ésultat est exact (C

si

en non-signé, V en signé).

La commande f du multiplexeur permet de sélectionner l’opération à effectuer.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –21– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité Arithmétique et Logique UPS IUP SI - L3 Unité Arithmétique et Logique

Soustraction

– Entiers naturels : Opérations de décalage

Soit B̃ le complément à 2 de B. N (B̃) = 2n − N (B). Si on additionne A et B̃

Les opérations de décalage sont obtenus au moyen d’un multiplexeur situé à la

on obtient S tel que

sortie de l’Unité Arithmétique et Logique. Suivant la commande f , le résultat S peut

N (S) + 2n rn = N (A) + N (B̃) = N (A) − N (B) + 2n Le résultat est

ne pas être décalé (f = 0), ou être décalé d’un bit vers la droite (f = 1) ou vers la

celui de la soustraction si r n = 1. Dans ce cas, on calcule C = r¯n .

gauche (f = 2).

– Entiers relatifs :

s n−1 s1 s0

Z(B̃) = −Z(B) d’ou : Z(A) − Z(B) = Z(A) + Z(B̃). Le résultat est s2

s n−2

exact si celui de l’addition est exact soit si V=0.

– En résumé, la soustraction se traite de la manière suivante : f 0 1 2 0 1 2 0 1 2

– Prendre le complément à 2 de B

dn−1 d1 d0

– l’ajouter à A

– Vérifier le résultat : C=0 en contexte non-signé, V=0 en contexte signé

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –22– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Chemin de données UPS IUP SI - L3 Chemin de données

Multiplexeur

Unité de commande

Seule la ligne correspondante au code de sélection se retrouve en sortie.

– Automate qui élabore les ordres pour assurer l’exécution de chaque instruction.

– Peut être modélisé par une machine à états synchrone.

s0 s1

– Machine de Moore : la fonction de sortie ne dépend que de l’état courant.

fonction de sortie sorties

entrees fonction etat suivant

e0

registre

etat courant etat suivant

e1

horloge

– Entrées : code instruction et indicateurs d’état (C, V, etc...). e2

– Sorties : signaux de commande pour piloter le chemin de données.

e3

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –25– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Chemin de données UPS IUP SI - L3 Chemin de données

Chemins de données

Mémoire

– Registre : Elément de base constitué de n bascules de type D. Permet de Donnee

conserver des mots-codes de n bits.

E n

LR R WR RD

S n

L’activation du signal LR provoque la copie de la donnée présente sur le bus E

dans le registre R.

– Bus direct entre registres :

n

L Rs Rs

n

L Rd Rd

n

Adresse

Decodage

L’activation du signal LRd provoque la copie de la donnée du registre Rs dans le

registre Rd , opération notée : Rd ← Rs .

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –26– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Chemin de données UPS IUP SI - L3 Chemin de données

Transfert bus → registre

bus

RISC et CISC

LR1 registre 1 LR2 registre 2 Memoire

– Processeurs de type CISC (Complex Instruction Set Computer) : nombreuses

WR

Adresse instructions de la plus simple à la plus complexe. Formats très variables

(non-homogène). Décodeur d’instructions et unité de commande complexes.

Transfert registre → bus

Nombreux modes d’adressage. Faible nombre de registres

registre 2 registre 3

registre 1 Exemples : familles Intel 80x86 et Motorola 680x0.

– Processeurs de type RISC (Reduced Instruction Set Computer) : Jeu

E 0 1 d’instructions réduit mais exécution plus rapide (moins de cycles d’horloge).

mux

Homogénéité du format et régularité de l’exécution. Décodeur simple mais

bus

compilateur plus complexe. Nombreux registres.

Exemples : PowerPC, Alpha, MIPS, Sparc, etc..

Memoire

RD

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –29– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Chemin de données UPS IUP SI - L3 Chemin de données

Différentes Architectures

– Choix pour le stockage transitoire des données : Von Neumann vs Harvard

– accumulateurs (registres spécialisés) Architecture de Von Neumann

– pile bus donnees

– registres généraux CPU

Memoire

– pas de stockage

bus adresses

– Sources de données pour l’UAL :

– registres/mémoire Architecture de Harvard

– registres/registres instructions donnees

– mémoire/mémoire memoire

CPU

memoire

instructions donnees

➱ 2 types d’architectures : adresses adresses

instructions donnees

– CISC : accumulateurs, calculs registres/mémoire

– RISC : registres généraux, calculs registres/registres

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –30– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Exemple d’architecture UPS IUP SI - L3 Exemple d’architecture

Exemple d’architecture d’un processeur Fonctions de l’UAL

Le processeur pris comme exemple d’étude comporte : f S fonction f S fonction

– Une Unité Arithmétique et Logique traitant des mots de 16 bits.

0 0 mise à zéro 8 E1 complément à 1

– Une banque de 16 registres généraux de 16 bits reliés par deux bus de donnés

1 E1+E2 addition 9 E1.E2 ET logique

Yi et Yj aux entrées E1 et E2 de l’UAL

2 E1+E2+C addition avec retenue A E1+E2 OU logique

– Un bus de données bidirectionnel de 16 bits DBUS

3 E1-E2 soustraction B E1 ⊕ E2 OU exclusif

– Un bus d’adresses de 12 bits ABUS (Espace adressable : 8 Ko)

←−

4 E1-E2+C soustraction avec retenue C E1 décalage à gauche

– Un registre PC contenant l’adresse de la prochaine instruction à exécuter.

−→

– Un registre IR contenant le code de l’instruction à exécuter 5 E1+1 incrémentation D E1 décalage à droite

←−

– Un registre SP contenant l’adresse du sommet de la pile système 6 E1-1 décrémentation E c E1 rotation à gauche via C

−→

– Un registre d’indicateurs d’états I. 7 -E1 négation F E1 c rotation à droite via C

– Une unité de commande générant les divers signaux de contrôle.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –33– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Exemple d’architecture UPS IUP SI - L3 Exemple d’architecture

WRF D in

Jeu d’instructions j

Le jeu d’instructions que l’on veut fournir au processeur est divis é en 4 familles : R[0] 0

16

1. Instructions de traitement : opérations arithmétiques et logiques effectuées par R[1] Yj

l’UAL entre registres (pas d’opérations directement avec la mémoire) 15

Decodage

2. Instructions de chargement/rangement : instructions permettant des transferts

0

registre/registre et registre/mémoire. 16

Yi

3. Instructions de branchement : branchements conditionnels et inconditionnel.

R[15] 15

4. Instructions pour la programmation modulaire : gestion de la pile syst ème, 4

i

sous-programmes et interruptions.

Banque de registres

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –34– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Exemple d’architecture UPS IUP SI - L3 Exemple d’architecture

Recherche et décodage des instructions

– Recherche de l’instruction en mémoire (état R1) :

– L’adresse de l’instruction dans PC est sur le bus d’adresses ABUS

Machine à états pour la recherche d’instructions

– L’activation du signal RD , met sur DBUS le code de l’instruction

– Le signal LR charge le contenu de DBUS dans le registre IR

– Le signal LP C charge le compteur PC avec sa valeur incrémenté de 1 pour R1

préparer la recherche de l’instruction suivante.

H IR<−M[PC], PC<− PC+1

Pendant l’état R1, les sorties actives sont RD , LR et LP C .

Le signal d’horloge fait passer l’unité de commande de l’état R1 à l’état R2. Les R2

opérations : IR ← M [P C] et P C ← P C + 1 (notation RTL) sont effectives

au moment du changement d’état.

– Décodage de l’instruction (état R2) : L’analyse du contenu de IR par l’unité de

commande permet de générer les signaux permettant d’exécuter l’instruction

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –37– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Exemple d’architecture UPS IUP SI - L3 Exemple d’architecture

DBUS

16

Registres

Memoire

E1 E2

4

f

S

Z N V C

I

-

LPC

12

L IR LPC

WR PC ABUS

Unite RD

de

Commande SP

16

WR RD

IR

+1

+

H 12

L IR Processeur V.1

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –38– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de traitement UPS IUP SI - L3 Instructions de traitement

Format des instructions de traitement

16 DBUS

WRF 16

4 D in

j

16 Yj

Les instructions de traitement sont effectuées par l’Unité Arithmétique et Logique. Registres

Ce sont des opérations du type : R[i] ← f (R[i], R[j]) codées sur 16 bits suivant 16 Yi Memoire

4

i

le format (appelé format a) : 4 E1 E2

4

f

S

15...12 11...8 7...4 3...0 Z N V C

LI EUAL

c.o. c.c.o i j

LPC

12

– c.o : code opératoire. Egal à 0 pour toutes les instructions de traitement L IR

WR

LPC

PC ABUS

Unite RD

(instruction générique). de i

j LSP

Commande SP

– c.c.o. : complément au code opératoire. Permet de sélectionner l’opération à

f

EUAL

LI

effectuer. Signal f de l’UAL.

16

WRF WR RD

IR

– i : indice du registre contenant le 1er opérande +1

– j : indice du registre contenant le second opérande +

H

12

L IR Processeur V.2

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –41– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de traitement UPS IUP SI - L3 Instructions de traitement

Jeu d’instructions de traitement Analyse des instructions de traitement

c.o. c.c.o mnémonique fonction commande actions

0 0 clr Ri R[i] ← 0 i=IR(7..4) Yi ← R[i], E1 ← Yi

0 1 add Ri,Rj R[i] ← R[i] + R[j] j=IR(3..0) Yj ← R[j], E2 ← Yj

0 2 adc Ri,Rj R[i] ← R[i] + R[j] + C f=IR(11..8) S ← f (E1, E2)

0 3 sub Ri,Rj R[i] ← R[i] − R[j] EU AL = 1 DBU S ← S , Din ← DBU S

0 4 sbc Ri,Rj R[i] ← R[i] − R[j] − C WRF = 1 R[i] ← Din

0 5 inc Ri R[i] ← R[i] + 1 LI = 1 maj indicateurs

0 6 dec Ri R[i] ← R[i] − 1

0 7 neg Ri R[i] ← −R[i] Machine à états

0 8 comp Ri R[i] ← R[i]

0 9 and Ri,Rj R[i] ← R[i].R[j] R1

0 A or Ri,Rj R[i] ← R[i] + R[j]

0 B xor Ri,R[j] R[i] ← R[i] ⊕ R[j] H IR<−M[PC], PC<− PC+1

←−−

0 C lsl Ri R[i] ← R[i]

−

−→ R2

0 D lsr Ri R[i] ← R[i]

←−− R[i]<−f(R[i],R[j])

0 E rol Ri R[i] ← R[i] via C E0

−

−→ c.o.=0 H

0 F ror Ri R[i] ← R[i] via C H

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –42– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de transfert UPS IUP SI - L3 Instructions de transfert

Transferts de données

– Opérations de l’UAL : registres → registres

Modifications de l’architecture

– Transferts : Pour effectuer les instructions de transfert qui viennent d’être définies, des

– registre → registre améliorations doivent être apportées à l’architecture de notre processeur :

– registre → mémoire

– Il faut pouvoir connecter Ri et Rj en sortie sur DBUS. On rajoute pour cel à les

– mémoire → registre

portes 3 états commandées par ERi et ERj .

Modes d’adressage – Le bus d’adresses ABUS doit pouvoir être alimenté par Rj (adressage indirect) où

par les 12 bits de poids faible du registre IR (adressage absolu). On rajoute pour

– Adressage direct de registre : R[i]

← R[j].

celà le multiplexeur muxAd.

– Adressage absolu implicite : R[0] ← M [adresse] ou M [adresse] ← R[0]

– Adressage indirect : R[i] ← M [R[j]] ou M [R[j]] ← R[i] Ceci conduit à la version 3 de notre processeur.

– Adressage immédiat : R[i] ← valeur

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –45– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de transfert UPS IUP SI - L3 Instructions de transfert

Formats des instructions de transfert DBUS

WRF 16

16

15...12 11...8 7...4 3...0 E Ri E Rj

4 D in

j

a: c.o. 0 i j 16 Yj

Registres

15...12 11...0 Memoire

16 Yi

b: c.o. adresse i

4

4 E1 E2

4

15...12 11...8 7...4 3...0 f

S

c: c.o. 0 i 0 Z N V C EUAL

LI

valeur 5

2

Jeu d’instructions

IR(11..0)

LPC 1

12

L IR LPC

WR PC 0 ABUS

Unite

format c.o. mnémonique fonction RD

de i

j LSP SP

a 1 move Ri,Rj R[i] ← R[j] Commande f

muxAd

EUAL

b 2 load adresse R[0] ← M [adresse] LI

16

WRF WR RD

b 3 store adresse M [adresse] ← R[0] IR muxAd

E Ri

a 4 load Ri,[Rj] R[i] ← M [R[j]] E Rj

+1

a 5 store [Rj],Ri M [R[j]] ← R[i]

+

c 6 load Ri,valeur R[i] ← valeur H

L IR 12

Processeur V.3

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –46– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de transfert UPS IUP SI - L3 Instructions de transfert

Analyse des instructions (1)

R1

H IR<−M[PC], PC<− PC+1

E1 : R[i] ← R[j] R2

R[i]<−f(R[i],R[j])

– On sélectionne R[j] et on le relie à DBUS : j=IR(3..0), ERj

=1 E0

c.o.=0

H

– On sélectionne R[i] et on copie DBUS dedans : i=IR(7..4), WRF = 1 H

R[i]<−R[j]

E1

E2 : R[0] ← M [adresse] c.o=1

– On place adresse contenue dans IR sur ABUS : muxAd=1 c.o.=2

E2

R[0]<−M[adresse]

– on place la donnée (M (adresse)) sur DBUS : RD=1

M[adresse]<−R[0]

E3

– On sélectionne R[0] et on copie DBUS dedans : i=0, WRF =1 c.o.=3

E3 : M [adresse] ← R[0] R[i]<−M[R[j]]

E4

– On place adresse contenue dans IR sur ABUS : muxAd=1 c.o.=4

– On sélectionne R[0] et on le connecte à DBUS : i=0, ERi = 1 E5

M[R[j]<−R[i]

c.o.=5

– On copie DBUS dans M [adresse] : WR=1

R[i]<−M[PC], PC<−PC+1

c.o=6 E6

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –49– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de transfert UPS IUP SI - L3 Instructions de transfert

Analyse des instructions (2)

E4 : R[i] ← M [R[j]]

Résumé des signaux de commande :

– On sélectionne R[j] et on le connecte à ABUS : j=IR(3..0), muxAd=2

– On place M[R[j]] sur DBUS : RD=1 – E0 : muxAd=0, i=IR(7..4), j=IR(3..0), f=IR(11..8), EU AL = 1, WRF = 1,

– On sélectionne R[i] et on copie DBUS dedans : i=IR(7..4), WRF =1 LP C = 1

E5 :M [R[j]] ← R[i] – E1 : j=IR(3..0), ERj = 1, i=IR(7..4), WRF = 1

– On sélectionne R[i] et on le connecte à DBUS : i=IR(7..4), ERi =1 – E2 : muxAd=1, RD=1, i=0, WRF = 1

– On sélectionne R[j] et on le connecte à ABUS : j=IR(3..0), muxAd=2 – E3 : muxAd=1, i=0, ERi = 1, WR=1

– On effectue l’écriture en mémoire (M [ABU S] ← DBU S ) : WR=1 – E4 : j=IR(3..0), muxAd=2, RD=1, i=IR(7..4), WRF = 1

E6 :R[i] ← valeur – E5 : i=IR(7..4), ERi = 1, j=IR(3..0), muxAd=2, WR=1

– PC est connecté à ABUS, on connecte M[PC] à DBUS : muxAd=0, RD=1 – E6 : muxAd=0, RD=1, i=IR(7..4), WRF = 1, LP C = 1

– On sélectionne R[i] et on écrit dedans : i=IR(7..4), WRF =1

– On incrémente PC pour l’instruction suivante : LP C =1

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –50– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de branchements UPS IUP SI - L3 Instructions de branchements

Instructions de ruptures de séquence

Principe : Si une condition est vérifiée : sauter à une adresse spécifiée

Sinon : continuer en séquence.

Interprétation des conditions de branchement

Généralement, une instruction de branchement conditionnel est précédé d’une

vrai

cond?

faux opération de comparaison ente 2 registres c’est à dire une soustraction : A-B.

Les conditions de saut peuvent alors être interprétées ainsi :

suite

– beq : branchement si A=B (A-B=0 d’ou Z=1)

– blo : branchement si A < B en contexte non-signé

– Condition de branchement : basée sur les indicateurs mis à jour par l’UAL

– blt : branchement si A < B en contexte signé

(Z,N,V,C).

– bls : branchement si A ≤ B en contexte non-signé

– Adresse de branchement : on veut coder l’instruction sur un seul mot-code (16

– ble : branchement si A ≤ B en contexte signé

bits). Or, c.o : 4 bits, adresse : 12 bits. Il faudrait un c.o. différent pour chaque test.

Solution choisie : On utilise 3 bits (c.c.o) pour coder le test (8 possibilit és) et on

ne code qu’un déplacement relatif sur 9 bits (-256 à +255).

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –53– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de branchements UPS IUP SI - L3 Instructions de branchements

Modifications de l’architecture

Format d’instruction :

L’instruction de branchement (instruction générique) peut être exécuté de la manière

15...12 11...9 8...0

format c :

c.o. c.c.o deplacement suivante :

(deplacement est un entier relatif codé sur 9 bits.)

– On calcule la condition à l’aide d’un circuit combinatoire :

Z N V C

Jeu d’instructions :

c.o. c.c.o. mnémonique condition c.c.o.=IR(9..11)

Calcul condition

7 0 bra deplacement 1

7 1 bns deplacement N

7 2 bvs deplacement V condition

7 3 beq deplacement Z Ce calcul est fait dans l’unité de commande.

7 4 blo deplacement C

– On rajoute la possibilité d’additionner PC avec les bits 0..9 de IR (déplacement) :

7 5 blt deplacement N⊕V

7 6 bls deplacement C+Z

c’est le rôle du multiplexeur mux1.

7 7 ble deplacement Z +(N ⊕ V) – Le déplacement étant un entier relatif sur 9 bits, on doit l’étendre à 12 bits pour

conserver l’information de signe (circuit EXT).

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –54– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de branchements UPS IUP SI - L3 Programmation modulaire

16 DBUS

Programmation modulaire

WRF 16

E Ri E Rj

j

4 D in Sous-programmes, fonctions.

16 Yj

Registres

Principe : Interrompre le programme en cours pour exécuter un sous-programme

Memoire

puis revenir au programme en cours (programme appelant).

16 Yi

4

i

4 E1 E2

4 Instruction

f

S

Sous−Programme

Z N V C EUAL

LI jsr

5

2

IR(11..0)

LPC 1

12

L IR LPC

WR PC 0 ABUS

Unite RD rts

de i

j LSP SP

Commande f Programme

muxAd appelant

EUAL

LI IR(8..0)

16

WRF WR RD

IR

Nécessite de stocker l’adresse de retour.

EXT

muxAd +1

E Ri

E Rj 0 1 mux1

mux1

Registre spécialisé : un seul niveau de sous-progamme possible.

+

H

L IR 12

Processeur V.4 ➱ Utilisation d’une structure de données de type pile

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –57– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Instructions de branchements UPS IUP SI - L3 Programmation modulaire

Analyse de l’instruction

Si condition=1, l’exécution de l’instruction peut être représentée, en notation RTL, Pile système

par : PC ← PC+déplacement.

Structure de données de type LIFO implémentée en mémoire.

Les signaux de commande sont donc : mux1=1 et LP C = 1.

Branchement à un sous-programme : empilage de l’adresse de retour

Dans le cas contraire, il n’y a rien à faire.

Retour du sous-programme : dépilage de l’adresse de retour

On peut représenter ceci par la machine à états :

Pointeur de pile : registre SP contenant l’adresse du sommet de la pile.

R1

Implémentation de la pile : adresses hautes (Ex : FFFh) et empilage vers les

H IR<−M[PC], PC<− PC+1

adresses basses.

R2

R[i]<−f(R[i],R[j])

c.o.=0 E0 ...

H

H FFD SP

FFE SP valeur 2 SP

FFF valeur 1 valeur 1 valeur 1

E7

PC<−PC+deplacement empilage depilage

c.o=7

condition=1

c.o.=7 et condition=0

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –58– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Programmation modulaire UPS IUP SI - L3 Programmation modulaire

16 DBUS

WRF 16

E Ri E Rj E PC

Formats des instructions de pile

4 D in

j

16 Yj

Registres

15...12 11...8 7...4 3...0

16 Yi Memoire

a: c.o. 0 i 0 i

4

4 E1 E2

4

15...12 11...0 f

S

b: c.o. adresse Z N V C

LI EUAL

5

2

Jeu d’instructions LPC

L IR

mux3 0 1

IR(11..0)

1

12

LPC

WR PC 0 ABUS

format c.o. mnémonique fonction Unite RD

de i 3

b 8 jsr adresse saut au sous-programme adresse Commande

j LSP SP

f

E IR muxAd

a 9 rts retour d’un sous-programme EUAL

LI IR(7..0)

16

a A push Ri M [SP ] ← R[i], SP ← SP + 1 WRF WR RD

IR muxAd +1

EXT

−1

E Ri

a B pop Ri SP ← SP + 1, R[i] ← M [SP ] E Rj mux1

mux2 0 1 0 1 2

mux1

mux2

E IR mux3 +

H E PC

12

L IR Processeur V.5

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –61– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Programmation modulaire UPS IUP SI - L3 Programmation modulaire

Analyse des instructions (1)

jsr adresse

Modification de l’architecture

L’instruction doit réaliser, en notation RTL :

Pour implémenter les instructions pour la programmation modulaire, il faut :

– Sauvegarde de l’adresse de retour sur la pile M [SP ] ← P C et décrémentation

– Pouvoir relier SP à ABUS : rajout de l’entrée 3 de muxAd. de la pile : SP ← SP − 1.

– Pouvoir incrémenter et décrémenter SP : rajout de mux2 et d’une entrée sur Les signaux de commande sont donc : muxAd=3, EP C = 1, WR=1 ainsi que :

mux1. mux1=2, mux2=1, LSP = 1 et sont générés dans l’état E81.

– Pouvoir charger où ranger PC en mémoire : rajout de mux3 et de la porte 3 états – Branchement à la 1ère instruction du sous-progammme : P C ← IR(11..0). Le

commandée par EP C . transit de IR vers PC se fait par DBUS. Il faut pour celà générer les commandes :

– Pouvoir connecter la sortie de IR sur DBUS : rajout de la porte 3 états mux3=1, EIR = 1 et LP C = 1. C’est fait dans l’état E82.

commandée par EIR . rts L’instruction doit

– Incrémenter SP : mux1=0, mux2=1, LSP = 1 (état E91)

– Mettre M[SP] dans PC : muxAd=3, RD=1, mux3=1, LP C = 1 (état E92)

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –62– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Programmation modulaire UPS IUP SI - L3 Interruptions

Interruptions matérielles

Analyse des instructions (2)

– Une interruption consiste à interrompre le programme en cours (tàche de fond)

push Ri : Pour réaliser M [SP ] ← R[i] il faut :

pour exécuter un sous-programme totalement indépendant.

– Sélectionner R[i] : i=IR(7..4), et le connecter à DBUS : ERi = 1,

– Une interruption matérielle est provoquée par un événement externe provenant

– connecter SP à ABUS : muxAd=3,

d’une unité périphérique (Exemple : appui d’une touche du clavier).

– envoyer un ordre d’écriture à la mémoire : WR=1,

– Elle se matérialise sur notre processeur par l’activation d’une ligne reli é à l’unité

– décrémenter SP : mux1=2, mux2=1, LSP = 1.

de commande du processeur (ligne int).

pop Ri : Pour réaliser R[i] ← M [SP ] il faut :

– Le sous programme à exécuter est localisée à une adresse fixée par le

– incrémenter SP : mux1=0, mux2=1, LSP = 1 puis :

concepteur du système (vecteur d’interruption).

– connecter SP à ABUS : muxAd=3,

– L’interruption du programme ne peut se faire qu’à la fin de l’exécution en cours

– envoyer l’ordre de lecture à la mémoire : RD=1,

(retour vers l’état R1).

– sélectionner R[i] et charger DBUS dedans : i=IR(7..4), WRF =1

– Le registre d’indicateurs (I) doit être sauvegardé sur la pile avant le départ en

Cette instruction prend 2 cycles (états EB1 et EB2).

interruption et restauré au retour.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –65– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Programmation modulaire UPS IUP SI - L3 Interruptions

Machine à états

Masque d’interruptions

R1

– Le départ en interruption consiste à charger le pointeur de programme PC avec

H IR<−M[PC], PC<− PC+1

l’adresse du sous programme d’interruption après la fin d’une instruction et avant

R2 le retour à l’état R1 (recherche de la prochaine instruction).

R[i]<−f(R[i],R[j])

c.o.=0

E0

H – La ligne de demande d’IT (int) n’est désactivée qu’à la fin du SP d’IT. Il faut

H

donc rajouter un indicateur indiquant que l’on est en train de traiter une demande

d’IT. C’est le rôle de l’indicateur IE.

M[SP]<−PC, SP<−SP−1 PC<−adresse

jsr

c.o=8 E81 E82

– Si IE=1 et int=1, on se déroute vers le SP d’IT et on met IE à 0.

SP<−SP+1 PC<−M[SP]

c.o=9 E91 E92

rts

Sinon (IE=0 ou int=0), on traite les instructions normalement.

EA

M[SP]<−R[i], SP<−SP−1 push – A la fin du SP d’IT, on remet à 1 l’indicateur IE pour pouvoir traiter la prochaine

c.o=A

SP<−SP+1 R[i]<−M[SP] pop

interruption.

c.o=B EB1 EB2

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –66– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Interruptions UPS IUP SI - L3 Interruptions

Modification de l’architecture

Instructions supplémentaires

– on rajoute la ligne d’entrée int

format c.o. mnémonique fonction

– on rajoute le bit IE au registre d’indicateurs I. Ce bit peut être mis à 1 (signal SIE)

a C sei Autorisation interruptions

où à 0 (signal CIE) a D cli Interdiction interruptions

– on connecte le registre I au bus de données en lecture et écriture : rajout du a E rti retour d’interruption

multiplexeur muxI et de de la porte 3 états EI .

– on rajoute une entrée au multiplexeur muxAd fixant l’adresse du vecteur Analyse des instructions

d’interruptions. instruction notation RTL Etat signaux de commande

“Instruction” d’interruption sei IE ← 1 EC SIE = 1

cli IE ← 0 ED CIE = 1

rti SP ← SP + 1 EE1 mux1=0, mux2=1, LSP =1

notation RTL Etat signaux de commande

I ← M [SP ], SP ← SP + 1 EE2 muxAd=3, RD=1, muxI=1, LI =1

M [SP ] ← P C , SP ← SP − 1 I1 muxAd=3, EP C = 1, WR=1 mux1=2, mux2=1, LSP = 1

mux1=0, mux2=1, LSP =1

M [SP ] ← I , SP ← SP − 1 I2 muxAd=3, EI = 1, WR=1 mux1=2, mux2=1, LSP = 1

P C ← M [SP ] EE3 muxAd=3, RD=1, mux3=1, LP C =1

P C ← addIT , IE ← 0 I3 muxAD=4, RD=1, mux3=1, LP C = 1, CIE=1

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –69– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Interruptions UPS IUP SI - L3 Interruptions

16 DBUS

Machine à états

WRF 16

E Ri E Rj E PC

PC<−addIT I<−M[SP] PC<−M[SP]

j

4 D in IE<−0 SP<−SP−1

16 Yj

I3 I2 SP<−SP−1 I1

Registres

int=1 et IE=1

Yi Memoire

16 int=0 ou IE=0

4

i

R1

4 E1 E2

4

muxI f

1 0

S H

IR<−M[PC], PC<− PC+1

IE Z N V C AddIT

LI EUAL 4

5

2 R2

EI C IE

mux3

IR(11..0) R[i]<−f(R[i],R[j])

LPC 0 1 1

12 E0

L IR LPC c.o.=0

S IE

WR PC 0 ABUS H

Unite RD

H

de i 3

j LSP SP

Commande f

E IR muxAd

EUAL IE<−1

LI IR(8..0)

16 EC

WRF WR RD c.o=C

IR muxAd +1

EXT

−1

E Ri IE<−0

E Rj mux1

mux2 0 1 0 1 2

ED

mux1 c.o=D

mux2 I<−M[SP]

E IR mux3 SP<−SP+1 SP<−SP+1 PC<−M[SP]

H E PC

+

EE1 EE2 EE3

12 c.o=E

L IR

int

muxI

EI

Processeur V.6

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –70– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Interruptions UPS IUP SI - L3 Unité de commande

Interruptions logicielles

– Une interruption logicielle est une interruption provoquée par le programmeur

(instruction trap). On parle aussi de “trappe logicielle”. Synthèse de l’unité de commande

– Une différence avec un sous-programme (instruction jsr) est qu’une trappe L’unité de commande a été modélisée comme une machine à états synchrone.

correspond à une adresse pré-fixée (numéro de trappe correspondant à une Deux solutions peuvent être mises en oeuvre pour la réaliser :

entrée d’un vecteur d’interruption)

➽ Synthèse par PLA : Solution utilisée dans les processeurs de type RISC.

– Elle permet d’exécuter une procédure du système d’exploitation de manière

– Peu d’instructions ➯ complexité limitée

transparente.

– Rapidité ➯ grande fréquence de fonctionnement

– Comme une IT matérielle, une trappe logicielle provoque la sauvegarde dans la

➽ Synthèse par Micro-Programmation : processeurs de type CISC.

pile du registre d’indicateurs I.

– synthèse par PLA trop complexe.

Pour notre processeur, le codage choisi et de format b qui permet de coder – évolutivité plus grande.

l’adresse dans l’instruction. En général, c’est un numéro qui est codé dans

l’instruction à partir duquel une adresse et calculée.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –73– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Interruptions UPS IUP SI - L3 Unité de commande

Programmable Logic Array

Instruction de trappe :

Matrices de portes ET et OU permettant de réaliser des fonctions logiques de type

c.o instruction notation RTL Etat signaux de commande

SIGMA-PI. Exemple :

F trap adresse M [SP ] ← P C , SP ← SP − 1 EF2 muxAd=3, EP C = 1, WR=1

mux1=2, mux2=1, LSP =1 a

M [SP ] ← I , SP ← SP − 1 EF1 muxAd=3, EI = 1, WR=1

mux1=2, mux2=1, LSP =1 b

P C ← IR(11..0) EF3 muxAd=1, RD=1, mux3=1, LP C =1

c

H

IR<−M[PC], PC<− PC+1

f1

R2

f2

M[SP]<−PC M[SP]<−I

SP<−SP−1 SP<−SP−1 PC<−adresse

f 1 = a.b + a.b + a.c

EF1 EF2 EF3

c.o=F

f 2 = a.b.c + a.b + a.c

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –74– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

Synthèse par PLA

Etat code c.o. cond etat suiv. code etat suiv. code

courant IR(15..12) si IE.int=0 si IE.int=1

R1 00h - - R2 01h R2 01h

Application à une machine de Moore synchrone :

R2 01h 0 - E0 02h E0 02h

entrees Matrice R2 01h 1 - E1 03h E1 03h

... ... ... ... ... ... ... ...

ET

etat courant R2 01h 7 0 R1 00h R1 00h

Horloge registre termes R2 01h 7 1 E7 08h E7 08h

produits

... ... ... ... ... ... ... ...

etat suivant

E0 02h - - R1 00h I1 19h

Matrice

E1 03h - - R1 00h I1 19h

sorties OU

... ... ... ... ... ... ... ...

I1 19h - - I2 1Ah I2 1Ah

– Codage des états ➯ fonction etat suivant=f(etat present,entrees) ... ... ... ... ... ... ... ...

– Sorties : ne dépendent que de l’état présent : signaux de commandes I4 1Ch - - R1 00h R1 00h

– Entrées : code instruction... Bilan : 5 fonctions logiques à 11 entrées.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –77– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

Fonction Etat Suivant

Etape 1 : codage des états : La solution la plus simple est de coder les états de la

machine à états par des codes binaires croissants en partant de R1.

Signaux de commande

A chaque état est associé des signaux de commandes à activer, par exemple pour

Etats de la MEF : R1, R2, E0, E1, E2, E3, E4, E5, E6, E7, E81, E82, E91, E92, EA,

R1 : RD=1, LR = 1, LP C = 1, muxAD=0.

EB1, EB2, EC, ED, EE1, EE2, EE3, EF1, EF2, EF3, I1, I2, I3. Soit 28 états. Il faut

donc 5 bits pour coder un état. A partir de là, il faut déterminer l’expression logique de chaque signal de commande

en fonction du code des états dans lesquels le signal apparaı̂t.

Etape 2 : On construit un tableau dont chaque ligne représente une transition de la Par exemple, RD doit être activé dans les états : R1, E2, E4, E6, E92, EB2, EE2,

machine à état dans laquelle on code l’état suivant en fonction de l’état courant et EE3, EF3 et I3 dont les codes respectifs sont : 0, 4, 6, 8, 13, 16, 20, 21, 24 et 27.

des entrées (code opératoire : c.o. et condition).

L’expression logique est écrite sous forme d’une somme de produits pour être

Demande d’interruption : dans le cas d’une demande d’IT, l’état suivant dépend de implémenté gràce à un réseau PLA.

la prise en compte ou pas de la demande. Si une demande doit être prise en

compte, l’état suivant est R1 sinon, c’est I1.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –78– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

Unité de commande

Unité de commande micro-programmée 0 AdIT=19h

➟ L’unité de commande peut être vue comme un interpréteur d’instructions qui, à int.IE 0 1

+1

partir du code opération, ordonne une séquence de micro-instructions pour en +

5

assurer l’exécution.

➟ Chaque instruction du processeur est vue comme un micro-programme, chaque IR(15..12) cond

4 1

cycle correspondant à une micro-instruction de ce micro-programme.

0 ROM de commande

5

➟ Le rôle d’une micro-instruction est d’activer certains signaux de commande pour

distributeur 2

activer un chemin de données. Les bits qui composent la micro-instruction sont 5

muPC

donc les signaux de commande du chemin de données.

mux 2

Signaux de commande

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –81– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

L’unité de commande peut-être réalisée au moyen d’une architecture semblable à

celle d’un processeur c’est à dire composée : Fonctionnement

– d’une mémoire qui stocke les micro-instructions. ROM de commande

– d’une micro-unité de commande (micro-séquenceur) qui lit les instructions

La mémoire de commande est constitué de mots (1 par micro-instruction)

successives d’un micro-programme.

possédant autant de bits que de signaux de commande plus deux bits de

– d’un registre micro-pointeur de programme (µPC).

commande du multiplexeur mux.

Les dispositifs devant être mis en oeuvre sont :

– un dispositif d’incrémentation de µPC La première adresse contient le code (signaux de commande) de la

– un dispositif de chargement de µPC avec l’adresse de début d’un micro-instruction correspondant à l’état R1 (phase 1 de la recherche d’instruction).

micro-programme Reamarque : Les micros-instructions sont stockées à des adresses correspondant

– un dispositif de retour à la phase de recherche d’instruction (état R1) a la fin au codage des états choisis pour la réalisation par PLA. Un autre choix aurait été

d’une instruction courante. possible.

– la possibilité de se dérouter vers une procédure d’interruption

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –82– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

Commande du multiplexeur mux :

Schéma du distributeur

– La commande mux=0 permet, s’il n’y a pas d’interruption à prendre en compte

Adresse

(int.IE=0), de charger µPC avec l’adresse 0 et donc de démarrer une recherche 0 0 0 0 1 0

d’instruction. Si une interruption doit être traitée, µPC sera chargée avec 1 0 0 0 1 1

l’adresse de la micro-instruction correspondante (I1).

La dernière instruction de chaque micro-programme contiendra donc ce code de

commande de mux.

– La commande mux=1 incrémente µPC et permet donc de passer à la

micro-instruction suivante du micro-programme (par exemple de l’ état E91 à E92). E 1 1 0 0 1

F 1 0 1 1 0

– La commande mux=2 va charger µPC avec l’adresse fourni par le distributeur qui

0

dépend des entrées c.o et cond. Cette adresse est celle du micro-programme

correspondant à l’instruction à exécuter. c.o.=7 et cond=0 0 1

5 adresse

On retrouve cette commande dans la micro-instruction R2. Elle correspond au micro−programme

décodage de l’instruction du processeur à exécuter.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –85– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Unité de commande UPS IUP SI - L3 Unité de commande

Distributeur

Le distributeur doit associer l’adresse d’un micro-programme (dans la ROM de

commande) à un code opération (c.o.) suivant la valeur de cond.

Il est réalisé à l’aide d’une ROM de 16 mots de 5 bits contenant les adresses des

-

micro-programmes.

A l’adresse correspondant à la valeur de c.o. est codée l’adresse du

micro-programme, l’entrée cond étant traitée grace a un multiplexeur.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –86– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Architecture de la mémoire

Deux classes de mémoire : Boı̂tier mémoire

Din

➟ Mémoire principale (où centrale) : m

– reliée directement au processeur par un bus rapide

k

– capacité limitée : typiquement 1 Go adresse

boitier

– volatile

memoire

– accès aléatoire : temps d’accès indépendant l’adresse de stockage

2k x m bits

➟ Mémoire secondaire (où de masse) : CS

– reliée au bus système par un processeur d’E/S R/W

OE

– supports magnétiques où optiques, capacité importante : plusieurs centaines

de Go. m

– non-volatile Dout

– accès séquentiel : accès par blocs

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –89– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Association de boı̂tiers (banque de mémoire)

Mémoire principale Exemple : réalisation d’une banque mémoire de 2 Méga-mots de 16 bits à partir de

boı̂tiers de 1 Méga-mot de 4 bits :

➟ Mémoire vive (volatile) : RAM

– statique Extension du nombre de mots

– dynamique A0..A19 A0

...

A19

➟ Mémoire morte (non-volatile) : ROM CS

D3..D0

– PROM

– EPROM A0

Decodeur CS1 ...

– EEPROM A20..A31 d’adresse A19

12

CS2

– flash

CS

D3..D0

bus donnees 4

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –90– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Association de boı̂tiers (suite) Exemple de micro-système

Extension de la longueur des mots 8 8 8

D7..D0 D7..D0 D7..D0 D7..D0

A0..A19

A0 A0 A0

A0

A0 A0 A0 . . .

... ... ...

13 13 2 A1

A12 A12 A12

A19 A19 A19

A13

Decodeur 3 EPROM RAM PIA

A20..A31

CS CS CS A14

d’adresse D3..D0 D3..D0 D3..D0

A15 CS CS CS

12 CS Processeur R R/W R/W

Decodeur

D15..D12 D11..D8 D3..D0 d’adresses

R/W

bus donnees

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –93– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Décodage d’adresse

L’adresse d’un mot-mémoire peut être décomposé en deux parties : l’adresse du

mot-mémoire dans le boitier et l’adresse localisant le boitier dans l’espace Décodage d’adresse

adressable (poids forts de l’adresse). 0000 EPROM 8Ko 0000 EPROM

2000 8Ko x 4

➟ Décodage complet : on utilise toutes les lignes d’adresse pour réaliser la

fonction de sélection. Le boitier n’utilise que sa propre dimension dans l’espace

8000 RAM 8000 RAM

adressable. A000 8Ko 4Ko x 2

➟ Décodage partiel : On n’utilise qu’un sous-ensemble des lignes d’adresse pour C000

réaliser la fonction de sélection.

Si x lignes ne sont pas utilisées, le boitier occupe 2x fois sa dimension dans FFFC

FFFF 4o FFFF 4o x 4096

l’espace adressable. On parle d’efffet de miroir. La même information est

disponible à partir d’adresses différents. Decodage complet Decodage partiel

Le décodage partiel est facile à réaliser mais gaspille l’espace adressable. Il est

réservé aux micro-systèmes figés.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –94– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Hiérarchie de mémoires Taux de succès et taux d’échec

➟ Mémoire secondaire La mémoire cache est d’autant plus efficace que les défauts de cache sont rares.

Soit h le taux de succès et n le rapport en nombre de cycles entre un accès à la

➟ Mémoire principale

mémoire principale et un accès au cache, la réduction du temps d’accès peut être

➟ Mémoire cache de niveau 2 évalué par la relation : R = n/(h + n(1 − h))

➟ Mémoire cache de niveau 1

Exemple : Pour h = 0, 95 et n = 50, on obtient R = 14, 5, soit un temps moyen

➟ Registres internes d’accès divisé par 14,5.

Plus on descend dans la hiérarchie, plus la capacité mais aussi le temps d’accès Les taux de succès élevés sont obtenus grace aux principes de localité spatiale et

diminuent. temporelle.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –97– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Localité spatiale et temporelle

Le principe de localité affirme que les informations auxquelles va accéder le

processeur ont une forte probabilité d’être localisées dans une fenêtre spatiale et

Mémoire cache une fenêtre temporelle.

Lorsque le processeur doit accéder à une information, la recherche est effectuée ➟ Localité spatiale : A un instant donné le processeur fait référence à des objets

proches du dernier qu’il a utilisé : code séquentiel (sauf rupture de séquence),

d’abord dans la mémoire cache.

données consécutives : tableaux, structures

– Si l’information est présente, elle est fournie immédiatement au processeur

– Sinon, il y a défaut de cache. La lecture doit se faire dans la mémoire principale ➟ Localité temporelle : En général, si un processeur à fait récemment référence à

ce qui bloque le processeur pendant plusieurs cycles. un objet, il va très probablement y faire à nouveau référence (structures

C’est le gestionnaire de cache qui se charge de gérer celà. Pour le processeur, itératives).

cette gestion est transparente. La localité spatiale suggère de copier des blocs de mots dans le cache plutôt que

des mots isolés.

La localité temporelle suggère de conserver pendant quelque temps dans le cache

les informations auxquelles on vient d’accéder.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –98– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Découpage de l’espace adressable

Quelle que soit l’organisation physique de la mémoire, on peut définir une

organisation purement logique et découper celle-ci de différentes manières.

Mémoire cache

➟ Bloc mémoire (ou ligne) : un bloc mémoire représente un nombre fixe de mots

mémoire. La mémoire est découpée en blocs et une adresse mémoire peut être ➟ totalement associative : solution la plus naturelle mais complexe à réaliser.

vue comme la concaténation de l’adresse d’un bloc et de l’adresse du mot ➟ à correspondance directe : simple à réaliser mais moins efficace.

mémoire dans le bloc. ➟ à plusieurs voies (hybride) : compromis entre l’efficacité de la technique

➟ Page mémoire : On peut regrouper les blocs pour définir une page mémoire de associative et la simplicité du cache à correspondance directe.

la même manière que l’on regroupe des mots pour définir un bloc.

L’adresse d’un mot mémoire se décompose alors en un numéro de page , un

numéro de bloc et une position dans le bloc.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –101– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS IUP SI - L3 Architecture de la mémoire

Mémoire associative

n−1 0

Mémoire cache associative

Decodeur presence

mot 0

n etat

etiq[0] bloc[0]

donnee num. bloc

adresse etiq[1] l bloc[1] memoire

mot 1 l ... ...

Encodeur principale

de

etiq[2^l−1] bloc[2^l−1]

priorite presence

adresse R/W

logique de com.

k wait

l

mot

mot 2^k−1 adresse dans le bloc

donnee

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –102– Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006

IUP SI - L3 Architecture de la mémoire UPS

Remplacement d’un bloc

Si le cache est plein et que le processeur à besoin d’un bloc qui n’est pas dans le

cache, il faut remplacer un des blocs du cache. Plusieurs politiques de

remplacement sont possibles :

➟ aléatoire : très rapide mais peut supprimer un bloc à accès fréquent.

➟ FIFO : on utilise une file circulaire. Simple à implémenter et relativement

efficace.

➟ LRU (Least Recently Used) :La ligne dont le dernier accès et le moins récent et

celle qui sera remplacée.

Implémentation pratique : un bit d’état A est mis à 1 chaque fois que le

processeur accède à un bloc. A intervalle régulier, tous les bits A sont remis à 0.

Le gestionnaire remplace le premier bloc dont le bit A est à 0.

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –105–

IUP SI - L3 Architecture de la mémoire UPS

Mémoire cache à correspondance directe

etat

etiq[0]

etiq[1]

num. bloc bloc[0]

...

adresse l bloc[1] memoire

l ...

etiq[2^l−1] principale

num page bloc[2^l−1]

presence

R/W

logique de com.

wait

l

mot

adresse dans le bloc

donnee

Jean-Michel ENJALBERT - enjalber@laas.fr, 2005/2006 –106–

Vous aimerez peut-être aussi

- Formulaire Rapport D'expertise D'un Cours en Ligne - BendaliDocument3 pagesFormulaire Rapport D'expertise D'un Cours en Ligne - BendaliNanou Bendali90% (10)

- Intro Mémoire ProcesseurDocument209 pagesIntro Mémoire ProcesseurImane el omariPas encore d'évaluation

- Chapitre N°01Document14 pagesChapitre N°01Youssouf gairanPas encore d'évaluation

- Chap 2Document5 pagesChap 2christimimbangPas encore d'évaluation

- PIC LeçonN°0Document7 pagesPIC LeçonN°0Smart ClassePas encore d'évaluation

- Chapitre 2 - Architecture de BaseDocument5 pagesChapitre 2 - Architecture de BaseAbakar MamadouPas encore d'évaluation

- Architecture Et Technologies Des Systemes InformatiquesDocument74 pagesArchitecture Et Technologies Des Systemes InformatiquesHamzaoui AnasPas encore d'évaluation

- ArchiOrd Chap1 Et Chap2Document87 pagesArchiOrd Chap1 Et Chap2Lisa Lisa liliPas encore d'évaluation

- 1-Architecture de baseDocument9 pages1-Architecture de basewadesidickPas encore d'évaluation

- Chap 1 - Architecture D'un Processeur de Traitement Et Coprocesseur GLO RES TELDocument13 pagesChap 1 - Architecture D'un Processeur de Traitement Et Coprocesseur GLO RES TELAhmed YasinPas encore d'évaluation

- Cours Arch OrdDocument36 pagesCours Arch OrdhamedileezizPas encore d'évaluation

- Cours Arch Ord2Document36 pagesCours Arch Ord2Malak elPas encore d'évaluation

- OrdStrApp2010 Chap1Document79 pagesOrdStrApp2010 Chap1Hind BAHRIPas encore d'évaluation

- Cours Emi Micro 2020 (Microp CHP 1,2,3)Document15 pagesCours Emi Micro 2020 (Microp CHP 1,2,3)Youssef El AjraouiPas encore d'évaluation

- Initiation Programmation CDocument122 pagesInitiation Programmation CredasacretPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 66 PDFDocument28 pagesCours Microcontrôleur Microprocesseur 66 PDFAbderrahim RiadPas encore d'évaluation

- COURS INFORMATIQUE 4ème H InformatiqueDocument19 pagesCOURS INFORMATIQUE 4ème H InformatiquefelixmindekemPas encore d'évaluation

- Architecture Des Ordi PDFDocument87 pagesArchitecture Des Ordi PDFCouro SowPas encore d'évaluation

- CourLinuxAsimi2022 2023Document112 pagesCourLinuxAsimi2022 2023Mohammed LaalahmiPas encore d'évaluation

- Fiche TD1 corrigé derniére version(2)(1)Document6 pagesFiche TD1 corrigé derniére version(2)(1)adem BenPas encore d'évaluation

- Architecture Des OrdinateursDocument21 pagesArchitecture Des OrdinateursSOW KaridjatouPas encore d'évaluation

- Chapitre IV Microcontrôleurs PDFDocument55 pagesChapitre IV Microcontrôleurs PDFBouzid AchrefPas encore d'évaluation

- Chapitre 1 AODocument5 pagesChapitre 1 AOMoujahed GassoumiPas encore d'évaluation

- Chapitre 4 - Etude D'un MicroproDocument13 pagesChapitre 4 - Etude D'un MicroproMorsPas encore d'évaluation

- Chapitre 1: Introduction Aux MicroprocesseursDocument26 pagesChapitre 1: Introduction Aux MicroprocesseursAbir HammamiPas encore d'évaluation

- Acfrogbomoqtev40hikghc3covwhsdznviwifokez75jhwpsg2grvi68z7emfz Wsd32dift9jiiirnuryqhvs071f8a8uxi7xpfjnwjy Kxbucsdlyz3mgfay9jz Y7uiyhzzdmf2 Fls1ijnDocument26 pagesAcfrogbomoqtev40hikghc3covwhsdznviwifokez75jhwpsg2grvi68z7emfz Wsd32dift9jiiirnuryqhvs071f8a8uxi7xpfjnwjy Kxbucsdlyz3mgfay9jz Y7uiyhzzdmf2 Fls1ijnHamza RahaliPas encore d'évaluation

- WWW - Cours Gratuit - Com Id 5297Document90 pagesWWW - Cours Gratuit - Com Id 5297Madjilem NayamPas encore d'évaluation

- Architecture Des OrdinateursDocument17 pagesArchitecture Des Ordinateursdhia.trimech.123Pas encore d'évaluation

- Chapitre 3 - Architectures Des MicroprocesseursDocument43 pagesChapitre 3 - Architectures Des Microprocesseurskhalid.ennajiPas encore d'évaluation

- SE CHAP 01 Concepts de Base Site 2LMDDocument14 pagesSE CHAP 01 Concepts de Base Site 2LMDImen BoukhorsPas encore d'évaluation

- Architecture Des OrdinateursDocument17 pagesArchitecture Des OrdinateursMohsen GharbiPas encore d'évaluation

- Qu'est Que L'informatique Industrielle?: - Les Domaines D'application: Systèmes EmbarquésDocument43 pagesQu'est Que L'informatique Industrielle?: - Les Domaines D'application: Systèmes Embarquésfazfrito lacaviataPas encore d'évaluation

- Chapitre 1 ArchitectiureDocument8 pagesChapitre 1 Architectiuremaram koukiPas encore d'évaluation

- Chapitre3 Premier Ordinateur MARIEDocument32 pagesChapitre3 Premier Ordinateur MARIENouhaila AtabetPas encore d'évaluation

- Chapitre_3_Composants Matériels v2Document81 pagesChapitre_3_Composants Matériels v2kossiferdinabaita437Pas encore d'évaluation

- CH2 - Architecture Des OrdinateursDocument5 pagesCH2 - Architecture Des OrdinateursJean LucPas encore d'évaluation

- 2 Ao Uf 21 22Document38 pages2 Ao Uf 21 22Ha JarPas encore d'évaluation

- Systèmes MicroprogrammésDocument6 pagesSystèmes MicroprogrammésNasriMohsenPas encore d'évaluation

- Archi2 Cours2 Architecture PDFDocument26 pagesArchi2 Cours2 Architecture PDFSagesse TetyaPas encore d'évaluation

- Chap 1Document21 pagesChap 1Mouhamed MayelPas encore d'évaluation

- Presentation 11Document59 pagesPresentation 11Oussama DaliPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 32Document37 pagesCours Microcontrôleur Microprocesseur 32Frank EffeuzePas encore d'évaluation

- Chapitre1 Architecture - Ordinateurs - 2019 - 2020Document13 pagesChapitre1 Architecture - Ordinateurs - 2019 - 2020Bessem BessemPas encore d'évaluation

- Cours Architecture Matérielle de L'ordinateurqsdfqDocument22 pagesCours Architecture Matérielle de L'ordinateurqsdfqjedipi7523Pas encore d'évaluation

- intro-archiDocument5 pagesintro-archiTONY BENSPas encore d'évaluation

- Cours Archtecture Des OrdiDocument9 pagesCours Archtecture Des OrdiemmanuelfreddyPas encore d'évaluation

- Algorithm i QueDocument81 pagesAlgorithm i QueradioPas encore d'évaluation

- STR Temps Réel Cours 1Document14 pagesSTR Temps Réel Cours 1Nori AzzaouiPas encore d'évaluation

- Architecture Des Ordinateurs Cours-1Document14 pagesArchitecture Des Ordinateurs Cours-1Louis KouassiPas encore d'évaluation

- Chapitre 3 - MicroDocument21 pagesChapitre 3 - MicroTayssir zayetPas encore d'évaluation

- Chap3 SETDocument8 pagesChap3 SETSamira cherifPas encore d'évaluation

- Expose Groupe 5 Asi (1) - 1Document11 pagesExpose Groupe 5 Asi (1) - 1lavoisierkomabou84Pas encore d'évaluation

- Intro ArchitectureDocument16 pagesIntro ArchitectureIsraa AlPas encore d'évaluation

- Cours de PIC Généralités PDFDocument18 pagesCours de PIC Généralités PDFAhmed FeradjiPas encore d'évaluation

- Cours Architecture Des OrdinateursDocument16 pagesCours Architecture Des Ordinateurslingom2alfredPas encore d'évaluation

- Ch3 Les MicroprocesseursDocument8 pagesCh3 Les MicroprocesseursyessinePas encore d'évaluation

- CM Dui Ue3 ArchiDocument133 pagesCM Dui Ue3 ArchiMouhamed GueyePas encore d'évaluation

- Automates Programmables IndustrielsDocument32 pagesAutomates Programmables Industrielssumororo100% (1)

- Cours 01 Les Composants de L'ordinateur FSTDocument12 pagesCours 01 Les Composants de L'ordinateur FSTdembelejacob719Pas encore d'évaluation

- Rendu de ligne de balayage: Explorer le réalisme visuel grâce aux techniques de rendu ScanlineD'EverandRendu de ligne de balayage: Explorer le réalisme visuel grâce aux techniques de rendu ScanlinePas encore d'évaluation

- Profil de couleur: Explorer la perception et l'analyse visuelles en vision par ordinateurD'EverandProfil de couleur: Explorer la perception et l'analyse visuelles en vision par ordinateurPas encore d'évaluation

- Theme 3 PDFDocument1 pageTheme 3 PDFEmma DjomoPas encore d'évaluation

- Cours Sur Les Processus Et ThreadDocument12 pagesCours Sur Les Processus Et ThreadEmma DjomoPas encore d'évaluation

- Theme 2Document1 pageTheme 2Emma DjomoPas encore d'évaluation

- 1-Intro HandoutDocument58 pages1-Intro HandoutEmma DjomoPas encore d'évaluation

- Langage CDocument171 pagesLangage CEmma DjomoPas encore d'évaluation

- Présentation Cours Algo Prog MIPDocument25 pagesPrésentation Cours Algo Prog MIPEmma DjomoPas encore d'évaluation

- Réseaux Technologie Communication Support4Document44 pagesRéseaux Technologie Communication Support4Emma DjomoPas encore d'évaluation

- Structures Données LinéairesDocument55 pagesStructures Données LinéairesEmma DjomoPas encore d'évaluation

- PolyDocument85 pagesPolyEmma DjomoPas encore d'évaluation

- Réseaux Technologie Communication Support3Document36 pagesRéseaux Technologie Communication Support3Emma DjomoPas encore d'évaluation

- Programmation Evenementielle Et IHM 1Document50 pagesProgrammation Evenementielle Et IHM 1Emma Djomo100% (2)

- Sopport de Cours Info - EOB1Document55 pagesSopport de Cours Info - EOB1Emma DjomoPas encore d'évaluation

- StructuresDocument23 pagesStructuresEmma DjomoPas encore d'évaluation

- Support ASMDocument9 pagesSupport ASMEmma DjomoPas encore d'évaluation

- Chapitre 8 Les Peripheriques de StockageDocument30 pagesChapitre 8 Les Peripheriques de StockageEmma DjomoPas encore d'évaluation

- Chapitre 2 - PROTOCOLES ET NORMALISATION DES RESEAUXDocument18 pagesChapitre 2 - PROTOCOLES ET NORMALISATION DES RESEAUXEmma DjomoPas encore d'évaluation

- Systèmes DynamiquesDocument9 pagesSystèmes DynamiquesEmma DjomoPas encore d'évaluation

- Lecon 1 Les Étapes de Résolution D'un Problème Et La Structure D'un AlgorithmeDocument2 pagesLecon 1 Les Étapes de Résolution D'un Problème Et La Structure D'un AlgorithmeEmma Djomo100% (2)

- Os01 PrincipesDocument32 pagesOs01 PrincipesEmma DjomoPas encore d'évaluation

- GEII ElecNum Codage PolyDocument9 pagesGEII ElecNum Codage PolyEmma Djomo100% (1)

- Memoires de MasseDocument14 pagesMemoires de MasseEmma DjomoPas encore d'évaluation

- Algorithme Et Structure de DonnéesDocument4 pagesAlgorithme Et Structure de DonnéesEmma DjomoPas encore d'évaluation

- Infographie & MultimdiaDocument9 pagesInfographie & MultimdiaEmma Djomo100% (1)

- FIN1125Document9 pagesFIN1125kamel1205Pas encore d'évaluation

- formalisation des entreprisesDocument10 pagesformalisation des entreprisesFARI-DY OfficielPas encore d'évaluation

- Plan de Formation Intervenants Pour La Formation de Responsable Administratif Et FinancierDocument3 pagesPlan de Formation Intervenants Pour La Formation de Responsable Administratif Et FinancierIdianne Rachid Ettalibi100% (1)

- Algorithme de Moore-35Document2 pagesAlgorithme de Moore-35Aymen RakiPas encore d'évaluation

- Faute Lucrative1Document19 pagesFaute Lucrative1utilisateur vPas encore d'évaluation

- Guide D'installation SAGEM 3302 FAWRIDocument14 pagesGuide D'installation SAGEM 3302 FAWRIAhmed Bidali100% (1)

- TP FlexionDocument6 pagesTP FlexionufegfPas encore d'évaluation

- UFS Manuel en FrançaisDocument33 pagesUFS Manuel en FrançaisMohan RajPas encore d'évaluation

- Devoir 1 VF ATDocument39 pagesDevoir 1 VF ATAudry TSHIPAMBAPas encore d'évaluation

- Rapport À DéposerDocument37 pagesRapport À Déposerabdellah kassi100% (1)

- Chapitre2-Régression SimpleDocument57 pagesChapitre2-Régression SimpleBassma Azarhoun100% (1)

- Les Gourous de La QualitéDocument15 pagesLes Gourous de La QualitéNdiaw YatéPas encore d'évaluation

- Solutions MFDocument1 pageSolutions MFAlaa SahliPas encore d'évaluation

- Annales Physique Chimie CNC Concours National Commun MarocainDocument6 pagesAnnales Physique Chimie CNC Concours National Commun MarocainLarbi Badrour0% (2)

- VideoDocument7 pagesVideoFranck BerndPas encore d'évaluation

- Cours Autodesk PDFDocument1 012 pagesCours Autodesk PDFYshong MPOUOGPas encore d'évaluation

- Ltic 2021Document7 pagesLtic 2021saadawinour10Pas encore d'évaluation

- Liste Des RessourcesDocument52 pagesListe Des RessourcesSara NahidPas encore d'évaluation

- Le Progrès TechniqueDocument2 pagesLe Progrès TechniqueRahik AhamadiPas encore d'évaluation

- TP6Document4 pagesTP6Anonymous PKdzRZ7Pas encore d'évaluation

- TD Bilan Financier CorrectionDocument3 pagesTD Bilan Financier Correctionsayari firasPas encore d'évaluation

- Otkrijte Mostar Mostar À DécouvrirDocument84 pagesOtkrijte Mostar Mostar À DécouvrirJasmin ĆosićPas encore d'évaluation

- Paysages CoursDocument14 pagesPaysages CoursDaria DoneaPas encore d'évaluation

- Audit Interne Dans Le Secteur PublicDocument98 pagesAudit Interne Dans Le Secteur PublicMarina AlaouiPas encore d'évaluation

- ProfessionsDocument2 pagesProfessionsSurajit HalderPas encore d'évaluation

- DIOP, Sokhna Assiatou Diop 20179Document66 pagesDIOP, Sokhna Assiatou Diop 20179Jeces Reinold LewaguiPas encore d'évaluation

- Etalonnage MECIIIDocument37 pagesEtalonnage MECIIIanon_258320919100% (2)

- DM1Document3 pagesDM1abdel dalilPas encore d'évaluation

- TD Les Types de DocumentsDocument6 pagesTD Les Types de Documentsfatimamadih222Pas encore d'évaluation