# Secure Interface Design Leveraging Hardware/Software Support

THIS IS A TEMPORARY TITLE PAGE

It will be replaced for the final print by a version

provided by the registrar's office.

Doctoral Thesis by

Atri Bhattacharyya

presented on 2<sup>nd</sup> April, 2024 at EPFL, Lausanne

(To be) Approved by the examining committee:

Prof. Carmela González Troncoso, Jury President

Prof. Mathias Payer, Thesis Director

Prof. Babak Falsafi, Thesis Co-director

Prof. Sanidhya Kashyap, Internal Examiner

Dr. Anil Kurmus, IBM Research, External Examiner

Dr. Anjo Lucas Vahldiek-oberwagner, Intel Labs, External Examiner

Let us think the unthinkable,

Let us do the undoable,

Let us prepare to grapple with the ineffable itself,

And see if we may not eff it after all.

Douglas Adams

To those who inspired and encouraged my pursuit of knowledge

# **Acknowledgments**

" It's a dangerous business, Frodo, going out your door. You step onto the road, and if you don't keep your feet, there's no knowing where you might be swept off to. ", Bilbo Baggins often said to his young nephew Frodo Baggins. When I left India to start my Master's study at EPFL in 2016, little did I know of the journey that lay ahead. Looking back at the path culminating in the attainment of the PhD, I must thank the many people who accompanied me through my wanderings, sweeping me off on unknown paths and shining light in times of darkness.

Every journey requires guidance, and I would like to first thank my academic advisors, Prof. Mathias Payer and Prof. Babak Falsafi, who led me through my PhD. Mathias has been a source of inspiration throughout the years, with his belief that all systems are definitely and undeniably "broken". Mathias was critical to my successes during the PhD, pushing me to try every new avenue, teaching me to believe in my ideas, and providing the ever present support required to realize ideas. My thesis is the culmination of a long series of ideas and "weekend projects" of increasing depth and clarity. Many of the ideas comprising this thesis result from ideas refined and polished with Mathias' invaluable insights. Mathias' humanity was also key to surviving the unprecedented COVID-19 crisis marking a major fraction of the PhD. I am also deeply indebted to Babak, who hosted me in PARSA during my masters studies in addition to being my PhD co-advisor. Babak is an exceptional leader, and has the ability to push research projects to look beyond the superficial symptoms ailing computer systems, and find the right questions to ask. Babak's belief and insistence on pushing for excellence has been instrumental in deciding my research topics.

I would also like to thank the members of my thesis committee, Prof. Carmela Troncoso, Prof. Sanidhya Kashyap, Dr. Anil Kurmus, and Dr. Anjo Vahldiek-Oberwagner. I greatly appreciate their detailed and constructive feedback on my thesis draft, and for providing a fresh perspective on my research allowing me to iron the final wrinkles in my research.

I have also profited from a set of amazing collaborators helping me realize my research ideas. Dr. Anil Kurmus' sabbatical at EPFL was an incredible opportunity to explore the finer details of microarchitectural side-channel attacks. I have also been fortunate to closely collaborate with other PhD students, primarily Siddharth Gupta, Florian Hofhammer, Andres Sanchez, Yuanlong Li, Uros Tesic and Lana Josipovic. Without our time spent working through tough problems, and working late to meet ambitious deadlines, the PhD journey would have been particularly lacking luster. I would like to particularly thank Siddharth and Florian for teaching me to structure papers into logical sequences of details from an unmanageable heap of ideas and data. I must also thank

my student collaborators, Andrej Gorjan, Lucas Lopez Cendes, and Solène Husseini, who enabled me to explore the ideas which I never had time to do justice to. Alongside the students I had the pleasure to help during teaching assistant duties, they helped me realize my love for teaching, for sharing knowledge, and for learning together.

My love for teaching stems from the efforts of many amazing academics who have injected me with their passion for knowledge. I fondly remember the passionate high school lessons by Mr. Dey, Mr. Sur, Mr. Royan Mrs. Basu, and Mrs. Chakrabarthy. They helped develop an adoration for maths, the sciences, and the arts. My bachelors would have been far less educative without the efforts of Prof. Mainak Chowdhury, Prof. Aloke Dutta, Prof. Achla Raina, and Prof. Suchitra Mathur. The efforts of Prof. Chowdhury and Prof. Dutta formed the basis for my future in low-level topics in computer science. Prof. Raina and Prof. Mathur fascinated me with the use of science to understand society and particularly its language. I am also thankful to my teachers at EPFL for the knowledge imparted during numerous courses through my Masters and PhD studies here. I have found the advice "prepare to throw one away" imparted during the Principles of Computer Systems course invaluable for my PhD research.

I would like to specially extend thanks to Natascha Fontana for seamlessly managing the myriad administrative tasks and for dealing with EPFL's bureaucracy. She managed to wrap her head around the interminable list of funding sources supporting my PhD, and always managed to simplify requirements from our side. Natascha's efforts made dealings with EPFL administration, from organizing and cancelling visiting talks, reimbursing expenses, renewing contracts, hiring interns, and procuring hardware trivial.

No person walks through a PhD alone, and I am deeply grateful for my many colleagues who walked beside me. I would like to particularly thank the members of the Hive and PARSA, my two primary academic families during my time at EPFL. I am indebted to Florian Hofhammer, who has evolved from being a student I supervised for a Master's thesis to a close collaborator to eventually becoming a constant fixture in innumerable rambling discussions over coffee, rants against every conceivable inconvenience, and being a rubber ducky for many random, ambitious or otherwise zany ideas. Without your engineering skills, SecureCells may never have been a paper, and I might not have finished a thesis. Next, I have to thank Nicolas Badoux who has been an unending source of generosity, joy, cakes and chocolate across the years. I must also thank Luca di Bartolomeo for teaching me to unabashedly ask "Why?", and for teaching me to not feel guilty about being constructively competitive. My gratitude also goes out to the other members of the Hive. Ahmad Hazimeh has been my colleague in the lab for the longest, and has shared my earliest days here. Andres Sanchez has been a close collaborator across numerous projects, and will be remembered for his terrible puns. The postdocs, Flavio Toffalini and Marcel Busch brought a fresh dose of life into the lab. I feel like Flavio always has an ear to listen to whatever I need to get off my mind. I look forward to more afternoons playing badminton with the Hive's permanent visitor, Qiang Liu. Marcel has been instrumental in creating many indelible memories, specially on Fridays. I have also enjoyed spending time with the many other members of the lab, Antony Vennard, Lucio Romerio, Jelena Jankovic, Uros Tesic, Gwangmu Lee, Daniele Antonioli, Chibin

Zhang, Jean Michel, Han Zheng, Zhiyao Feng, and Phillip Mao. On the PARSA side, I must thank Siddharth Gupta with whom I shared many experiences including working on multiple projects and having a major skiing accident. Sid also taught me how to write good papers. Ognjen Glamocanin has been a constant presence throughout the years, and I look forward to sharing more burgers with you. I must thank the remaining members, Alex Daglis, Mario Drumond, Arash Pourhabibi, Mark Sutherland, Javier Picorel, Dimitrii Ustiugov, Yuanlong Li, Shanqing Lin, Simla Harma, Yunho Oh, Rafael Pizzaro for welcoming me into the lab across many years. I was also lucky to have an amazing cohort of other PhD peers. Mahyar Emami was present at my first PC build, many intermediate Kashmiri lunches, and will likely help me with my next PC build. I will remember Sahand Kashani-Akhavan, the FPGA wizard, whose humor, humility and technical knowledge always left me astounded. I must thank the many others with whom I spent innumerable light moments in the fellowship room, Athanasios Xygkis, Xinrui Jia, Zeinab Shmeis, and Khashayar Barooti. Finally, I must acknowledge the remaining systems PhDs who contributed to making my PhD life amazing, Rishabh Iyer, David Aksun, Marios Kogias, Adrien Ghosn, Neelu Kalani, Stefan Nikolic, Matthaios Olma, Stella Giannakopoulou, Lana Josipovic, and Andrea Guerrieri.

Next, I want to thank the entire Zenith family, which was a crucial part of my Master's and PhD life, and helped support me particularly through COVID-19 times. The years in Marcelin were my best in Switzerland. The board game group comprising Kirtan Padh, Kenneth Joseph Paul, Christina Grimm, Asli Yörüsün, Soner Serbest, and (more recently) Saskia Thomi have contributed to many periods of fun and intense competition. I am also grateful for the many moments shared with Yassir el Maaroufi, Rahul Gupta, Rasool Ahmad, Sharbatanu Chatterjee, Shankha Nag, and Debdatta Ray. I would also like to thank Nina and Daniel Brissot, who welcomed me to Switzerland with open arms.

Finally, and most importantly, I must thank my family who have steadfastly been the base on which each of my achievements is based. This journey has been as much theirs as mine. I must thank my parents, who taught me to pursue my interests and supported me through thick and thin. My mother has inspired me to teach and to excel, teaching me how to find joy and happiness in every aspect of life. My father taught me to care, for everyone and anyone. I have rarely found people as compassionate as my father. I must also thank my aunt (Mashimoni) and uncle (Meshoi), who have cared for me like a son. I cannot express my gratitude for my grandmother (Dida), grandfather (Dadabhai), and grand-uncle (Chinida) who catalyzed my academic ambitions. Finally, I must acknowledge my hero, my elder brother, has enabled each of my successes and has been a key ingredient to my efforts through more than 30 years. There are no words to describe how he has helped me navigate each phase of my life. I doubt I would have progressed far beyond kindergarten without his active help. I must thank the remaining two members of "Chaarmurti", my cousins. They have always been a source of happiness and relaxation. Neel, Rishi, Dada, I look forward to more great times together.

I thank the various sources of funding supporting this thesis. My PhD research has been partially supported by EPFL, the 2020 IBM Research Fellowship, the European Research Council (grant agreement No. 850868), DARPA (HR001119S0089-AMP-FP-034), ONR (award N00014-18-1-2674 and 13000660-052), the 2023 Qualcomm Innovation Fellowship, Fondation Botnar, and a gift from Intel Corporation.

Lausanne, 2<sup>nd</sup> April, 2024

Atri Bhattacharyya

## **Abstract**

Computer systems rely heavily on abstraction to manage the exponential growth of complexity across hardware and software. Due to practical considerations of compatibility between components of these complex systems across generations, developers have favoured stable interfaces at crucial boundaries such as between hardware and software, or between the kernel and userspace. While these interfaces have persisted across more than 20 years, the modern computing environment has evolved significantly in terms of security and performance. Our increasingly connected systems share code components of widely varying provenance and legacy interfaces are unable to counter modern threats while maintaining strict performance objectives. Computing requires new interfaces with stronger security guarantees which can also support high performance applications. First, the kernel-user interface remains one of the primary vectors for inter-application attacks as compromising the kernel gives an attacker total control over the system's resources and to other applications on the same system. Second, the virtual memory interface has newly emerged as another crucial interface enabling attackers to remotely compromise systems as applications increasingly execute third-party code, for example JavaScript scripts downloaded from the internet. In this thesis, therefore, we investigate these two key interfaces to improve their security and performance limits.

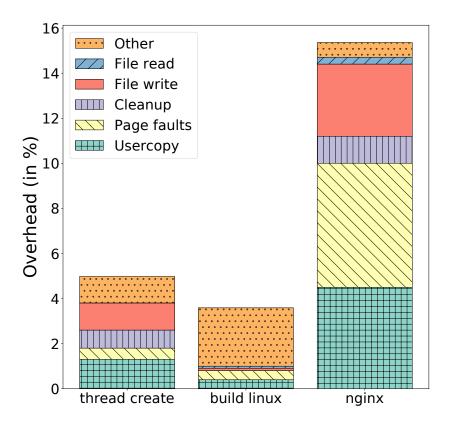

The kernel-user system call interface suffers from double-fetch bugs for passed-by-reference arguments stored in user memory. Double fetches allow malicious users to compromise the isolation guaranteed at the kernel-user interface to illegally access memory, cause kernel crashes, or to escalate their privileges. The modern multi-user, multiprocessing environment allows the user to change the arguments read by the kernel by modifying the contents of memory from a concurrent thread. Traditional testing techniques cannot eliminate all double-fetch bugs due to the complexity and configurability of the kernel. The extensibility of the kernel further exacerbates the challenge as third-party modules loaded by the kernel may further introduce double-fetches. We present Midas, a systematic mitigation for kernel double-fetches which leverages the kernel's interface to read user memory to guarantee that every kernel read of a user object during a system call will return the same value. Midas's guarantee makes an implicit assumption by kernel developers explicit, protecting the kernel against a class of bugs while incurring merely 3.4% overhead on diverse workloads across the NPB and PTS benchmark suites.

Whereas modern systems software runs code from a plethora of sources with varying degrees of trust, the traditional virtual memory abstraction lacks support for isolating untrusted parts of an application within the same virtual address space. Since all code running within a process execute

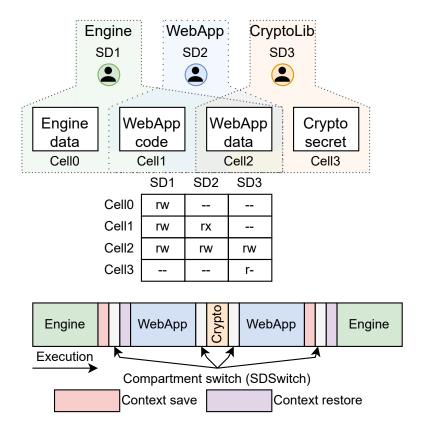

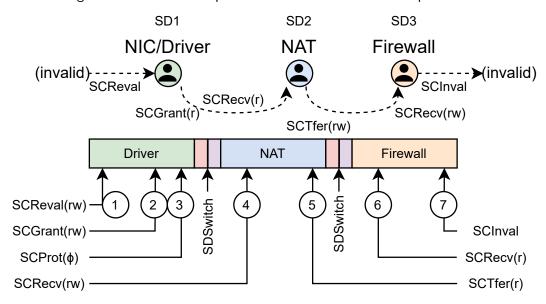

at the same trust level, buggy or malicious third-party code can compromise the process by directly leaking or modifying memory used by other components of the application. We must redesign the virtual memory interface to allow applications to be compartmentalized, essentially implementing the principle of least privilege by isolating untrusted parts of the application within compartments with limited access to the application's resources. We present SecureCells, a novel architectural interface for intra-address space compartmentalization. SecureCells enables applications to define hardware-enforced memory views for application compartments with accelerated userspace instructions for inter-compartment calls. In microbenchmarks, SecureCells enables a 5-stage in-order core to switch compartments in only 8 cycles reducing the cost of transitions by an order of magnitude compared to the state of the art. We also build a full-system prototype of SecureCells, based on the RISC-V RocketChip core running the seL4 kernel to evaluate userspace benchmarks.

This thesis also presents the first systematization of knowledge for compartmentalization mechanisms, evaluating both qualitative and quantitative properties. We describe relevant security and performance properties for practical compartmentalization, and show how well each mechanism provides each property. A comprehensive review of compartmentalization techniques aims to enable computer systems developers to define a secure, performant and usable interface to support widespread compartmentalization of applications in the future. Our systematization exposes common shortcomings of these mechanisms, pointing future research efforts to opportunities for more comprehensive compartmentalization support.

This thesis posits that legacy interfaces between components of modern computing systems inhibits their security guarantees, and explores issues at two major interfaces. We show that principled redesign of interfaces enables the implementation of more secure systems while supporting high-performance application needs, with the design and implementation of Midas and SecureCells to tackle challenges at the kernel-user and intra-process interfaces respectively.

### Résumé

Les systèmes informatiques font un lourd usage d'abstraction pour répondre à la croissance exponentielle de la complexité du matériel et du logiciel. A cause des considérations pour maintenir une compatibilité entre des éléments de différentes générations de ces systèmes complexes, les développeurs ont favorisé des interfaces stables aux limites critiques tels que celles entre le matériel et le logiciel ou entre les espaces utilisateurs et noyaux. Alors que ces interfaces perdurent depuis plus de 20 ans, l'environnement informatique moderne a évolué significativement en termes de sécurité et de performance. Ces systèmes sont de plus en plus connectés et partagent des composants de provenance très diverses. Ces anciennes interfaces ne sont pas à même de contrer les menaces modernes tout en maintenant des objectifs de performances stricts. L'informatique nécessite de nouvelles interfaces garantissant une plus grande sécurité tout en gardant possible des applications à haute performance. L'interface utilisateur-noyau reste un des vecteurs principaux d'attaques entre applications car la compromission du noyau permet à l'attaquant de contrôler les ressources du système ainsi que les autres applications installées. Au vue de l'augmentation de code tiers exécuté par les applications, par exemple des scripts Javascript téléchargé depuis l'internet, l'interface de la mémoire virtuelle est en train d'émerger comme une autre interface critique pouvant offrir à des attaquants l'accès au système. Dans cette thèse, nous investiguons donc ces deux interfaces critiques afin d'améliorer leurs limites de performances et de sécurité.

L'interface d'appel noyau-utilisateur souffre de bogues de double récupération pour les arguments passés par référence stockés dans la mémoire utilisateur. Les double récupérations permettent à un utilisateur malveillant de compromettre l'isolation garantie par l'interface noyau-utilisateur pour accéder illégalement à la mémoire, provoquant des crashs du noyau, ou permettant l'escalade de leurs privilèges. L'environnement moderne multi-utilisateur et multi-processus permet à l'utilisateur de modifier les arguments lus par le noyau à différents moments en modifiant le contenu de la mémoire à partir d'un fil concurrent. La complexité du noyau empêche les développeurs de trouver et de corriger tous ses bogues. L'extensibilité du noyau aggrave encore le défi, car des modules tiers chargés par le noyau peuvent également introduire des double récupérations. Nous présentons Midas, une prévention systématique des double récupérations du noyau en exploitant son interface pour accéder à la mémoire utilisateur afin de garantir que chaque lecture demandée par le noyau d'un objet utilisateur lors d'un appel système renverra la même valeur. La garantie de Midas rend explicite une hypothèse implicite des développeurs du noyau, protégeant le noyau contre une classe de bogues tout en entraînant un coût de seulement 3,4% sur les charges de travail diverses des

suites de benchmarks NPB et PTS.

Alors que les logiciels système modernes exécutent du code provenant de nombreuses sources avec des degrés de confiance variables, l'abstraction traditionnelle de la mémoire virtuelle ne permet pas l'isolation des parties non fiables d'une application partageant le même espace d'adressage virtuel. Tout le code s'exécutant au sein d'un processus a le même niveau de confiance. Par conséquent, un code tiers défectueux ou malveillant dans un processus peut compromettre le processus en divulguant ou modifiant directement la mémoire utilisée par d'autres composants de l'application. L'interface de la mémoire virtuelle doit être repensée pour permettre aux applications d'être compartimentées, implémentant le principe du moindre privilège en isolant les parties non fiables de l'application dans des compartiments avec un accès limité à certaines ressources de l'application. Nous présentons SecureCells, une nouvelle interface architecturale pour la compartimentation intraespace d'adressage. SecureCells permet aux applications de définir des vues de mémoire garantie par le matériel pour les compartiments d'application avec des instructions d'espace utilisateur accélérant les appels inter-compartiments. Dans des microbenchmarks, SecureCells permet à un cœur ordré à 5 étages de passer d'un compartiment à un autre en seulement 8 cycles, réduisant le coût des transitions d'un ordre de grandeur par rapport aux meilleures alternatives. Nous construisons également un prototype complet de SecureCells, basé sur le cœur RISC-V RocketChip exécutant le noyau seL4, pour évaluer des benchmarks d'espace utilisateur.

De plus, cette thèse présente la première systématisation des connaissances sur les mécanismes de compartimentation, évaluant à la fois les propriétés qualitatives et quantitatives. Nous décrivons les propriétés de sécurité et de performance pertinentes pour une compartimentation pratique, et montrons dans quelle mesure chaque mécanisme fournit chaque propriété. Une revue complète des techniques de compartimentation vise à permettre aux développeurs de systèmes informatiques de définir de future interfaces sécurisées, performantes et utilisables pour soutenir la compartimentation généralisée des applications. Notre systématisation expose les lacunes communes de ces mécanismes, orientant ainsi les efforts de recherche future vers des opportunités de soutien à une compartimentation plus exhaustive.

Cette thèse soutient que les interfaces entre les composants des systèmes informatiques modernes entravent leurs garanties de sécurité, et explore les problèmes de deux interfaces majeures. Nous montrons qu'une refonte raisonnée de ces interfaces permet la mise en œuvre de systèmes plus sécurisés tout en soutenant les besoins d'applications haute performance, avec la conception et la mise en œuvre de Midas et SecureCells pour résoudre les défis aux interfaces noyau-utilisateur et intra-processus respectivement.

# **Contents**

| Αd | cknow  | rledgments                                        | ٧    |

|----|--------|---------------------------------------------------|------|

| ΑI | bstrac | t                                                 | ix   |

| Li | st of  | Figures                                           | xvii |

| Li | st of  | Tables                                            | xix  |

| 1  | Intro  | oduction                                          | 1    |

|    | 1.1    | Kernel TOCTTOU Protection Overview                | 5    |

|    | 1.2    | Intra-address Space Compartmentalization Overview | 6    |

|    | 1.3    | Thesis Contributions                              | 8    |

|    |        | 1.3.1 Midas                                       | 9    |

|    |        | 1.3.2 SecureCells                                 | 9    |

|    | 1.4    | Thesis Organization and Details                   | 10   |

| 2  | Mid    | as: Systematic Kernel TOCTTOU Protection          | 13   |

|    | 2.1    | Introduction                                      | 14   |

|    | 2.2    | Background                                        | 15   |

|    |        | 2.2.1 Page Tables and Memory Protection           | 15   |

|    |        | 2.2.2 Linux Memory Subsystem                      | 16   |

|    |        | 2.2.3 Supervisor Memory Protection                | 17   |

|    |        | 2.2.4 Double-Fetch Bugs                           | 18   |

|    | 2.3    | Threat Model                                      | 19   |

|    | 2.4    | Attack Classification                             | 19   |

|    | 2.5    | Midas Design                                      | 21   |

|    |        | 2.5.1 Page State Machine                          | 23   |

|    |        | 2.5.2 Discussion                                  | 26   |

|    | 2.6    | Midas Implementation                              | 31   |

|    |        | 2.6.1 Tracking Page State                         | 32   |

|    |        | 2.6.2 Kernel Reads from User Memory               | 32   |

|    |        | 2.6.3 Handling Faults                             | 35   |

#### Contents

|   |      | 2.6.4 Syscall Completion                           | <br>37 |

|---|------|----------------------------------------------------|--------|

|   |      | 2.6.5 File System Writes                           | <br>38 |

|   |      | 2.6.6 New Mappings to Protected Pages              |        |

|   |      | 2.6.7 Discussion                                   | <br>39 |

|   | 2.7  | Evaluation                                         |        |

|   |      | 2.7.1 Mitigation of CVE-2016-6516                  | <br>40 |

|   |      | 2.7.2 Performance evaluation                       | <br>41 |

|   |      | 2.7.3 Overhead breakdown                           | <br>44 |

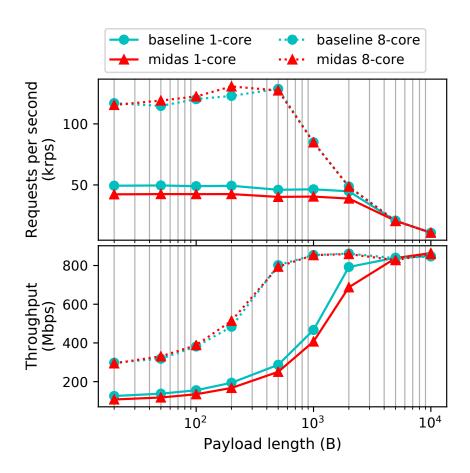

|   |      | 2.7.4 Case study: Nginx                            | 45     |

|   | 2.8  | Related Work                                       | <br>46 |

|   | 2.9  | Midas Summary                                      | <br>48 |

| 3 | Seci | reCells: A Secure Compartmentalized Architecture   | 49     |

|   | 3.1  | Introduction                                       | <br>50 |

|   | 3.2  | Background                                         | <br>52 |

|   |      | 3.2.1 Principles supporting compartmentalization   | <br>52 |

|   |      | 3.2.2 Compartmentalization properties              | <br>54 |

|   | 3.3  | Objectives For Architectural Isolation             | <br>54 |

|   |      | 3.3.1 Threat Model                                 | <br>55 |

|   |      | 3.3.2 Security Objectives                          | <br>57 |

|   |      | 3.3.3 Performance Objectives                       | <br>58 |

|   |      | 3.3.4 Flexibility                                  | <br>59 |

|   |      | 3.3.5 Alternate Visions for Compartmentalization   | <br>60 |

|   | 3.4  | SecureCells                                        | <br>62 |

|   |      | 3.4.1 Access control                               | <br>63 |

|   |      | 3.4.2 Userspace Instructions                       | <br>64 |

|   |      | 3.4.3 Software Mechanisms                          | <br>68 |

|   |      | 3.4.4 Implementation                               | <br>69 |

|   | 3.5  | Evaluation                                         | <br>70 |

|   |      | 3.5.1 Security Evaluation                          | <br>71 |

|   |      | 3.5.2 Performance Microbenchmarks                  | <br>74 |

|   |      | 3.5.3 Compartment Switching and Access Control     | <br>74 |

|   |      | 3.5.4 Compartmentalized pipeline                   | <br>76 |

|   | 3.6  | Related Work                                       | <br>78 |

|   | 3.7  | Discussion                                         | <br>80 |

|   | 3.8  | SecureCells Summary                                | <br>82 |

| 4 | SoK  | Classifying Compartmentalization Mechanisms        | 83     |

| - | 4.1  | Introduction                                       | <br>84 |

|   | 4.2  | Compartmentalization: A Deeper Dive                |        |

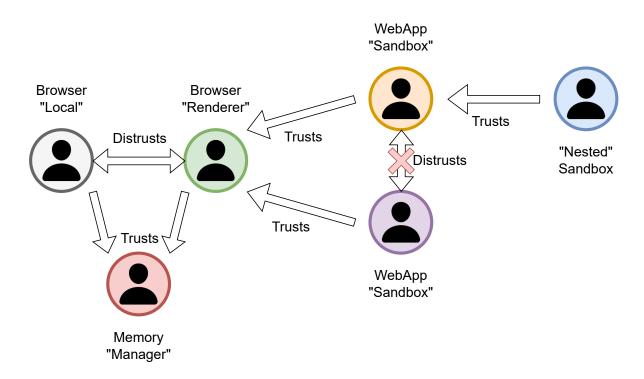

|   |      | 4.2.1 Example: <i>Browser</i> Compartmentalization |        |

|   |      | b.s. = =be.:                                       | <br>   |

|    |      | 4.2.2    | Execution Model and Threat Model            | 90   |

|----|------|----------|---------------------------------------------|------|

|    | 4.3  | Mecha    | anisms Implement Restrictions               | 91   |

|    |      | 4.3.1    | Resource Access                             | 91   |

|    |      | 4.3.2    | Operation Arguments                         | 94   |

|    |      | 4.3.3    | Instructions and Operations                 | 94   |

|    | 4.4  | Praction | cal Considerations                          | 95   |

|    | 4.5  | Evalua   | ating Mechanisms                            | 97   |

|    |      | 4.5.1    | Mechanisms Compared                         | 97   |

|    |      | 4.5.2    | Methodology and Rationale                   | 108  |

|    |      | 4.5.3    | Comparison                                  | 108  |

|    | 4.6  | Discus   | sion                                        | 114  |

|    |      | 4.6.1    | Opportunities                               | 114  |

|    |      | 4.6.2    | Limitations of our Methodology              | 115  |

|    | 4.7  | Summ     | ary                                         | 116  |

| 5  | Futi | ıre Wo   | r <b>k</b>                                  | 117  |

| •  | 5.1  |          | d Midas: Double-fetch Protection and More   |      |

|    | 5.2  | =        | pread Compartmentalization with SecureCells |      |

|    | 0.2  | Wides    | preda compartmentanzation with Securecens   | 0    |

| 6  | Con  | clusion  | 1                                           | 121  |

| Αį | pend | lices    | 1                                           | 123  |

| Α  | Mid  | as Arti  | fact                                        | 125  |

|    | A.1  | Artifac  | ct Appendix                                 | 125  |

|    |      | A.1.1    | Description                                 | 125  |

|    |      | A.1.2    | Installation                                | 126  |

|    |      | A.1.3    | Experiment Workflow                         | 127  |

|    |      | A.1.4    | Expected Results                            | 128  |

|    |      | A.1.5    | Artifact meta-information                   | 128  |

| В  | Seci | ıreCells | s Details                                   | 131  |

| _  | B.1  |          | ry layout of the unified PTable-GTable      | _    |

|    | B.2  |          | cation for Table 3.1                        |      |

|    | B.3  |          | ng mechanisms with SecureCells              |      |

|    | B.4  |          | Cells Implementation Trade-Offs             |      |

|    | B.5  |          | eCells ISA definitions                      |      |

|    | B.6  |          | rating SecureCells Instruction Emulation    |      |

|    | 2.0  | B.6.1    |                                             |      |

|    |      | D.U.     | Generic Trap-and-Emulate Acceleration       | 1,)/ |

|    |      |          | Generic Trap-and-Emulate Acceleration       |      |

#### Contents

| C Details for SoK on Compartmentalization C.1 Classification Data | Mechanisms         141 |

|-------------------------------------------------------------------|------------------------|

| Bibliography                                                      | 145                    |

| Curriculum Vitae                                                  | 165                    |

# **List of Figures**

| 1.1  | Illustrating the double-fetch attack at the system call interface                  | 5   |

|------|------------------------------------------------------------------------------------|-----|

| 1.2  | Illustrating intra-process trust components for an application                     | 6   |

| 2.1  | Example of a double-fetch bug                                                      | 18  |

| 2.2  | State diagram for a page in Midas                                                  | 23  |

| 2.3  | Diagram illustrating Midas preventing double-fetch exploitation                    | 24  |

| 2.4  | Diagram illustrating Midas preventing multi-page double-fetch exploitation         | 28  |

| 2.5  | Illustration of a theoretical speculative leakage attack against Midas' protection | 30  |

| 2.6  | Midas' bookkeeping information for a page                                          | 33  |

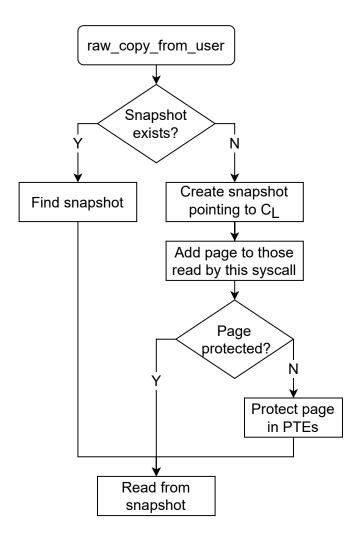

| 2.7  | Midas: Flowchart for the transfer function raw_copy_from_user                      | 34  |

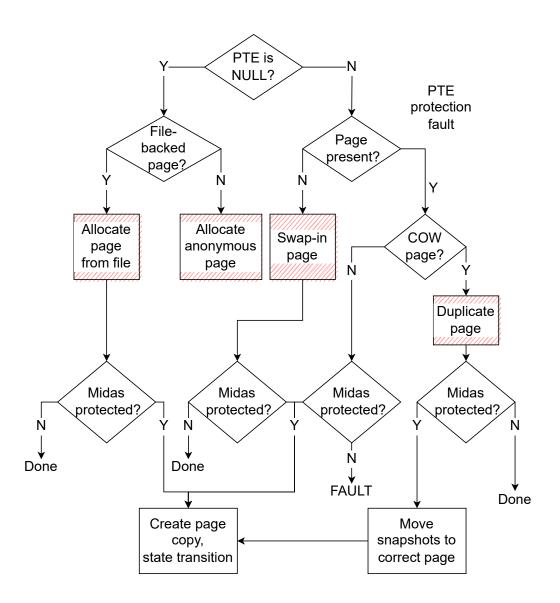

| 2.8  | Midas: Flowchart for handling a page fault                                         | 36  |

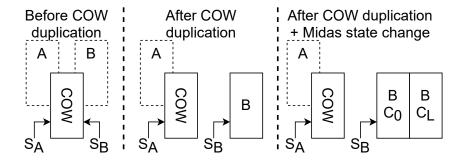

| 2.9  | Midas: Flowchart for handling a page fault to a COW page                           | 36  |

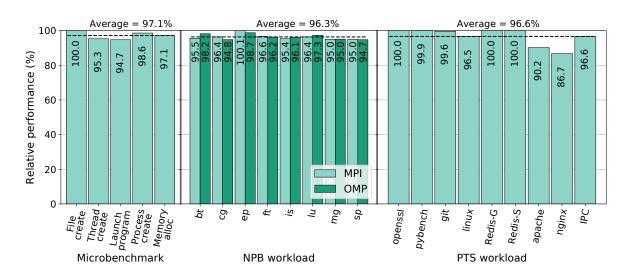

| 2.10 | Midas performance comparison                                                       | 42  |

| 2.11 | Classification of overheads for various benchmarks due to Midas                    | 44  |

| 2.12 | Midas: Request rates and throughput for the Nginx server                           | 46  |

| 3.1  | Browser compartmentalization with three compartments                               | 56  |

| 3.2  | Permission transfers for a packet between SecureCells compartments                 | 56  |

| 3.3  | SecureCells: Architecture                                                          | 62  |

| 3.4  | SecureCells: State and userspace instructions                                      | 65  |

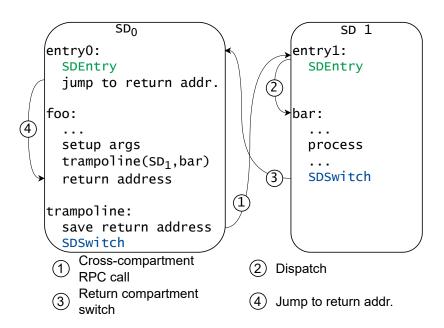

| 3.5  | Cross-compartment procedure call in SecureCells                                    | 68  |

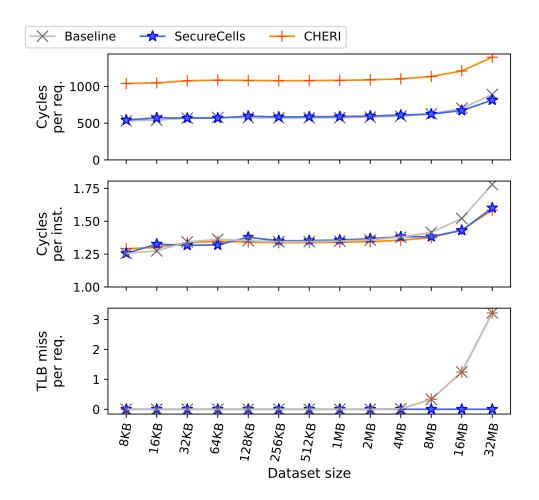

| 3.6  | SecureCells performance comparison: memcached                                      | 75  |

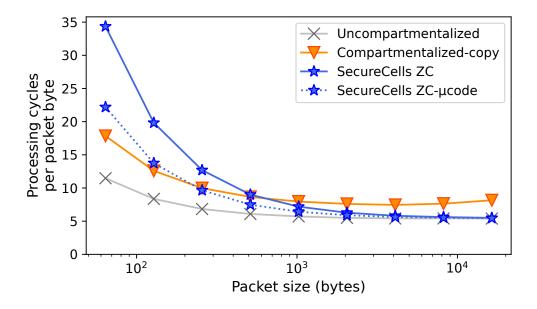

| 3.7  | SecureCells performance comparison: Network function                               | 77  |

| 4.1  | Architecture of a compartmentalized <i>Browser</i>                                 | 87  |

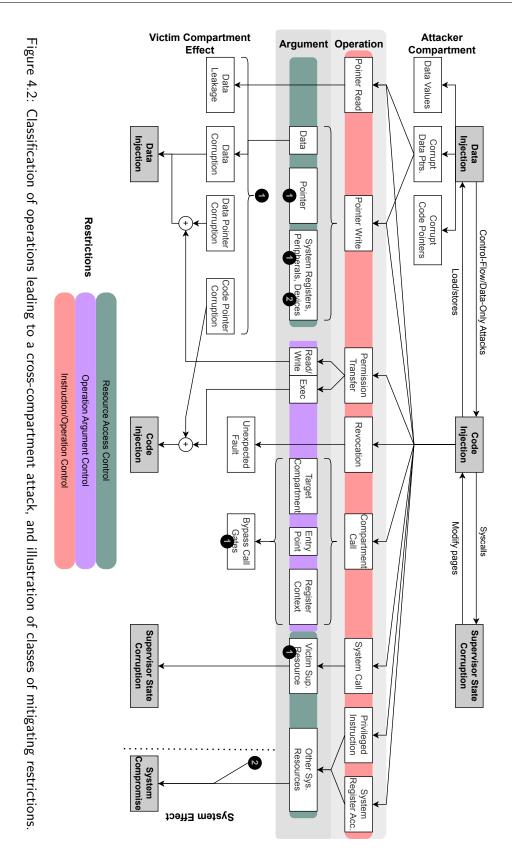

| 4.2  | Classification of operations leading to a cross-compartment attack                 | 92  |

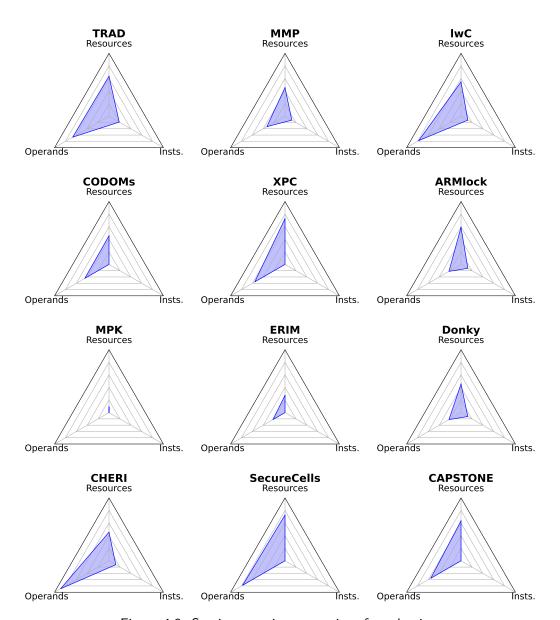

| 4.3  | Scoring security properties of mechanisms.                                         | 109 |

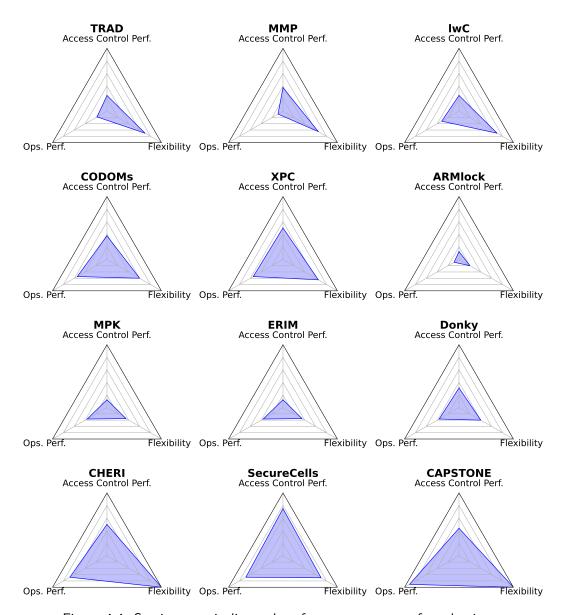

| 4.4  | Scoring practicality and performance aspects of mechanisms                         | 110 |

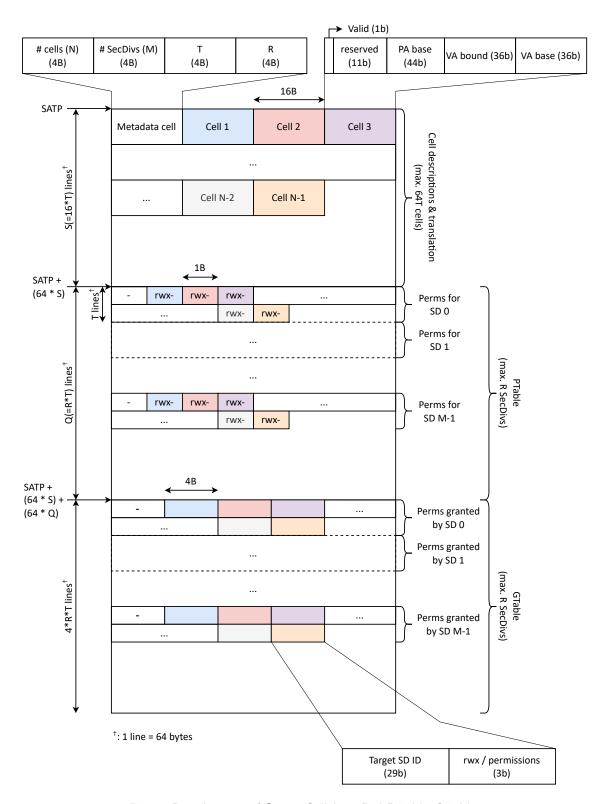

| R 1  | Layout of SecureCells' unified PTable-GTable                                       | 132 |

# **List of Tables**

| 2.1 | Attack vector classification for TOCTTOO exploits                     | 19  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | System calls uninstrumented by Midas                                  | 27  |

| 2.3 | Prominent syscalls used by OSBench microbenchmarks                    | 42  |

| 3.1 | Qualitative comparison of compartmentalization mechanisms             | 61  |

| 3.2 | Overview of SecureCells' userspace instructions                       | 64  |

| 3.3 | HW configuration of the SecureCells prototype                         | 71  |

| 3.4 | FPGA resource utilization for SecureCells' MMU                        | 71  |

| 3.5 | Compartment switching cost of various compartmentalization mechanisms | 73  |

| 3.6 | Cycles for emulating SecureCells instructions                         | 74  |

| 3.7 | Mapping SecureCells instructions to similar APIs                      | 81  |

| 4.1 | Summary of privileges restricted by compartmentalization mechanisms   | 93  |

| 4.2 | Summary classifying compartmentalization mechanisms                   | 98  |

| B.1 | Mapping SecureCells instructions to the RISC-V prototype instructions | 136 |

| B.2 | Instruction encodings for SecureCells' prototype                      | 136 |

| B.3 | SecureCells exception codes                                           | 139 |

| B.4 | Mapping SecureCells exception codes to values                         | 140 |

| C.1 | Scoring matrix for mechanisms for security guarantees                 | 142 |

| C.2 | Scoring matrix for mechanisms for performance and flexibility metrics | 143 |

# Chapter 1

# Introduction

The computing landscape is one of rapidly growing software and hardware complexity. Modern computing systems inherit many of the abstractions and interfaces developed at the inception of personal computing and mainframe servers, but face a very different computing environment. The complexity and scale of computing systems have increased exponentially over the decades, far outscaling the ability for developers to exhaustively test and verify their systems, leading to an abundance of bugs. Popular software runs hundreds of millions of lines of source code, with millions of lines worth of changes every year. Linux, a widely-used operating system, itself currently accounts for 23 million lines of code, roughly increasing 20x since the turn of the millennium. Transistor counts for processors have roughly followed Moore's law for the last 50 years, and a modern Apple M2 chip has more than a  $10^{11}$  transistors compared to the  $10^4$  transistors of the Motorola 68k processor from 1979. This scaling in complexity relies on, and also enables, pervasive code sharing. A web browser (e.g., Firefox) along with the underlying operating system (e.g., Linux) accounts for hundreds of millions of lines of code including

- mainline kernel code written by a informal melange of developers distributed across the globe with varying industrial/academic/governmental/individual affiliation,

- numerous device drivers written by the respective hardware vendors,

- shared libraries and modules developed independently and written in a plethora of languages,

- code from websites, often embedding other pages, written by their respective web developers.

Modern systems need to consider the threat of bugs in shared code compromising their security, and implement the necessary mitigations. For example, a web developer must account for the threat that any of the thousands of JavaScript packages their code depends on might be malicious, currently or in the future. The security of computing is reliant on the security properties at the

interfaces between components (trusted and untrusted). The abstractions and interfaces at the core of computer systems need to enable systems to face up to today's security challenges.

While computing systems have evolved significantly, interfaces between many parts of this system have remained relatively unchanged. The designs of these interfaces reflect the requirements and threat landscape from their respective design periods, but fail to adequately address modern needs. Linux, for example, started development in the 1990s and is heavily inspired by Unix, initially developed in the 1960s-70s. The Linux kernel system call interface is cognizant of the threat of attacks or faults from untrusted userspace compromising the kernel, reflecting the contemporary shared use of mainframes running applications for a limited set of known users. System calls, therefore, typically check the validity of arguments passed from userspace. However, computing and the associated threat vectors developed over the past 30 years, rendering Linux' original system call interface dated. Linux has evolved from being a hobby project to becoming the operating system underlying critical computer infrastructure forming the backbone of industries and governments. The threat model has simultaneously evolved from accidentally triggered bugs in applications leading to crashes, to sophisticated exploits developed by experienced attackers targeting remote control of the entire system. One consequence of the dated designs of key interfaces is that these interfaces might not adequately mitigate threats that have arisen or worsened after the design of the interface. Since the 1990s, computing has evolved to support increased concurrency and true parallelism, with the rise in popularity of multicore CPUs and multi-threaded programs. For system call arguments stored in user memory and passed by reference, this evolution has enabled data races if the user program modifies the arguments from a second thread while the kernel executes a system call from one thread. This trend extends to other interfaces with widespread usage. The C programming language, dating back to the 1970s, remains in popular use despite the lack of memory safety by default. The rise of the internet and corresponding emergence of cyber warfare has exacerbated the effects malicious exploitation of memory safety bugs, leading to major vulnerabilities (e.g., Heartbleed [90], GHOST [91] and NetUSB [92]). A second consequence is that interfaces might not provide the correct abstractions to efficiently support designs that reflect trust relations within parts of modern applications. For example, the dominant abstraction for isolation within userspace code is a process, and different applications typically execute in different processes to isolate applications from bugs in other applications. The process virtual memory interface is supported by hardware enforced page table permissions across major commercial instruction set architectures (x86, SPARC, ARM) developed across the 1970s and 1980s. Process isolation is well suited to the historical state of software development where software vendors wrote their own applications with limited code sharing between vendors. Processes isolated code for one application, from one software vendor, from other applications, from other software vendors or for another user. With more code within applications originating from third-party developers and less trust in code run within a single process, intra-process isolation has become crucial. Security-critical programs, like browsers, microservices and microkernel operating systems (OSs), refactored to enforce intra-application isolation using processes are limited by the high overheads of this abstraction, and only support coarse-grained isolation to cap performance overheads [11, 86, 88].

Recognizing emerging threats, key interfaces have gradually evolved, fixing bugs and introducing new defense features. Most improvements tend to be incremental. By adding a NX/XD bit to mark pages as non-executable, popular processor architectures added support for Data Execution Prevention (DEP) and prevented code injection exploiting buffer overflows. Over the years, millions of commits have added various patches to Linux. However, many improvements address individual bugs while failing to comprehensively improve an interface's security. Continuing industrial and academic efforts have proposed various improvements to improve the kernel-user boundary and add support for isolation within an application. The security of operating system kernels is an area of active research, and many methodologies have been proposed to fix the issue of data races at the system call interface, primarily focussing on finding and fixing instances of this class of bugs. One group of proposals leverage static analysis [80, 136, 138, 147] to comb through the kernel codebase looking for vulnerable double fetches. These static analysis techniques have progressively improved from matching code against known double-fetch bug patterns to symbolic execution-based analyzers. Alternative proposals leverage dynamic analysis to detect instances of data races at runtime [59, 114, 143] by tracking kernel memory accesses while executing various common workloads (for e.g., booting up, running a browser, playing multimedia). Eliminating the discovered data race bugs by fixing source code allows the kernel to present a more secure interface, though the invulnerability to data races remains an informal assumption rather than a guarantee. Finally, a proposed mitigation [114] repurposes a CPU-specific feature designed for accelerating database transactions to instead dynamically detect user updates between kernel double fetches, rolling back the system call execution to prevent exploitation. Bug squashing techniques, however, are insufficient — they can only fix bugs found — and both static and dynamic analysis are incomplete. The significant churn in code further complicates the challenge, as every change potentially introduces new double-fetch bugs. The proposed mitigation is also inadequate, since the protection depends on a vendor-specific feature which has since also been deprecated on newer processors. The system call interface requires a more principled and reliant mitigation against data race attacks. Similarly, while researchers and processor vendors continue to propose mechanisms for finer-grained isolation within a process' address space, these mechanisms vary in their design goals, and do not adequately support widespread adoption of compartmentalization. Mechanisms which prioritize backward compatibility with existing systems [40, 52, 55, 69, 76] introduce the security benefits of intra-address space isolation but continue to suffer the consequences of other legacy design choices, such as expensive supervisor-mediated context switches. Some mechanisms [52, 96] trade off performance for security, either providing weaker security than processes to provide better performance or making restrictive assumptions on application use cases. A common approach among researchers is to retrofit protections to vulnerable interfaces abusing the side effects of unrelated mechanisms co-existing on the systems, bringing immediate protection to certain systems at the cost of a few fundamental shortcomings. Researchers have applied this approach to both mitigate double-fetch bugs [114] using Intel TSX and to implement compartmentalization [52, 69] using Intel VT-x. This approach is limited by dependence on specific systems (using Intel CPUs, for example) and potentially inhibits concurrently using applications requiring these features for

#### Chapter 1. Introduction

their proper functioning. Most importantly, such defense mechanisms lack principled design and resemble targeted protections rather than fundamental security guarantees baked into interface design.

Security guarantees should inform the design of interfaces — either by extending or redesigning interfaces. At the kernel-user interface, we see that data races require the kernel to access the same argument in user memory at least twice, which allows the user to modify the data in the meantime. In fact, such bugs which are generally called double-fetch bugs commonly (but not exclusively) manifest from the same usage pattern. The kernel first loads arguments once to check their validity, then loads them at a later time in order to use them. This pattern earns these bugs the popular moniker of Time-of-Check to Time-of-Use (TOCTTOU) bugs. Double-fetch bugs contain an implicit assumption by the developer that the fetched data is the same, which may be violated by another thread through a concurrent modification. OS kernels generally use a software interface to access user memory, to manage protections like Supervisor Memory Access Prevention (SMAP), and we can extend this interface with a secure invariant. Within userspace applications, the requirements for isolation have changed drastically: from isolating per-user processes which occupy millisecond-scale scheduling slots to finer grained module or library-level isolation, which demands sub-microsecond operations (for example, switching trust domains). An userspace process needs to be further divided into isolated compartments which can communicate along well-defined APIs. OS-based mechanisms are expensive — even supervisors optimized for inter-process communication (IPC) on commodity hardware achieve microsecond-scale compartment switches at best. We notice that the traditional trusted-computing base (TCB) includes the processor hardware alongside the supervisor. Hence, we can securely delegate particular operations (access control, inter-compartment control, and data flow) from the supervisor to the hardware, improving performance while maintaining the same security guarantees. Improvements and trends in microarchitectural design, such as the move towards virtual memory area-based access control in the core's translation-lookaside buffer (TLB) [51], greatly assist in this transition.

In this thesis, we present secure designs for the user-kernel interface used by processes, and for interfaces between intra-process domains, both of which are security- and performance-critical. Midas provides systematic protection to the user-kernel interfaces against double-fetch attacks by maintaining an invariant: through a system call's lifetime, every read to a userspace object will return the same value. Midas can also be extended as a sanitizer, enabling detection of TOCTTOU attacks against the kernel. To validate the design, we also present an implementation of Midas on the Linux kernel. SecureCells, meanwhile, is a compartmentalization mechanism providing isolation between interacting userspace compartments. SecureCells' design is based on three pillars: hardware-enforced access control for isolation, unprivileged instructions for accelerating common operations and flexible software operations where necessary. SecureCells is the first mechanism to combine the security and performance requirements for flexible fine-grained intra-address space compartmentalization.

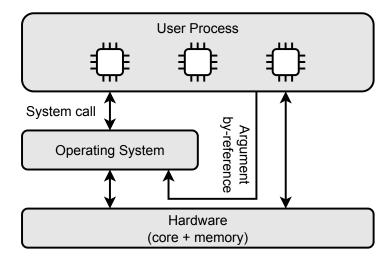

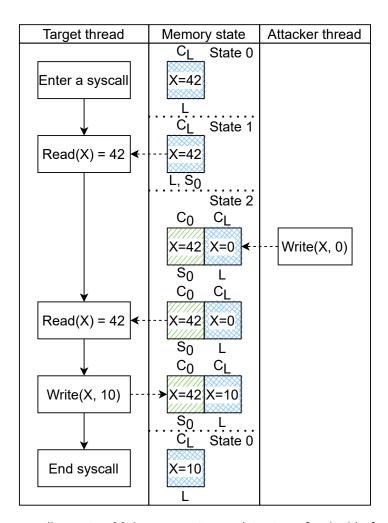

Figure 1.1: Illustrating the double-fetch attack at the system call interface

#### 1.1 Kernel TOCTTOU Protection Overview

The operating system (OS) kernel is a key component of modern computer systems, tasked with multiplexing resources like memory, execution time and I/O among users on a shared machine, or among different tasks by the same user. The kernel is part of the system's trusted computing base (TCB), and interacts with untrusted userspace processes through system calls (syscalls). The userspace/kernel interface is a security-critical barrier, and forms the primary attack vector for attacker processes to compromise an entire system. The kernel must, therefore, implement extensive checks at this interface to protect itself from malicious arguments to syscalls. Most modern OS kernels trace their heritage to systems designed or developed in the 1980's and 90's, and inherit many of their system calls. The Linux, Darwin/XNU (used by MacOS) and FreeBSD kernels are all mostly compatible with the POSIX interface, first defined in 1988 [9]. The POSIX interface, itself, draws inspiration from the UNIX kernel first published in 1971. Over this time, the computing landscape has evolved immensely. Whereas the original UNIX kernel was not designed for multi-tasking, the modern desktop, server or mobile computing environment involves a multi-user, multi-tasking, multi-processing systems connected via internal or internet interfaces. Kernel security has come under ever-increasing threats, and requires stronger protection guarantees.

Untrusted userspace processes interact with the kernel using system calls, passing arguments by value (through registers) or by reference (in memory), as illustrated in Figure 1.1. When an argument is passed by reference, and the kernel loads the same value twice, an attacking user process can leverage the temporal window between the loads to modify the value in memory, potentially triggering a kernel bug. Double-fetch bugs plague operating system kernels, but also extend beyond to the similar OS-hypervisor interface [26–32, 34–36]. For example, the user could pass a buffer, and its corresponding length as arguments, then later maliciously change the length to influence the

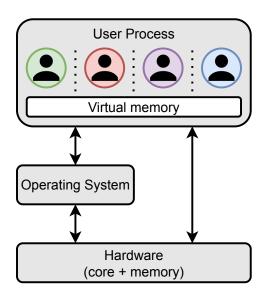

Figure 1.2: Illustrating intra-process trust components for an application

kernel to access memory outside the buffer. A time-of-check to time-of-use (TOCTTOU) violation occurs when the first read is used to validate an argument (example, the length above) and the second read is to use the argument. More generally, a double-fetch bug manifests as system call code which reads the same argument (passed by a user application by reference) two or more times. Double-fetch bugs might be particularly difficult to identify, as the two reads might be in entirely different parts of the kernel, or even in external code loaded through the eBPF interface or as modules. Additional kernel security, such as through system call filters like SecComp [115], could also introduce double-fetches if extended to include "deep argument inspection" (i.e., arguments passed by reference).

A systematic mitigation for double-fetch bugs must guarantee that a system call will always read the same argument values. Therefore, the mitigation must prohibit or hide all concurrent changes to memory objects accessed by the kernel during the execution of a system call, including writes from threads in the same process, other processes, or from concurrently executing system calls. The userspace memory access interface can be tasked with providing the required guarantee for argument accesses.

#### 1.2 Intra-address Space Compartmentalization Overview

The complexity and rapid pace of change of modern software systems inevitably leads to a plethora of bugs across the stack. Open source projects regularly encounter and fix a steadily increasing stream of bugs and vulnerabilities in their codebases [124–126]. System developers heavily rely on abstraction and isolation to tackle application complexity stemming from interacting subsystems,

an extensive list of shared libraries, plugins, interpreted code and on-demand downloaded code, interacting over untrusted I/O interfaces such as the network, disks, various accelerators, and peripherals. Each software component hides much of its complexity behind an accessible interface (commonly called Application Programming Interfaces or APIs). Traditional threat models have resulted in isolation at a few security-critical interfaces. The operating system (OS) kernel tasked with system management is already isolated from userspace processes running untrusted applications. Commercial hardware provides the abstraction of privilege levels, allowing the kernel to reliably isolate itself within a separate level. The kernel isolates applications from different users and different applications from the same user using a common abstraction: processes. Processes protect applications from other faulting or malicious applications, with isolated per-process virtual memory spaces and kernel resources. These abstractions provide systems crucial security and robustness guarantees. Applications cannot access other applications' memory spaces, or the kernel's data. The kernel can gracefully handle an application faulting, killing the corresponding process without affecting itself or other applications. Essentially, these abstractions work to mirror the trust relations between components of the massive code base. However, existing interfaces fail to protect systems against more recent threat models.

Rapid development in computing, supercharged by the explosion of the internet, has resulted in applications which cannot trust all code executing within its process. A bug in the one logging module allowed attackers to leverage the Log4J vulnerability to compromise entire server applications, and remotely take over the machines running these applications. A browser, for example, contains hundreds of shared libraries and executes code downloaded from untrusted websites. To prevent website code, controlled by a remote adversary, from directly accessing local resources, modern browsers are already compartmentalized into two components: an internet-facing rendering engine running in one process interacting with a separate local system-facing kernel process using a welldefined API over remote procedure calls (RPCs). This architecture is motivated by the browser's strong security requirements, but remains limited by the coarse-grained abstraction of isolation (processes) available on traditional systems. Bugs in the sandbox within the rendering engine can still compromise all other components in the sandbox, including the just-in-time compiler. The first key limitations of the process abstraction is that all code within a process is equally privileged and can equally access all of that process' resources including memory. The second limitation of this abstraction is that interactions between processes require system calls incurring microsecond-scale overheads. The first limitation prevents applications from implementing and enforcing barriers expressing the complex trust relations between code components. Applications rely on complex software isolation techniques like sandboxing and software fault isolation, which are buggy at scale. The second downside limits how finely applications can be decomposed into processes, due to performance overhead considerations. However, the process abstraction is flexible and widely supported, and remains the mechanism of choice for usable isolation.

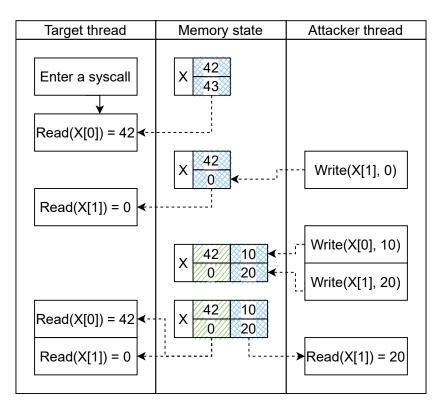

Modern software requires an intra-address space compartmentalization mechanism that provides strong isolation for application components running within the same address space (see Figure 1.2),

#### Chapter 1. Introduction

with low-overhead nanosecond-scale operations to support compartments with short nanosecond-scale execution timescales, all while maintaining the flexibility to support a variety of software trust relationships. In this thesis, we highlight that the limitations of the process abstraction stem from the software-hardware design of virtual memory. First, page-based virtual memory requires permission and translation tracking at page granularity, and near-core permission caching buffers (TLBs) whose entry count cannot scale with the rate of growth of memory. Second, the privileged kernel is tasked with changing between memory permissions (involving changing page tables) and incurs the unacceptable cost of kernel entry and exits.

Systems can implement secure and performant compartmentalization by moving key checks and operations from the supervisor into the hardware. While the hardware is part of the trusted-computing base, its view of virtual memory remains rooted in the designs of the 80s. A compartmentalized abstraction of virtual memory, with the hardware capable of tracking compartments and enforcing the requisite permissions to memory, can eliminate the kernel overheads while preserving strong security checks. Further, the hardware can accelerate specific common compartmentalization operations for data and control flow if it is aware of compartments. Finally, operations which do not benefit from hardware acceleration can be retained in software, retaining the accompanying flexibility.

#### 1.3 Thesis Contributions

This thesis aims to protect systems by redesigning interfaces to satisfy the security and performance requirements of modern and future computing systems, against emerging threat models. While the security of current systems is of paramount importance, the performance of these systems must also satisfy strict deployment requirements. Foremost, we prioritize the security of our proposed interfaces, and consider performance as a crucial secondary requirement. For the user-kernel interface, we consider compatibility with the existing system call semantics as an essential requirement. For intra-address space compartmentalization, we deem the flexibility of the interface to support varying software use-cases to be vital for adoption.

We present two redesigned security- and performance-critical interfaces, specifically the user-kernel boundary and intra-process trust domain boundaries. We add strongly-guaranteed protection against double-fetch bugs to the system call interface. Further, we introduce a intra-address space mechanism for isolating untrusted application parts. Finally, we present a comprehensive survey of existing and proposed compartmentalization mechanisms to enable a principled comparison of these mechanisms.

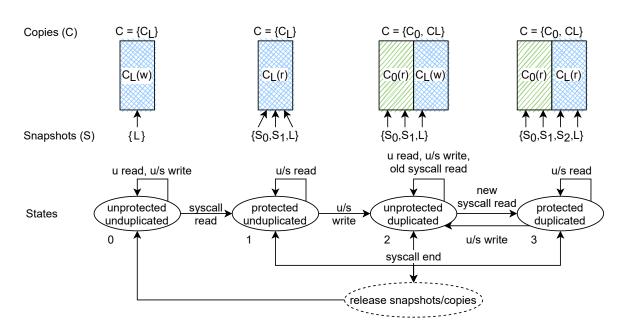

#### 1.3.1 Midas

Midas presents a multi-versioning concurrency control mechanism, inspired from database systems, for maintaining a key invariant during user data accesses from system calls: through a system call's lifetime, every read to a userspace object will return the same value. A security property derived from this invariant is enforced — Midas uses kernel metadata to track userspace pages accessed, maintains page-table permissions to enforce immutability and leverages page faults to on-demand duplicate pages where necessary to preserve an original copy for a system call. A correctness property is also described in this thesis, showing how the system's execution remains correct under execution with Midas. Since, the user-kernel interface is performance-critical and affects the system's performance on syscall-intensive workloads, Midas' design optimizes for low overheads. As concurrent writes to system call arguments are practically non-existent for well-behaved programs, Midas strives to minimize expensive page duplications and relies on snapshotting for protecting accesses.

Midas has numerous use cases. First, Midas defends against existing, even potentially unknown, double-fetch bugs on current and future systems. Second, Midas can protect the kernel against double-fetch bugs in dynamically-added code such as modules and eBPF code. Third, Midas can enable system call filters to securely examine arguments passed by reference without introducing vulnerable double-fetches. Finally, Midas can protect older systems, where modules or other vulnerable components lack bug-fixing updates, with a single update to the kernel core.

We have implemented a Midas prototype for the Linux kernel, demonstrating its practicality, and evaluated the system's performance during system-call dependent workloads from the NAS Parallel Benchmark Suite (NPB) and the Phoronix Test Suite (PTS). Midas results in an average performance overhead of 3.7% on NPB and 3.4% on PTS. We also perform a security evaluation to demonstrate that Midas successfully stops an attack against a vulnerable system call.

#### 1.3.2 SecureCells

In this work, we also present a comprehensive set of objectives for a compartmentalization mechanism to support widespread adoption. SecureCells presents a novel virtual memory architecture for secure, high-performance, flexible intra-address space compartmentalization. SecureCells maintains the strong security guarantees of process-based isolation for fine-grained compartments within a process, with a mix of hardware and software support. SecureCells tracks the compartment executing on a core, and implements access control to memory regions based on a supervisor determined permission table stored in memory. Additionally, SecureCells provides unprivileged instructions to implement fast compartmentalization operations, specifically inter-compartment calls, zero-copy permission transfer to data regions, and to manage lifetimes for data regions. Each of these instructions includes specific checks and controls to maintain specific security properties, including preventing

#### Chapter 1. Introduction

privilege escalation, code injection and data races. Finally, SecureCells delegates operations to software when the corresponding hardware implementation would bring no advantage.

This work also describes our prototype SecureCells implementation, including the RTL description of an in-order core based on the RISC-V RocketChip design, a QEMU port for quick emulation, porting of the seL4 microkernel operating system, and simplified versions of server benchmarks. We investigate the performance characteristics of our prototype core, using microbenchmarks designed to test the limits of access control, compartment switching and dataflow between compartments, and compare them to related work. SecureCells' in-order core can switch between compartments (a key performance metric) in as few as 8 cycles, which compares favorably to state-of-the-art compartmentalization mechanisms and is orders of magnitude faster than the traditional process abstraction. We also demonstrate that SecureCells can help isolate the networking and data storage of a memcached-like benchmark with a small (<3%) overhead even for the smallest requests. These improvements are a direct consequence of tailoring the software-hardware interface to the requirements of modern programs.

#### Thesis statement

Critical interfaces underlying computing systems must adapt to support mitigating emerging threats and to enable the performance demanded by modern applications. Interfaces at key trust boundaries, e.g., between untrusted intra-process components and at the kernel-userspace border, especially require strong isolation at low overheads.

#### 1.4 Thesis Organization and Details

**Thesis Organization.** This thesis is distributed across three chapters. Chapter 2 describes Midas, the systematic mitigation to kernel double-fetch bugs. Chapter 3 describes SecureCells, a novel secure and performant mechanism for intra-address space compartmentalization. Finally, Chapter 4 contains a comprehensive comparison of compartmentalization mechanisms along qualitative and quantitative metrics.

**Bibliographic Notes.** This thesis was supervised by my advisors, Prof. Mathias Payer and Prof. Babak Falsafi. Sections of the thesis describe projects conducted in collaboration with academic peers, namely Uros Tesic, Florian Hofhammer, Yuanlong Li, Siddharth Gupta, and Andres Sanchez. This thesis contains contributions from the following conference publications:

Atri Bhattacharyya, Uros Tesic, and Mathias Payer. "Midas: Systematic Kernel TOCTTOU Protection". In: 31st USENIX Security Symposium, USENIX Security 2022, Boston, MA, USA, August 10-12, 2022. Ed. by Kevin R. B. Butler and Kurt Thomas. USENIX Associ-

- ation, 2022, pp. 107-124. ISBN: 978-1-939133-31-1. URL: https://www.usenix.org/conference/usenixsecurity22/presentation/bhattacharyya

- Atri Bhattacharyya, Florian Hofhammer, Yuanlong Li, Siddharth Gupta, Andrés Sánchez, Babak Falsafi, and Mathias Payer. "SecureCells: A Secure Compartmentalized Architecture". In: 44th IEEE Symposium on Security and Privacy, SP 2023, San Francisco, CA, USA, May 21-25, 2023. IEEE, 2023, pp. 2921–2939. ISBN: 978-1-6654-9336-9. DOI: 10.1109/SP46215.2023.10179472. URL: https://doi.org/10.1109/SP46215.2023.10179472

During the course of his PhD studies, the author of this thesis also contributed to other projects resulting in the publications listed below. The results from these publications are not included in this thesis.

- Lana Josipovic, Atri Bhattacharyya, Andrea Guerrieri, and Paolo lenne. "Shrink It or Shed It! Minimize the Use of LSQs in Dataflow Designs". In: *International Conference on Field-Programmable Technology, FPT 2019, Tianjin, China, December 9-13, 2019*. IEEE, 2019, pp. 197–205. ISBN: 978-1-7281-2943-3. DOI: 10.1109/ICFPT47387.2019.00031. URL: https://doi.org/10.1109/ICFPT47387.2019.00031

- Atri Bhattacharyya, Alexandra Sandulescu, Matthias Neugschwandtner, Alessandro Sorniotti, Babak Falsafi, Mathias Payer, and Anil Kurmus. "SMoTherSpectre: Exploiting Speculative Execution through Port Contention". In: Proceedings of the 2019 ACM SIGSAC Conference on Computer and Communications Security, CCS 2019, London, UK, November 11-15, 2019. Ed. by Lorenzo Cavallaro, Johannes Kinder, XiaoFeng Wang, and Jonathan Katz. ACM, 2019, pp. 785–800. ISBN: 978-1-4503-6747-9. DOI: 10.1145/3319535.3363194. URL: https://doi.org/10.1145/3319535.3363194

- Atri Bhattacharyya, Andrés Sánchez, Esmaeil Mohammadian Koruyeh, Nael B. Abu-Ghazaleh, Chengyu Song, and Mathias Payer. "SpecROP: Speculative Exploitation of ROP Chains". In: 23rd International Symposium on Research in Attacks, Intrusions and Defenses, RAID 2020, San Sebastian, Spain, October 14-15, 2020. Ed. by Manuel Egele and Leyla Bilge. USENIX Association, 2020, pp. 1–16. ISBN: 978-1-939133-18-2. URL: https://www.usenix.org/conference/raid2020/presentation/bhattacharyya

- Siddharth Gupta, Atri Bhattacharyya, Yunho Oh, Abhishek Bhattacharjee, Babak Falsafi, and Mathias Payer. "Rebooting Virtual Memory with Midgard". In: 48th ACM/IEEE Annual International Symposium on Computer Architecture, ISCA 2021, Valencia, Spain, June 14-18, 2021. IEEE, 2021, pp. 512–525. ISBN: 978-1-6654-3333-4. DOI: 10.1109/ISCA52012.2021.00047. URL: https://doi.org/10.1109/ISCA52012.2021.00047

# Chapter 2

# Midas: Systematic Kernel TOCTTOU Protection

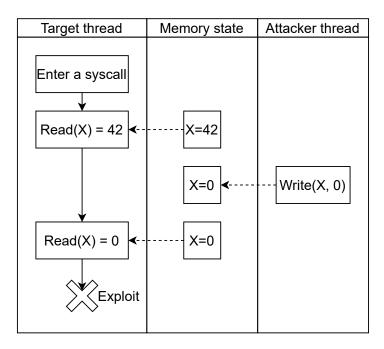

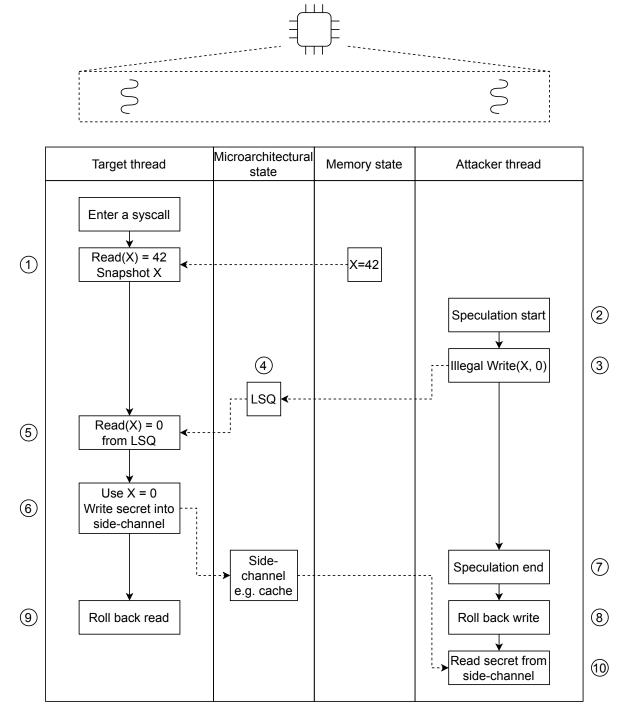

Double-fetch bugs are a plague across all major operating system kernels. These bugs occur when data is fetched twice across the user/kernel trust boundary while allowing concurrent modification, violating an implicit assumption at this interface. Double-fetches enable an attacker to illegally access memory, cause denial of service, or to escalate privileges. So far, the only protection against double-fetch bugs is to detect and fix them. However, existing methods to find double-fetch bugs are incomplete. The double-fetch problem also fundamentally prohibits efficient, kernel-based stateful system call filtering. Thus, we propose *Midas* to mitigate double-fetch bugs and secure the system call interface. Midas creates on-demand snapshots and copies of accessed data, enforcing the key invariant that throughout a system call's lifetime, every read to a userspace object will return the same value.

Midas shows no noticeable drop in performance when evaluated on compute-bound workloads. On system call heavy workloads, Midas incurs 0.2-14% performance overhead, while protecting the kernel against any TOCTTOU attacks. On average, Midas shows a 3.4% overhead on diverse workloads across two benchmark suites.

#### 2.1 Introduction

The operating system (OS) kernel provides isolation between processes and is a key component of the system's trusted computing base. Each untrusted userspace process runs under a dedicated user in its own address space and must request resources (such as communication channels or changes to its address space) from the trusted kernel. The userspace/kernel interface forms an explicit trust barrier; all data that crosses this boundary in either direction must be carefully checked by the kernel. Userspace processes attack the kernel by issuing system calls (syscalls) that then trigger kernel bugs, elevating the privileges of the process. A common class of kernel bugs are so-called double-fetch bugs [117, 128, 137, 143]. They occur when higher-privileged code, such as the kernel, reads the same data from the lower-privileged address space twice. Double-fetch bugs are a race condition between threads of different privileges. A time-of-check to time-of-use (TOCTTOU) violation occurs when the first read is used to check a condition while the second read is used to modify state. An example of a double fetch bug is when the kernel reads the length of a buffer from userspace, allocates a kernel buffer, then reads the length a second time to finally copy the data from userspace to the kernel. An attacker may concurrently overwrite the length of the buffer (with a larger number) after allocation, causing the memory copy to overflow the kernel buffer. Double-fetch bugs are a frequent problem in kernels and hypervisors [26–32, 34–36]. Watson [140] blames an unfixable TOCTTOU constellation as a reason for the generic insecurity of syscall wrappers. Syscall filtering wrappers require that data read from userspace for the initial check remains the same when the kernel later uses it for computation. Therefore, such filters can currently only check arguments passed by value. Midas enables "deep argument inspection" for SecComp [115, 116] and Janus [134] (i.e., checks arguments passed by reference). Without Midas, such inspection is impossible: these checks introduce double fetches, and consequently TOCTTOU bugs.

To mitigate double-fetch bugs in the kernel, a system must prohibit concurrent changes  $^1$ to memory accessed by the syscall. Attackers may find crafty ways to trigger such concurrent writes, including: i) direct writes from userspace (e.g., from concurrent threads), ii) kernel writes from syscalls (e.g., from concurrent syscalls), iii) modifying address space mappings, iv) concurrent write syscalls to a file that alters mapped file pages, and v) storing arguments on device-backed pages, leveraging devices to trigger concurrent writes. To prevent attacks, all concurrent writes must be prohibited.

"Through a syscall's lifetime, every read to a userspace object will return the same value."

We base our defense on one key invariant, stated above. From this invariant we derive a *security* property ensuring that every read during the execution of a syscall is tracked. Subsequent reads

<sup>&</sup>lt;sup>1</sup>The attacker model includes both concurrent and parallel writes. For readability, this chapter refers to both writes as "concurrent".

from the same address will always return the same value. For performance, multiple versions of an object may exist simultaneously, depending on when the syscall was started and how many concurrent syscalls are in flight. Orthogonally, we derive a *correctness property* that ensures the sharing of the correct version among inflight syscalls. All writes end up on the most recent version of the objects, guaranteeing forward progress. While we implement this invariant in our Midas prototype for the Linux kernel, this defense applies to any modern OS kernel.

Our evaluation of Midas demonstrates low performance overhead. On workloads from the NAS Parallel Benchmarks suite, Midas shows an average performance overhead of 3.7%. Similarly, its performance overhead on more kernel-intensive workloads from the Phoronix Test Suite is 3.4% (with negligible memory overhead). Our security evaluation demonstrates how Midas successfully stops all attacks against vulnerable syscalls. Our contributions are:

- Distillation of TOCTTOU attack vectors into an invariant that protects the kernel against malicious concurrent modifications,

- Midas, a design that prohibits and detects TOCTTOU attacks against modern kernels, prohibiting their exploitation, enabling developers to detect TOCTTOU bugs, and providing the foundation for safe syscall interposition and validation, and

- An efficient implementation of Midas for the Linux kernel that exhibits low (3.4%) performance overhead.

#### 2.2 Background

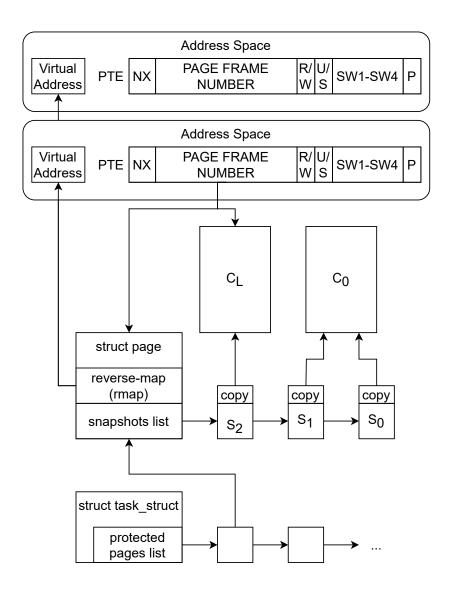

Midas orchestrates several mechanisms within the Linux memory subsystem to provide its protection guarantees. Linux uses architecturally defined per-address space page tables to define mappings to pages. Midas protects these pages by temporarily marking them read-only in the page tables. This section provides background information necessary to reason about why and how Midas protects syscalls from concurrent writes.

#### 2.2.1 Page Tables and Memory Protection

Virtually all contemporary architectures (e.g., x86, ARM, SPARC, and RISC-V) implement separate virtual and physical address spaces (AS) based on fixed-size regions called pages. Programs execute in their virtual address space while caches and main memory are accessed with physical addresses. Architectures rely on page tables orchestrated by the operating system to translate between these address spaces and to protect memory accesses. Page tables are arranged as radix trees, where different bits of the virtual address are used as indices into successive levels of the page table.

#### Chapter 2. Midas: Systematic Kernel TOCTTOU Protection

At the leaf page table, a unique page table entry (PTE) stores the translation and protection information for a page.

A PTE in x86-64 is a 64-bit value holding, among others, the following metadata: a *Present bit (P)* to mark the PTE's validity; *Protection bits (NX, R/W, U/S)* to restrict the type of access and the privilege level of the accessing code; *Software-usable bits (SW1-SW4)* that are ignored by the MMU and used by the operating system to store metadata; and a *Page Frame Number (PFN)* to identify the page's physical address. The U/S separates kernel (supervisor) pages from user pages. The R/W controls whether pages are writable or not.

An access using a virtual address first reads the corresponding PTE's present bit to check its validity. Then, the access checks whether the access is allowed from the executing code's privilege level by checking the U/S bit and whether the read/write access is allowed by checking the R/W bit. When all checks pass, the processor uses the PFN to find the data in the caches or in memory. When a check fails, the processor raises a protection fault/exception and moves control to an OS-specified exception handler.

Reading PTEs from a multi-level page table is an expensive operation, and modern processors cache PTEs in caches known as Translation Lookaside Buffers (TLBs) to reduce the cost of subsequent accesses. On most architectures, the OS is responsible for keeping TLBs coherent with the page table, necessitating entries to be flushed from TLBs when the corresponding PTE is updated. Modern multiprocessing CPUs have a TLB for each core, and PTE information may be cached in one or more TLBs. Therefore, when the OS changes a PTE value, the OS is also responsible for flushing remote TLBs (i.e., on another cores) as required. Commercial-off-the-shelf systems typically rely on an inter-process interrupt (IPI) to the OS running on a remote core followed by a local TLB invalidation. Due to the scalability limitations of broadcasting IPIs to remote cores, the TLB invalidation process is highly optimized in software, and has received dedicated hardware support in more recent processors and in research proposals [108, 132, 150].

#### 2.2.2 Linux Memory Subsystem

Linux implements various abstractions—including processes, files, and shared memory—using the architecture's page tables. All threads within a Linux process share a single address space, and consequently use the same page table for translation and protection. Each page within the process' virtual address space may be mapped or unmapped. Mapped pages have separate read/write/execute permissions. Programs typically have write-execute exclusion, meaning code pages cannot be written to and data pages cannot be executed. These permissions map directly to page-table bits. Pages in Linux may also be copy-on-write (COW) pages, which are mapped read-only in multiple address spaces, but duplicated when any process writes to it, resulting in a separate copy.

Linux maintains userspace and kernel mappings to memory in distinct parts of the virtual address space. The PTE entries for kernel mappings, located in the top half of the address space, have the U/S bit set. These kernel mappings are identical for all address spaces, and are kept consistent across the corresponding page tables. In contrast, the PTE entries for userspace mappings, located in the bottom half of the address space, have the U/S bit reset. A userspace page has at least one userspace mapping and at least one kernel mapping. Shared userspace memory is implemented by mapping a page in more than one address space.