# COMPUTING OF COMPU

- Data Engineering

- Cloud Computing

- QuantumComputing

- History

MARCH 2022

www.computer.org

# CALL FOR SPECIAL ISSUE PROPOSALS

Computer solicits special issue proposals from leaders and experts from a broad range of computing communities. Proposed themes/issues should address timely, emerging topics that will be of broad interest to Computer's readership. Special issues are an important component of Computer, as they deliver essential research insights and well-developed perspectives on new and established technologies and computing strategies.

We encourage submissions of high-quality proposals for the 2023 editorial calendar. Of particular interest are proposals centered on:

- offsite educational and business continuity technology challenges,

- privacy related to personal location tracking and surveillance (digital and physical),

- · artificial intelligence and machine learning,

- $\cdot$  technology's role in disrupted supply chains,

- misinformation and disinformation (fake information—malicious or non-malicious), and

- $\cdot \ \ \text{cyberwarfare/cyberterrorism}$

Proposal guidelines are available at:

www.computer.org/csdl/magazine/co/write-for-us/15911

### **STAFF**

**Editor** Cathy Martin

Production & Design Artist

Carmen Flores-Garvey

**Publications Portfolio Managers** Carrie Clark, Kimberly Sperka

**Publisher** Robin Baldwin **Senior Advertising Coordinator**

Debbie Sims

Circulation: ComputingEdge (ISSN 2469-7087) is published monthly by the IEEE Computer Society. IEEE Headquarters, Three Park Avenue, 17th Floor, New York, NY 10016-5997; IEEE Computer Society Publications Office, 10662 Los Vaqueros Circle, Los Alamitos, CA 90720; voice +1 714 821 8380; fax +1 714 821 4010; IEEE Computer Society Headquarters, 2001 L Street NW, Suite 700, Washington, DC 20036.

**Postmaster:** Send address changes to *ComputingEdge*-IEEE Membership Processing Dept., 445 Hoes Lane, Piscataway, NJ 08855. Periodicals Postage Paid at New York, New York, and at additional mailing offices. Printed in USA.

**Editorial:** Unless otherwise stated, bylined articles, as well as product and service descriptions, reflect the author's or firm's opinion. Inclusion in *ComputingEdge* does not necessarily constitute endorsement by the IEEE or the Computer Society. All submissions are subject to editing for style, clarity, and space.

Reuse Rights and Reprint Permissions: Educational or personal use of this material is permitted without fee, provided such use: 1) is not made for profit; 2) includes this notice and a full citation to the original work on the first page of the copy; and 3) does not imply IEEE endorsement of any third-party products or services. Authors and their companies are permitted to post the accepted version of IEEE-copyrighted material on their own Web servers without permission, provided that the IEEE copyright notice and a full citation to the original work appear on the first screen of the posted copy. An accepted manuscript is a version which has been revised by the author to incorporate review suggestions, but not the published version with copy-editing, proofreading, and formatting added by IEEE. For more information, please go to: http://www.ieee.org/publications\_standards/publications

/rights/paperversionpolicy.html. Permission to reprint/republish this material for commercial, advertising, or promotional purposes or for creating new collective works for resale or redistribution must be obtained from IEEE by writing to the IEEE Intellectual Property Rights Office, 445 Hoes Lane, Piscataway, NJ 08854-4141 or pubs-permissions@ieee.org. Copyright © 2022 IEEE. All rights reserved.

**Abstracting and Library Use:** Abstracting is permitted with credit to the source. Libraries are permitted to photocopy for private use of patrons, provided the per-copy fee indicated in the code at the bottom of the first page is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

**Unsubscribe:** If you no longer wish to receive this *ComputingEdge* mailing, please email IEEE Computer Society Customer Service at help@computer.org and type "unsubscribe *ComputingEdge*" in your subject line.

IEEE prohibits discrimination, harassment, and bullying. For more information, visit www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

# **IEEE Computer Society Magazine Editors in Chief**

### Computer

Jeff Voas, *NIST*

# Computing in Science & Engineering

Lorena A. Barba, George Washington University

# IEEE Annals of the History of Computing

Gerardo Con Diaz, *University* of California, Davis

# IEEE Computer Graphics and Applications

Torsten Möller, Universität Wien

### IEEE Intelligent Systems

Longbing Cao, *University* of Technology Sydney

### **IEEE Internet Computing**

George Pallis, *University* of Cyprus

### **IEEE Micro**

Lizy Kurian John, *University* of Texas at Austin

### IEEE MultiMedia

Shu-Ching Chen, Florida International University

### **IEEE Pervasive Computing**

Marc Langheinrich, *Università* della Svizzera italiana

### **IEEE Security & Privacy**

Sean Peisert, Lawrence Berkeley National Laboratory and University of California, Davis

## **IEEE Software**

Ipek Ozkaya, Software Engineering Institute

### **IT Professional**

Irena Bojanova, NIST

Validating "Data Validation" 18

The Next Wave in Cloud Systems

Architecture

24

Interhost

Orchestration

Platform

Architecture for

Ultrascale Cloud

Applications

# **Data Engineering**

Data Labeling for the Artificial Intelligence Industry: Economic Impacts in Developing Countries

NIR KSHETRI

12 Validating "Data Validation"

NORITA AHMAD AND KEVIN DIAS

# **Cloud Computing**

18 The Next Wave in Cloud Systems Architecture

AMIN VAHDAT AND DEJAN MILOJICIC

24 Interhost Orchestration Platform Architecture for Ultrascale Cloud Applications

SASKO RISTOV, THOMAS FAHRINGER, RADU PRODAN, MAGDALENA KOSTOSKA, MARJAN GUSEV, AND SCHAHRAM DUSTDAR

# **Quantum Computing**

Emerging Technologies for Quantum Computing

JONATHAN M. BAKER AND FREDERIC T. CHONG

40 Quantum Computing

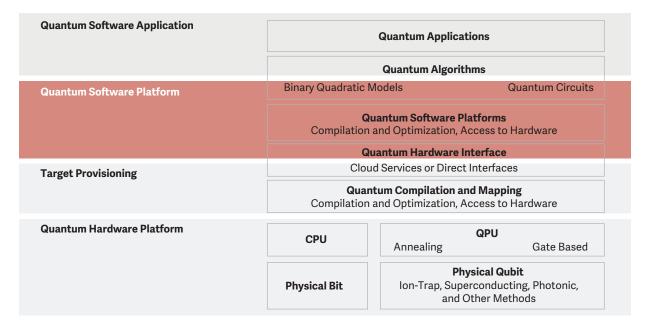

JOSE LUIS HEVIA, GUIDO PETERSSEN, CHRISTOF EBERT, AND MARIO PIATTINI

# **History**

48 Preserving the Past by Industry Participants

JAMES W. CORTADA

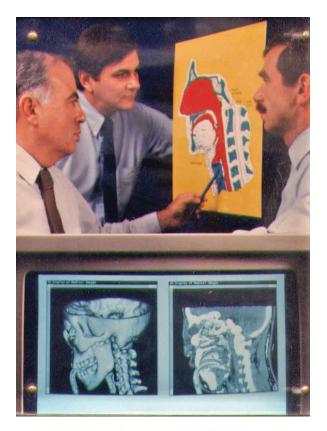

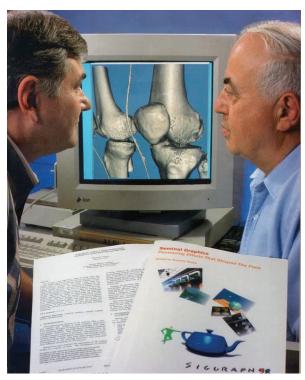

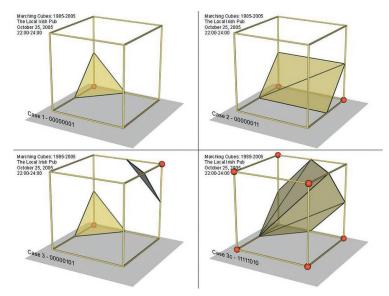

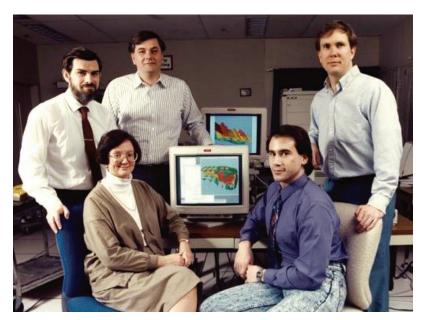

51 History of the Marching Cubes Algorithm

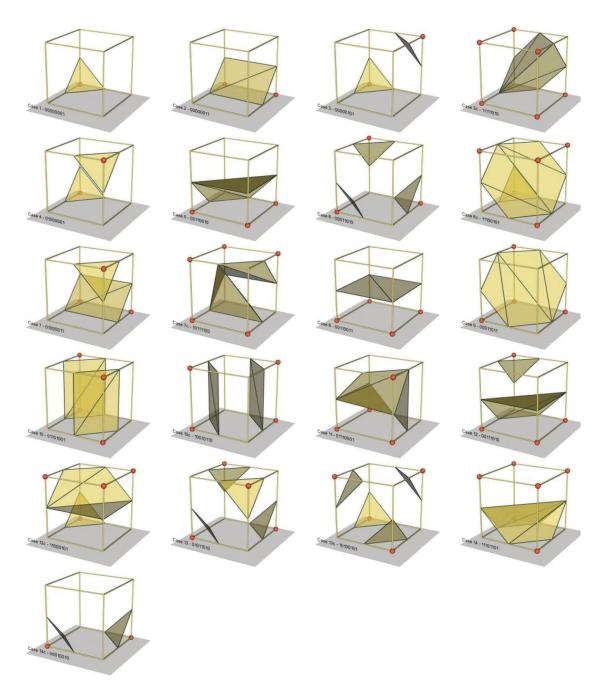

WILLIAM E. LORENSEN

# **Departments**

- 4 Magazine Roundup

- 7 Editor's Note: The People behind the Data

- 58 Conference Calendar

Subscribe to *ComputingEdge* for free at www.computer.org/computingedge.

# Magazine Roundup

he IEEE Computer Society's lineup of 12 peer-reviewed technical magazines covers cutting-edge topics ranging from software design and computer graphics to Internet computing and security, from scientific applications and machine intelligence to visualization and microchip design. Here are highlights from recent issues.

# Computer

# When Scientific Software Meets Software Engineering

The authors of this article from the December 2021 issue of *Computer* investigate the different levels of abstraction, linked to the diverse artifacts of the scientific software development process, that a software language can propose and the validation and verification facilities associated with the corresponding level of abstraction the language can provide to the user.

# **Computing**

Reproducibility Practice in High-Performance Computing: Community Survey Results

In a recent survey of the SC conference community, the authors of this article from the September/ October 2021 issue of Computing in Science & Engineering collected information about the SC reproducibility initiative activities. Results show that the reproducibility initiative activities have contributed to higher levels of awareness on the part of SC conference

technical program participants, and hint at contributing to greater scientific impact for the published papers of the SC conference series. Stringent point-of-manuscript-submission verification is problematic, as are inherent difficulties of computational reproducibility in HPC. Future efforts should better decouple the community educational goals from goals that specifically strengthen a research work's potential for long-term impact through reuse 5 to 10 years down the road.

# Leonardo Torres Quevedo: Pioneer of Computing, Automatics, and Artificial Intelligence

The search for little-known pioneers of automation, missed fathers or mothers of the computer, unfamiliar founders of computer science, or unrecognized creators of artificial intelligence invites us to look at the past with an open mind. In this article from the July–September 2021 issue of *IEEE Annals of the History of Computing*, the authors provide a comprehensive examination of the

almost unknown contribution of a Spanish pioneer in all those fields during the first two decades of the 20th century, the engineer and mathematician Leonardo Torres Quevedo (1852–1936).

# Computer Graphics

# DeepGD: A Deep Learning Framework for Graph Drawing Using GNN

Many graph drawing techniques have been proposed for generating aesthetically pleasing graph layouts, but it remains a challenging task since different layout methods tend to highlight different characteristics of the graphs. Recently, studies on deep learning-based graph drawing algorithms have emerged, but they are often not generalizable to arbitrary graphs without retraining. In this article from the September/October 2021 issue of IEEE Computer Graphics and Applications, the authors propose a convolutional graph neural networkbased deep learning framework, DeepGD, which can draw arbitrary graphs once trained. It attempts to generate layouts by compromising among multiple prespecified

aesthetics, considering a good graph layout usually complies with multiple aesthetics simultaneously. To balance the tradeoff, they propose two adaptive training strategies, which adjust the weight factor of each aesthetic dynamically during training.

# liitelligent Systems

# An Emotional Recommender System for Music

Recommender systems have become essential to users for finding "what they need" within large collections of items. Meanwhile. recent studies have demonstrated that user personality can effectively provide more valuable information to significantly improve recommenders' performance, especially considering behavioral data captured from social network logs. In this article from the September/October 2021 issue of IEEE Intelligent Systems, the authors describe a novel music recommendation technique based on the identification of personality traits, moods, and emotions of a single user, starting from solid psychological observations recognized by the analysis of user behavior within a social environment. Users' personality and mood have been embedded within a content-based filtering approach to obtain more accurate and dynamic results.

# **Internet Computing**

# Future of HPC: The Internet of Workflows

Driven by convergence with artificial intelligence and data analytics, increased heterogeneity, and a hybrid cloud/on-premises delivery model, dynamic composition of workflows will be a key design criteria of future high-performance computing (HPC) systems. While tightly coupled HPC workloads will continue to execute on dedicated supercomputers, other jobs will run elsewhere, including public clouds and at the edge. Connecting these distributed computing tasks into coherent applications that can perform at scale is what the authors of this article from the September/October 2021 issue of IEEE Internet Computing call "Internet of Workflows."

# The Birth of the Microprocessor

The story starts in February 1968 when the author of this article from the November/December 2021 issue of *IEEE Micro* joined Fairchild Semiconductor R&D Lab in Palo Alto, CA, USA. At that time, nearly all the integrated circuits in production used bipolar technology. Metal–oxide–semiconductor

(MOS) technology was up and coming but still had many problems; it was extremely slow and was not yet reliable. The author believed that the future of digital electronics belonged to MOS technology because one could integrate in the same silicon area ten times more logic gates with half the number of manufacturing steps required by bipolar technology.

# **MultiMedia**

# EGGAN: Learning Latent Space for Fine-Grained Expression Manipulation

Fine-grained facial expression aims at changing the expression of an image without altering facial identity. Most current expression manipulation methods are based on a discrete expression label, which mainly manipulates holistic expression with details neglected. To handle the above-mentioned problems, the authors of this article from the July-September 2021 issue of IEEE MultiMedia propose an end-to-end expressionguided generative adversarial network (EGGAN), which synthesizes an image with expected expression given continuous expression label and structured latent code. An adversarial autoencoder is used to translate a source image into a structured latent space. The encoded latent code and the target expression label are input to a conditional GAN to synthesize an image with the target expression. A perceptual loss and a multiscale structural similarity loss are introduced to preserve facial identity and global shape during expression manipulation.

# Electronic Textile Gaia: Ubiquitous Computational Substrates Across Geometric Scales

From in-body implantables to geotextiles and large-area spacecraft blankets, electronic fabric is now poised to operate across geometric scales that span many orders of magnitude, and thus operational contexts across with divergent material resiliency requirements—reaching far beyond the wearable device regime that is typically considered. This article from the July-September 2021 issue of IEEE Pervasive Computing reviews the key technical trends and lingering hurdles that are relevant to using functional fibers and e-textiles for operating at disparate scales. The authors focus on leveraging the unique material properties of a textile and the miniaturization of electronic devices in concert with the revolution in mass-manufacturing and digital fabrication technologies used to customize the device at the level of polymer, fiber, fabric, three-dimensional form, and system.

# SECURITY& PRIVACY

# A Research Road Map for Building Secure and Resilient Software-Intensive Systems

Poor software engineering processes can result in insecure and brittle software-intensive systems. A new US agenda addresses this by advancing development and architectural paradigms, and by providing concrete research and development recommendations. The authors of this article from the November/December 2021 issue of IEEE Security & Privacy propose that the security community work closely with the software engineering community to realize secure, resilient software-intensive systems.

# Söftware

# Managing Technical Debt Under Uncertainty

Managing technical debt in the presence of uncertainty is a fundamental problem and an open challenge. The authors of this article from the November/December 2021 issue of *IEEE Software* provide an overview of the research, practical limitations, and future study of the current state of technical debt management under uncertainty.

# **Professional**

# A Process Model for Service-Oriented Development of Embedded Software Systems

The concepts of service-oriented computing (SOC) have previously

been used in the embedded systems domain, mostly at the device level in ad hoc manners to achieve advantages of device integration. However, SOC has not been used for the development of embedded software systems (ESS), i.e., software controlling the embedded devices. To fill this gap, a process model is proposed in this article from the September/October 2021 issue of IT Professional that allows the systematic development of ESS based on SOC concepts. The proposed process consists of analysis and design phases of embedded software development. The analysis phase is concerned with the collection of system information and preparation for system design. Based on this, the service-based software architecture is developed in the design phase. The effectiveness of the proposed process model is demonstrated through its application in a smart home case study. 9

# The People behind the Data

ata engineers are responsible for collecting and preparing the data that we rely on in myriad industries and contexts. Despite advances in data analysis software, humans often perform better than algorithms at certain tasks, such as data labeling and validation. This ComputingEdge issue reflects on the essential role of data engineers and highlights developments in the field.

IT Professional's "Data Labeling for the Artificial Intelligence Industry: Economic Impacts in Developing Countries" describes the labor-intensive work of data labelers and how this new type of job has grown in countries like China and India. Computer's "Validating 'Data Validation'" proposes a dashboard as a means for an experienced data

practitioner to monitor automated processes to ensure data quality and accuracy.

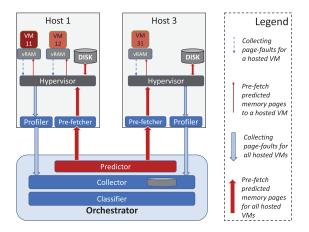

Large amounts of data are stored and processed in the cloud. In Computer's "The Next Wave in Cloud Systems Architecture," experts discuss emerging data-hosting approaches such as hybrid, multicloud, and edge. In IEEE Internet Computing's "Interhost Orchestration Platform Architecture for Ultrascale Cloud Applications," the authors present an intelligent page management method to reduce memory utilization and access time in cloud datacenters.

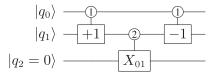

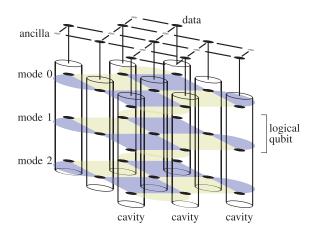

Both hardware and software will need to adapt to quantum computing. In *IEEE Micro's* "Emerging Technologies for Quantum Computing," the authors aim to improve quantum hardware scalability by evaluating new technologies such as superconducting resonant cavities and neutral atoms. The authors of *IEEE Software's* "Quantum Computing" argue that software development methodologies must evolve to address a future with quantum technology.

Finally, this ComputingEdge issue features two articles about the history of computing. In "Preserving the Past by Industry Participants," from IEEE Annals of the History of Computing, the author encourages practitioners in industry to preserve materials related to computing history. "History of the Marching Cubes Algorithm," from IEEE Computer Graphics and Applications, recounts the creation of an influential and widely used algorithm in computer graphics.

March 2022

# **DEPARTMENT: IT ECONOMICS**

# Data Labeling for the Artificial Intelligence Industry: Economic Impacts in Developing Countries

Nir Kshetri, University of North Carolina at Greensboro

rtificial intelligence (AI) applications, although at a nascent stage of development, are already having considerable economic and social impacts in developing countries. An equally fascinating and important aspect of the development of the global AI industry is that a high proportion of jobs that require relatively low skills in this industry are being performed by the developing countries. The multibillion-dollar data labeling industry represents an interesting example to illustrate this trend.

According to the professional services firm PwC, Al's contribution to the global economy will reach about US\$16 trillion by 2030 (https://www.pwc.com/gx/en/issues/data-and-analytics/publications/artificial-intelligence-study.html). Accurately labeling data for training machine learning (ML) models is integral to the creation of this value. The global market for data labeling, also known as content labeling or data annotation, is expected to reach US\$5 billion by 2023.<sup>2</sup>

Data labeling activities, however, are extremely time and labor intensive. Developing countries are in a position to take advantage of the opportunities provided by the global AI industry. This phenomenon has thus created a whole new industry of data labeling in developing countries, which is described as "a new type of blue-collar industry" (https://www.forbes.com/sites/korihale/2019/05/28/google-microsoft-banking-on-africas-ai-labeling-workforce/#34b0fd0d541c). Data labelers are referred to as the blue-collar workers of the AI age (https://towardsdatascience.com/the-invisible-workers-of-the-ai-era-c83735481ba).

# DATA LABELING IN DEVELOPING COUNTRIES POWERING THE GLOBAL AI INDUSTRY

Data need to be cleaned, categorized into appropriate groups, and labeled so that Al algorithms can

1520-9202 © 2021 IEEE Digital Object Identifier 10.1109/MITP.2020.2967905 Date of current version 31 March 2021. recognize patterns.3 For instance, for ML algorithms to accurately recognize a car, the algorithms may need to be trained with a large number of car pictures (https://www.vice.com/en\_us/article/7xyabb/china-aidominance-relies-on-young-data-labelers). In the most common form of Al-the supervised learning-the algorithms need to be fed with millions of pretagged examples of car pictures until they correctly identify the pictures.2 These activities need a large amount of human labor. For instance, one hour of video data related to autonomous driving may need as much as 800 man-hours of data labeling work (https://www. axios.com/ai-data-labeling-billion-dollar-market-409704bc-e63c-4af0-b0d0-44424abcd561.html). Estimates suggest that data labeling activities account for as much as 80% of the time needed to build AI systems.4

Labeling data for some AI apps may need high levels of skills and knowledge. For instance, to develop an AI app to detect cancer on images from a CT scan, experienced radiologists may have to train the algorithms (https://towardsdatascience.com/the-invisible-workers-of-the-ai-era-c83735481ba). However, there are many tasks that computers lack the capability to perform as well as ordinary human beings. Even less-skilled workers can easily be trained to perform such tasks. Most data labeling trainings can be completed in a short period of time. For instance, in order to learn their tasks, data labelers at iMerit typically take a one-week online training course via video calls with U.S.-based trainers.<sup>4</sup>

Table 1 provides some examples of data labeling companies operating in developing economies. These firms mainly serve foreign clients. Chinese data labeling firms such as MBH, on the other hand, mainly support the domestic Al industry.

In China, which has gained global prominence in recent years in the AI field, research and development activities to support the growth of the AI industry are conducted in wealthy cities such as Beijing, Shanghai, Hangzhou, and Shenzhen. Most of the data labeling

| <b>TABLE 1.</b> Some Examples of Data Labeling Companies Operating in Developing Economies. | TABLE 1. Some Examp | oles of Data Labeling | Companies Operation | ing in Developing Economies. |

|---------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------------------------------|

|---------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------------------------------|

| Data labeling company | Operations and workforce                                                                                                                                                     | Profiles of clients                                                                                                                                                                                                                                   |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iMerit                | Based in India and the U.S. 2500 in data labeling centers in India such as Ranchi, Shillong, Vizag, and Kolkata (https://tinyurl.com/y465cqmq).                              | 90% are U.Sbased (https://tinyurl.com/<br>yyzn8vjd).                                                                                                                                                                                                  |

| Samasource            | Offices in San Francisco, New York, the Hague, Kenya, and Uganda. Global staff of 2900: East Africa's largest AI and data annotation employer (https://tinyurl.com/wqanmja). | Include 25% of the Fortune 50 companies including major automakers and U.Sbased technology companies such as Google, Microsoft, and IBM (https://tinyurl.com/qnwlgxo).                                                                                |

| MBH                   | 300,000 in China's backward provinces (https://tinyurl.com/yeb7qtbb).                                                                                                        | Mainly Chinese companies such as the Beijing-based video-sharing social networking platform TikTok.                                                                                                                                                   |

| Playment              | Based in India and the U.S. More than 300 000 crowdsourced data labelers (https://tinyurl.com/y2dqm3c3).                                                                     | Over 100 customers in more than 12 countries (https://tinyurl.com/upp4wsu). Some include Samsung, Didi Chuxing Technology, Alibaba, Drive.ai, and Continental AG. Most clients are in the autonomous vehicle industry (https://tinyurl.com/y2dqm3c3). |

works, on the other hand, are performed in the country's disadvantaged regions such as smaller towns and rural areas in Shandong, Henan, Hebei, and Shanxi provinces in the North.<sup>5</sup> In particular, Henan Province is the epitome of an economy that has experienced an Al-led transformation. The Province's Zhengzhou city has been known for the manufacturing plants of Taiwanese electronics company Foxconn. It was estimated that Foxconn employed about 350 000 people and produced about half of the world's iPhones in Zhengzhou in 2016 (https://www.businessinsider.com/apple-iphone-factory-foxconn-china-photos-tour-2018-5).

The growth in data labeling also reflects the influences of a number of trends in the manufacturing sector. First, manufacturing activities have become increasingly automatized. For instance, between 2012 and 2016, Foxconn was reported to deploy tens of thousands of robots, which replaced more than 400 000 jobs. The company's plan includes full automation of 30% of production activities by 2020 (https://www.scmp.com/economy/china-economy/article/2185993/man-vs-machine-chinas-workforce-starting-feel-strain-threat).

Second, manufacturing jobs in China are declining due to a decline in the country's economic growth and, hence, demand for products, increasing costs, and competition from other economies (https://www.nytimes.com/2016/07/23/business/international/china-jobs-donald-trump.html). For instance, the Boston Consulting Group's study conducted in 2015 found that manufacturing costs in some of China's major

manufacturing hubs were almost at the same levels as in the U.S. Unsurprisingly, many western companies have been moving and relocating manufacturing activities into other developing countries in Asia as well as to the U.S., Canada, and Mexico (https://www.nytimes.com/2016/07/23/business/international/china-jobsdonald-trump.html). For instance, factory workers in Bangladesh and Vietnam can be hired for less than a quarter and a half, respectively, of the salary of a Chinese worker.

Finally, there has been a generational shift in preference for work. An increasing number of Chinese millennials do not like dull, boring, and tedious factory jobs (https://www.latimes.com/world/la-fg-china-millennials-jobs-20190512-story.html).

The upshot of the above is a decline in industrial manufacturing and exports in China. For instance, Henan's mobile phone exports reduced by 23.7% in January 2019 compared to a year earlier (https://www. scmp.com/economy/china-economy/article/2188162/ foxconn-tale-slashed-salaries-disappearing-benefitsand-mass). China's economically backward regions are embarking on ambitious plans to develop the data labeling industry. For instance, North China's landlocked province Shanxi, which is among the poorest provinces in China, plans to attract more than 100 data labeling companies and train more than 10 000 workers by 2022. The province's goal is to have a RMB 5 billion (US\$726 million) industry by 2025 (https:// kr-asia.com/data-labeling-jobs-are-coming-tounderdeveloped-regions-in-china-but-can-they-stay).

Workers who were employed in assembly lines and construction sites before are thus finding new jobs in the Chinese data labeling industry.<sup>6</sup>

Partly as a response to the decline in manufacturing activities, in recent years, data labeling companies are mushrooming in the towns and villages of backward regions such as the Henan province. In the Pingdingshan village of the province, some large data labeling projects are reported to employ tens of thousands of people.

# ECONOMIC AND SOCIAL IMPACTS OF THE DATA LABELING INDUSTRY

Finding high quality AI talents such as ML engineers has been big challenge for companies in developing economies (https://factordaily.com/india-ai-talent-gap-google-microsoft/). For instance, India is estimated to have only about 50-75 AI researchers (https://via.news/asia/artificial-intelligence-development-india/). According to India's skill assessment company Aspiring Minds' Annual Employability Survey 2019, 80% of Indian engineers were considered to be unfit for a job. The survey also found that only 2.5% of them had skills required by the AI industry (https://www.businesstoday.in/current/corporate/indian-engineers-tech-jobs-survey-80-per-cent-of-indian-engineers-not-fit-for-jobs-says-survey/story/330869. html). India has also faced a severe shortage of qualified faculty members to teach AI courses in its universities. 9

On the other hand, there is an abundant supply of low-skill and low-wage labors in India and other developing countries. For instance, Indian high schools graduated 20 million students in 2017.<sup>10</sup> There are, however, only a few job opportunities available to absorb these graduates. As an example, in a Mumbai city police's job advertisement for 1137 constable positions with US\$357/month salary, which required only a high school education, over 200 000 people applied. Many of the candidates had been trained in highly skilled jobs such as doctors, lawyers, and engineers.<sup>11</sup>

In light of the high rates of unemployment and underemployment in developing countries, the economic impacts of the newly emerging data labeling industry are undoubtedly important. However, controversies have arisen regarding ethical and fair practices of data labeling firms.

Some data labeling firms have been accused of paying low wages to their workers. In this way, organizations engaged in this industry are allegedly facilitating a "new kind of slavery in the digital era" (https://www.weforum.org/agenda/2019/08/ai-low-skilled-workers/).

Although some data labeling firms have claimed to produce positive social effects, such claims cannot be easily verified. There are virtually no regulations that govern the working conditions of data labelers. Industry standards related to ethical sourcing are weak. There is no standard for reporting data-labeling firms' social impacts. There is also the lack of validation of such impacts by third parties. There is little hard evidence to counter critics' concerns that these firms claiming that they engage in impact sourcing is nothing more than marketing gimmicks or "impact-washing." <sup>3</sup>

Some data labeling firms such as CloudFactory, DDD, iMerit, and Samasource are members of the Global Impact Sourcing Coalition (GISC), which was founded in 2016. Among other measures, the GISC has established an "impact sourcing standard." The standard defines minimum requirements that the GISC members are to satisfy. It has also provided voluntary best practices for employment. The GISC requires its members' performance on criteria such as nondiscrimination and equal pay to be assessed every two years.<sup>3</sup>

When it comes to promoting ethical and socially responsible behaviors, however, the GISC at best is of questionable effectiveness and value. For instance, the violators face no penalty or sanction if they do not pass the assessment. They do not lose the GISC membership, the GISC members also differ significantly in the terms of the information they publish. Samasource's impact audits report includes indicators such as workforce demographics and the number of people lifted from poverty. The data labeling firm DDD's reports contain information about employees' earnings and increase in lifetime income. CloudFactory had not published social impact report since 2015. As of 2019, iMerit had not published any such reports.3 The U.S.-based provider of data labeling and annotation services Alegion, which is not a GISC member, has outlined broad targets that it seeks to achieve but lacks specific metrics.3

Another challenge that arises here is that unlike fair-trade goods that are directly sold to consumers, data labeling firms provide their services to businesses. These firms thus face little public pressure to be honest, and it is ineffective to pressure them to engage in ethical practices.<sup>3</sup>

# **SUMMARY**

The rapidly growing global AI industry has created demands for highly skilled jobs such as ML engineers and data scientists, as well as less-skilled works such as those of data labelers. In particular, most AI

systems heavily rely on human-powered data labeling activities. Developing countries provide very large and seemingly bottomless sources and resources to support these activities to boost the global AI industry. Data labelers in these countries are playing a key role in curating the data that powers AI systems.

A notable feature of the data labeling industry is that it does not favor locations with specific cultural contexts. The data labeling market thus is characterized by a low entry barrier for most developing countries. Whereas the outsourcing of call center jobs gravitated to countries with sizable English-speaking populations such as India and the Philippines, English skill is less of a factor in data labeling jobs. Digital literacy is sufficient to participate in most data labeling tasks such as image classification.

Among developing countries, China has emerged as a key global Al player. The country's wealthy regions and big cities lack attractiveness for the development of data-labeling services industry. Such services in the country are thus mostly performed in the poorer and backward regions, which are providing economic incentives for data labeling firms.

What is not clear is whether data labeling firms in developing countries are operating in more or less ethical ways compared to other foreign firms operating in these countries. Some critics have claimed that this industry has features that are akin to slavery. While data labeling firms claim to engage in activities that have positive social impacts, it is not easy to assess the validity of such claims. Data labeling companies have their own definitions as to what are ethical and fair practices. Moreover, the definitions vary widely across them. Thus, we may not be able to take selfreported information provided by data labeling firms as proof positive that these firms are creating more positive social impacts in developing countries compared to other foreign firms. In many cases, the problem of assessing such claims is made more complex by the fact that they do not publish any information or fail to provide relevant information on such impacts. 9

## REFERENCES

N. Kshetri, "Artificial intelligence in developing countries," *IEEE IT Pro.*, to be published, doi: 10.1109/MITP.2019.2951851.

- "Data-labelling startups want to help improve corporate AI," The Economist, Oct. 17, 2019. [Online]. Available: https://www.economist.com/business/2019/ 10/17/data-labelling-startups-want-to-help-improvecorporate-ai

- K. Kaye, "These companies claim to provide "Fair-trade" data work. Do they?" MIT Technol. Rev., Aug. 7, 2019. [Online]. Available: https://www.technologyreview.com/ s/614070/cloudfactory-ddd-samasource-imerit-impactsourcing-companies-for-data-annotation/

- C. Metz, "A.I. is learning from humans. Many humans," The New York Times, Aug. 16, 2019. [Online]. Available: https://www.nytimes.com/2019/08/16/technology/aihumans.html?auth=linked-google

- S. Dai, "Al promises jobs revolution but first it needs old-fashioned manual labour—from China," South China Morning Post, Oct. 8, 2018. [Online]. Available: https://www.scmp.com/tech/article/2166655/aipromises-jobs-revolution-first-it-needs-old-fashionedmanual-labour-china

- L. Yuan, "How cheap labor drives China's A.I. ambition," The New York Times, Nov. 25, 2018.

- H. Wu, "China Is achieving AI dominance by relying on young blue-collar workers," Vice, Dec. 21, 2018. [Online]. Available: https://www.vice.com/en\_us/article/7xyabb/ china-ai-dominance-relies-on-young-data-labelers

- C. Cadell, "Faces for cookware: Data collection industry flourishes as China pursues Al ambitions," Reuters, Jun. 28, 2019. [Online]. Available: https://www.reuters.com/ article/us-china-ai-data-insight/faces-for-cookwaredata-collection-industry-flourishes-as-china-pursues-aiambitions-idUSKCN1TS3EA

- S. Ravi and P. Nagaraj, "Harnessing the future of Al in India," *Brookings Inst.*, Oct. 18, 2018. [Online]. Available: https://www.brookings.edu/research/harnessing-thefuture-of-ai-in-india/

- K. Sheehy, "High school grads in China, India are better prepared for college," U.S. News., Aug. 27, 2012. [Online]. Available: https://www.usnews.com/education/blogs/ high-school-notes/2012/08/27/high-school-grads-inchina-india-are-better-prepared-for-college

- N. Bagri, "India is trapping its young people," Foreign Policy, May 14, 2019. [Online]. Available: https:// foreignpolicy.com/2019/05/14/india-is-trapping-itsyoung-people/

NIR KSHETRI is currently a Professor of management with the Bryan School of Business and Economics, University of North Carolina at Greensboro. Contact him at nbkshetr@uncg.edu.

# **DEPARTMENT: DATA**

# This article originally appeared in **Computer** vol. 54, no. 10, 2021

# Validating "Data Validation"

Norita Ahmad, American University of Sharjah Kevin Dias, MRM

We have more access to data than ever before, but it is difficult to make sense of it when the data is incomplete or inaccurate. As such, data validation is necessary to increase data quality for effective decision making.

ata validation is an essential part of data handling, notably in the fields of data science, artificial intelligence, and the Internet of Things. As the name suggests, it is the checking of quality and accuracy of data prior to processing it. Data validation is not a new topic; however, most data handling processes do not follow a systematized data validation approach and hence lead to smallor large-scale error-prone conclusions.<sup>1-3</sup> The use of a proper data validation process could prevent life-threatening scenarios such as incorrectly classifying a cancerous tissue as benign,1 prevent the loss of millions of dollars by ensuring the accuracy of a price prediction model,<sup>2</sup> or prevent a fatal accident of a self-driving car that failed to recognize a jaywalking pedestrian.<sup>3</sup> As such, there is an urgent need for efficient and effective data validation procedures.

Today, with the advances in big data and analytics, businesses, governments, and individuals can apply diverse data mining and machine-learning algorithms to bring new business opportunities and improve quality of life. The International Data Corporation predicted that, by 2025, data will grow to 175 trillion gigabytes worldwide, and businesses will become even more reliant on big data for decision making.<sup>4</sup> However, given the nature of big data (that is, huge volume of generated data, fast velocity of arriving data, and large variety of heterogeneous data), the quality of data can easily be compromised.<sup>5</sup> There are anecdotes where collected data was so voluminous

that people eventually discarded it since it derived no benefit.<sup>6</sup>

# WHAT IS DATA VALIDATION?

There are different definitions of data validation but, in general, data validation is a process of delivering clean and accurate data to specific programs, applications, and services.<sup>7</sup> For example, in machine learning, data validation means checking the quality and accuracy of source data before training a new model.<sup>8</sup> Different types of validation can be performed depending on the objectives and constraints of a given data set.

Data validation usually occurs during the transform stage of the extract, transform, and load (ETL) data process, where data are first extracted from a data source (Stage 1); validated, cleaned, merged, formatted, and/or appended with other data set extracts (Stage 2); and finally ready to load (Stage 3) and process as per the given use case.<sup>9</sup>

## WHY DATA VALIDATION?

Depending on a specific industry, there are numerous reasons why data validation is critical to data-driven projects. The two most important reasons that are often taken too lightly are: 1) early detection of errors and 2) the cost of time saved. <sup>5,8,10</sup> These two go hand in hand, but it is important to highlight them independently as various decision makers and data experts tend to exclude data validation due to a lack of knowledge on the many consequences from each of the two.

# Early detection of errors

Validating details of data are necessary to mitigate any project defects. Given that businesses rely on

Digital Object Identifier 10.1109/MC.2021.3099045

Date of current version: 24 September 2021

high-quality data to make critical decisions, they run the risk of basing decisions on data that are not accurately representative of the situation at hand if data validation is not properly performed. According to Gartner, on average, the financial impact of poor data quality on organizations is US\$9.7 million per year.<sup>2</sup>

## Cost of time saved

It is without question that data scientists, analysts, and engineers are in one of the highest paid lines of work. The reported median annual wage for these positions in 2020 was higher than the median annual wage for all other occupations. However, it was reported that one out of three data analysts spend over 40% of their time "vetting and validating their analytics data before it can be used for strategic decision-making. In the past, data prep tasks have occupied around 80% of a data scientist's time—challenging the wisdom of asking highly paid data scientists to spend most of their time preparing data instead of using them for the actual analysis and decision making. Imagine the value of time saved if there is a solution to this efficiency gap.

# HOW IS DATA VALIDATION PERFORMED?

The most straightforward rules used in data validation are rules that ensure data integrity, for example, the correct format to enter a phone number or the minimum password length. These basic data validation rules help to uphold standards that will effectively make working with data more efficient. During the data validation process, it is important that the standards and structure of the data model is also well understood. Structured data are data that has been formatted into a well-defined data model while unstructured data are data in a raw form. There is also semistructured data that fall in between structured and unstructured data. Understanding the difference between these types of data will help in

maintaining compatibility with applications and other data sets with which data are integrated and stored.

There are many methods available for data validation. The most common methods are using script and software programs. Writing a script may be an option for those who are fluent in coding languages such as Python and R. Script allows for a better interpretation of the data, such as comparing data values and structure against predefined rules and verifying all the necessary information within the required quality parameters. This method can however be very time consuming depending on the complexity and size of the data set. Today, there are many commercial software programs that can be used to perform data validation. For most

DIFFERENT TYPES OF VALIDATION CAN BE PERFORMED DEPENDING ON THE OBJECTIVES AND CONSTRAINTS OF A GIVEN DATA SET.

people, this is the preferred method since the program has been developed to understand the common rules and file structures used in data validation in the industry. No in-depth understanding of the underlying format is required from the user. However, this method can be a bit costly. As an alternative, a more technical user would opt for an open source software such as SourceForge and OpenRefine because they are more cost-effective.

Another important aspect of data validation is the evaluation of the validity of range measurements. The top use case is in satellites or deep-space exploration systems such as those used by NASA. Given that the system state estimates can be altered significantly by erroneous sensor data, an algorithm which decides whether to assimilate or reject data are required. Algorithms such as least squares, linear combinations, Bayesian, or Kalman filtering can be used to select

sensors that are consistent with the computed estimates and reject those that are far from the predicted values. <sup>14,15</sup>

# WHAT ARE THE CHALLENGES?

Let's face it, data validation is by far the least exciting data-related buzzword that exists. This is a fundamental failure in both industry as well as academia. The only people you see actively talking about it are veterans in the field who have firsthand experience in realizing its importance too late. Furthermore, as of the writing of this column, there is a surplus of data practitioners dominated by millennials, with a demand from employers who have a flawed view of recruiting based on quantity and not quality. It is only being part of a "trend" for 20-year-olds to hone in on their ability to build predictive models rather than

DECISION MAKERS NEED TO HAVE FUNDAMENTAL STANDARDS FOR QUALITY AND RELIABLE DATA BECAUSE THEY ARE CRITICAL FOR CORPORATE SURVIVAL.

verify the credibility of their data sources.<sup>5</sup> Additionally, the majority of data analytics teams today is so time constrained in delivering "quick insights" that data validation is unfortunately classified as a waste of time. To further stress on the broad lack of love for data validation in the industry, there are over a hundred different data science/analysis certifications available but how many data validation certifications are there?

The ETL processes are inherently so focused on "getting the job done" with speed and efficiency, with accuracy being a low priority. In the top-down team structures where there is a cascading effect of pressure, the data analyst doing the heavy lifting is left with a difficult choice between spending time sense checking their data or keeping their job. Data governance and data ethics—related roles such as the chief data officer are only recently being birthed into the industry and will hopefully bring more emphasis on the importance of allocating engineering hours specifically to data validation.

Additionally, the management teams often fail to make a clear distinction between a data science data validation and a human-oriented data validation. There is an industry-coined phrase called "human-in-the-loop" validation that is used for situations when it isn't enough to run if/else error tests but also necessary for a person to sense-check the data themselves. Examples of this are phone numbers (that require an actual phone call), email addresses (email bounce-back test), and websites (that need a Google search). When a human successfully makes these validation tests, machine learning can be applied to both learn from the validations and also to assess newly recruited "human data validators."

It is, however, important to note that personally identifiable information (PII) is sensitive, personal data that is protected by data regulatory laws such as the General Data Protection Regulation<sup>16</sup> and can make data validation tedious. This is particularly a challenge with the types of data mentioned earlier (that is, email address and phone number) that can be tied back to a person. Since these regulations make attaining, storing, and using PII data a costly liability for a company, it can be risky when PII data are used as part of the data validation approach or as the data being validated itself.

Perhaps the most challenging of all is scalability. Scalability of data validation is how decision makers find the easiest excuse to turn a blind eye on. It is a costly aspect of the data pipeline that needs more research and attention. To go from 95% accuracy to 99% accuracy, in confidence intervals, can cost a company an exponential amount more versus their standard resourcing cost in data validation due to the human aspect of it. When a business decision maker is more comfortable to go with 95% over 99% accuracy, it is often too late to realize that it could cost thousands of dollars to a startup or billions of dollars to a Fortune 500 company in a worst-case scenario. This needs to change. Decision makers need to have fundamental standards for quality and reliable data because they are critical for corporate survival.<sup>2</sup>

# DATA VALIDATION DASHBOARD

We have discussed some of the essential key concepts and challenges regarding data validation. It is evident that when it comes to data validation, human oversight cannot be completely removed from the practice.

Data validation is a part of a project that exists to help a human with a data-driven decision. For example, before digital marketing existed, traditional marketers with little to no data, would make decisions based on gut instinct and "intuition" from their experiences—invaluable human traits that cannot be learned. Even today, no matter how advanced data validation software is, or automated methodologies are, humans are unlikely to proceed with decisions that are not vetted by another human. The final decision would probably be made by someone at a senior level, with experience and contextual knowledge, who can tell whether the data validation process was successful.

A data validation dashboard might serve as a means for an experienced data practitioner to monitor data analysis processes from start to finish. The dashboard could also be used as a tool that, over time, improves recommendations for handling data validation by suggesting the appropriate time to be spent at each step, the number and types of people involved, the format of the data validation technique, and the expected results.

Two of the core functions of such a dashboard would be

- a. a checklist to help decide and sequence the most appropriate tasks to apply for a given problem

- b. a reference list of learned data quality issues filtered specific to the data set/problem at hand.

The dashboard could enable teams or project managers to allocate resources, tasks, and also more effectively supervise the status and the best outcome possible for projects.

Since many people are comfortable with knowing that they understand data validation at the fundamental level, it is most important for you to take away the more subtle nuances about it that this column article highlights. Data validation generally occurs but isn't exclusively at the data source level. Data sources or data sets should be acknowledged as being comparatively "more" or "less" accurate, as perfect accuracy is impossible to conclude. Records and data points, although confirmed accurate, can run the risk of inaccuracy over time if not routinely verified.

As marketing automation and data-driven retargeting becomes more widespread, there will be an increasing need to guarantee the accuracy of data pertaining to real people and business entities. A data analytics operation can produce ground-breaking data-driven solutions or recommendations, but when presented to an already risk-averse business decision maker, the last thing you want is to allow the risk of having employed inaccurate data from the very beginning.

RECORDS AND DATA POINTS,

ALTHOUGH CONFIRMED ACCURATE,

CAN RUN THE RISK OF INACCURACY

OVER TIME IF NOT ROUTINELY

VERIFIED.

## REFERENCES

- C. Farr, "This patient's medical record said she'd given birth twice-In fact, she'd never been pregnant," CNBC, Dec. 9, 2018. https://www.cnbc.com/2018/12/09 /medical-record-errors-common-hard-to-fix.html (accessed June 21, 2021).

- "Poor Quality data imposes costs and risks on business, says new Forbes insights report," Forbes, May 31, 2017. https://www.forbes.com/sites/forbespr/2017/05/31/poor-quality-data-imposes-costs-and-risks-on-businesses-says-new-forbes-insights-report/?sh=4eb96655452b (accessed June 21, 2021).

- A. Marshall and A. Davies, "Uber's self-driving car saw the woman it killed, report says," WIRED, May 24, 2018. https://www.wired.com/story/uber-self-driving-crash -arizona-ntsb-report/ (accessed June 21, 2021).

- 4. D. Reinsel, J. Gantz, and J. Rydning, "The digitization of the world from edge to core," International Data Corporation, Needham, MA, White Paper, 2018. Accessed: June 19, 2021. [Online]. Available: https://resources.moredirect.com/white-papers/idc-report-the-digitization-of-the-world-from-edge-to-core

- J. Gao, C. Xie, and C. Tao, "Big data validation and quality assurance - Issues, challenges, and needs," in Proc. IEEE Symp. Service-Oriented Syst. Eng. (SOSE), Mar. 2016, pp. 433–441. doi: 10.1109/SOSE.2016.63.

- J. Anderson and L. Rainie, "The future of big data Main findings: Influence of big data in 2020," Pew Research Center, 2012. https://www.pewresearch.org/internet

- /2012/07/20/main-findings-influence-of-big-data-in -2020/ (accessed July 8, 2021).

- 7. "Techopedia explains data validation," Techopedia, 2017. https://www.techopedia.com/definition/10283 /data-validation (accessed June 15, 2021).

- 8. N. Polyzotis, M. Zinkevich, S. Roy, E. Breck, and S. Whang, "Data validation for machine learning," in *Proc. Mach. Learn. Syst.*, 2019, vol. 1, pp. 334–347.

- T. Jun, C. Kai, F. Yu, and T. Gang, "The research & application of ETL tool in business intelligence project," in Proc. Int. Forum Inf. Technol. Appl., May 2009, vol. 2, pp. 620–623. doi: 10.1109/IFITA.2009.48.

- N. Polyzotis, S. Roy, S. E. Whang, and M. Zinkevich, "Data lifecycle challenges in production machine learning: A survey," ACM SIGMOD Rec., vol. 47, no. 2, pp. 17–28, June 2018. doi: 10.1145/3299887.3299891.

- "Salary guide 2020," Robert Half Technology, Menlo Park, CA, 2020. [Online]. Available: https://www.roberthalf.com/sites/default/files/documents\_not\_indexed/2020\_Salary\_Guide\_Technology\_NA.pdf (accessed June 20, 2021).

- C. Taylor, "Structured vs. unstructured data," Datamation, May 21, 2021. https://www.datamation.com/big-data/structured-vs-unstructured-data/ (accessed July 8, 2021).

- 13. M. Goetz, G. Leganza, E. Miller, and J. Vale, "Data

- performance management is essential to prove data's ROI," FORRESTER, 2018. https://www.forrester.com/report/Build±Trusted±Data±With±Data±Quality/-/E-RES83344 (accessed June 20, 2021).

- M. Fernandez and H. F. Durrant-Whyte, "An information-theoretic approach to data-validation," in Proc. IEEE Amer. Contr. Conf., June 1993, pp. 2351–2355. doi: 10.23919/ACC.1993.4793308.

- A. El-Mowafy, "Diagnostic tools using a multi-constellation single-receiver single-satellite data validation method," J. Navig., vol. 68, no. 1, pp. 196–214, 2015. doi: 10.1017/S0373463314000526.

- C. Bernstein, "Personally identifiable information (PII)," TechTarget, Feb. 2020. https://searchsecurity .techtarget.com/definition/personally-identifiable -information-PII (accessed June 27, 2021).

**NORITA AHMAD** is an associate professor of management information systems at American University of Sharjah, Sharjah, United Arab Emirates. Contact her at nahmad@aus.edu.

**KEVIN DIAS** is a performance and analytics manager at MRM, Toronto, M5V 0N6, Canada. Contact him at kevinrosedias @gmail.com.

**PURPOSE:** The IEEE Computer Society is the world's largest association of computing professionals and is the leading provider of technical information in the field.

**MEMBERSHIP:** Members receive the monthly magazine *Computer*, discounts, and opportunities to serve (all activities are led by volunteer members). Membership is open to all IEEE members, affiliate society members, and others interested in the computer field.

**COMPUTER SOCIETY WEBSITE: www.computer.org**

**OMBUDSMAN:** Direct unresolved complaints to ombudsman@computer.org.

**CHAPTERS:** Regular and student chapters worldwide provide the opportunity to interact with colleagues, hear technical experts, and serve the local professional community.

**AVAILABLE INFORMATION:** To check membership status, report an address change, or obtain more information on any of the following, email Customer Service at help@computer.org or call

- +1 714 821 8380 (international) or our toll-free number,

- +1 800 272 6657 (US):

- · Membership applications

- · Publications catalog

- · Draft standards and order forms

- · Technical committee list

- · Technical committee application

- · Chapter start-up procedures

- · Student scholarship information

- · Volunteer leaders/staff directory

- IEEE senior member grade application (requires 10 years practice and significant performance in five of those 10)

## **PUBLICATIONS AND ACTIVITIES**

**Computer.** The flagship publication of the IEEE Computer Society, Computer publishes peer-reviewed technical content that covers all aspects of computer science, computer engineering, technology, and applications.

**Periodicals:** The society publishes 12 magazines and 17 journals. Refer to membership application or request information as noted above.

**Conference Proceedings & Books:** Conference Publishing Services publishes more than 275 titles every year.

**Standards Working Groups:** More than 150 groups produce IEEE standards used throughout the world.

**Technical Committees:** TCs provide professional interaction in more than 30 technical areas and directly influence computer engineering conferences and publications.

**Conferences/Education:** The society holds about 200 conferences each year and sponsors many educational activities, including computing science accreditation.

**Certifications:** The society offers three software developer credentials. For more information, visit www.computer.org/certification.

### **BOARD OF GOVERNORS MEETING**

TBD

## **EXECUTIVE COMMITTEE**

President: William D. Gropp President-Elect: Nita Patel Past President: Forrest Shull

First VP: Riccardo Mariani; Second VP: David S. Ebert Secretary: Jyotika Athavale; Treasurer: Michela Taufer VP, Membership & Geographic Activities: Andre Oboler VP, Professional & Educational Activities: Hironori Washizaki

VP, Publications: David S. Ebert VP. Standards Activities: Annette Reilly

VP, Technical & Conference Activities: Grace Lewis

2021–2022 IEEE Division VIII Director: Christina M. Schober

2022-2023 IEEE Division V Director: Cecilia Metra 2022IEEE Division VIII Director-Elect: Leila De Floriani

### **BOARD OF GOVERNORS**

**Term Expiring 2022:** Nils Aschenbruck, Ernesto Cuadros-Vargas, David S. Ebert, Grace Lewis, Hironori Washizaki, Stefano Zanero

**Term Expiring 2023:** Jyotika Athavale, Terry Benzel, Takako Hashimoto, Irene Pazos Viana, Annette Reilly, Deborah Silver

**Term Expiring 2024:** Saurabh Bagchi, Charles (Chuck) Hansen, Carlos E. Jimenez-Gomez, Daniel S. Katz, Shixia Liu, Cyril Onwubiko

### **EXECUTIVE STAFF**

Executive Director: Melissa A. Russell

**Director, Governance & Associate Executive Director:** Anne Marie Kelly

**Director, Conference Operations:** Silvia Ceballos

Director, Information Technology & Services: Sumit Kacker

**Director, Marketing & Sales:** Michelle Tubb **Director, Membership & Education:** Eric Berkowitz **Director, Periodicals & Special Projects:** Robin Baldwin

# **COMPUTER SOCIETY OFFICES**

**Washington, D.C.:** 2001 L St., Ste. 700, Washington, D.C. 20036-4928; **Phone:** +1 202 371 0101; **Fax:** +1 202 728 9614; **Email:** help@computer.org

Los Alamitos: 10662 Los Vaqueros Cir., Los Alamitos, CA 90720; Phone: +1 714 821 8380; Email: help@computer.org

### **MEMBERSHIP & PUBLICATION ORDERS**

Phone: +1 800 678 4333; Fax: +1 714 821 4641; Email: help@computer.org

# **IEEE BOARD OF DIRECTORS**

K. J. Ray Liu, President & CEO Saifur Rahman, President-Elect John W. Walz, Director & Secretary Mary Ellen Randall, Director & Treasurer Susan "Kathy" Land, Past President

Stephen M. Phillips, Director & Vice President, Educational

Lawrence O. Hall, Director & Vice President, Publication Services and Products

David A. Koehler, *Director & Vice President, Member and Geographic Activities*

James E. Matthews, *Director & President, Standards Association*Bruno Meyer, *Director & Vice President, Technical Activities*Deborah M. Cooper, *Director & President, IEEE-US*

# **DEPARTMENT: PREDICTIONS**

# This article originally appeared in **Computer** vol. 54, no. 10, 2021

# The Next Wave in Cloud Systems Architecture

Amin Vahdat, Google

Dejan Milojicic, Hewlett Packard Labs

Twenty-five years ago, no one expected services to be seamlessly and consistently delivered across campuses and edge. It is now possible to envision machine learning-powered services capable of scaling to the reliability, performance, and security requirements of billions of users worldwide.

ecause of their visionary nature but also their highly volatile success-failure ratio, predictions have always been popular among a wide spectrum of audiences. The COVID-19 pandemic has turned this popularity into a necessity. Time constraints and a lack of thorough experimentation necessitated a dependence on predictions: which vaccines to use, when to close or open countries, when and how to reopen offices, and so on. Suddenly, predictions became a way of life.

After 10 years of making technology predictions for the IEEE Computer Society (see the press releases at https://www.computer.org/press-room), two successful special issues on technology predictions in *Computer* (December 2020 and July 2021), and panels at numerous events (SWITCH 2020; the IEEE Computer Society Computers, Software, and Applications Conference 2020; and so forth), we have decided to initiate the column "Predictions."

We decided to invite a reputable guest for each "Predictions" column. A guest should have a demonstrated vision for the future of computing and a track record of delivering on that vision. Our ideal guest should have a combination of academic rigor, deep technology knowledge, and an understanding of business implications.

Amin Vahdat, an engineering fellow and vice president at Google, is a perfect match for the inaugural

"Predictions" column. He leads systems infrastructure at Google, and prior to that, he was a professor of computer science at the University of California San Diego and Duke University. Vahdat brings a wealth of experience in compute, operating systems, accelerators, storage, and networking. In his professional role, it is essential to predict the workload evolutions, customer demands, and trends in technology.

In this article, Vahdat takes us on a prediction tour of the future of systems infrastructure, addressing topics such as the emergence of new accelerators, impact of the growth of data, disaggregated data center designs, the evolving roles of operating systems and programming languages, application delivery models, the roles of networking, and much more. I hope that you enjoy reading this column as much as I enjoyed working with him to deliver it.

**Dejan Milojicic:** Interesting technology and business implications are driven by the imminent end of Moore's law, such as a plethora of innovative accelerators, the rise of photonics, and the introduction of new memory technologies. Which one of these is a fundamental disruptor and which is a temporary transition?

Amin Vahdat: The computing industry has delivered incredible new business and societal capabilities through sustained, exponential improvements in the scale and performance efficiency of the underlying hardware and software. However, the underlying hardware trends that have powered this march over the past few decades are slowing or stopping with each

Digital Object Identifier 10.1109/MC.2021.3099955 Date of current version: 24 September 2021

generation of hardware, including general-purpose CPUs, dynamic RAM (DRAM), storage devices, and network elements, delivering incrementally less benefit relative to the previous generation, alarmingly with lower levels of reliability in many cases. This will mean that software optimizations, including novel algorithms, protocols, and replication strategies, will play an important role in maintaining the cadence of regular system-efficiency improvements.

I believe that all the technologies you point to, and more that are yet to come, are fundamental disruptors we will need to accommodate. For the first time in decades, a range of new technologies is actually a must have—rather than a nice to have—to sustain exponential growth in compute capability. Current capabilities, like real-time language recognition and translation, would simply not have been possible from either a cost or power standpoint without hardware acceleration through accelerators like tensor processing units and GPUs. Similarly, exploding demand for video consumption on a range of devices and networks could not be effectively supported without hardware-supported video coding. These examples are just the beginning of an increasing array of segment-specific hardware architectures that can deliver step-function improvements to domains such as analytics, high-performance computing, and real-time serving.

On the memory and storage front, we are hitting a wall in available improvements in cost per gigabyte, especially as we try to simultaneously meet the needs of different applications that are individually latency, bandwidth-, and capacity-bound on the same hardware. We now have underlying hardware technologies that can strike tradeoffs between cost, latency, bandwidth, and capacity somewhat independently, meaning that we will deploy servers with a range of memory and storage configurations, enabling higher-level scheduling infrastructure to map applications to available hardware configurations in the most cost- and performance-effective manner.

Photonics have always played a critical role in the scale of available computation in the data center. Today, silicon photonics, or integration of photonics onto integrated circuits, is emerging as a requirement for continued expansion of power-efficient data rates. We are already seeing this play out in traditional transceiver design, with the next question being the role silicon photonics will play in mainboard and ASIC design, with reliability for hundreds of optical engines integrated on a single board or ASIC being one of the most pressing challenges.

**Milojicic:** Data center design has been motivated by cost and performance for quite some time. Given the rate of evolution of individual technologies, is there an opportunity for rethinking interfaces to optimize performance? For example, accelerating access to data and/or interconnections by deploying computations closer to it. The so-called in- or near-memory computations and similar for interconnects with smart network interface controllers (NICs), data processing units, and so on?

Vahdat: Yes, absolutely. The rate of growth of data and the increasing computation required to summarize and transform data into suitable formats is growing well beyond what our CPU budgets will allow for power- and cost-efficient processing. Today, we strive to treat data as a large, location-independent "blob" with intermediate processing steps composed together in a manner not far from classic UNIX-pipe composition. While convenient, this means that data must often move back and forth across kilometers of compute within a large campus, compressed, encrypted, decompressed, decrypted, transformed, processed, and replicated dozens of times. Processor architects optimize pJ/ bit, and it is likely that we will need similar measures in considering the cost of end-to-end processing of every ingested byte of data.

The resulting metrics will lead to a number of necessary innovations in system design. First, some amount of computation power will be needed closer to data stores with closely coupled data ideally placed closer to one another in a logical topology. In the extreme, new hardware will colocate server-class processing power or even hardware accelerators in the same server or rack enclosure as the data. However, more generally, such sophisticated processing will require deep understanding of the logical data processing pipeline and an orchestration and runtime layer able to place and migrate data computation according to overall data lifetimes. Understanding the provenance of derived data will open opportunities to create efficient, intermediate formats, perhaps allowing different processing elements to handle a range of native formats and summaries, ideally with a "data compiler" capable of placing the right preprocessing at the right point for a specified data flow. Smart NICs and their generalization will form the nervous system in the above runtime, likely managing both the movement of the data from location to location but also its intermediate processing.

While there is substantial complexity required to realize this, the next wave of efficiency improvements will come from end-to-end performance considerations rather than lower-level measures such as million instructions per second and storage capacity/input-output per second. How much processing, energy, and storage is required to deliver an insight or result in the end-to-end composition? There are integer factors of performance, cost, and energy efficiency available in our infrastructure when viewed through this lens.

**Milojicic:** Do we need new operating systems, programming languages, programming environments, and middleware to make all this seamlessly work, or would those from the previous era suffice?

**Vahdat:** Software will drive the success of this next wave in infrastructure evolution. What we will see is that the shape of compute containers can change dynamically at runtime, perhaps adding and removing memory, storage, or accelerators based on the needs of the services currently scheduled on the server.

Real-time performance monitoring will support isolation among tenants while accounting for antagonists at multiple levels of the system hierarchy; for example, L3 or DRAM capacity versus bandwidth requirements, and behaviors of individual applications. The level of malleability in the composition of servers will need to fundamentally change from the operating systems' current view of a fixed "hardware" environment from boot to shutdown.

At the distributed systems level, services will require much more predictability and determinism in accessing remote storage and compute resources. This will, in turn, require a runtime capable of delivering isolation among millions of concurrent communication channels, all while ensuring efficiency and the mapping of requests to the underlying replica or resource best capable of fulfilling them.

**Milojicic**: How can we most effectively accomplish hardware–software co-design to account for optimizations adequately at different levels of the stack?

Vahdat: The level of visibility we have into the dynamic nature of real data center computation is incredibly limited. We understand what industry benchmarks like SPEC and TPC-H look like in isolation and know how to optimize them for hardware. However, actual data center workloads are increasingly heterogeneous, multitenant, and distributed, substantially reducing the predictive power of existing benchmarks.

Moving forward, we will need to start with much deeper hardware measurement infrastructure to characterize workloads in the wild. This can, in turn, support new benchmarks that account for wider variability in computational structure, potential hardware offload capability, and the fundamental distributed and multitenant nature of modern computation. Single-server, single-tenant benchmarks cannot be the basis for projecting the value of future infrastructure. An open question is the required scale, heterogeneity, and variability for sufficient predictive power.

**Milojicic:** To optimize the data center cost, disaggregated design has been taking off, with accelerators being separated from compute—deployed in racks-size units—disaggregated memory is emerging and storage has been deployed (for example,

storage area network and network attached storage) for quite some time. Is this trend going to continue in the future?

Vahdat: The interesting thing about disaggregation is that, while it holds fundamental technical appeal, including for me personally, its progression has been rather limited since we deployed the first disaggregated storage solutions. Systems like GFS (the Google File System) showed how to treat thousands of hard drives spread across the data center as the underlying storage for a distributed and disaggregated storage system. However, the bandwidth and latency of hard drives are modest compared to the speeds of data center networks and, as importantly, the software layers responsible for managing I/O requests.

True disaggregation of SSDs has been slower to progress in part because local, dedicated devices have high bandwidth and low latency relative to data center network speeds but also because there can be little software on the path between a client request and device access while maintaining the illusion of "local" access to a disaggregated device.

While accelerators are deployed in rack-scale units, they are also typically deployed with dedicated servers and often dedicated secondary networks. There is very little virtualization support for accelerators today.

I do believe that the next level of end-to-end system efficiency and flexibility will require support for disaggregation. However, it will also require some breakthroughs in hardware/software organization because the assumptions built up over decades about local device access over a dedicated PCIe link will be hard to break.

**Milojicic:** Can you tell us how networking is evolving in the data center and how it is affected by the trends and needs of data and compute?

Vahdat: The network today constitutes the smallest portion of our data center spend, but it offers some of the biggest challenges and opportunities. For example, the network is often the largest source of large-scale failures and extended downtime. Because it fundamentally connects computation and storage together at scale, a failure in the network most easily

cascades resulting in large-scale outages. Similarly, managing the lifecycle of the network from turnup to upgrades to turndown is often the most complex and toilsome for the operations team. Tying the two together, many network outages are correlated with network operations.

Given the increasing societal reliance on compute infrastructure, and the thousands of seemingly independent cloud services, we multiplex onto shared underlying network infrastructure, the reliability of the network must fundamentally improve. Since, in the end, individual network components and systems are unavoidable at cloud's scale of deployment and its rapid rate of evolution, solutions likely lie in designs that ensure hard levels of network isolation and multiplexing of services onto multiple independently operated network infrastructure.

Network performance and performance predictability will also be critical, as we discussed earlier. The disaggregated and data-centric data center will require not just higher performance and lower latency but predictability and isolation under a range of highly variable and bursty communication patterns. This will require us to continue the evolution of software-defined networking to enable visibility all the way to the end applications and their composite, multinode communication patterns, with microsecond-granularity actuation loops allocating bandwidth and rate limits to meet the real-time application SLOs, focusing on remote procedure calls and coflows rather than lower-level metrics focused on packets.

**Milojicic:** Data and compute delivery models have evolved from on premise to public cloud, to hybrid cloud to edge. What is the next step in delivery models?

Vahdat: One important note is that, while there is a lot of enthusiasm around emerging compute delivery models from public to hybrid to edge cloud, we are still in the very early stages of the migration to these emerging hosting approaches. The vast majority of computing and storage still runs in enterprise data centers with many challenges that must be overcome before we can get to baseline modernization of digital infrastructure.