# Christian-Albrechts-University of Kiel Faculty of Engineering

# Superposition Mapping & Related Coding Techniques

# Tianbin Wo

Kiel 2011

# Superposition Mapping & Related Coding Techniques

# Dissertation

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

der Technischen Fakultät

der Christian-Albrechts-Universität zu Kiel

vorgelegt von

Tianbin Wo

Kiel 2011

Tag der Einreichung: 21.01.2011 Tag der Disputation: 20.05.2011

Berichterstatter: Prof. Dr.-Ing. Peter Adam Höher

Prof. Dr.-Ing. Martin Bossert

Prof. Li Ping

# **Preface**

This thesis was developed during my time as a research and teaching assistant at the Information and Coding Theory Lab (ICT), Faculty of Engineering, University of Kiel, Germany.

At the time of publishing this thesis, I would first like to thank my advisor Prof. Dr.-Ing. Peter Adam Höher for his inspiring guidance throughout my work in Kiel. The research environment at the ICT is enjoyable and the research team of the ICT is excellent. Additionally, I would like to thank Prof. Höher for enabling me to frequently visit international conferences, which was surely a great help for enriching my academic experience.

I would like to thank Prof. Dr.-Ing. Martin Bossert from Ulm University and Prof. Li Ping from City University of Hong Kong for evaluating this work. Their pertinent suggestions are more than helpful for improving the quality of the thesis and their in-time review is important for setting up a prompt date for the thesis defense.

I would also like to thank my former colleagues of the ICT and the Institute for Circuit and System Theory for many interesting discussions and pleasant activities. I am pretty sure that I will continuously miss my time in Kiel.

Last but not least, I would like to thank my wife Lin Lin, who has accompanied and encouraged me throughout my study in Kiel, and my parents for their enduring support. Without their encouragement and support, this thesis would have been impossible.

gint of

# Abstract

Since Shannon's landmark paper in 1948, it has been known that the capacity of a Gaussian channel can be achieved if and only if the channel outputs are Gaussian. In the low signal-to-noise ratio (SNR) regime, conventional mapping schemes suffice for approaching the Shannon limit, while in the high SNR regime, these mapping schemes, which produce uniformly distributed symbols, are insufficient to achieve the capacity. To solve this problem, researchers commonly resort to the technique of signal shaping that mends the symbol distribution, which is originally uniform, into a Gaussian-like one.

Superposition mapping (SM) refers to a class of mapping techniques which use linear superposition to load binary digits onto finite-alphabet symbols that are suitable for waveform transmission. Different from conventional mapping schemes, the output symbols of a superposition mapper can easily be made Gaussian-like, which effectively eliminates the necessity of active signal shaping. For this reason, superposition mapping is of great interest for theoretical research as well as for practical implementations. It is an attractive alternative to signal shaping for approaching the channel capacity in the high SNR regime.

This thesis aims to provide a deep insight into the principles of superposition mapping and to derive guidelines for systems adopting it. Particularly, the influence of power allocation to the system performance, both w.r.t. the achievable power efficiency and supportable bandwidth efficiency, is made clear. Considerable effort is spent on finding code structures that are matched to SM. It is shown that currently prevalent code design concepts, which are mostly derived for coded transmission with bijective uniform mapping, do not really fit with superposition mapping, which is often non-bijective and nonuniform. As the main contribution, a novel coding strategy called low-density hybrid-check (LDHC) coding is proposed. LDHC codes are optimal and universally applicable for SM with arbitrary type of power allocation.

**Keywords:** Digital modulation, signal shaping, Gaussian channel, bit-interleaved coded modulation (BICM), soft-input soft-output (SISO) demapping, channel coding, low-density parity-check (LDPC) code, low-density summation-check (LDSC) code, low-density hybrid-check (LDHC) code, sparse matrix, iterative message passing, belief propagation.

# Contents

| 1        | Intr | roduction                             | 1  |

|----------|------|---------------------------------------|----|

|          | 1.1  | Background                            | 1  |

|          | 1.2  | Motivation                            | 3  |

|          | 1.3  | Scope and Aim                         | 5  |

|          | 1.4  | Thesis Outline                        | 6  |

| <b>2</b> | Gau  | ussian Channel                        | 7  |

|          | 2.1  | Channel Model                         | 7  |

|          | 2.2  | Mutual Information                    | 8  |

|          | 2.3  | Capacity for Zero Error Probability   | 9  |

|          | 2.4  | Capacity for Finite Error Probability | 11 |

| 3        | Sup  | perposition Mapping (SM)              | 13 |

|          | 3.1  | General Description                   | 14 |

|          | 3.2  | An Information Theoretical View       | 16 |

|          | 3.3  | Equal Power Allocation (EPA)          | 17 |

|          |      | 3.3.1 Overview                        | 17 |

|          |      | 3.3.2 Symbol Distribution             | 19 |

|          |      | 3.3.3 Symbol Entropy                  | 22 |

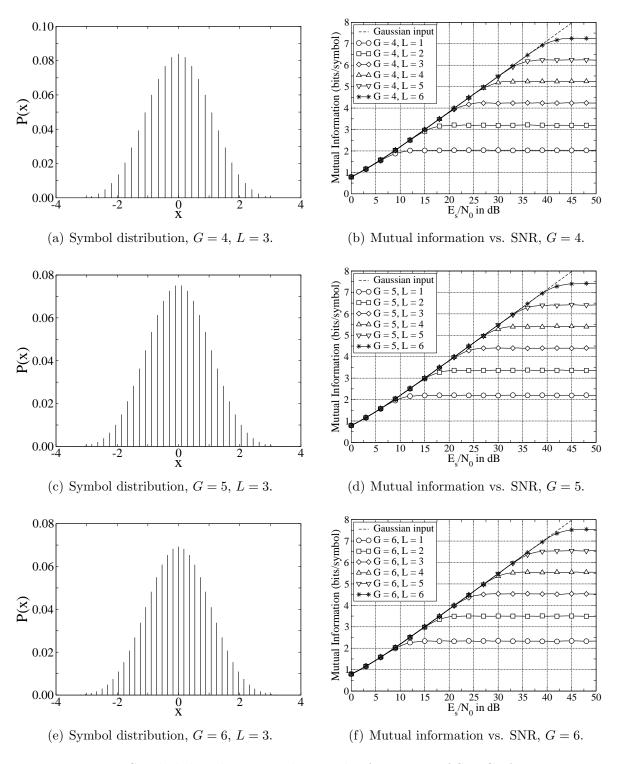

|          |      | 3.3.4 Mutual Information              | 24 |

|   | 3.4 | Unequ   | al Power Allocation (UPA)                | 26 |

|---|-----|---------|------------------------------------------|----|

|   |     | 3.4.1   | The Exponential Law                      | 26 |

|   |     | 3.4.2   | Mapping and Labeling                     | 28 |

|   | 3.5 | Group   | ed Power Allocation (GPA)                | 30 |

|   |     | 3.5.1   | Basic Idea                               | 30 |

|   |     | 3.5.2   | Symbol Distribution & Mutual Information | 31 |

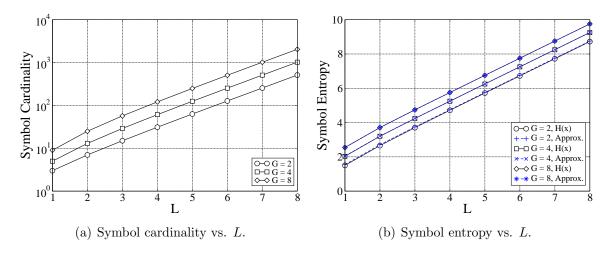

|   |     | 3.5.3   | Symbol Cardinality & Symbol Entropy      | 34 |

|   |     | 3.5.4   | Mapping & Labeling                       | 36 |

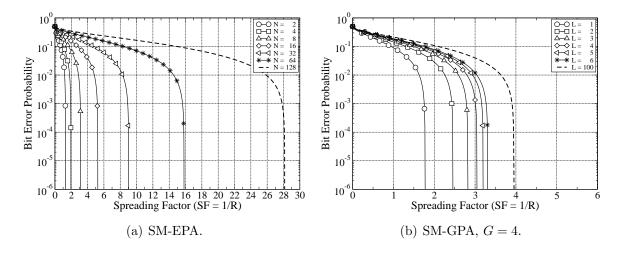

| 4 | Unc | coded S | SM Transmission                          | 37 |

|   | 4.1 | Maxim   | num-A-Posteriori Demapping               | 37 |

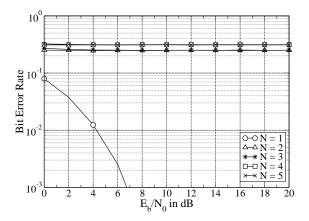

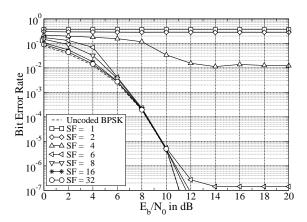

|   | 4.2 | Bit Er  | ror Probability of SM-EPA                | 38 |

|   | 4.3 | Bit Er  | ror Probability of SM-UPA                | 42 |

|   | 4.4 | Bit Er  | ror Probability of SM-GPA                | 43 |

| 5 | Cod | led SM  | I Transmission                           | 45 |

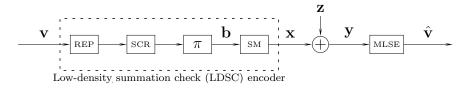

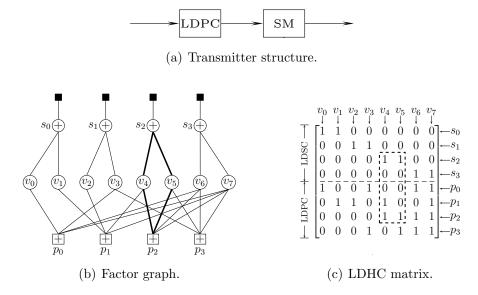

|   | 5.1 | System  | a Structure                              | 46 |

|   | 5.2 | Soft-In | nput Soft-Output Demapping               | 47 |

|   |     | 5.2.1   | Standard APP Approach                    | 47 |

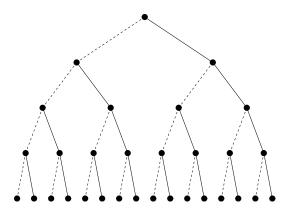

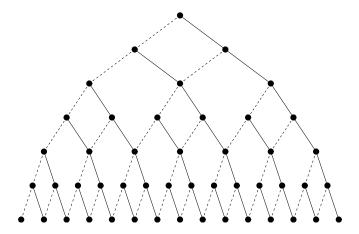

|   |     | 5.2.2   | Tree-Based APP Approach                  | 50 |

|   |     | 5.2.3   | Gaussian-Approximation Approach          | 56 |

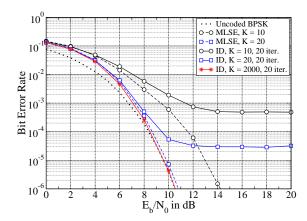

|   | 5.3 | Repeti  | tion-Coded SM                            | 58 |

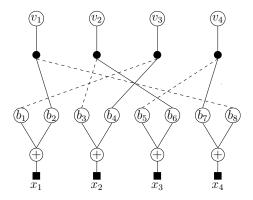

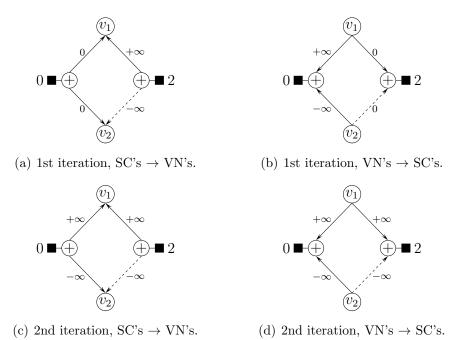

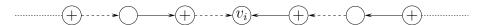

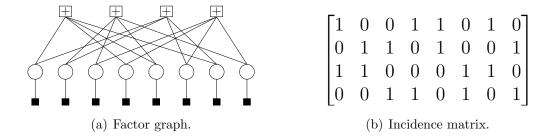

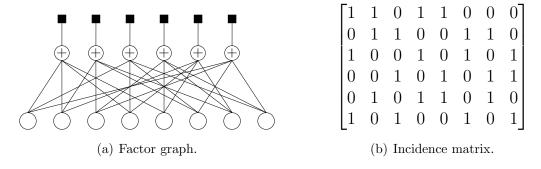

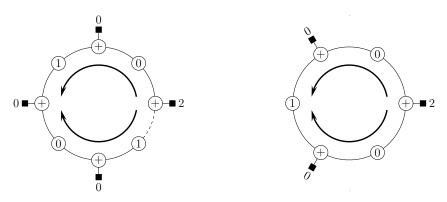

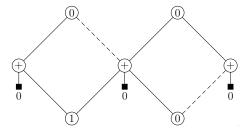

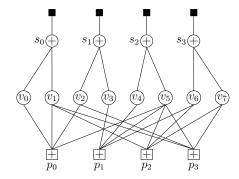

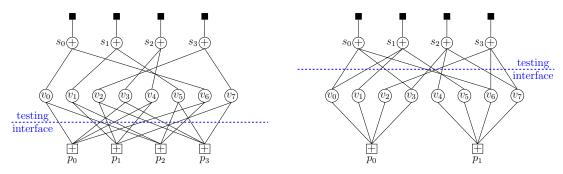

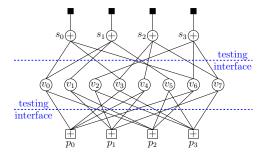

|   |     | 5.3.1   | Factor Graph Representation              | 59 |

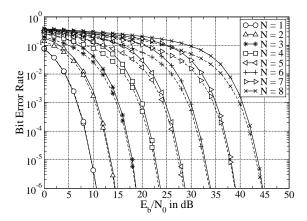

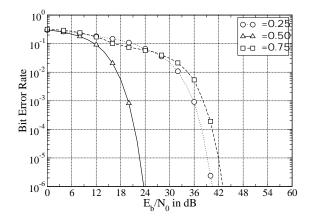

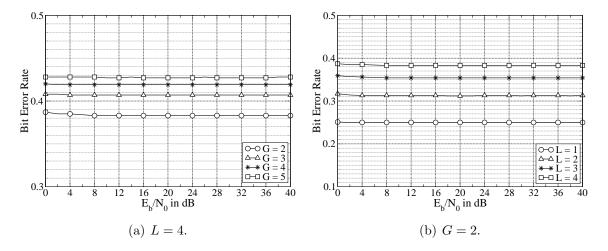

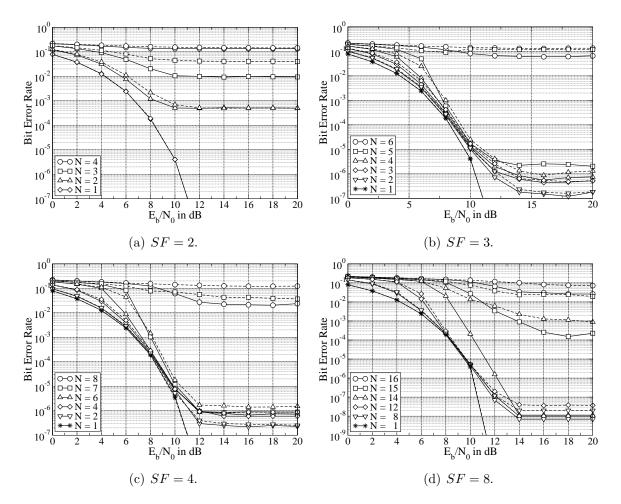

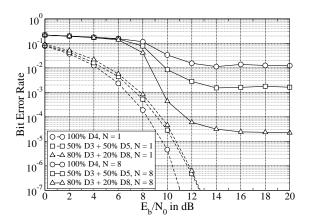

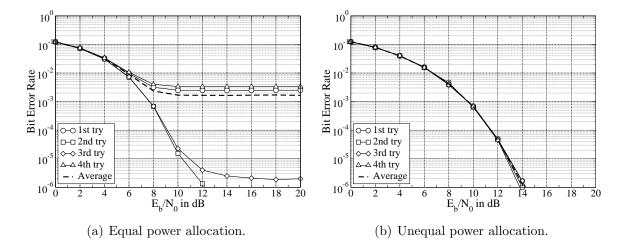

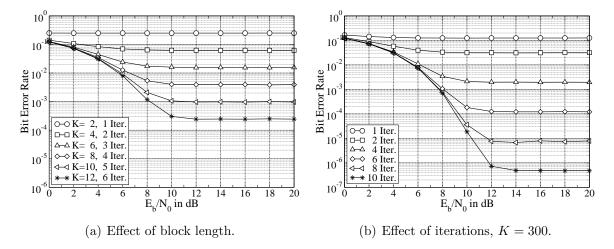

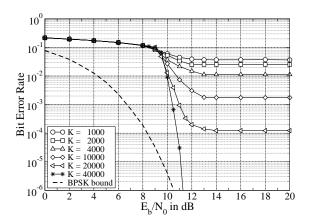

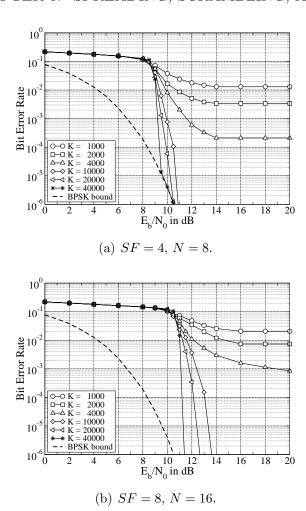

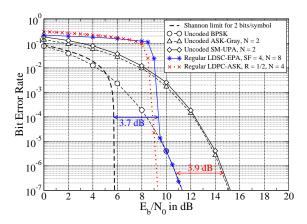

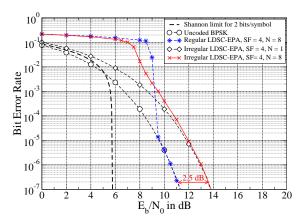

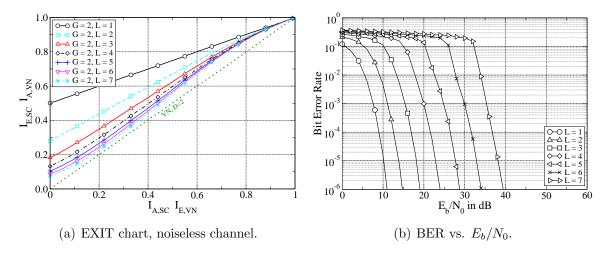

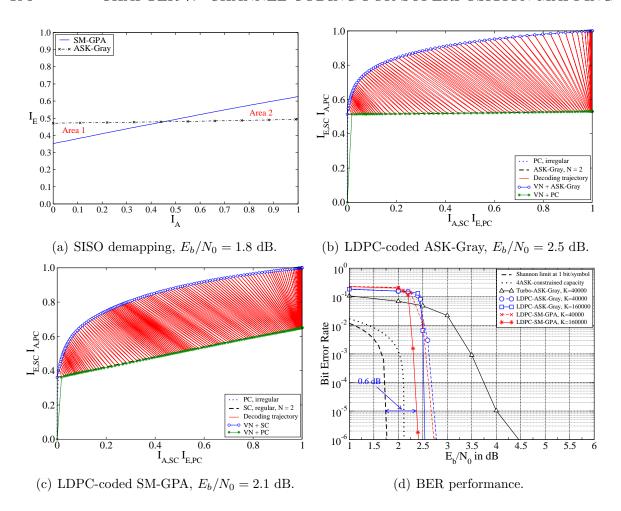

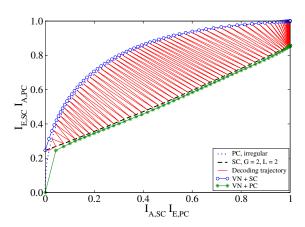

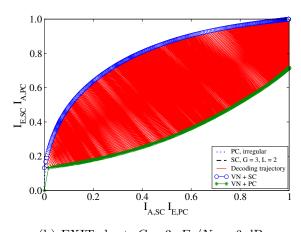

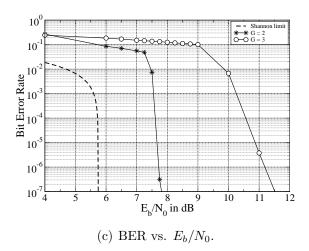

|   |     | 5.3.2   | Performance Overview                     | 60 |

|   | 5.4 | Parity- | -Check-Coded SM                          | 65 |

|   |     | 5.4.1   | Factor Graph Representation              | 65 |

|   |     | 5.4.2   | Performance Overview                     | 66 |

| 6 | Spr | eading  | , Scrambling, and Interleaving                         | <b>6</b> 9 |

|---|-----|---------|--------------------------------------------------------|------------|

|   | 6.1 | Effects | s of Spreading                                         | 70         |

|   |     | 6.1.1   | Regular Repetition                                     | 70         |

|   |     | 6.1.2   | Irregular Repetition                                   | 71         |

|   |     | 6.1.3   | Information Aggregation and Information Distribution   | 72         |

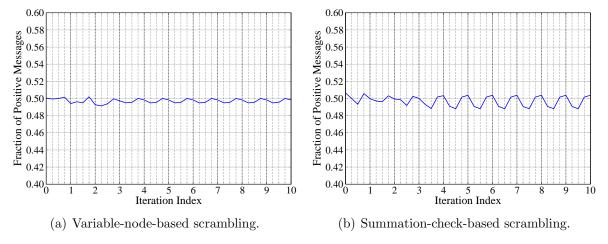

|   | 6.2 | Effects | s of Scrambling                                        | 76         |

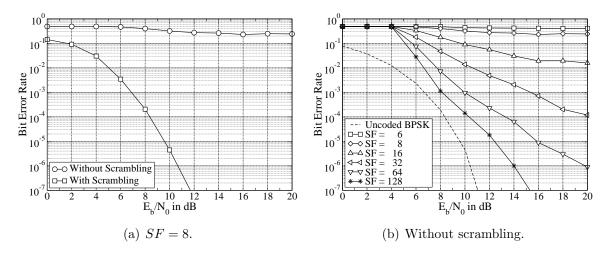

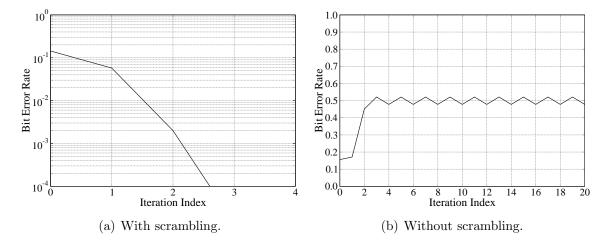

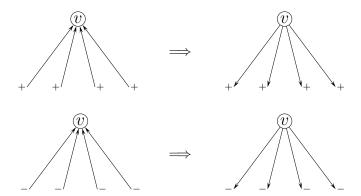

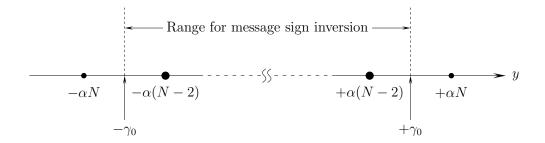

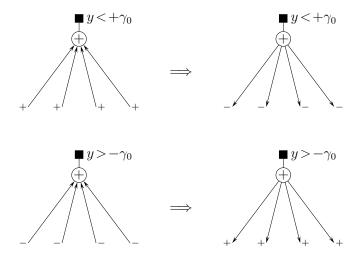

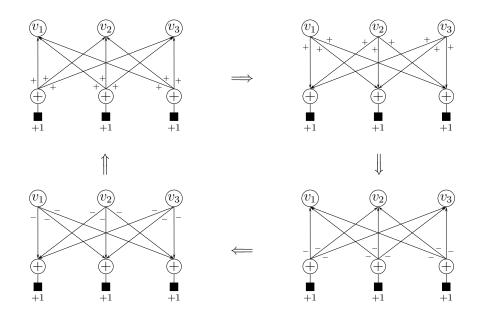

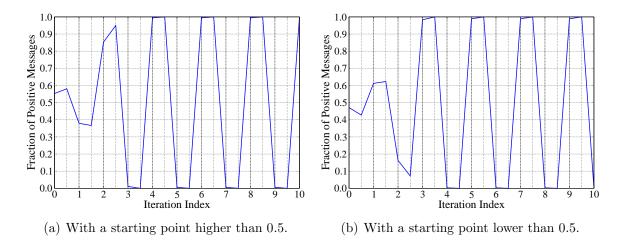

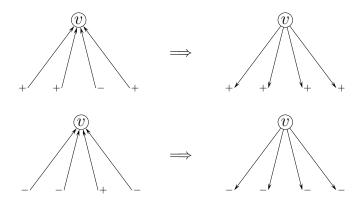

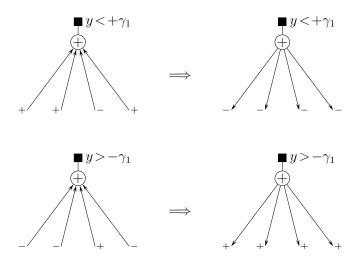

|   |     | 6.2.1   | The Trap of Message Oscillation                        | 77         |

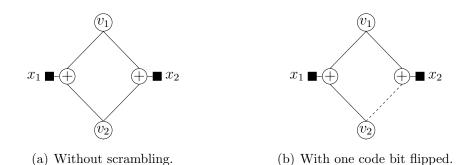

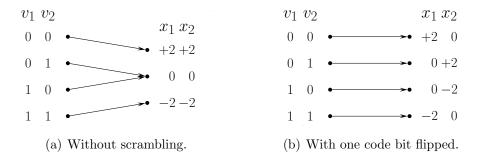

|   |     | 6.2.2   | Distinguishability of Overlapped Repetition Code Words | 85         |

|   | 6.3 | Effects | s of Interleaving                                      | 87         |

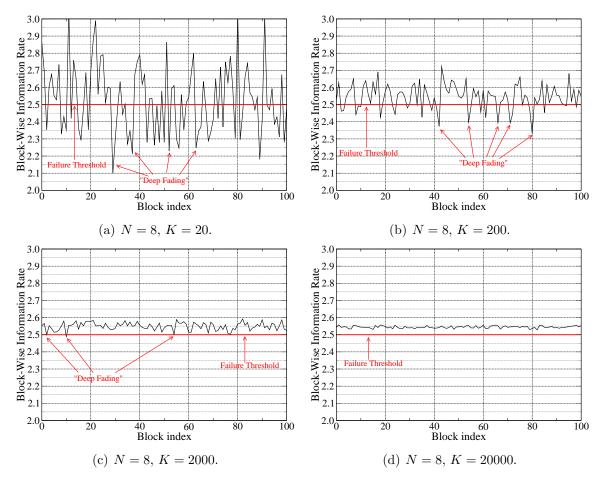

|   |     | 6.3.1   | A First Impression                                     | 87         |

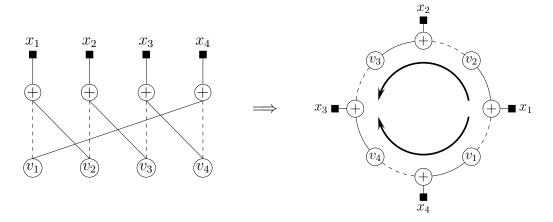

|   |     | 6.3.2   | A Heuristic Example for Interleaver Design             | 88         |

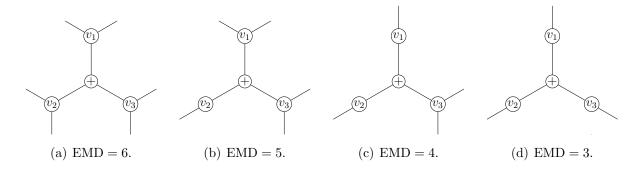

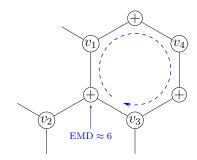

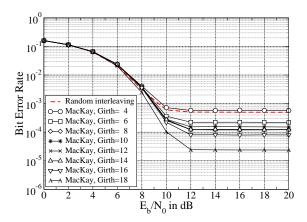

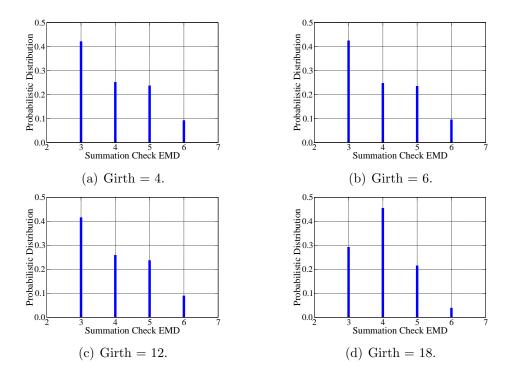

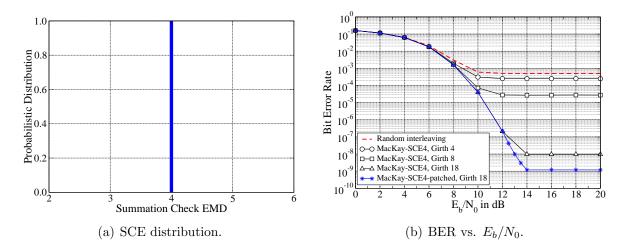

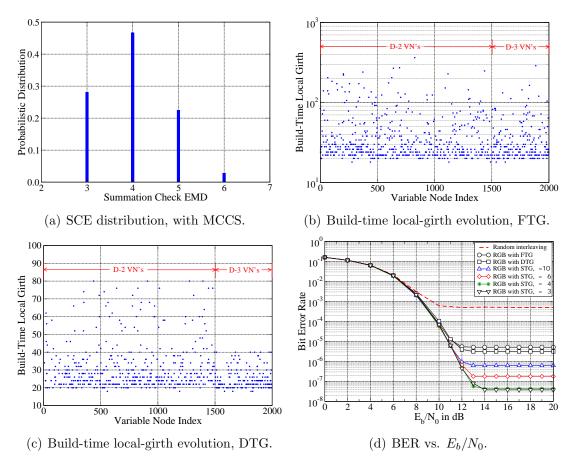

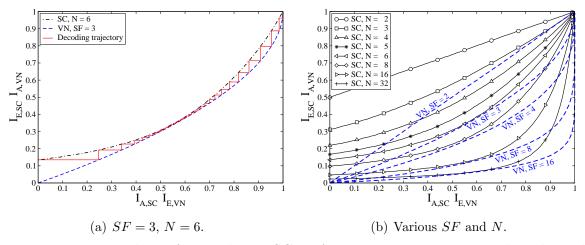

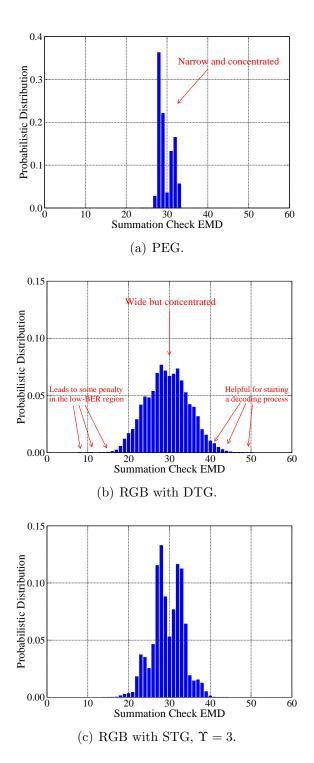

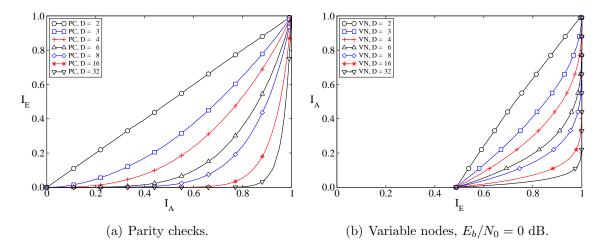

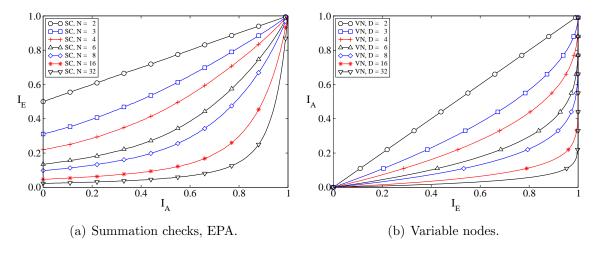

|   |     | 6.3.3   | Summation Check Extrinsic Message Degree               | 91         |

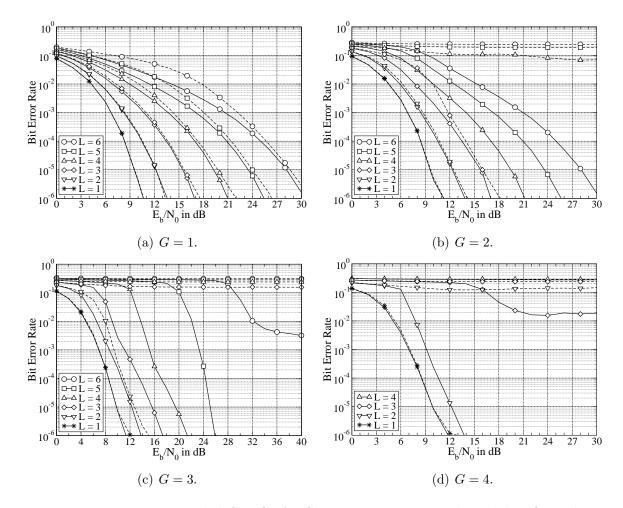

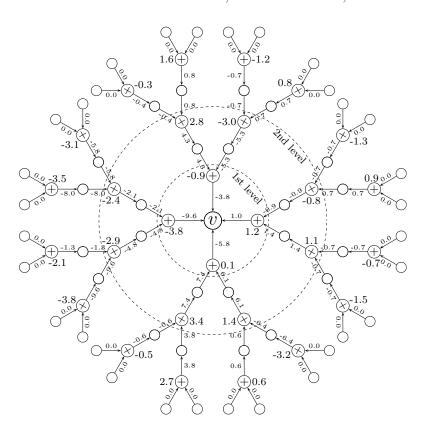

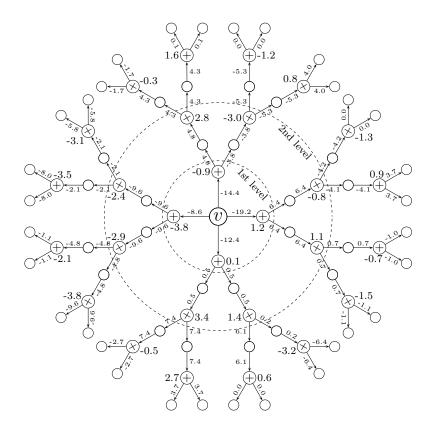

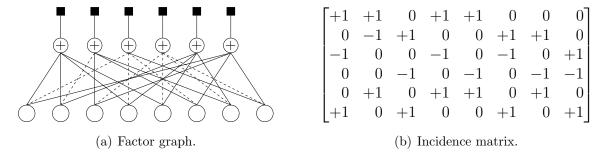

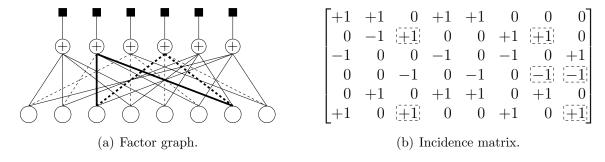

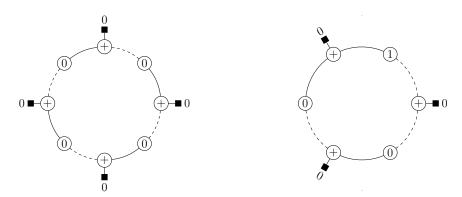

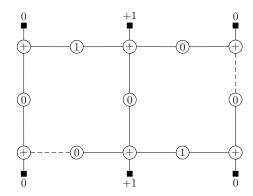

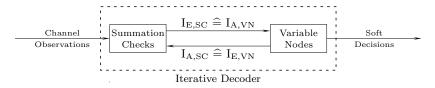

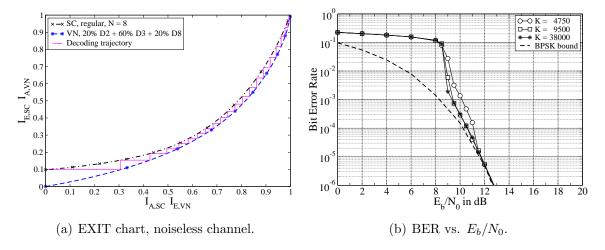

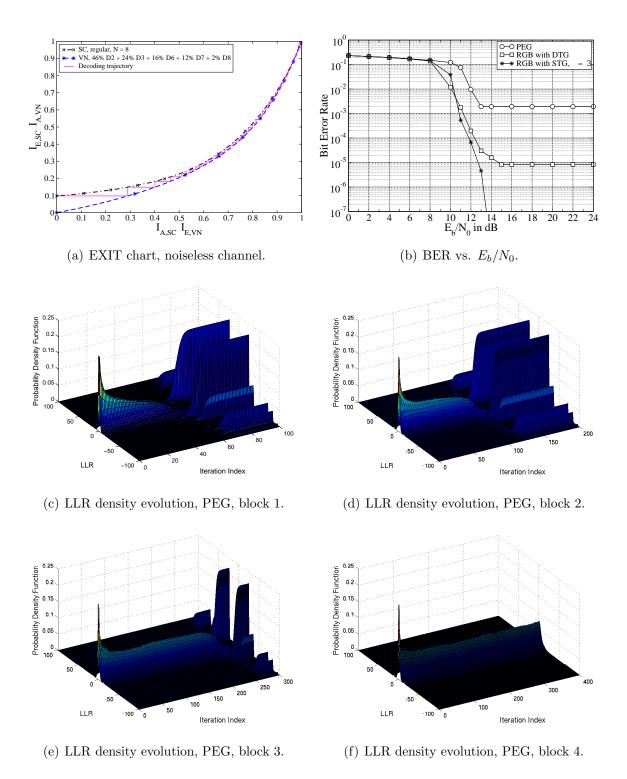

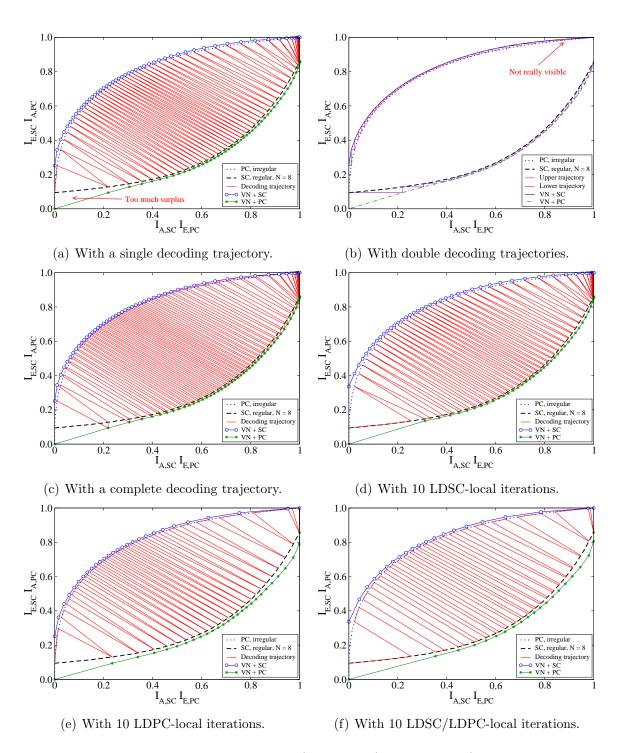

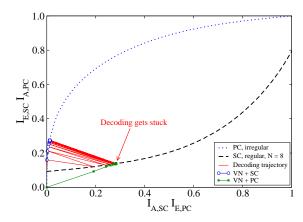

|   | 6.4 | Low-D   | Density Summation-Check Code                           | 93         |

|   |     | 6.4.1   | Basic Principle                                        | 94         |

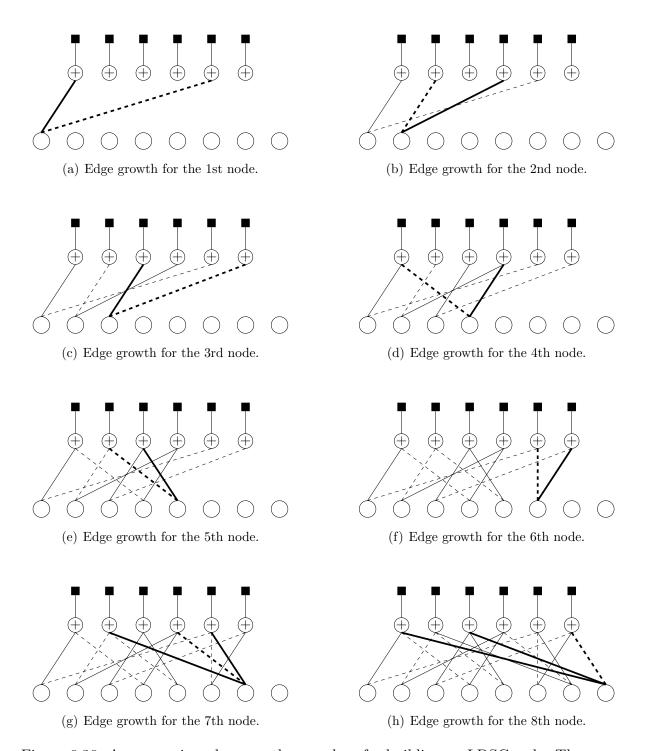

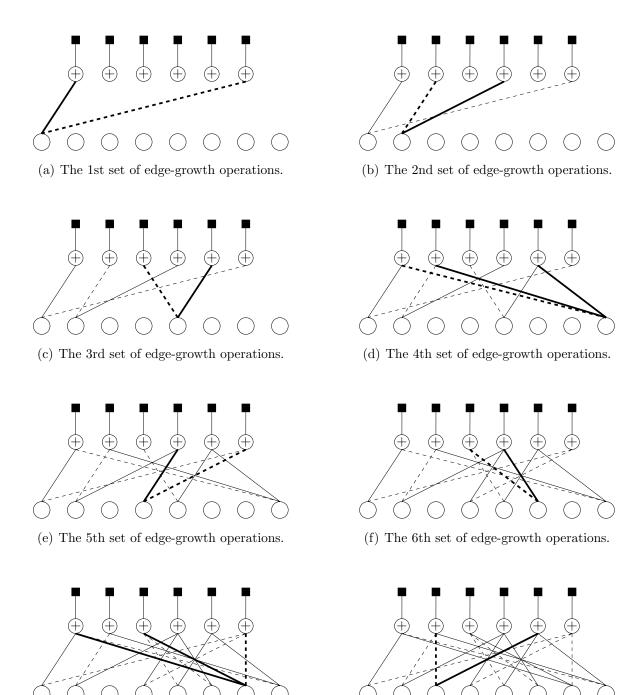

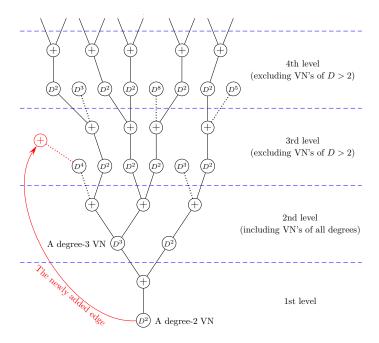

|   |     | 6.4.2   | Computer-Based Interleaver Design                      | 96         |

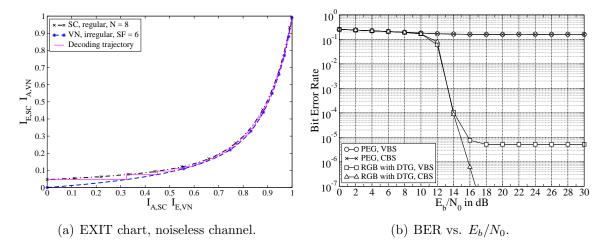

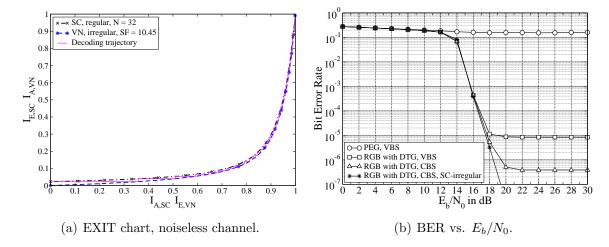

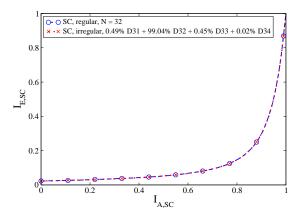

|   |     | 6.4.3   | Computer-Based Scrambler Design                        | 110        |

|   |     | 6.4.4   | Supportable Rate with Regular Repetition               | 116        |

|   |     | 6.4.5   | Supportable Rate with Irregular Repetition             | 119        |

| 7 | Cha | annel C | Coding for Superposition Mapping                       | 127        |

|   | 7.1 | Some    | Theoretical Aspects                                    | 128        |

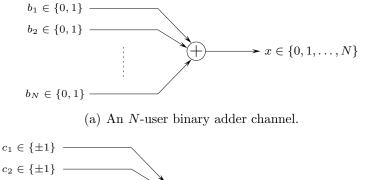

|   |     | 7.1.1   | Duality to Binary Adder Channel                        | 128        |

|   |     | 7.1.2   | Finite-Error Capacity for Coded SM Transmission        |            |

|   |     | 7.1.3   | Typicality of Finite-Length Symbol Sequences           |            |

|   |     | 7.1.4   | Maximum-Likelihood Decoding vs. Iterative Decoding     |            |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog | graphy         |                                          | 201   |

|---------------------------|--------|----------------|------------------------------------------|-------|

| 8                         | Sun    | nmary          | and Outlook                              | 199   |

|                           |        | 7.6.4          | The Case of 4 bits/symbol                | . 197 |

|                           |        | 7.6.3          | The Case of 2 bits/symbol                | . 195 |

|                           |        | 7.6.2          | The Case of 1 bit/symbol                 | . 193 |

|                           |        | 7.6.1          | Preliminary Remarks                      | . 192 |

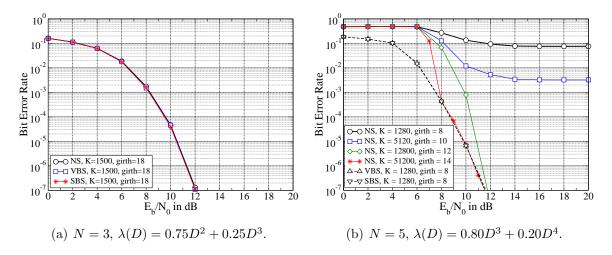

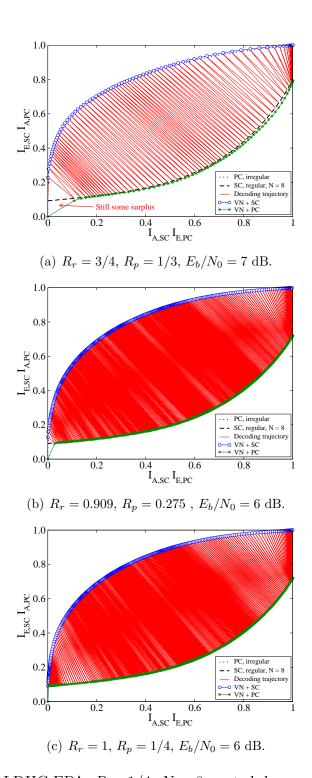

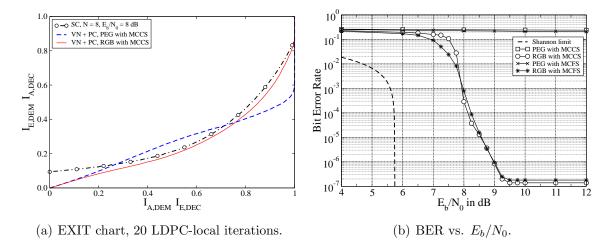

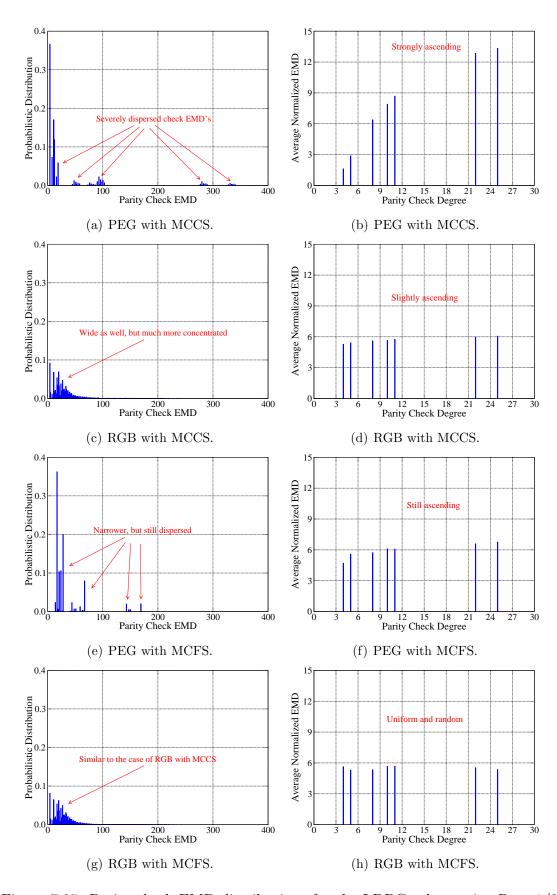

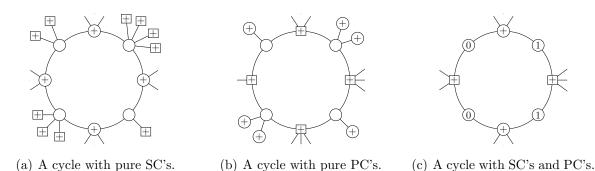

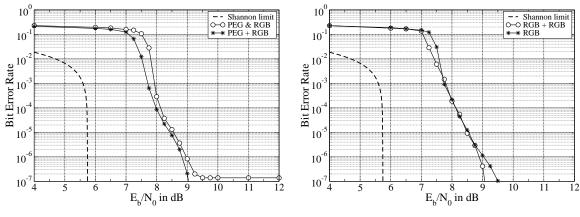

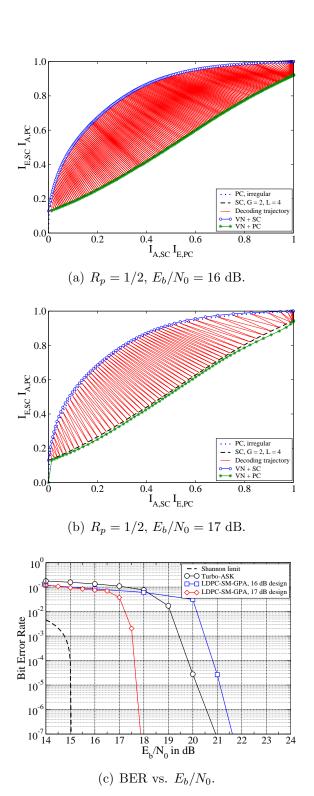

|                           | 7.6    | Code           | Design Examples for the AWGN Channel     | . 192 |

|                           |        | 7.5.4          | The Case of $N=16$                       | . 189 |

|                           |        | 7.5.3          | The Case of $N=8$                        | . 188 |

|                           |        | 7.5.2          | The Case of $N=4$                        |       |

|                           |        | 7.5.1          | The Case of $N=2$                        |       |

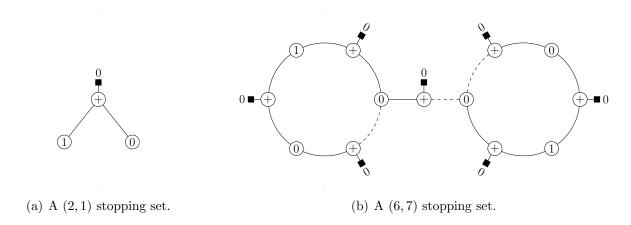

|                           | 7.5    |                | Design Examples for the Noiseless BAC    |       |

|                           |        | 7.4.5          | Is Scrambling Still Necessary?           |       |

|                           |        | 7.4.4          | Possible Ways for Interleaver Design     |       |

|                           |        | 7.4.2<br>7.4.3 | Compatible Code Structures               |       |

|                           |        | 7.4.1          | Basic Principle                          |       |

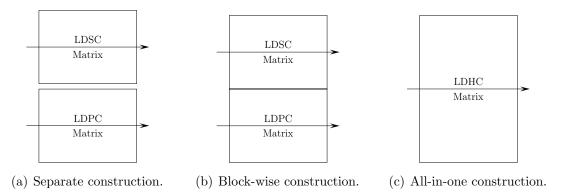

|                           | 7.4    |                | Density Hybrid-Check Code                |       |

|                           |        | 7.3.2          | Repetitions plus Parity Bits             |       |

|                           |        | 7.3.1          | Repetitions vs. Parity Bits              | . 143 |

|                           | 7.3    | Suitab         | ble Redundancy for Superposition Mapping | . 143 |

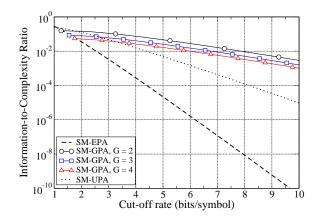

|                           |        | 7.2.2          | Compression Gain and Irregularity Loss   | . 140 |

|                           |        | 7.2.1          | Information-to-Complexity Ratio          | . 138 |

|                           | 7.2    | Some           | Practical Aspects                        | . 138 |

| A            | Acronyms and Abbreviations             | 211 |

|--------------|----------------------------------------|-----|

|              | A.1 Acronyms                           | 211 |

|              | A.2 Abbreviations                      | 213 |

| В            | Mathematical Notations                 | 215 |

| $\mathbf{C}$ | Mathematical Definitions & Derivations | 217 |

|              | C.1 Definition of LLRs                 | 217 |

|              | C.2 Entropy of Gaussian Variable       | 218 |

|              | C.3 Quantization of Gaussian Variable  | 219 |

| D            | Own Publications Related to the Thesis | 221 |

# Chapter 1

# Introduction

When considering data transmission over physical channels, a modulator is the interface which maps data sequences onto analog signals that match the characteristics of the channel [1]. By convention, digital modulation consists of three separate steps: mapping binary digits (bits) onto continuous valued symbols, mapping discrete-time symbols onto continuous-time pulses, and loading pulses onto carrier waves. All three steps have significant influence on the system power and bandwidth efficiency. Nevertheless, a discrete-time baseband channel model already comprises the second and third steps, as well as matched filtering and sampling. Therefore, the focus of this thesis will be merely on the first stage, i.e., the mapping from bits to symbols, and the related channel coding techniques. As a matter of fact, channel coding and mapping are the kernel parts of digital communication, from an information theoretical point of view.

## 1.1 Background

According to information theory, the capacity of a Gaussian channel corresponds to the maximum mutual information between channel inputs and outputs [2]. Given a power constraint, this maximum can be achieved if and only if the channel outputs are Gaussian distributed. Strictly speaking, this is only possible if the channel inputs are Gaussian as well. This issue has been puzzling engineers and researchers for several decades, as it is practically difficult to map bits onto a Gaussian symbol and to separate a Gaussian symbol from Gaussian noise. Nevertheless, at low signal-to-noise ratios (SNRs), binary antipodal symbols often suffice, due to the strong impact of the additive noise on the channel output distribution. This explains why early works focus on the power-limited regime and the proposed coding techniques are exclusively binary.

In the first 50 years since Shannon's landmark paper [3], tremendous effort has been spent on finding good codes for data transmission with binary symbols. As a result, the field of binary coding has already become rather mature, especially after the invention of turbo codes [4] and the rediscovery of low-density parity check (LDPC) codes [5, 6]. Given binary antipodal signalling and sufficiently long block lengths, researchers have been able to approach the Shannon limit of the Gaussian channel as close as just a few thousandths of decibels [7]. Hence, the problem of approaching the Gaussian channel capacity in the power-limited regime has mostly been solved. In contrast, the field of modulation as well as coding for the high-SNR bandwidth-limited regime is still under development. Until the 1970's, the common practical solution for high-rate transmission was nothing more than uncoded higher-order modulation, e.g., phase-shift keying (PSK) and quadrature amplitude modulation (QAM). The success of trellis-coded modulation [8], which is based on the concept of set partitioning, unveiled the importance of channel coding for nonbinary data transmission. Also based on set partitioning, multilevel coding [9,10] showed to be an alternative way to improve the performance of higher-order modulation. A breakthrough was finally achieved in the late 1990's when the concept of bit-interleaved coded modulation (BICM) [11,12] was formalized. Placing a bit-level interleaver between the encoder and the mapper and performing iterative demapping and decoding at the receiver, a superior performance was achieved for binary-encoded higher-order modulation systems. Upon this point, it was recognized that available capacity-achieving binary codes are also suitable for non-binary modulation formats, if the structure of BICM is adopted. Hence, there seems to be only one remaining issue for approaching the channel capacity in the high-SNR regime. That is to generate Gaussian-distributed symbols and devise corresponding receiver algorithms.

Mainly due to the desire of easy transmission and detection, most of the traditional mapping schemes produce uniformly distributed symbols. This in the end caused an impassable gap between the Shannon limit and the practically achievable performance, as the capacity of high-SNR Gaussian channels can only be achieved if the inputs are sufficiently Gaussian. To solve this problem, the concept of signal shaping came into being in the late 1980's [13,14]. Signal shaping is sometimes also called constellation shaping. The basic idea is to construct a high-dimensional uniform constellation which results in low-dimensional nonuniform constituent constellations. Since the high-dimensional constellation is uniform, a one-to-one mapping can be established between a block of bits and a block of symbols. Meanwhile, as the constituent constellation is now nonuniform, often Gaussian-like, a shaping gain can be obtained without any additional effort w.r.t. channel coding. It was shown that signal shaping yields an essential contribution to approach the capacity at high SNRs [13]. In the 1990's, many practical schemes were introduced for an efficient implementation of signal shaping. Among these schemes, the most well-known

1.2. MOTIVATION 3

and successful two are trellis shaping [15] and shell mapping [16–19], both of which are capable of delivering shaping gains about 1 dB. Particularly, shell mapping later became a part of the international telephone-line modem standard ITU recommendation V.34 [20].

With capacity-achieving binary codes, bit-interleaved coded modulation, and signal shaping, it is nowadays a common assumption for researchers that the problems in approaching the Shannon limit of linear Gaussian channels for the high SNR regime have essentially been solved [21]. Nevertheless, this is not completely true.

### 1.2 Motivation

It is true that available capacity-achieving binary codes can easily be incorporated into a BICM system. However, there will be some tricky issues when one applies signal shaping techniques in a BICM system. Both trellis shaping and shell mapping are block-wise uniform signaling methods, which can attain the ultimate shaping gain [13] only in the limit of infinite dimension, i.e., only in the case of infinite symbol block lengths. Hence, to obtain desirable shaping gain, one needs to take a sufficiently large block length. However, a large block length means a high addressing complexity [22], which also makes the calculation of bit-level soft decisions more difficult. As a matter of fact, given a practical symbol block length, e.g., 16 in ITU V.34, bit-level soft decisions can only be calculated in an approximate way. This certainly incurs performance losses when applying signal shaping in a BICM system, since available high-performance channel codes all demand soft decoding. As an alternative approach, Kschischang et al. proposed in [23] a nonuniform signaling scheme that maps simple variable-length prefix codes, particularly Huffman codes, onto a constellation that has been designed according to a Maxwell-Boltzmann distribution [24,25]. This approach can achieve the ultimate shaping gain in any dimension, i.e., can be performed in a symbol-wise manner, but is unfortunately a data-dependent variable-rate mapping scheme, which brings even more problems for a practical receiver.

To facilitate easy implementation, one needs a fixed-rate symbol-wise mapping scheme that produces Gaussian-like symbols. As mentioned above, trellis shaping, shell mapping, and Huffman decoding all violates this requirement. Nonetheless, a recently evolving technique seems to fulfill this requirement very well. The main idea is to load multiple bits onto a symbol simply via linear superposition. Without loss of generality, we may call the corresponding technique as superposition mapping (SM). For SM, the amount of bits loaded on a symbol is fixed and data-independent, subject to the concrete system design. Besides, superposition mapping generally operates in a symbol-wise manner. According to the central limit theorem, the summation of many i.i.d. variables tends to be Gaussian

distributed. Hence, it is very easy to let a superposition mapper to produce Gaussian-like symbols. Given these properties, superposition mapping provides an attractive solution for the applications that demand high bandwidth and power efficiency.

In 1997, Duan et al. proposed in [26] a modulation scheme which resembles very much a multiple access system. In this scheme, multi-level coded symbol streams are linearly superimposed before being sent via the channel, and are sequentially separated at the receiver side via successive interference cancellation (SIC). Due to linear superposition, the channel symbols have Gaussian-like nonuniform distributions regardless the fact that the parallel constituent symbol streams are all binary antipodal. For this reason, the authors claimed that large signal constellation and active signal shaping are no longer necessary in such a system. This is the first time that researchers explicitly use linear superposition as a mapping scheme. Although no detailed discussion was presented in [26], this work initiated the research on the topic of superposition mapping.

Ma and Li Ping provided a comprehensive analysis of superposition mapping in [27]. It was shown that single-level coded superposition mapping can achieve similar performance. It was also shown that, with a capacity-achieving binary code, e.g., a Turbo code, superposition mapping is indeed capacity-achieving for linear Gaussian channels. Nevertheless, the bandwidth efficiency of the reported results is limited to 2 bits/symbol per signal dimension. Almost at the same time, Schoeneich and Hoeher proposed in [28] a multi-layer interleave-division multiple access (ML-IDMA) scheme where interleave-division multiplexing (IDM) is done for each user. The kernel part of IDM is in fact a phase-shifted superposition mapper (PSM), which is different from the scheme proposed in [27] by adding a unique phase shift to each antipodal signal before superposition. However, the reported results were limited to 2 bits/symbol per signal dimension as well. It was presumed by the authors of both [27] and [28] that higher bandwidth efficiency can only be supported by means of performance tradeoff via unequal power allocation. Although this presumption is later found to be unprecise [29, 30], it does give an important message about the special property of superposition mapping, that is it is very challenging to support high bandwidth efficiency in case of equal power allocation. Similar issues are also encountered in SM-related modulation techniques, which are non-unique mapping [31], generalized modulation [32], modulation doping [33], etc...

Because of its fixed-rate symbol-wise working style, superposition mapping is undoubtedly an attractive solution for generating near-optimum nonuniform symbols. However, without breaking the tight limit on supportable bandwidth efficiency, the applicable scenarios will be constrained. Certainly, breaking the bandwidth efficiency limit should not be done at the price of degraded power efficiency, or in other words it should not be done at the price of damaging the Gaussian-like symbol distribution. Both [27] and [28] did

not provide sufficient theoretical analysis in the concern of the reason of the bandwidth efficiency limit of superposition mapped data transmission. Nevertheless, one thing is clear, that is the commonly applied coding approaches for superposition mapping are not optimal. Since superposition mapping resembles very much a multiple-access system, one may wonder if we can use the techniques available therein to accomplish this task. As a matter of fact, the coding theory for multiple-access systems, or equivalently linear superposition channels, is still far from being mature. Up to the time of writing this thesis, there are indeed no capacity-achieving practical codes for general multiple-access channels with Gaussian noise. Besides, when researchers are designing codes for multiple-access systems, the issue of keeping Gaussian-like symbol distribution is usually not taken into account, as this is rarely an issue in that scenario. For example, the so-called near-optimum uniquely decodable codes [34–36] for multiple-access channels are capacity-achieving only in the case of noiseless channels, as these codes all lead to non-Gaussian-like symbol distributions. Therefore, in order to fully exploit the capacity-achieving potential of SM, suitable channel codes need to be found. This gives the motivation for this thesis work.

## 1.3 Scope and Aim

This thesis aims to provide a deep insight into the principles of superposition mapping and to develop channel codes that well fit with this type of mapping schemes. It does not try to solve all the open problems, but it does try to solve the most important issues that are critical for practical applications.

The first attempt is to examine the effect of power allocation on the power/bandwidth efficiency of superposition mapping. In many previous works [27, 37–40], it is observed that unequal power allocation can efficiently enhance the supportable bandwidth efficiency of coded superposition mapping, but also causes the symbol distribution non-Gaussian-like. Certainly, this is undesirable from an information theoretical point of view, as this undermines the capacity-achieving potential of superposition mapping. Hence, to find an unequal power allocation strategy that improves the supportable bandwidth efficiency of SM but does not degrade the achievable power efficiency is of particular importance.

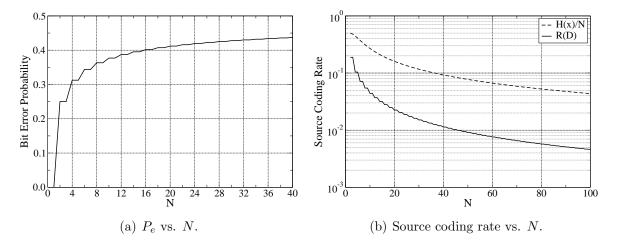

Due to linear superposition, superposition mapping is often non-bijective, which raises a problem that ambiguity-free detection is even not possible for a noiseless channel. This fact brings a fundamental challenge for the design of channel codes, as currently available code design techniques are all targeted at bijective mapping schemes. A non-bijective superposition mapper might be treated as a lossy source encoder, or in other words lossy compression happens during the mapping process. To enable ambiguity-free decoding at

the receiver side, the channel code has to be designed in a way that the lossy compression (superposition mapping) on the code bits does not incur any information loss on the info bits. This special requirement opens an interesting new research area for channel coding.

For clearness and compactness, the additive white Gaussian noise (AWGN) channel is assumed throughout this thesis, i.e., topics related to fading, intersymbol interference (ISI), and transmission with imperfect channel knowledge are excluded. However, the coding techniques proposed in this thesis can easily be extended to more general applications, such as multi-antenna transmission, multi-carrier transmission, etc..

#### 1.4 Thesis Outline

The contents in the remainder of this thesis develop as follows.

Chapter 2 introduces the discrete-time additive white Gaussian noise channel model and related information theoretical concepts.

Chapter 3 provides a systematic view on superposition mapping. The main attention is given to the effects of power allocation. Given different types of power allocation strategies, the signal properties of superposition mapping are carefully studied, particularly the achievable power efficiency and supportable bandwidth efficiency. A grouped power allocation strategy is proposed to boost the performance potential of SM.

**Chapter 4** examines the performance of uncoded SM transmission over the Gaussian channel, given maximum-a-posteriori bit-by-bit detection. Some interesting issues related to source coding are inspected.

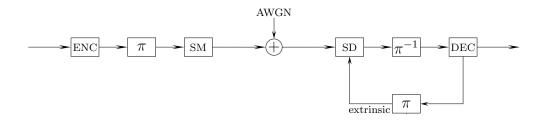

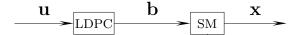

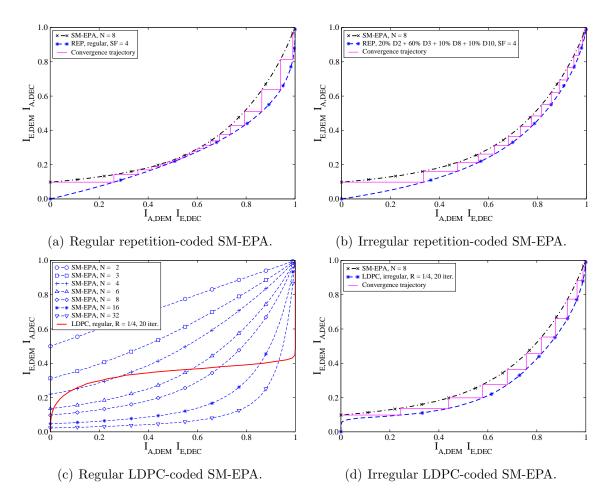

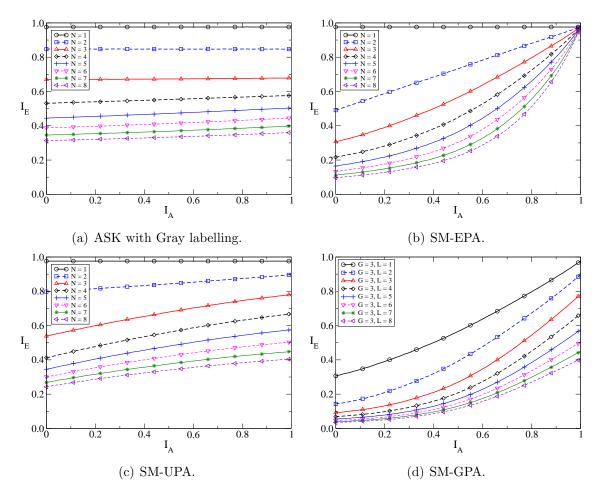

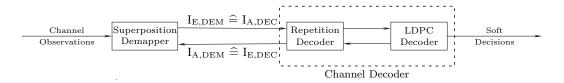

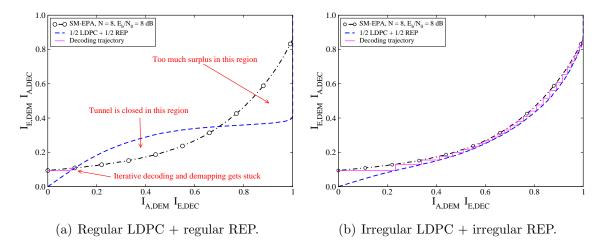

Chapter 5 provides a preliminary discussion for coded SM transmission over the Gaussian channel. Several low-complexity SISO demapping algorithms are introduced. The performance of repetition-coded SM and parity-check-coded SM are briefly surveyed.

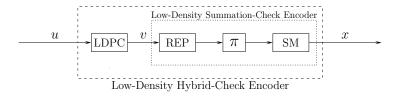

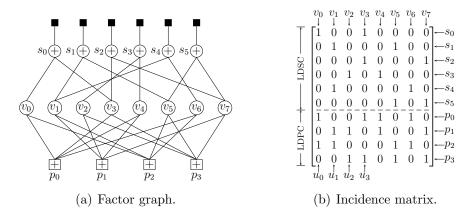

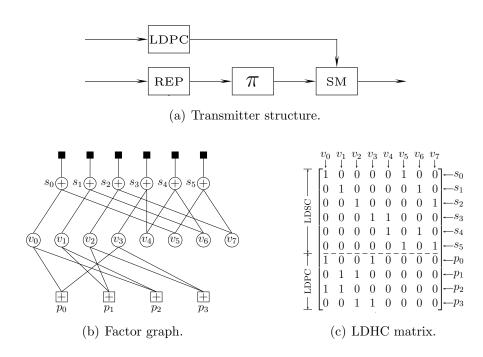

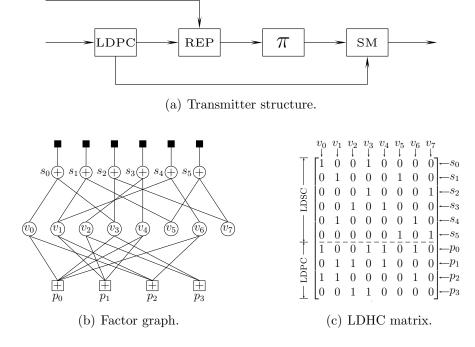

Chapter 6 makes a thorough investigation for the influence of spreading, scrambling, and interleaving on the performance of repetition-coded SM. A novel concept, called low-density summation-check (LDSC) coding, is proposed to facilitate system optimization.

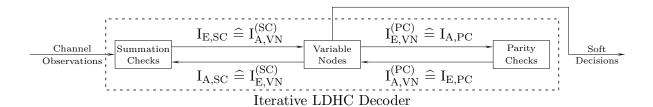

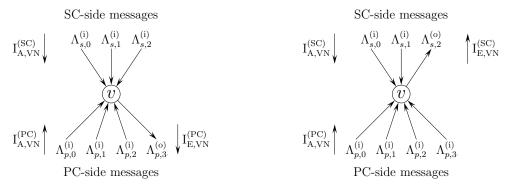

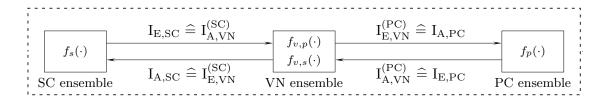

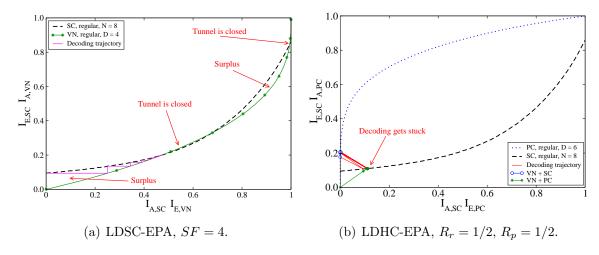

Chapter 7 discusses the topic of channel coding for superposition mapping in a more general framework. Various theoretical as well as practical issues are investigated. To enable a clever combination of repetition coding and parity check coding for SM, a unified coding concept called low-density hybrid-check (LDHC) coding is proposed.

Chapter 8 summarizes the work and enumerates interesting topics for future research.

# Chapter 2

# Gaussian Channel

The additive white Gaussian noise (AWGN) channel is probably the most important continuous alphabet channel, and is the prime for algorithm prototyping and system design. Though very simple, it models the fundamental effects of communication in a noisy environment. The AWGN channel is a building block for most practical channel models. Since the channel gain of the AWGN channel is constant, it provides a performance upper bound for many communication channels.

## 2.1 Channel Model

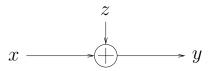

For modern digital communication systems, the most popular channel model is the discrete-time AWGN channel model described by

$$y = x + z$$

,  $z \sim \mathcal{N}(0, \sigma_z^2)$ , (2.1)

where y is the channel output, x is the channel input, and z is a noise sample drawn i.i.d. from a zero-mean Gaussian distribution with variance  $\sigma_z^2$  and is assumed to be independent of the channel input. Fig. 2.1 depicts this channel model. In reality, the additive noise may be caused by many different things, such as the circuit noise, the ambient noise, and the quantization noise, etc. However, according to the central limit theorem, the

Figure 2.1: Discrete-time additive white Gaussian noise channel.

cumulative effect of a large number of small random effects will be approximately normal distributed. Therefore, the Gaussian assumption of the additive noise is valid in a large number of situations.

To keep consistence with the convention and avoid possible notation confusion, throughout this thesis, we use  $E_s$  to represent the average symbol power/energy:

$$E_s \doteq \mathrm{E}\left\{x^2\right\}\,,\tag{2.2}$$

and  $N_0$  to represent the single-sided noise spectral density in the passband:

$$N_0 \doteq 2E\left\{z^2\right\} = 2\sigma_z^2 \ . \tag{2.3}$$

The technical background of this notation convention can be found in [1].

#### 2.2 Mutual Information

Mutual information is a measure of the amount of information that one random variable contains about another variable [2]. For a communication channel, the mutual information between its input and output is the reduction in the uncertainty of the input due to the knowledge of the output. If the channel input distribution is certain, this mutual information indeed gives the maximum rate at which information can pass through this channel with an arbitrarily low error probability.

Given the channel model in (2.1), the mutual information between the channel input and output is

$$I(x;y) = h(y) - h(y|x) = h(y) - h(z), (2.4)$$

where  $h(\cdot)$  denotes the differential entropy of a continuous random variable. By definition, the entropy of the channel output can be calculated as

$$h(y) = -\int p(y) \log p(y) \, dy. \qquad (2.5)$$

p(y) is the probability density function (PDF) of y, which is determined by the distribution of the channel input and the additive noise. For practical systems, the channel input will usually be a finite-alphabet discrete random variable, which leads to

$$p(y) = \sum_{x \in \mathcal{X}} P(x)p(z = y - x) = \sum_{x \in \mathcal{X}} P(x) \frac{1}{\sqrt{2\pi\sigma_z^2}} e^{-\frac{(y - x)^2}{2\sigma_z^2}},$$

(2.6)

where  $\mathcal{X}$  is the finite alphabet of x, and P(x) is the probability mass function (PMF) of x. In this scenario, the PDF p(y) is a so-called mixed Gaussian function, which can be evaluated numerically via a computer.

Figure 2.2: Liquid (information) flowing through a pipe (channel).

For Gaussian distributed noise samples z, we have

$$h(z) = \frac{1}{2} \log 2\pi e \sigma_z^2 . \tag{2.7}$$

A detailed mathematical derivation of (2.7) is given in Appendix C.2.

Using (2.4) to (2.7), the mutual information given any input distribution can be computed.

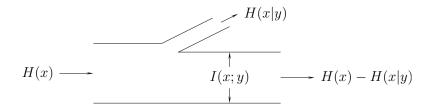

In general we have

$$I(x;y) \leqslant H(x) , \qquad (2.8)$$

where  $H(\cdot)$  denotes the entropy of a discrete random variable. Hence, some information carried in x can not pass through the channel due to the disturbance from the noise. This phenomenon resembles a pipe with one input port, one narrower output port, and one leaking port, as illustrated in Fig. 2.2. The amount of information that is leaked out is given by H(x|y), and the amount of information that finally passes the channel is given by I(x;y) = H(x) - H(x|y). A communication system engineer needs to optimize the distribution of x (without changing the average power) to widen the pipe output port as much as possible so that information can pass through it easily. A natural question would be what is the maximum channel throughput and what is the corresponding distribution for x. This motivates the concept of channel capacity.

## 2.3 Capacity for Zero Error Probability

The channel capacity is the highest rate in bits per channel use at which information can be transfered with an arbitrarily low error probability [2]. Without any constraint on the channel input, the capacity of an AWGN channel is infinite. This is easy to understand, as one may choose an infinite set of inputs which are arbitrarily far apart from each other, so that they are distinguishable at the output with an arbitrarily small error probability. In practice, however, there will be always certain type of constraints on the channel input, among which the most common limitation is the power/energy constraint. Usually, the average power/energy that can be used to transmit a symbol is limited by physical reasons.

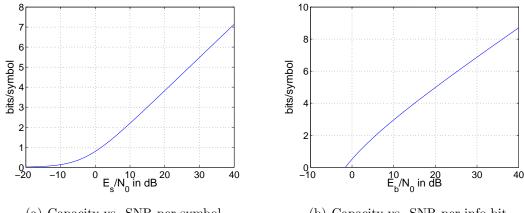

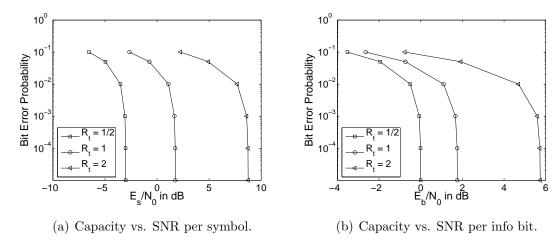

- (a) Capacity vs. SNR per symbol.

- (b) Capacity vs. SNR per info bit.

Figure 2.3: AWGN channel capacity for a zero error probability.

The channel capacity under input power constraint is given by

$$C = \max_{p(x): E\{x^2\} = E_s} I(x; y) = \max_{p(x): E\{x^2\} = E_s} \{h(y) - h(z)\}.$$

(2.9)

Since h(z) is constant as long as the noise power is certain, the only concern is to maximize h(y) given the power constraint. Noting that the noise z is zero-mean and independent of x, we have

$$E\{y^2\} = E\{(x+z)^2\} = E\{x^2\} + E\{z^2\} = E_s + N_0/2.$$

(2.10)

It is known that the Gaussian distribution maximizes the entropy over all distributions with the same variance [2], which brings the following inequality:

$$h(y) \leqslant \frac{1}{2} \log 2\pi e(E_s + N_0/2)$$

(2.11)

Hence, the capacity of the AWGN channel is

$$C = \frac{1}{2}\log 2\pi e(E_s + N_0/2) - \frac{1}{2}\log 2\pi e(N_0/2) = \frac{1}{2}\log_2\left(1 + 2\frac{E_s}{N_0}\right) \text{ bits/symbol}, (2.12)$$

which is attained if and only if y is Gaussian, which in turn requires x to be Gaussian. Therefore, to maximize the mutual information for a Gaussian channel, one needs to make the channel input as Gaussian as possible, which gives the motivation for studying superposition mapping.

Fig. 2.3(a) plots the channel capacity versus SNR per symbol. It is often useful to have a plot of channel capacity vs. SNR per info bit. This can be obtained by treating the relationship between channel capacity and SNR in a different way. With a little bit of manipulation on (2.12), we get

$$\frac{E_s}{N_0} = \frac{1}{2}(2^{2C} - 1) , \qquad (2.13)$$

Figure 2.4: A transmission system with a finite error probability.

which states the minimum SNR per symbol required to achieve capacity C in bits/symbol. Noting that  $E_b = E_s/C$ , we attain the minimum SNR per info bit to achieve the capacity:

$$\frac{E_b}{N_0} = \frac{E_s}{N_0} / C = \frac{1}{2} (2^{2C} - 1) / C . \tag{2.14}$$

Fig. 2.3(b) gives the plot of channel capacity vs. SNR per info bit.

## 2.4 Capacity for Finite Error Probability

Fig. 2.3 gives a fundamental guideline for the design of practical communication systems, as it clearly states the maximum achievable information rate for error-free transmission. Equivalently, it states that the channel capacity must be larger than or equal to the transmission rate in order to guarantee a perfect reconstruction of the transmitted info bits. In the AWGN channel scenario, it tells the minimum required SNR for perfect transmission, given a certain transmission rate.

What happens if errors are allowed? In practical applications, the bit error probability is usually required to be lower than a certain threshold but not necessarily to be zero, particularly in voice and video communication. In such cases, one may want to know the minimum required SNR for a finite error probability instead of a zero error probability, which is however not explicitly stated in the theorem of channel capacity. To provide the answer for this question, it is necessary to incorporate the rate distortion theory.

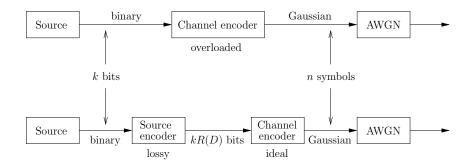

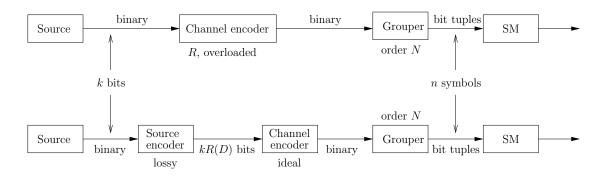

Consider a communication system with a binary source, a channel encoder with Gaussian outputs, and an AWGN channel, as depicted in the upper part of Fig. 2.4. The binary source generates a sequence of k i.i.d. bits with Bernoulli( $\frac{1}{2}$ ) distribution. After channel encoding, n Gaussian symbols are sent over the AWGN channel. Hence, the transmission rate of this system is given by  $R_t = k/n$  bits/symbol. The maximum allowed bit error probability is assumed to be  $P_e$ . To calculate the minimum required SNR, it is necessary

Figure 2.5: AWGN channel capacity for finite error probabilities.

to introduce an equivalent transmission system as depicted in the lower part of Fig. 2.4. In this equivalent system, lossy source encoding with Hamming distortion D is applied. The following channel encoder is assumed to be ideal, so that errors are now only introduced by the source encoder. According to the rate distortion theory, the minimum rate of the source code is given by the rate distortion function R(D). Consequently, the minimum information load of each code symbol is given by kR(D)/n bits. To have error-free channel decoding at the receiver side, the following inequality must be fulfilled:

$$C \geqslant kR(D)/n = R(D)R_t , \qquad (2.15)$$

i.e., the channel capacity must be larger than or equal to the information rate at the channel encoder output. For a Bernoulli( $\frac{1}{2}$ ) source, the rate distortion function with Hamming distortion D is given by

$$R(D) = \begin{cases} 1 - h(D) , & 0 \leq D \leq \frac{1}{2} , \\ 0 , & D > \frac{1}{2} , \end{cases}$$

(2.16)

and the bit error probability is exactly the same as the Hamming distortion. The above statements give the following inequality:

$$\frac{1}{2}\log_2(1+2\frac{E_s}{N_0}) \geqslant k(1-h(P_e))/n \implies \frac{E_s}{N_0} \geqslant \frac{1}{2} \left(2^{2(1-h(P_e))R_t} - 1\right) , \qquad (2.17)$$

which tells the minimum required SNR, given a certain bit error probability and a certain transmission rate. If the equality in (2.17) is attained, the system is said to be optimal. Fig. 2.5 gives an example for several transmission rates. These curves serve as tight bounds for the achievable power efficiency of practical systems, i.e., the BER curve of a practical system will always be on the right side of the corresponding bound.

# Chapter 3

# Superposition Mapping (SM)

According to Shannon's information theory, the capacity of a Gaussian channel can be achieved if and only if the channel outputs are Gaussian distributed. In the low SNR regime, the strong impact from the additive Gaussian noise makes the channel outputs Gaussian even if the inputs are far from Gaussian. For this reason, conventional uniform mapping schemes are already capacity-achieving at low SNRs. Nonetheless, low SNR means low capacity, and low capacity means low bandwidth efficiency. To attain high bandwidth efficiency, one needs to operate in the high SNR regime. For high SNRs, the channel outputs can only be Gaussian if the channel inputs have a distribution with a Gaussian-like envelope. In this scenario, conventional uniform mapping schemes are no longer suitable. Superposition mapping (SM), as a newly evolving modulation technique, seems to fulfill this requirement very well. The characteristic feature of this technique is that the conversion from binary digits to symbols is done by a certain form of linear superposition instead of bijective (one-to-one) mapping. Due to linear superposition, the symbol distribution can be as Gaussian as desired. On the other hand, superimposed components interfere with each other, and the resulting relationship between bit tuples and symbols is often non-bijective. As a result, SM shows many different features w.r.t. conventional uniform mapping schemes. In this chapter, we perform a systematic study on SM and try to understand SM from an information theoretical point of view. Particular focus is on the effects of power allocation. It will be shown that equal power allocation (EPA) provides an excellent power efficiency but comes with a limited bandwidth efficiency for a reasonable superposition order. In contrast, unequal power allocation (UPA) provides a high bandwidth efficiency but a degraded power efficiency. To overcome the drawbacks of EPA and UPA, a novel scheme called grouped power allocation (GPA) is proposed. SM-GPA delivers a significantly improved bandwidth efficiency w.r.t. SM-EPA but does not degrade the achievable power efficiency like SM-UPA does.

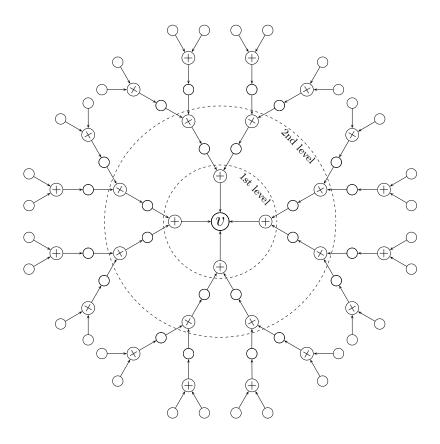

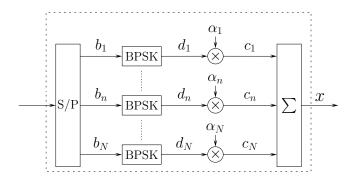

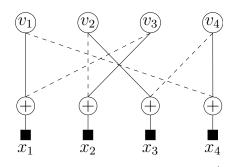

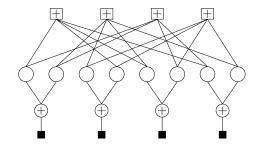

Figure 3.1: General structure of superposition mapping.

## 3.1 General Description

Linear superposition is a natural phenomenon in the real world, which partly explains the prevalence of the normal distribution, as the cumulative effect of many random effects will be approximately normal distributed. According to the central limit theorem, the mean of a sufficiently large number of i.i.d. random variables will be approximately Gaussian distributed. Equivalently, if one superimpose many i.i.d. variables and fix the total power of these variables, the resulting summation will be approximately Gaussian. Hence, it is a natural idea to use linear superposition to create Gaussian-like symbols.

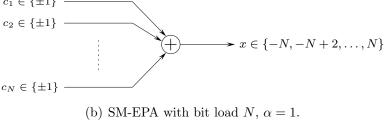

Fig. 3.1 shows a general structure of superposition mapping (SM) with binary antipodal component symbols. After serial-to-parallel conversion, N code bits are first converted into binary antipodal symbols via binary phase shift keying (BPSK). Then, a certain amplitude is allocated to each of these symbols. Afterwards, these component symbols are linearly superimposed to create a finite-alphabet output symbol. This procedure might be described by the following equation:

$$x = \sum_{n=1}^{N} c_n = \sum_{n=1}^{N} \alpha_n d_n = \sum_{n=1}^{N} \alpha_n (1 - 2b_n) , \quad \alpha_n \in \mathbb{R} , \quad b_n \in \{0, 1\} .$$

(3.1)

In the terminology of mapping, the SM mapping rule can be defined as

$$\phi_{\text{SM}}(\mathbf{b}) = \sum_{n=1}^{N} \alpha_n (1 - 2b_n) , \quad \mathbf{b} \in \mathbb{F}_2^N , \qquad (3.2)$$

i.e., a binary N-tuple is mapped onto a symbol with a finite alphabet. The amplitude coefficients  $\alpha_n$ ,  $1 \leq n \leq N$ , should be chosen in a way that  $E_{\phi_{\text{SM}}} = E_s$  is fulfilled. That is

$$E\{x^{2}\} = \sum_{n=1}^{N} E\{d_{n}^{2}\alpha_{n}^{2}\} = \sum_{n=1}^{N} \alpha_{n}^{2} \stackrel{!}{=} E_{s}, \qquad (3.3)$$

assuming that all chips are mutually independent. To fairly compare with other mapping schemes, one should normally take  $E_s = 1$ .

Certainly, instead of taking  $\alpha_n \in \mathbb{R}$ , one may also take  $\alpha_n \in \mathbb{C}$ . By using complexvalued coefficients  $\alpha_n$ , one can control not only the power of each chip but also the phase. This brings another degree of freedom for the design of superposition mapping. In [29], it is shown that allocating unique phases to superimposed chips increases the symbol cardinality and consequently improves the supportable bandwidth efficiency of SM given conventional channel coding schemes, e.g., convolutional codes. Nevertheless, allocating unique phases to superimposed chips also makes the SM constellation points non-equispaced and geometrically irregular in the complex signal space. This degrades the quality of SM symbol distribution and consequently deteriorates the performance of SM transmission over the Gaussian channels. Furthermore, unequispaced constellation points may cause a troublesome issue for the frontend circuit of a transmission system. As a matter of fact, the preference of phase-shifted superposition mapping (PSM) in many previous works [29, 38, 41–43] is mainly for the reason that the supportable bandwidth efficiency of SM without phase allocation is very limited, which is actually due to the unavailability of suitable channel codes. However, with the coding approaches provided in Chapter 6 and Chapter 7, this issue will be no longer existing. Given these considerations, we exclude the topic of phase allocation in this thesis and focus our discussion on realvalued superposition mapping, which might be considered as one signal dimension (either in-phase or quadrature) of complex-valued superposition mapping.

Hereafter, N will be called the bit load of the superposition mapper, and the binary antipodal component symbols  $c_n$  will be called chips. Obeying the convention of BPSK, the following correspondence holds:

$$b_n = 0 \quad \leftrightarrow \quad d_n = +1 \quad \leftrightarrow \quad c_n = +\alpha_n b_n = 1 \quad \leftrightarrow \quad d_n = -1 \quad \leftrightarrow \quad c_n = -\alpha_n$$

(3.4)

Note that using binary antipodal chips does not cause any limit on the overall bandwidth efficiency. To support different data rates, it is only necessary to adjust the bit load N of SM. Certainly, one may use higher-order modulation formats for the chips, but this merely increases the mapping and demapping complexity without bringing any practical or theoretical benefits. Hence, throughout this thesis, chips will be always binary antipodal.

Different from conventional mapping schemes, the cardinality of an SM symbol is not necessarily  $2^N$ . Let  $\mathcal{X}$  denote the alphabet of x. In general, the situation is

$$|\mathcal{X}| \leqslant 2^N \,, \tag{3.5}$$

i.e., the mapping rule is often non-bijective and subsequently the symbol distribution is often nonuniform. A nonuniform symbol distribution is desirable from an information theoretical point of view. However, a non-bijective mapping rule brings a fundamental challenge for the design of suitable channel codes, as discussed in later chapters.

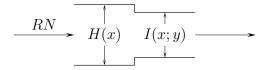

$$\underbrace{\text{ENC}}_{R} \xrightarrow{\text{N}} \underbrace{\text{AWGN}}_{V} \xrightarrow{y}$$

Figure 3.2: Coded SM transmission over Gaussian channel.

Figure 3.3: A "pipe" interpretation of the information path.

#### 3.2 An Information Theoretical View

Since a superposition mapper is often non-bijective, it takes some special carefulness when using it. In this section, superposition mapping is reexamined from an information theoretic point of view. The discussion herein serves as a guideline for the usage of SM.

When a superposition mapper is non-bijective, one has

$$H(x) < N \text{ bits}$$

, (3.6)

where  $H(\cdot)$  denotes discrete entropy. By the definition of entropy, H(x) is the average amount of information that an SM symbol can carry. In case of uncoded transmission, the total amount of information carried by N input bits is exactly N bit, assuming an ideal source encoder. If (3.6) holds, one is eventually loading more information than an SM symbol can carry. Consequently, error-free detection will not be possible. Hence, non-bijective superposition mapping is not suitable for uncoded transmission. To enable error-free detection, channel coding is necessary to reduce the information rate of the input bits of a superposition mapper.

Consider coded SM transmission over the AWGN channel, depicted in Fig. 3.2. The channel coding rate is given by R and the bit load of the superposition mapper is given by N. Without loss of generality, one may interpret the above system as a "pipe" with two sections, and the information passing through as certain type of "liquid", as illustrated in Fig. 3.3. The diameter of the first pipe section is given by the information-carrying capability of SM symbols, i.e., the symbol entropy H(x). The diameter of the second pipe section is given by the mutual information between the channel input and output, which is denoted by I(x;y). Due to the disturbance from the additive noise,  $I(x;y) \leq H(x)$  holds in general. As commonly known, the maximum throughput of a pipe is determined by the diameter of the narrowest section. Similarly, the maximum information rate of the above system is given by I(x;y), which is frequently called channel capacity with constrained

input. To enhance the effective system throughput, one should try to maximize I(x;y) instead of H(x).

Each SM symbol carries N code bits, while each code bit carries R bits information. Therefore, the amount of information that one loads onto an SM symbol is RN bits. To have error-free detection in case of noiseless transmission, the following condition has to be fulfilled:

$$RN \leqslant H(x) \quad \Rightarrow \quad R \leqslant H(x)/N \ . \tag{3.7}$$

This gives a tight constraint for systems employing superposition mapping. Note that for a non-bijective superposition mapper, one has H(x) < N. In this concern, SM is inferior to conventional uniform mapping schemes for which H(x) = N holds. Nevertheless, if the channel is noisy, an even tighter condition applies:

$$RN \leqslant I(x;y)$$

. (3.8)

In this scenario, SM with a properly designed power allocation strategy outperforms uniform mapping schemes in the sense of higher mutual information given a certain power constraint, which is the main topic of discussion in the following sections.

## 3.3 Equal Power Allocation (EPA)

In principle, one can take infinite possibilities in choosing the power allocation scheme for superposition mapping. Nevertheless, the simplest yet the most essential scheme is the equal power allocation (EPA) scheme, which assigns all chips with the same amplitude. This simple mechanism leads to an elegant mathematical description and a well-structured symbol distribution. As a matter of fact, the EPA scheme lies in the heart of the capacity-achieving potential as well as the working philosophy of superposition mapping. This section gives an extensive and in-depth study on SM-EPA and try to reveal its strength as well as its limits.

#### 3.3.1 Overview

For equal power allocation, the chip amplitudes are all identical. That is

$$\alpha_i = \alpha_j \quad \forall \quad 1 \leqslant i, j \leqslant N \ . \tag{3.9}$$

Consequently, one may use a single  $\alpha \in \mathbb{R}$  to denote the chip amplitudes. The mapping rule of SM-EPA can be written as

$$\phi_{\text{SM-EPA}}(\mathbf{b}) = \alpha \sum_{n=1}^{N} (1 - 2b_n) , \quad \mathbf{b} \in \mathbb{F}_2^N , \qquad (3.10)$$

where  $\alpha$  is chosen to satisfy  $E_{\phi_{\text{SM-EPA}}} = E_s$ , or equivalently  $\alpha^2 N = E_s$ . Hence, to have  $E_s = 1$ , the amplitude coefficient should be chosen as  $\alpha = \sqrt{1/N}$ . Nevertheless, in order to achieve simple expressions, we often take  $\alpha = 1$ , i.e.,  $E\{x^2\} = N$ , for the purpose of illustration, while  $\alpha = \sqrt{1/N}$  for the purpose of performance assessment.

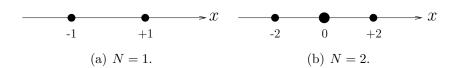

In the simplest case, N=1, SM-EPA is merely a BPSK mapper, with a symbol alphabet consisting of two distinct values, depicted in Fig. 3.4(a). In this scenario, SM-EPA is bijective and all constellation points are equiprobable. Increasing the bit load from 1 to 2, the property of the mapper shows a significant change. Depicted in Fig. 3.4(b), the cardinality of the symbol alphabet at N=2 is 3 instead of  $2^N=4$ , and the probability of x=0 is twice that of  $x=\pm 2$ . The constellation points are equipposed but no longer equiprobable, which gives a big difference to conventional mapping schemes.

As a matter of fact, for  $N \ge 2$ , SM-EPA will be always non-bijective, i.e., having a many-to-one correspondence between the bit tuples and output symbols. For example, given N=4, the mapping rule will be given by Tab. 3.1, which is indeed very interesting. It can be seen that bit tuples with the same amount of 0's or 1's are always mapped onto the same symbol value, or in other words the permutation of 0's and 1's does not make any difference in the mapping result. Particularly, the bit tuples corresponding to x=0 are typical sequences of Bernoulli( $\frac{1}{2}$ ) distribution. Given independently and uniformly distributed (i.u.d.) input bits, this mapping mechanism resembles very much source coding. In source coding, the most frequently occurring message is encoded with the shortest code word, such that the average code word length is minimized, while in superposition mapping, the most frequently occurring set of bit tuples is mapped onto the least-energy symbol value, which minimizes the average energy of symbol transmission. Nevertheless, due to a many-to-one correspondence between bit tuples and symbols, information loss happens during this mapping procedure. Hence, SM-EPA works as if a lossy source encoder.

Back for 20 years, researchers might consider such a mapper as catastrophic, as ambiguity-free detection is not possible even over a noiseless channel. Nevertheless, with modern results on coded modulation, one will find that this is a mapper that Shannon would applaud, since it fulfills the requirement for approaching Gaussian channel capacity.

Figure 3.4: Symbol alphabets of SM-EPA,  $\alpha = 1$ .

| $b_1, b_2, b_3, b_4$ | $c_1, c_2, c_3, c_4$ | $x = \sum_{n=1}^{4} c_n$ |

|----------------------|----------------------|--------------------------|

| 1111                 | -1 $-1$ $-1$ $-1$    | -4                       |

| 0 1 1 1              | +1 $-1$ $-1$ $-1$    |                          |

| 1011                 | -1 + 1 - 1 - 1       | -2                       |

| 1101                 | -1 $-1$ $+1$ $-1$    | -2                       |

| 1110                 | -1 $-1$ $-1$ $+1$    |                          |

| 0 0 1 1              | +1 +1 -1 -1          |                          |

| 0 1 0 1              | +1 $-1$ $+1$ $-1$    |                          |

| 0 1 1 0              | +1 $-1$ $-1$ $+1$    | 0                        |

| 1001                 | -1 + 1 + 1 - 1       | U                        |

| 1010                 | -1 + 1 - 1 + 1       |                          |

| 1100                 | -1 $-1$ $+1$ $+1$    |                          |

| 0 0 0 1              | +1 +1 +1 -1          |                          |

| 0 0 1 0              | +1 +1 -1 +1          | 1.9                      |

| 0 1 0 0              | +1 -1 +1 +1          | +2                       |

| 1000                 | -1 + 1 + 1 + 1       |                          |

| 0 0 0 0              | +1 +1 +1 +1          | +4                       |

Table 3.1: Mapping rule of SM-EPA,  $N=4,\,\alpha=1.$

### 3.3.2 Symbol Distribution

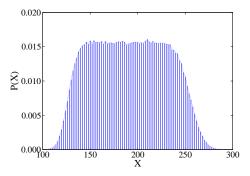

Given equal power allocation (EPA), superimposed chips all have identical distribution. Consequently, an SM-EPA symbol, which is the summation of N i.i.d. chips, will have a Gaussian-like distribution as long as N is sufficiently large. To offer a solid understanding, this section provides a detailed survey of the symbol distribution of SM-EPA.

Revisiting (3.1), it is easy to find that an SM-EPA symbol is formed as

$$x = \alpha \sum_{n=1}^{N} d_n , \quad d_n \in \{\pm 1\} .$$

(3.11)

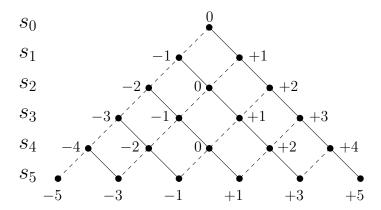

As a matter of fact, the resulting symbol alphabet  $\mathcal{X}$  grows (w.r.t. N) in an interesting way, demonstrated in Tab. 3.2. There is a simple relationship between the bit load and the symbol cardinality:

$$|\mathcal{X}| = N + 1. \tag{3.12}$$

Hence, the symbol cardinality increases linearly with the bit load, instead of exponentially. This property is very helpful in reducing the demapping complexity, as explained in Sec. 5.2.2. Besides, it can be seen from Tab. 3.2 that the symbol alphabet of SM-EPA

| N | $\mathcal{X}$          | $ \mathcal{X} $ |

|---|------------------------|-----------------|

| 1 | -1, +1                 | 2               |

| 2 | -2, 0, +2              | 3               |

| 3 | -3, -1, +1, +3         | 4               |

| 4 | -4, -2, 0, +2, +4      | 5               |

| 5 | -5, -3, -1, +1, +3, +5 | 6               |

Table 3.2: Symbol alphabets of SM-EPA,  $\alpha = 1$ .

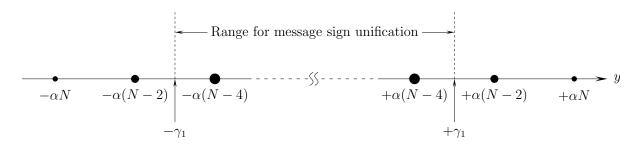

can be written as

$$\mathcal{X} = \{-\alpha N, -\alpha(N-2), \dots, \alpha(N-2), \alpha N\}. \tag{3.13}$$

Let  $\chi_i$  denote these possible symbol values in an ascending order, one attains

$$\chi_i = -\alpha(N - 2i) , \quad 0 \leqslant i \leqslant N , \tag{3.14}$$

where the subscript i actually also gives the number of 0's in the corresponding bit tuples, cf. Tab. 3.1. Given that the input bits are i.i.d., an SM-EPA symbol conforms to a binomial distribution  $\mathcal{B}(N, p)$ :

$$P(x = \chi_i) = \binom{N}{i} (1 - p)^i p^{N-i} , \qquad (3.15)$$

where p is the probability of each bit to be 1 and

$$\binom{N}{i} = \frac{N!}{i!(N-i)!} \tag{3.16}$$

is the binomial coefficient. In the field of digital communication, it is a common practice to make code bits uniformly distributed, e.g., via scrambling. Whenever this is the case, one has p = 1/2 and

$$P(x = \chi_i) = {\binom{N}{i}} (1/2)^i (1/2)^{N-i} = {\binom{N}{i}} / 2^N .$$

(3.17)

In this case, the skew of the distribution is zero, i.e., the distribution is symmetric w.r.t. the mean of x. If N is large enough, an excellent approximation to P(x) is given by a normal distribution with a suitable continuity correction [44].

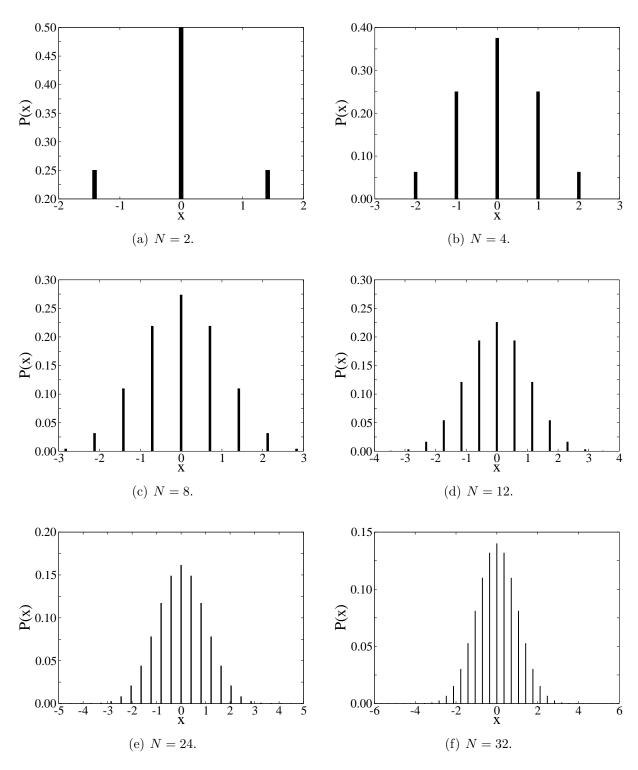

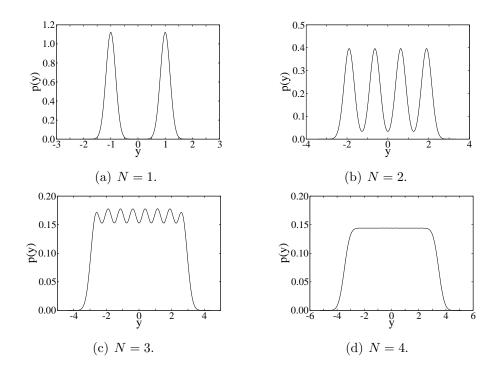

Fig. 3.5 plots the symbol distribution of SM-EPA for various bit loads. As N increases, the envelope of P(x) first becomes triangular-like and then Gaussian-like. Note that, all constellation points are equispaced, and the gap between neighboring points is given by  $2\alpha$ . For a fixed energy per symbol, the chip amplitude  $\alpha$  is inversely proportional to the square root of the bit load:

$$\alpha \propto \frac{1}{\sqrt{N}}$$

, (3.18)

Figure 3.5: Symbol distributions of SM-EPA,  $E_s = 1$ ,  $\alpha = \sqrt{1/N}$ .

| N  | $ \mathcal{X} $ | H(x)        | H(x)/N |

|----|-----------------|-------------|--------|

| 1  | 2               | 1.0000 bits | 1.0000 |

| 2  | 3               | 1.5000 bits | 0.7500 |

| 4  | 5               | 2.0306 bits | 0.5077 |

| 8  | 9               | 2.5442 bits | 0.3180 |

| 12 | 13              | 2.8385 bits | 0.2365 |

| 16 | 17              | 3.0465 bits | 0.1904 |

| 24 | 25              | 3.3393 bits | 0.1391 |

| 32 | 33              | 3.5470 bits | 0.1108 |

| 64 | 65              | 4.0471 bits | 0.0632 |

Table 3.3: Symbol entropies and compression rates of SM-EPA.

which leads to

$$\alpha \to 0 \quad \text{for } N \to \infty \ .$$

(3.19)

Hence, as N tends to be infinity, P(x) asymptotically approaches a continuous Gaussian distribution, which is very desirable from an information theoretical point of view.

#### 3.3.3 Symbol Entropy

Due to the nonuniform distribution, the symbol entropy of SM-EPA will generally be less than the bit load. Without loss of generality, one may call H(x)/N the compression rate of a superposition mapper, as N independent code bits are compressed into a symbol carrying H(x) bits of information. As introduced in Section 3.2, this compression rate tightly upper bounds the coding rate for error-free transmission over noiseless channels.

Follow the definition of entropy [2] and revisit (3.17), we obtain

$$H(x) = -\sum_{x \in \mathcal{X}} P(x) \log P(x) = -\sum_{i=0}^{N} \frac{\binom{N}{i}}{2^{N}} \log_2 \frac{\binom{N}{i}}{2^{N}} \text{ bits }.$$

(3.20)

Tab. 3.3 lists the symbol entropies as well as the compression rates for some N. It can be seen that the symbol entropy grows slower and slower as the bit load increases. As a consequence, the compression rate decreases with N, which also means that the maximum permissible coding rate decreases with N (since  $R \leq H(x)/N$  according to (3.7)). The reason of this phenomenon is that when N goes up the size of the typical sequence set for each symbol value gets larger, which in turn introduces more information loss or in other words more compression.

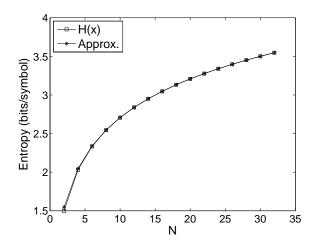

Figure 3.6: Symbol entropy of SM-EPA vs. bit load N.

Equation (3.20) is mathematically strict but does not give any intuition on the relationship between H(x) and N. According to probability theory [45, 46], a binomial distribution  $\mathcal{B}(N, \frac{1}{2})$  can be well approximated by a Gaussian distribution p(u) with the same mean and variance for  $N \geq 5$ , given that a proper continuity correction [47] is done. It is clear that x is zero-mean and its variance is given by

$$E\{x^{2}\} = \sum_{n=1}^{N} \alpha^{2} E\{d_{n}^{2}\} = \sum_{n=1}^{N} \alpha^{2} = \alpha^{2} N.$$

(3.21)

Note that the distance between neighboring constellation points is always  $2\alpha$ . Then for large N we have the following approximation

$$P(x) \approx \int_{x-\alpha}^{x+\alpha} p(u) \, du = \int_{x-\alpha}^{x+\alpha} \frac{1}{\sqrt{2\pi\sigma_u^2}} e^{-u^2/(2\sigma_u^2)} \, du$$

(3.22)

with

$$\sigma_u^2 = \alpha^2 N \ . \tag{3.23}$$

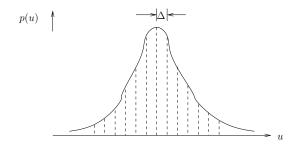

Without loss of generality, x might be considered as a linear quantization of a Gaussian variable u. Correspondingly, the quantization bin size is given by  $\Delta = 2\alpha$ . Using formula (C.10) provided in Appendix C.3, we have

$$H(x) \approx \frac{1}{2}\log(2\pi e\sigma_u^2/\Delta^2) = \frac{1}{2}\log(2\pi e\alpha^2 N/(4\alpha^2)) = \frac{1}{2}\log(\frac{\pi}{2}eN)$$

, (3.24)

i.e.,  $H(x) \approx h(\mathcal{N}(0, N/4))$ . As a matter of fact,  $\frac{1}{2} \log(\frac{\pi}{2}eN)$  already gives a very good approximation for H(x) even when N is not so large, depicted in Fig. 3.6, where "Approx." stands for the approximation under concern<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>This topic already attracts interest in the 1970's [35]. Later on, Hughes *et al.* proposed in [36] a simplified mathematical derivation by utilizing the relationship between the entropy of a continuous variable and the discrete entropy of its quantization [2]. An interesting study on a precise asymptotic approximation of the entropy of binomial distribution can be found in [48].

Figure 3.7: Mutual information over the AWGN channel.

Given the above derivation, it is now clear that the symbol entropy H(x) of SM-EPA is approximately logarithmic w.r.t. the bit load N. This explains the decrease of compression rate H(x)/N when increasing N. As listed in Tab. 3.3, by choosing N=32 the amount of information that one SM-EPA symbol can carry is merely 3.5470 bits, which indicates that SM-EPA is inefficient in supporting very high bandwidth efficiencies.

#### 3.3.4 Mutual Information

The maximum throughput of a channel is given by the mutual information (MI) between its input and output. For the AWGN channel we have

$$I(x; y) = h(y) - h(y|x) = h(y) - h(z)$$

.

Given a power constraint, h(y) is maximized when y conforms to a Gaussian distribution. Hence, whether a mapping scheme is capacity-achieving or not is determined by whether the corresponding channel output distribution is Gaussian or not.

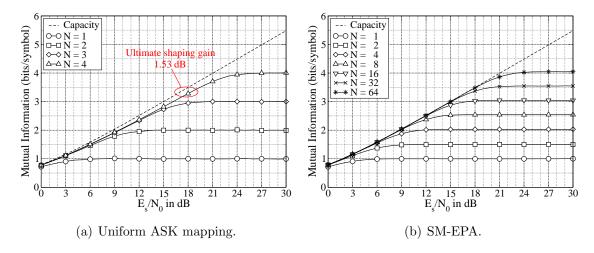

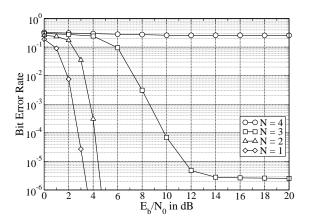

It is well-known that conventional uniform ASK mapping is not capacity-achieving at high SNRs. As illustrated in Fig. 3.7(a), there is a gap of about 1.53 dB between the MI curves of ASK and the channel capacity curve. In the terminology of signal shaping, this gap is often referred to as the ultimate shaping gain, as this is the maximum possible gain that signal shaping can yield w.r.t. uniform ASK mapping. Fig. 3.8 gives a good explanation for the MI performance of ASK. One sees that the channel output distribution does not become Gaussian for uniform ASK with large bit loads.

As introduced in Section 3.3.2, the symbol distribution of SM-EPA tends to have a Gaussian-like envelope as the bit load increases. Naturally, one expects a better performance from SM-EPA than that from uniform ASK. Demonstrated by Fig. 3.7(b),

Figure 3.8: AWGN channel output distribution for uniform ASK,  $E_s/N_0=12~\mathrm{dB}.$

Figure 3.9: AWGN channel output distribution for SM-EPA,  $E_s/N_0=12~\mathrm{dB}.$

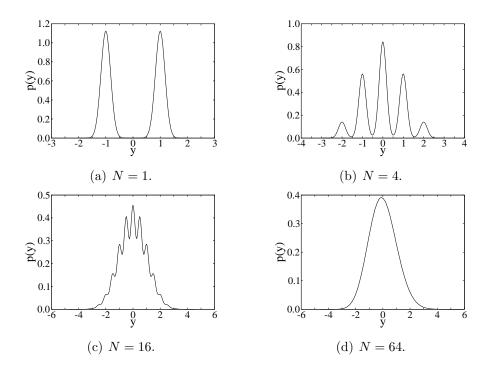

SM-EPA is indeed capacity-achieving. For example, given N = 64, the MI curve of SM-EPA sticks with the capacity curve till  $E_s/N_0 \approx 18$  dB. It is not difficult to imagine that SM-EPA can be capacity-achieving at arbitrarily large SNRs as long as the bit load is large enough. Fig. 3.9 illustrates the channel output distribution for SM-EPA. What we see is that for SM-EPA with large bit loads the distribution of the continuous additive noise smoothes out the gaps between the discrete symbol values of SM-EPA.

## 3.4 Unequal Power Allocation (UPA)

In the previous section, superposition mapping with equal power allocation has been thoroughly studied. It has been shown that the symbol distribution of SM-EPA is Gaussian-like and consequently is capacity-achieving for Gaussian channels. In this section, another important class of power allocation strategy will be investigated, namely unequal power allocation (UPA). This type of power allocation strategy can not really demonstrate the main merits of superposition mapping but deserves interest for academic study. It will be shown that SM-UPA shows a significantly different behaviour compared to SM-EPA, both w.r.t. the symbol property and the achievable power/bandwidth efficiency.

#### 3.4.1 The Exponential Law

Though there are virtually unlimited possibilities for unequal power allocation, the most meaningful choice is the exponential law both for practice and theoretical study. Mathematically, an exponential power allocation strategy can be described as

$$x = \sum_{n=1}^{N} c_n = \sum_{n=1}^{N} \alpha_n d_n , \qquad d_n \in \{\pm 1\} , \qquad (3.25)$$

with

$$\alpha_n = a \cdot \rho^{n-1} , \quad 0 < \rho < 1 , \qquad (3.26)$$

where  $\rho$  is the exponential base, and the value of a should be such that  $\mathrm{E}\{x^2\} = E_s$  is fulfilled. Note that the power of the (n+1)-th chip is always  $\rho^2$  of that of the n-th chip.

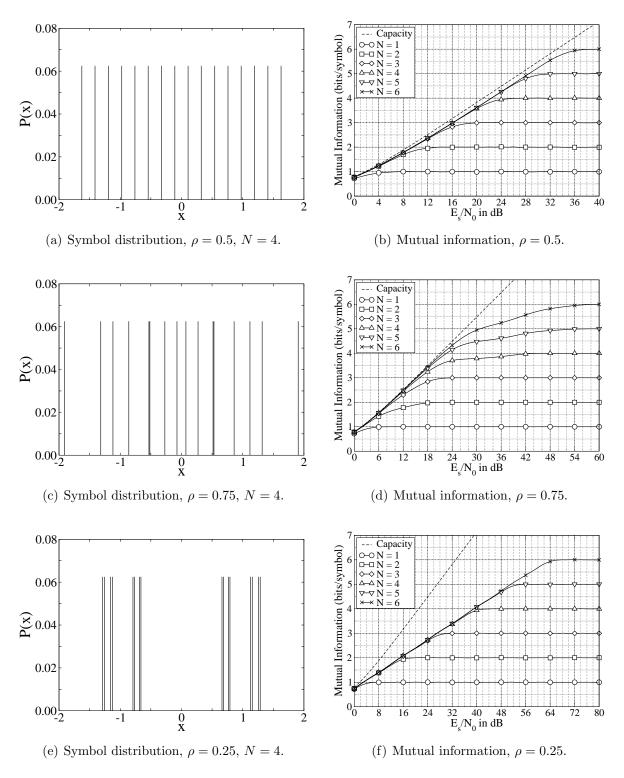

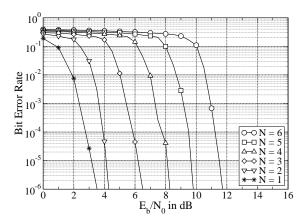

Let us first consider the case that  $\rho = 0.5$ . Given this exponential base, the power of the (n+1)-th chip will be exactly a quarter of the n-th chip. The corresponding SM-UPA is actually bijective and uniform, regardless of the bit load. Shown in Fig. 3.10(a), the symbol cardinality is exactly given by  $2^N$ , and the symbol distribution is uniform. As a result, the respective mutual information (MI) curves are apart from the capacity curve for

Figure 3.10: Symbol distribution and mutual information of SM-UPA.

about 1.53 dB in the linear section, depicted in Fig. 3.10(b). Comparing Fig. 3.10(b) with Fig. 3.7(a), one recognizes that the MI performance of SM-UPA in this case is identical to that of uniform ASK. A nice feature is that the supportable bandwidth efficiency, given by the top position of the MI curves, is linear in the bit load, while an obvious drawback is that the mapping scheme is not capacity-achieving, just like the case of uniform ASK mapping. Hence, the SM scheme under consideration does not show any advantage over conventional uniform ASK mapping but also no disadvantage, from an information theoretical point of view. To be elaborated in Section 3.4.2, SM-UPA with  $\rho = 0.5$  exactly emulates a uniform ASK with natural labeling.

For most bases  $\rho \neq 0.5$ , the symbol distribution of SM-UPA is still probabilistically uniform but the constellation points will no longer be equispaced. For  $0.5 < \rho < 1$ , the density of constellation points in the region close to zero is higher than that in the region far from zero, depicted in Fig. 3.10(c). Consequently, the capacity-achieving SNR range is wider than that of  $\rho = 0.5$ , cf. Fig. 3.10(d). However, for  $N \geq 4$  the MI curves shows a strange shape in the middle section. Note that in Fig. 3.10(c) there are two pairs of constellation points being very close to each other around  $\pm 0.5$ , which explains the transition behaviour of the MI curves from low SNR to high SNR. When one chooses  $0 < \rho < 0.5$ , the symbol property of SM-UPA becomes rather undesirable. As demonstrated by Fig. 3.10(e), the constellation points are level-wise polarized by relatively strong chips, and the minimum distance between constellation points is rather small for high bit loads. This feature is clearly unfavorable for the receiver algorithm. Besides, the symbol distribution is geometrically nonuniform, however, developing in a trend that being more and more non-Gaussian, which is adverse for the MI performance, cf. Fig. 3.10(f).

In general, non-equispaced constellation presents a troublesome issue for the front-end circuits which likely introduce certain nonlinear distortion. To improve the MI property of SM in the linear section, one should choose equal power allocation instead of UPA with  $0.5 < \rho < 1$ , from a practical point of view. Therefore, among all the possibilities for  $\rho$ , 0.5 is a distinguished choice for SM-UPA. In the rest of this thesis, an exponential law with  $\rho = 0.5$  will always be assumed for SM-UPA, if not explicitly stated otherwise.

#### 3.4.2 Mapping and Labeling

Given the exponential law with  $\rho = 0.5$ , the mapping rule of SM-UPA

$$\phi_{\text{SM-UPA}}(\mathbf{b}) = a \sum_{n=1}^{N} \rho^{n-1} (1 - 2b_n) , \quad \mathbf{b} \in \mathbb{F}_2^N ,$$

(3.27)

will always be bijective. Hence, no information loss will occur during the mapping proce-

| N | $ \mathcal{X} $ | H(x)     | H(x)/N |  |

|---|-----------------|----------|--------|--|

| 1 | 2               | 1.0 bits | 1.0    |  |

| 2 | 4               | 2.0 bits | 1.0    |  |

| 3 | 8               | 3.0 bits | 1.0    |  |

| 4 | 16              | 4.0 bits | 1.0    |  |

| 5 | 32              | 5.0 bits | 1.0    |  |

| 6 | 64              | 6.0 bits | 1.0    |  |

Table 3.4: Symbol entropies and compression rates of SM-UPA,  $\rho = 0.5$ .

| $b_0, b_1, b_2, b_3$ | $c_0, c_1, c_2, c_3$       | $x = \sum_{n=1}^{4} c_n$ |

|----------------------|----------------------------|--------------------------|

| 0 0 0 0              | +1 +0.5 +0.25 +0.125       | +1.875                   |

| 0 0 0 1              | +1 +0.5 +0.25 -0.125       | +1.625                   |

| 0 0 1 0              | +1 +0.5 -0.25 +0.125       | +1.375                   |

| 0 0 1 1              | +1 +0.5 -0.25 -0.125       | +1.125                   |

| 0 1 0 0              | +1 $-0.5$ $+0.25$ $+0.125$ | +0.875                   |

| 0 1 0 1              | +1 -0.5 +0.25 -0.125       | +0.625                   |

| 0 1 1 0              | +1 -0.5 -0.25 +0.125       | +0.375                   |

| 0 1 1 1              | +1 $-0.5$ $-0.25$ $-0.125$ | +0.125                   |

| 1000                 | -1 +0.5 +0.25 +0.125       | -0.125                   |

| 1001                 | -1 +0.5 +0.25 -0.125       | -0.375                   |

| 1010                 | -1 +0.5 -0.25 +0.125       | -0.625                   |

| 1011                 | -1 +0.5 -0.25 -0.125       | -0.875                   |

| 1100                 | -1 $-0.5$ $+0.25$ $+0.125$ | -1.125                   |

| 1 1 0 1              | -1 $-0.5$ $+0.25$ $-0.125$ | -1.375                   |

| 1110                 | -1 $-0.5$ $-0.25$ $+0.125$ | -1.625                   |

| 1111                 | -1 $-0.5$ $-0.25$ $-0.125$ | -1.875                   |

Table 3.5: Mapping rule of SM-UPA,  $N=4, a=1, \rho=0.5.$

dure, and sequentially the compression rate of SM-UPA will always be equal to 1, as listed in Tab. 3.4. For this reason, error-free transmission is also possible for uncoded SM-UPA, which gives a big difference w.r.t. SM-EPA. Tab. 3.5 elaborates the mapping rule of SM-UPA with N=4. One may recognize that this mapping rule is exactly the same as that of uniform 16-ASK mapping with natural labeling. Certainly, the resulting performance will also be identical to that of 16-ASK with natural labeling. Therefore, conventional uniform ASK mapping can easily be emulated by SM-UPA, as long as natural labeling is desired, which brings a practical benefit that one may use a tree-based BCJR [49] algorithm to reduce the detection complexity, as introduced in the next chapter.

## 3.5 Grouped Power Allocation (GPA)

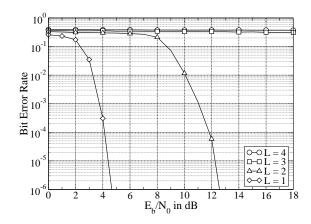

In Section 3.3, we have seen that superposition mapping with equal power allocation delivers a Gaussian-like symbol distribution, which brings a capacity-achieving power efficiency, but suffers from a logarithmically growing symbol entropy w.r.t. the bit load, which significantly limits the supportable bandwidth efficiency for a reasonable computational complexity. On the other hand, superposition mapping with unequal power allocation offers a linearly growing symbol entropy w.r.t. the bit load, which brings a virtually unlimited supportable bandwidth efficiency, but suffers from a geometrically and probabilistically uniform symbol distribution, which eliminates the possibility to achieve the Gaussian channel capacity, as described in Section 3.4. Therefore, both equal power allocation and unequal power allocation have their pros and cons. In short, equal power allocation is beneficial for power efficiency, while unequal power allocation is beneficial for bandwidth efficiency.

Today's communication systems demand high power efficiency and high bandwidth efficiency simultaneously. Meanwhile, the computational complexity is still a critical concern for the reason of hardware cost and electricity consumption. Therefore, it is of great practical interest to design a power allocation strategy for superposition mapping, such that high power and bandwidth efficiency can be achieved simultaneously at an affordable computational complexity. In this section, a grouped power allocation (GPA) scheme is proposed, which is a hybrid of equal and unequal power allocation strategy. GPA shows the merits of EPA and UPA, while considerably eliminates the problems from both.

#### 3.5.1 Basic Idea

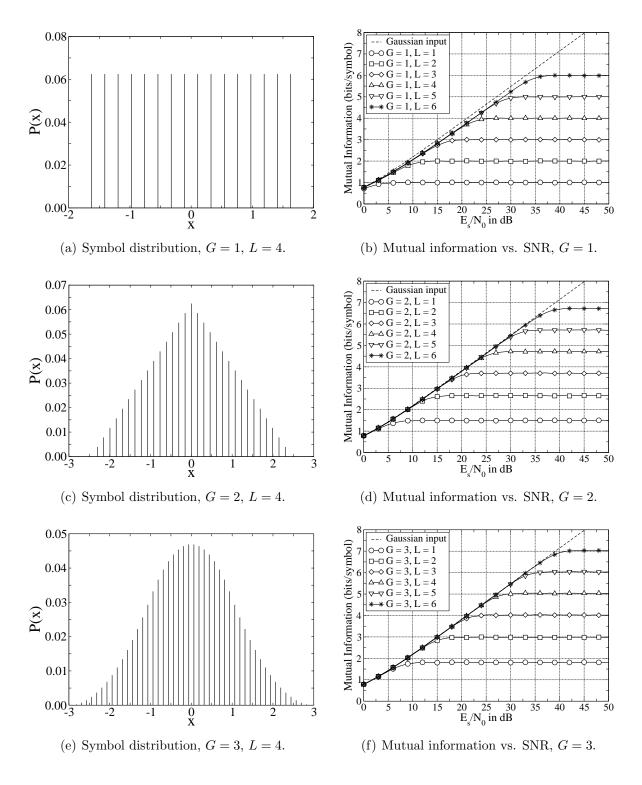

From Fig. 3.5 one observes that equal power allocation helps to build up a Gaussian-like symbol distribution, while from Fig. 3.10 one sees that unequal power allocation helps to increase the symbol cardinality. Following this observation, we may construct a hybrid power allocation strategy such that superimposed chips are divided into several groups with each group assigned a different power level and chips within each group assigned an identical power level. Given a sufficiently large group size, the summation of chips within each individual group will have a Gaussian-like distribution, and consequently the summation of multiple groups will also have a Gaussian-like distribution. Meanwhile, due to the existence of multiple power levels, the symbol cardinality will be enlarged and thus the supportable bandwidth efficiency will be improved, comparing to the case of SM-EPA.

The above idea can be formulated as follows:

$$x = \sum_{l=1}^{L} \alpha_l \sum_{g=1}^{G} d_{l,g} , \qquad d_{l,g} \in \{\pm 1\} , \qquad (3.28)$$

where L gives the number of power levels and G gives the group size. Clearly,  $N = L \cdot G$  defines the total amount of chips per symbol, i.e., the bit load.  $\alpha_l$  is the amplitude coefficient of the l-th power level, which is defined as

$$\alpha_l \doteq a \ 2^{-(l-1)}$$

(3.29)

with the value of a chosen to fulfill  $E\{x^2\} = E_s$ . Note that the base of exponential has been carefully chosen to be 2. The reason of this choice is obvious when one observes the elegant symbol distribution resulting from this power allocation strategy.

#### 3.5.2 Symbol Distribution & Mutual Information