# nature portfolio

### **Peer Review File**

**Open Access** This file is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to

the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. In the cases where the authors are anonymous, such as is the case for the reports of anonymous peer reviewers, author attribution should be to 'Anonymous Referee' followed by a clear attribution to the source work. The images or other third party material in this file are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <u>http://creativecommons.org/licenses/by/4.0/</u>.

#### **REVIEWER COMMENTS**

Reviewer #1 (Remarks to the Author):

This is a very good manuscript in the field of 2D-materials-based electronic devices for multiple reasons that are very clear to see. First of all, the authors fabricate small devices of 1um2, and they present data from many devices (>160). Moreover, they do cross-sectional TEM to prove the structure of the device, and they do advanced electrical characterization (i.e., very few articles measure so short switching times). The conclusions are interesting and, more important, solidly proved.

However, there are several points that could be improved:

1 – Figure 2a gives bad impression. I would replace it by something like Figure S7a an then mention in the text that 8% of the devices were discarded because showed low resistance.

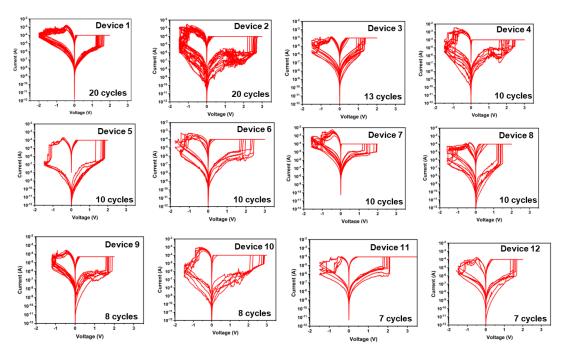

2 – Figure 2b is nice, but I'd like to see that for many devices. If not 160, then select the best 40-50 ones and put them together in the supporting information, indicating the number of cycles measured for each one. Similar to supplementary figure 20 of this paper: https://www.nature.com/articles/s41928-020-00473-w

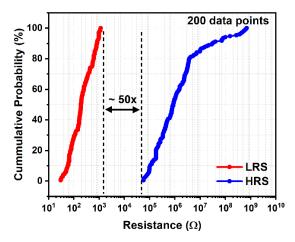

3 – Figure 3c is a bit misleading, should give the ratio from the most-right red symbol to the most-left blue symbol, like in Figure 2d of this paper: https://www.nature.com/articles/s41928-020-00473-w

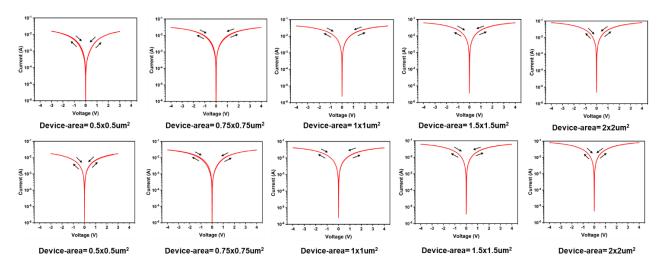

4 – I would like to see in the article the characteristics (fresh I-V curves) of 5-10 devices without the h-BN, to prove that what they are showing is not produced by the Ti film (which sometimes can easily form TiO2 and show RS even without an insulating layer).

5 – Regarding the switching mechanism, it is fine for me and properly demonstrated. I would say that the authors could include the EELS data in Figure 2 to make it more powerful. Also, the authors should comment on the recent article demonstrating that non-filamentary RS in h-BN is possible (see https://www.nature.com/articles/s41586-023-05973-1)

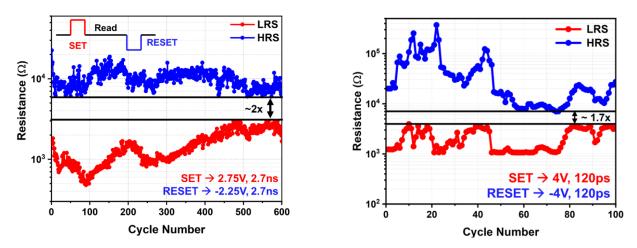

6 – In the pulsed voltage stresses they should show at least one entire read/write/read/erase/read cycle, so that it can be confirmed that it switches well with cycles. Something like Extended Data Figure 8 in the paper https://www.nature.com/articles/s41586-023-05973-1

7 – The authors should discuss why the endurance is so low. They may show SEM images after the stresses, to see what happens. I guess the wires will melt because the currents are high. Please comment. In fact, I think they could reach higher endurance changing the design of the masks. There is no need to make such long narrow lines, one can reduce the width progressively from the pad as one approaches to the Crosspoint section. This reduces current density and slows down electromigration.

8 – I wonder why the authors don't make TEM image wish higher resolution to see more clearly the structure of the devices. It would be good if they can provide something like in this paper: https://www.nature.com/articles/s41699-022-00341-5

I think that, after these minor revisions, the article should be published because it advances the state-of-the-art in this field.

Reviewer #2 (Remarks to the Author):

This paper presents a study on hBN-based memristors that exhibit an ultra-fast response of 120 ps. To investigate the memristor switching mechanism, the authors employed statistical analysis. The work includes a comprehensive analysis of the hBN memristor model, covering filament growth, joule heating effect, and the correlation between switching energy and switching ratio. In addition, they conducted endurance measurements with ultra-fast pulses and employed statistical analysis to demonstrate the device's potential for high-frequency applications. Despite the potential significance of the work, the novelty and contribution are inadequately described and do not meet the publication standards of Nature Communications. The detailed reasons are listed below:

Major issues:

1. In the introduction, the authors noted that there has been relatively little attention devoted to studying the switching dynamics of memristors. However, numerous studies have explored the dynamic mechanisms in both metal-oxide-based and hBN-based memristors. For instance, TEM has been used to observe the electrochemical dynamics of nanoscale metal conductive filaments in metal-oxide-based memristors, and a model has been established to consider the applied electric field, metal ion diffusion, and filament shape based on dynamic metal cluster nucleation and growth. [1,2] In the case of 2D hBN-based memristors, the dynamic analysis of nano-conductive filaments has also been investigated,

including the effect of temperature. [3,4] Additionally, a Monte Carlo simulation has been shown to simulate filament growth and erase dynamics. [5]

2. In Figure 2a, have the initial currents measured from devices with different areas been plotted together? If not, the authors should clearly state the device area that used in this figure. If initial currents have been plotted together, the authors should include a legend specifying the device area, as this parameter is critical in determining the high-resistance state (HRS) initial current. A similar issue is observed in Supplementary Figure 7a, where the authors plot the correlation between the forming voltage and the initial current. In this case, the authors should keep the device area constant.

3. In Fig. 2d, the device cycle-to-cycle variation is much higher than other hBN-based memristors.[6] The range of set voltages is wide, spanning from 1 to 3 V, creating significant difficulties in selecting memristor devices for cross bar arrays. Furthermore, device-to-device variation exacerbates this issue. To understand the cause of this considerable variation, the authors should conduct further analysis.

4. In the study on dynamic filament formation (see Fig. 4 and Supplementary Fig. 10), the authors employed a conventional model that takes into account the effects of temperature, the heat equation, and the Arrhenius relationship for filament growth. It should be noted, however, that this model was originally developed for oxide memristors. [7,8] As such, it is unclear how the model in this work differs from the one used for metal oxide, and how it specifically contributes to understanding the filament growth dynamics in hBN.

5. The authors need to provide a clear explanation of the fundamental reason for the ultra-fast switching behavior observed in their memristor, as compared to other fast-switching memristors discussed in previous studies.[9,10] To achieve this, the authors should provide a detailed explanation in terms of their model and material properties.

6. It would be beneficial if the authors could compare the fitted filament diameter obtained from their model with experimental results obtained from techniques such as C-AFM or HRTEM, which can directly measure the filament diameter.

7. The authors should discuss more metrics or guidelines for measuring the pulse characteristics of their memristor. In Figures 4 and 5, the authors have presented statistical analysis of the transient pulse response and established correlations between switching ratio, switching time, and switching energy. It shows that the switching energy and switching time is highly related to the switching ratio before/after pulse. To better understand the performance of their ultra-fast switching device, the authors should discuss key performance metrics for fast-switching devices and the differences between normal

endurance (with pulse widths of tens of microseconds) and ultra-fast pulse endurance (with subnanosecond pulses).

8. The authors demonstrate 600-cycle endurance with ultra-fast pulses, which is higher than other fast memristors' endurance results. However, it is important to note that other memristors can achieve endurance up to 108 cycles with pulse widths of microseconds. Therefore, to prove the stability of their device, the authors should provide endurance results with a higher cycle number.

#### Minor issues:

1. There are some typos in the manuscript. (Line 81, the SET should be transition to lower resistance instead of lower conductance)

2. The image quality is poor in the manuscript, some of the images cannot be viewed clearly. (Figure 2g, 2h)

3. Scale bar labeling is confusing. In Supplementary Fig. 3a, the sample electrode width seems to be larger than 2 um. However, the maximum electrode width is 2 um in this work.

#### **References list:**

[1] Y. Yang, P. Gao, L. Li, X. Pan, S. Tappertzhofen, S. Choi, R. Waser, I. Valov, W. D. Lu, Nat. Commun. 2014, 5, 1.

[2] Y. Yang, P. Gao, S. Gaba, T. Chang, X. Pan, W. Lu, Nat. Commun. 2012, 3, 1.

[3] M. Lanza, F. Palumbo, Y. Shi, F. Aguirre, S. Boyeras, B. Yuan, E. Yalon, E. Moreno, T. Wu, J. B. Roldan, Adv. Electron. Mater. 2022, 8, 2100580.

[4] K. Zhu, X. Liang, B. Yuan, M. A. Villena, C. Wen, T. Wang, S. Chen, F. Hui, Y. Shi, M. Lanza, ACS Appl. Mater. Interfaces 2019, 11, 37999.

[5] F. Qian, R.-S. Chen, R. Wang, J. Wang, P. Xie, J.-Y. Mao, Z. Lv, S. Ye, J.-Q. Yang, Z. Wang, Y. Zhou, S.-T. Han, IEEE Trans. Electron Devices 2022, 69, 6049.

[6] S. Chen, M. R. Mahmoodi, Y. Shi, C. Mahata, B. Yuan, X. Liang, C. Wen, F. Hui, D. Akinwande, D. B. Strukov, M. Lanza, Nat. Electron. 2020, 3, 638.

[7] P. Huang, X. Y. Liu, B. Chen, H. T. Li, Y. J. Wang, Y. X. Deng, K. L. Wei, L. Zeng, B. Gao, G. Du, X. Zhang, J. F. Kang, IEEE Trans. Electron Devices 2013, 60, 4090.

[8] D. Ielmini, IEEE Trans. Electron Devices 2011, 58, 4309.

[9] B. J. Choi, A. C. Torrezan, K. J. Norris, F. Miao, J. P. Strachan, M.-X. Zhang, D. A. A. Ohlberg, N. P. Kobayashi, J. J. Yang, R. S. Williams, Nano Lett. 2013, 13, 3213.

[10] B. J. Choi, A. C. Torrezan, J. P. Strachan, P. G. Kotula, A. J. Lohn, M. J. Marinella, Z. Li, R. S. Williams, J. J. Yang, Adv. Funct. Mater. 2016, 26, 5290.

Reviewer #3 (Remarks to the Author):

This manuscript demonstrates the first sub-nanosecond switching of a 2D hBN-based memristor. In addition to novel switching data, a compelling thermal model is used to understand the nature of the filament during switching in this material. The statistical analysis of switching over many cycles in 30 devices is uniquely useful. Overall, the methods used in this work are sound and I was particularly happy to see the careful techniques like the control resistor experiment in S-Fig 11. It is well written and on a topic of interest to the community. Previous works are well referenced. I recommend publication after considering a few potential points for improvement:

--It would be useful if the authors could elaborate on the proposed switching mechanism. The implication that a Ti filament is responsible for switching (lines 99-103) a very interesting point, but only briefly mentioned. If cationic motion of Ti is responsible for the filament, perhaps this is a differentiating feature of 2D-based memristors from the traditional TMO memristors which are (typically) thought to be modulated by oxygen vacancy anions. I wonder if the physical insight here is applicable to traditional TMO memristors.

--Supplementary Table 1 is a useful reference comparing switching in standard TMO and 2D memristor. I am wondering if, based on this work, the authors can further comment on fundamental differences between switching in traditional versus 2D materials. I realize there is quite a bit of interest in the novelty of 2D materials, but am wondering if there are fundamental advantages of the 2D stack. My impression from this work and refs in the Table is that that 2D memristors have similar switching speed and energy, but the endurance may be somewhat worse.

--The resistance evolution in Fig 4d does not appear to align with the level described in the text. On lines 154, the initial range is 10k-100kohms, but in Fig 4d, we see the evolution of resistance in a much lower

range, from about 700-1000 to 200 ohms. If the authors have data showing SET switching starting from the higher range, that would be of interest.

--Minor: In general the variables are carefully defined for the model in the supplement, but I would recommend adding definitions for supplementary Eqn 6.

--Minor: The plot text on several figures is too small and hard to read (esp insets).

Reviewer #4 (Remarks to the Author):

The manuscript by Nibhanupudi et. al. represents the memristor device prepared by thin hBN layer and Ti and Au electrodes. Experiments present successful fabrication of device and memristance characterization as well as pulse characteristic including statistical analyses. Theory presents formation of filaments in a thermo-static medium. In my opinion this work is a valuable study in memristor but can not advice it for publication in Nature Communication. There are major list of comments in following

Theory: In my opinion the theoretical model is a valuable work but cannot be accepted as a close model of what happens in experiments. For example, 3 nm filament has very similar thickness to hBN layer. The materials of filament is not clear. There might be a population of filaments at the interface to electrode with different sizes. There is a complicated heat bath (generation and dissipation) that is not argued. What are authors looking for and what consequences are expected with such a model is not clear. Way VCM and TCM are not modeled and only attention is made on filament formation.

Experiment: The is no motivation to accept the reported record of fast switching in this layer as there is not a big change w.r.t. the previous studies. The finding of paper is not clear. What is new? statics? fast switching? thermal and heat model?

Technical points: intro: There is repeated theme of fast electronics or switching application is different paragraphs and there is no focus. There is not a coherent introduction that what are authors plan to present in the paper. experiment: i) a high resolution image of filament formation (for different biases) is lacking, ii) in the calculation of power, since current and thus impedance changes, how authors are sure to have a delivery of power to/from different resistance loads? Could part of power be reflected? What are high risk points that might not be considered?

Ultra-fast switching memristors based on two-dimensional materials

#### Author response to reviewer comments

Firstly, we would like to thank all the reviewers for taking the time to review and provide valuable feedback to improve the quality of our manuscript. We have updated and modified the manuscript to reflect the suggestions. Please see below the detailed point-by-point response for each comment.

#### Reviewer1

Figure 2a gives bad impression. I would replace it by something like Figure S7a and then mention in the text that 8% of the devices were discarded because they showed low resistance.

Thank you for the comment. As suggested, this figure has been moved to Supplementary Information (Fig.7) and we state the device yield (92%) in the main text.

Figure 2b is nice, but I'd like to see that for many devices. If not 160, select the best 40-50 ones and put them together in the supporting information, indicating the number of cycles measured for each. Similar to supplementary figure 20 of this paper: <u>https://www.nature.com/articles/s41928-020-00473-w</u>

Figure R1.1 DC IV characteristics collected from 12 different devices.

As suggested, we included measured DC electrical characterization data with a current compliance limit of 100uA. Although 160 devices were tested for initial resistance measurements, only 30 were tested for DC cycling measurements. The rest were allocated for AC testing, temperature measurements, retention testing, and TEM characterization. Here, we include data collected from 12 devices (Fig.R1.1). This figure has been included as Fig.9 in the supplementary information.

Figure 3c is a bit misleading, it should give the ratio from the most-right red symbol to the most-left blue symbol, like in Figure 2d of this

paper: https://www.nature.com/articles/s41928-020-00473-w

Thank you for the comment. In the original manuscript, we included the ratio between LRS and HRS at the 50% percentile point, as reported in some earlier studies [1-2]. However, we agree with

your comment that this method of reporting the resistance window does not capture the worstcase scenario. Therefore, as suggested, we have updated the figure (Fig.2b main text) with the ratio between the highest LRS resistance and the lowest HRS resistance (Fig.R1.2).

Figure R1.2 Cumulative probability distribution of the resistance in HRS and LRS states extracted from DC sweeps at  $V_{READ}$ =0.1V collected from 200 I-V traces

## I would like to see in the article the characteristics (fresh I-V curves) of 5-10 devices without the h-BN, to prove that what they are showing is not produced by the Ti film (which sometimes can easily form TiO2 and show RS even without an insulating layer).

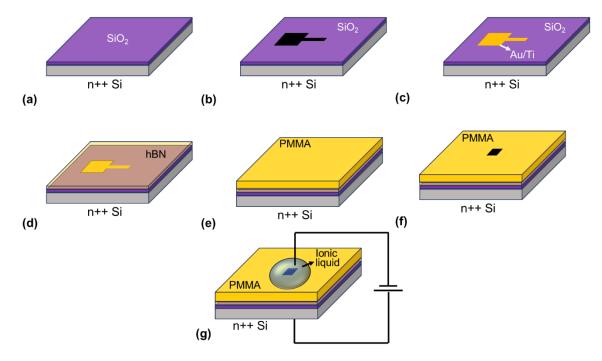

Thank you for the insightful comment. The process flow adopted for fabricating the devices in this study is as follows,

- 1. Pattern and deposit bottom electrode (Au)

- 2. Transfer CVD-grown hBN

- 3. Pattern and deposit top electrode (Ti/Au)

Both top and bottom electrodes are deposited using electron beam evaporation of metals in a vacuum (1e-6 Torr) environment. During the top electrode deposition, Ti and Au are deposited without breaking the vacuum, thus eliminating Ti's exposure to oxygen. Nevertheless, as rightly pointed out, confirming that the resistive switching in our devices does not originate from an inadvertent TiO<sub>2</sub> layer is critical. Therefore, as suggested, we fabricated and measured the memristor devices without the hBN layer.

Fig.R1.3 shows measured data from 10 devices with different cross-sectional areas  $(0.5x0.5um^2 \rightarrow 2x2um^2)$ . All the devices exhibit ohmic conduction with no conceivable memory window. Moreover, the resistance of these devices is very low  $(50\Omega - 180\Omega)$  compared to the devices with hBN (92% of devices with resistance > 1M $\Omega$ ). Therefore, we can ascertain that the resistive switching observed in this study can be attributed to the hBN layer. We have included this figure as Supplementary Fig.8 in the manuscript.

Figure R1.3 DC IV characteristics of Ti/Au devices without the hBN layer. Data collected from devices with varying cross-section areas (500x500nm<sup>2</sup> to 2x2um<sup>2</sup>).

Regarding the switching mechanism, it is fine for me and properly demonstrated. I would say that the authors could include the EELS data in Figure 2 to make it more powerful. Also, the authors should comment on the recent article demonstrating that non-filamentary RS in h-BN is possible (see <u>https://www.nature.com/articles/s41586-023-05973-1</u>)

Thank you for your suggestion to improve the quality of our manuscript. As suggested, we have included the EELS data as Fig.2g in the main text.

The suggested recent article presents interesting results observed in 2D memristors integrated with CMOS transistors. The 1Transistor-1Memristor (1T1M) bitcell exhibited non-filamentary resistive switching with lower transistor  $V_G$  (gate voltage) and filamentary switching with higher transistor  $V_G$ . This shows controllable soft-breakdown in hBN layers facilitated by the current limiting action of the adjoining transistor. On the contrary, the devices in this study have no current limiting device and exhibit filamentary switching confirmed by ohmic behavior in LRS, positive TCR in LRS, and high LRS currents.

We thank the reviewer for providing this helpful reference highlighting the various possible switching mechanisms in 2D hBN. We have included additional text in the manuscript (lines 167-168 main text) commenting on the reported non-filamentary conduction in hBN.

In the pulsed voltage stresses they should show at least one entire read/write/read/erase/read cycle, so that it can be confirmed that it switches well with cycles. Something like Extended Data Figure 8 in the paper - (https://www.nature.com/articles/s41586-023-05973-1)

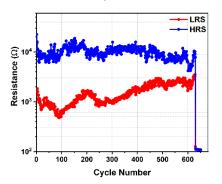

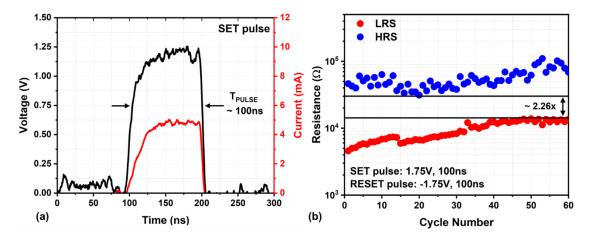

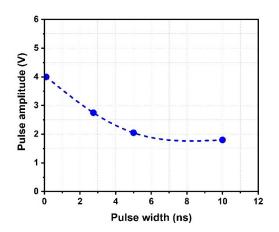

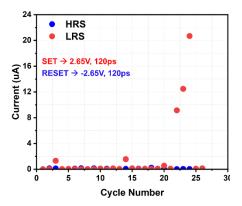

Thank you for the comment. We have conducted extensive cycling studies on the devices (both 7-8 layer and 3-4 layer hBN). Thick hBN devices show consistent switching for 600 cycles (with  $V_{PULSE} \sim 2.75V$ ,  $T_{PUL} \sim 2.7ns$ ), and the thin hBN devices exhibit 100 cycles (with  $V_{PULSE} \sim 4V$ ,  $T_{PUL} \sim 120ps$ ) as seen from Fig.R1.4.

Unfortunately, using our pulse setup, we cannot conduct a measurement similar to Extended Figure 8 of the reference paper. The pulse generator used in this study (PSPL10070A) cannot produce alternating positive and negative pulses in sequence. Therefore, we program the pulse generator every cycle through a computer for the endurance tests. Since the output is measured on a high-frequency scope, two consecutive cycles (separated by milliseconds) cannot be captured due to the limitation of the oscilloscope memory depth (1Gpts).

Figure R1.4 Cycling endurance data for (a) thick devices (7-8 layer hBN) with 2.7ns pulses (b) thin devices (3-4 layer hBN) with 120ps pulses.

The authors should discuss why the endurance is so low. They may show SEM images after the stresses, to see what happens. I guess the wires will melt because the currents are high. Please comment. In fact, I think they could reach higher endurance changing the design of the masks. There is no need to make such long narrow lines, one can reduce the width progressively from the pad as one approaches the Crosspoint section. This reduces current density and slows down electromigration.

We want to answer this question on endurance in the following three sub-sections.

#### Endurance in 2D memristors

The endurance in 2D memristors has always been a concern, mainly attributed to the ultra-thin switching layer. Transition metal oxide (TMO) based memristors typically have a switching layer thickness ranging between 5nm-50nm [3-4]. On the contrary, 2D memristors can be scaled down to even monolayer thickness. The reduced vertical separation between metal electrodes enhances the electric field, which results in reduced control over the metal ion migration into the switching layer and subsequent filament formation. Moreover, as the thickness of the switching layer reduces, the impact of bottom/top electrode roughness plays a significant role in determining the overall device performance. In the following table, we have listed the reported endurance in 2D memristors along with the thickness of the switching layer.

|           | Switching layer stack    | Thickness (nm) | Endurance cycles |

|-----------|--------------------------|----------------|------------------|

| [5]       | Au/hBN/Au                | 0.33           | 50               |

| [6]       | Au/MoS₂/Au               | 0.65           | 20               |

| [7]       | Au/MoS₂/Au               | 0.65           | 150              |

| [8]       | Ag/hBNO <sub>x</sub> /Gr | 0.9            | 100              |

| [9]       | Au/ReSe <sub>2</sub> /Au | 1              | 200              |

| [10]      | Cu/MoS <sub>2</sub> /Au  | 1.4            | 20               |

| [11]      | Ti/hBN/Au                | 2.4            | 100              |

| [12]      | Ti/hBN/Au                | 2.4            | 100              |

| [13]      | Ti/hBN/Ni                | 3.96           | 100              |

| [14]      | Ti/hBN/Au                | 4.3            | 50               |

| [15]      | Ti/hBN/Au                | 4.95           | 250              |

| [16]      | Ti/hBN/Gr                | 5              | 1000             |

| [17]      | Au/MoS <sub>2</sub> /Au  | 5              | 120              |

| [18]      | Au/hBN/Au                | 6              | 50               |

| [19]      | Pd/WS <sub>2</sub> /Pt   | 6.45           | 15               |

| [20]      | Ti/hBN/Au                | 6.6            | 1200             |

| [21]      | Ti/MoTe₂/Au              | 7              | 600              |

| This work | Ti/hBN/Au                | 2.64           | 600              |

| This work | Ti/hBN/Au                | 1.32           | 100              |

From the table, we see that the 2D memristors with switching layer thickness <5nm, typically exhibit <250 cycles endurance. Some memristors [12,16] exhibit about 1000 cycle endurance with >5nm switching layer thickness. In comparison, our devices exhibit on-par or better device performance with 600 cycles for thicker ( $T_{hBN}$ ~ 2.6nm) memristors and 100 for thinner ( $T_{hBN}$ ~ 1.32nm) memristors.

On the other hand, only two research studies report high endurance (~10<sup>7</sup>) using thicker 2D memristors (>10nm) [22-23]. Many studies report low endurance even with thicker memristors [24-26].

Overall, the 2D material based memristor technology is still in the early stages of exploration. The quality of the 2D material (grain size, uniformity, thickness, defect density etc.,) largely determines the device's performance. Superior control over the CVD growth parameters will enable the fabrication of high-quality memristors with enhanced endurance. With several university and industry research groups working in this direction, we believe that 2D material memristors can outperform oxide-based memristors in the near future.

#### Role of Current Compliance (CC)

A recent study [27] (suggested by the reviewer in previous comments) reported high endurance of  $\sim 10^6$  cycles in the 1T1M (1 Transistor – 1 memristor) bitcell with just  $\sim 6.6$ nm thick switching layer. In this study, the standalone devices without CMOS transistors exhibited only 100 cycles, whereas devices with transistors exhibited a million cycles. This promising result suggests that the adjoining selector device can improve endurance in 2D memristor devices.

The characterization setup utilized in this study cannot support external current compliance (CC) for high-frequency pulse testing. For the frequency range studied in this article, the external CC device (resistor, diode or transistor) must be located within <1cm distance from the DUT (device under test) to be considered as a lumped circuit element. Therefore, the only possible option is to have a CC device fabricated monolithically, like in [27]. Without current compliance, most of our devices get shorted during testing, which cannot be recovered. We expect that having a 1T1M configuration would improve the endurance of our devices.

#### Current leads

We thank the reviewer for the insightful comment about electromigration in the current leads. However, the devices in our study predominantly fail by getting short due to excess metal ion migration into the ultra-thin switching layer. These excess metal ions form wide filaments which the RESET pulse cannot dissolve, as seen in Fig.R1.5. A similar failure mechanism has also been observed with the DC characterization of the devices. The resistance in this state is <100 $\Omega$ , which is the range for contact resistance contributed by the current leads.

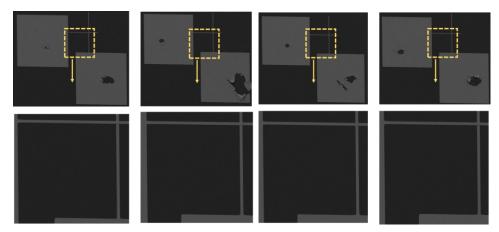

Figure R1.5 Devices fail by getting shorted after repeated cycling

Electromigration in current leads would have resulted in devices failing in open circuits with high associated resistance. Our devices have bottom and top electrode thicknesses ~70nm, which should lower the probability of electromigration. However, as suggested, we imaged the devices using SEM after stressing the devices with voltage pulses. Fig.R1.6 shows SEM images collected from 4 different devices. The skid marks from the probe landing can be seen on the contact pads. The current leads remain intact without any conceivable electromigration damage.

Figure R1.6 Scanning electron microscope images of the devices after pulse characterization. Skid marks from probe landing on the bond pads are evident.

However, for future studies, we plan to change the mask with a progressively narrowing current leading to lower contact resistance and delayed electromigration, as suggested by the reviewer.

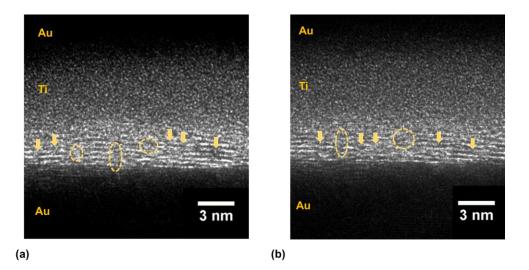

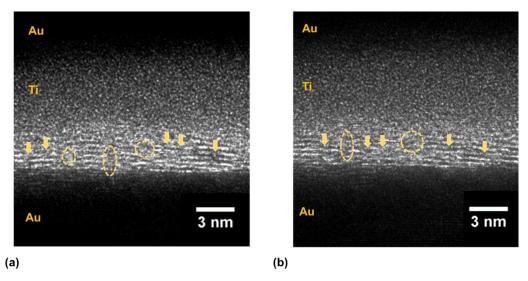

I wonder why the authors don't make TEM images with higher resolution to see more clearly the structure of the devices. It would be good if they could provide something like in this paper: <u>https://www.nature.com/articles/s41699-022-00341-5</u>

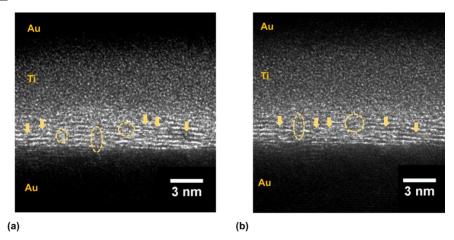

Thank you for the comment that helps improve the quality of the manuscript. As suggested, we have included TEM images with higher magnification that clearly show the device structure (Fig.R1.7). The hBN film has single-atom defects and few atom wide amorphous regions. These intrinsic defects aid in forming conductive filaments when stressed with high voltages. We have added the high-magnification TEM images as Figure 1e in the main text.

Figure R1.7 TEM images showing single-atom defects (arrows) and few atom wide amorphous regions (dashed circles).

#### <u>References</u>

- 1. Yu, S., Gao, B., Dai, H., Sun, B., Liu, L., Liu, X., Han, R., Kang, J. and Yu, B., 2009. Improved uniformity of resistive switching behaviors in HfO2 thin films with embedded AI layers. *Electrochemical and Solid-State Letters*, *13*(2), p.H36.

- Yuan, B., Liang, X., Zhong, L., Shi, Y., Palumbo, F., Chen, S., Hui, F., Jing, X., Villena, M.A., Jiang, L. and Lanza, M., 2020. 150 nm× 200 nm cross-point hexagonal boron nitride-based memristors. *Advanced Electronic Materials*, 6(12), p.1900115.

- Shen, Z., Zhao, C., Qi, Y., Xu, W., Liu, Y., Mitrovic, I.Z., Yang, L. and Zhao, C., 2020. Advances of RRAM devices: Resistive switching mechanisms, materials and bionic synaptic application. *Nanomaterials*, 10(8), p.1437.

- 4. Wong, H.S.P., Lee, H.Y., Yu, S., Chen, Y.S., Wu, Y., Chen, P.S., Lee, B., Chen, F.T. and Tsai, M.J., 2012. Metal–oxide RRAM. *Proceedings of the IEEE*, *100*(6), pp.1951-1970.

- Wu, X., Ge, R., Chen, P.A., Chou, H., Zhang, Z., Zhang, Y., Banerjee, S., Chiang, M.H., Lee, J.C. and Akinwande, D., 2019. Thinnest nonvolatile memory based on monolayer h-BN. *Advanced Materials*, 31(15), p.1806790.

- 6. Kim, M., Ge, R., Wu, X., Lan, X., Tice, J., Lee, J.C. and Akinwande, D., 2018. Zero-static power radio-frequency switches based on MoS2 atomristors. *Nature communications*, *9*(1), p.2524.

- Ge, R., Wu, X., Kim, M., Shi, J., Sonde, S., Tao, L., Zhang, Y., Lee, J.C. and Akinwande, D., 2018. Atomistor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. *Nano letters*, *18*(1), pp.434-441.

- Zhao, H., Dong, Z., Tian, H., DiMarzi, D., Han, M.G., Zhang, L., Yan, X., Liu, F., Shen, L., Han, S.J. and Cronin, S., 2017. Atomically thin femtojoule memristive device. *Advanced Materials*, 29(47), p.1703232.

- Huang, Y., Gu, Y., Wu, X., Ge, R., Chang, Y.F., Wang, X., Zhang, J., Akinwande, D. and Lee, J.C., 2021. ReSe2-Based RRAM and Circuit-Level Model for Neuromorphic Computing. *Frontiers in Nanotechnology*, *3*, p.782836.

- Xu, R., Jang, H., Lee, M.H., Amanov, D., Cho, Y., Kim, H., Park, S., Shin, H.J. and Ham, D., 2019. Vertical MoS2 double-layer memristor with electrochemical metallization as an atomic-scale synapse with switching thresholds approaching 100 mV. *Nano letters*, *19*(4), pp.2411-2417

- Shi, Y., Pan, C., Chen, V., Raghavan, N., Pey, K.L., Puglisi, F.M., Pop, E., Wong, H.S. and Lanza, M., 2017, December. Coexistence of volatile and non-volatile resistive switching in 2D h-BN based electronic synapses. In 2017 IEEE International Electron Devices Meeting (IEDM) (pp. 5-4). IEEE.

- Shi, Y., Liang, X., Yuan, B., Chen, V., Li, H., Hui, F., Yu, Z., Yuan, F., Pop, E., Wong, H.S.P. and Lanza, M., 2018. Electronic synapses made of layered two-dimensional materials. *Nature Electronics*, 1(8), pp.458-465.

- Jing, X., Puglisi, F., Akinwande, D. and Lanza, M., 2019. Chemical vapor deposition of hexagonal boron nitride on metal-coated wafers and transfer-free fabrication of resistive switching devices. 2D Materials, 6(3), p.035021.

- Wang, C.H., McClellan, C., Shi, Y., Zheng, X., Chen, V., Lanza, M., Pop, E. and Wong, H.S.P., 2018, December. 3D monolithic stacked 1T1R cells using monolayer MoS 2 FET and hBN RRAM fabricated at low (150° C) temperature. In 2018 IEEE International Electron Devices Meeting (IEDM) (pp. 22-5). IEEE.

- Yuan, B., Liang, X., Zhong, L., Shi, Y., Palumbo, F., Chen, S., Hui, F., Jing, X., Villena, M.A., Jiang, L. and Lanza, M., 2020. 150 nm× 200 nm cross-point hexagonal boron nitride-based memristors. *Advanced Electronic Materials*, 6(12), p.1900115.

- Yeh, C.H., Zhang, D., Cao, W. and Banerjee, K., 2020, December. 0.5 T0. 5R-Introducing an Ultra-Compact Memory Cell Enabled by Shared Graphene Edge-Contact and h-BN Insulator. In 2020 IEEE International Electron Devices Meeting (IEDM) (pp. 12-3). IEEE.

- Gu, Y., Serna, M.I., Mohan, S., Londoño-Calderon, A., Ahmed, T., Huang, Y., Lee, J., Walia, S., Pettes, M.T., Liechti, K.M. and Akinwande, D., 2022. Sulfurization Engineering of One-Step Low-Temperature MoS2 and WS2 Thin Films for Memristor Device Applications. *Advanced Electronic Materials*, 8(2), p.2100515.

- Shen, Y., Zheng, W., Zhu, K., Xiao, Y., Wen, C., Liu, Y., Jing, X. and Lanza, M., 2021. Variability and Yield in h-BN-Based Memristive Circuits: The Role of Each Type of Defect. *Advanced Materials*, 33(41), p.2103656.

- Yan, X., Zhao, Q., Chen, A.P., Zhao, J., Zhou, Z., Wang, J., Wang, H., Zhang, L., Li, X., Xiao, Z. and Wang, K., 2019. Vacancy-induced synaptic behavior in 2D WS2 nanosheet–based memristor for low-power neuromorphic computing. *Small*, *15*(24), p.1901423

- Zhuang, P., Lin, W., Ahn, J., Catalano, M., Chou, H., Roy, A., Quevedo-Lopez, M., Colombo, L., Cai, W. and Banerjee, S.K., 2020. Nonpolar resistive switching of multilayer-hBN-based memories. *Advanced Electronic Materials*, 6(1), p.1900979.

- Zhang, F., Zhang, H., Shrestha, P.R., Zhu, Y., Maize, K., Krylyuk, S., Shakouri, A., Campbell, J.P., Cheung, K.P., Bendersky, L.A. and Davydov, A.V., 2018, December. An ultra-fast multi-level MoTe 2-based RRAM. In 2018 IEEE International Electron Devices Meeting (IEDM) (pp. 22-7). IEEE.

- Tang, B., Veluri, H., Li, Y., Yu, Z.G., Waqar, M., Leong, J.F., Sivan, M., Zamburg, E., Zhang, Y.W., Wang, J. and Thean, A.V., 2022. Wafer-scale solution-processed 2D material analog resistive memory array for memory-based computing. *Nature Communications*, *13*(1), p.3037.

- Wang, M., Cai, S., Pan, C., Wang, C., Lian, X., Zhuo, Y., Xu, K., Cao, T., Pan, X., Wang, B. and Liang, S.J., 2018. Robust memristors based on layered two-dimensional materials. *Nature Electronics*, 1(2), pp.130-136.

- Braun, D., Lukas, S., Völkel, L., Hartwig, O., Prechtl, M., Belete, M., Kataria, S., Wahlbrink, T., Daus, A., Duesberg, G.S. and Lemme, M.C., 2022, June. Non-Volatile Resistive Switching in PtSe 2-Based Crosspoint Memristors. In 2022 Device Research Conference (DRC) (pp. 1-2). IEEE.

- Jeong, H.Y., Kim, J.Y., Kim, J.W., Hwang, J.O., Kim, J.E., Lee, J.Y., Yoon, T.H., Cho, B.J., Kim, S.O., Ruoff, R.S. and Choi, S.Y., 2010. Graphene oxide thin films for flexible nonvolatile memory applications. *Nano letters*, *10*(11), pp.4381-4386.

- Wang, Y., Yang, J., Wang, Z., Chen, J., Yang, Q., Lv, Z., Zhou, Y., Zhai, Y., Li, Z. and Han, S.T., 2019. Near-infrared annihilation of conductive filaments in quasiplane MoSe2/Bi2Se3 nanosheets for mimicking heterosynaptic plasticity. *Small*, *15*(7), p.1805431.

- Zhu, K., Pazos, S., Aguirre, F., Shen, Y., Yuan, Y., Zheng, W., Alharbi, O., Villena, M.A., Fang, B., Li, X. and Milozzi, A., 2023. Hybrid 2D/CMOS microchips for memristive applications. *Nature*, pp.1-3.

#### Reviewer 2

In the introduction, the authors noted that there has been relatively little attention devoted to studying the switching dynamics of memristors. However, numerous studies have explored the dynamic mechanisms in both metal-oxide-based and hBN-based memristors. For instance, TEM has been used to observe the electrochemical dynamics of nanoscale metal conductive filaments in metal-oxide-based memristors, and a model has been established to consider the applied electric field, metal ion diffusion, and filament shape based on dynamic metal cluster nucleation and growth. [1,2] In the case of 2D hBN-based memristors, the dynamic analysis of nano-conductive filaments has also been investigated, including the effect of temperature. [3,4] Additionally, a Monte Carlo simulation has been shown simulate filament growth and to erase dynamics. [5]

Thank you for providing valuable references that we missed during our literature survey. Through the statement, "little attention devoted to studying the switching dynamics of memristors," we meant to say that studying the switching dynamics through transient switching characteristics was less explored. However, we agree that the statement is ambiguous, and considerable research effort has been dedicated to studying the switching dynamics in memristors. Therefore, to avoid confusion, the sentence has been removed from the manuscript, and the introduction has been updated as suggested by another reviewer. We have included the suggested references for completeness.

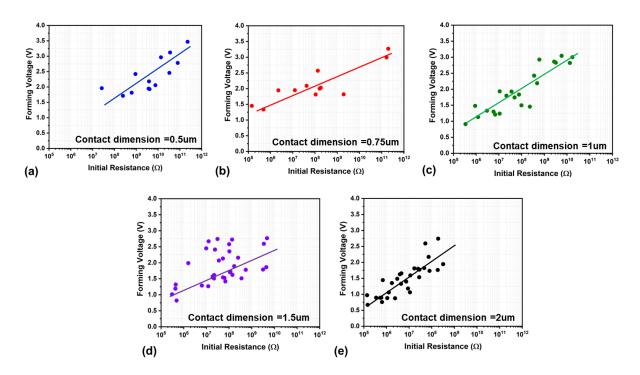

In Figure 2a, have the initial currents measured from devices with different areas been plotted together? If not, the authors should clearly state the device area that used in this figure. If initial currents have been plotted together, the authors should include a legend specifying the device area, as this parameter is critical in determining the high-resistance state (HRS) initial current. A similar issue is observed in Supplementary Figure 7a, where the authors plot the correlation between the forming voltage and the initial current. In this case, the authors should keep the device area constant.

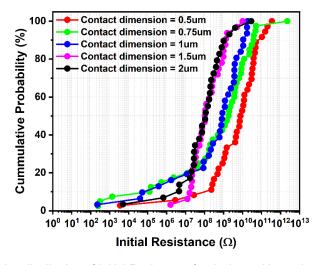

Thank you for the suggestion. The plot (Fig.2a in original manuscript) includes the initial resistance measured from devices with different cross-section areas. We agree that the device area determines the initial resistance and should have been plotted separately. As suggested, we have updated the figure by segregating the data points based on the device area and plotting the graphs separately with a corresponding legend (Figure R2.1). It is evident that the forming voltage increases with initial resistance for all device dimensions. Therefore, a generic relationship can be established between initial resistance and forming voltage for the 2D hBN based memristor devices.

Figure R2.1 Forming Voltage vs Initial Resistance for devices with contact dimensions (a) 0.5um (b) 0.75um (c) 1um (d) 1.5um (e) 2um

Similarly, we have updated Supplementary Figure 7a by segregating the data points based on device dimensions (Figure R2.2). As expected, the initial resistance distribution moves to lower values as the device's cross-sectional area increases.

Figure R2.2 Cumulative distribution of Initial Resistance for devices with varying contact dimensions

Both these figures have been included as Supplementary Fig.7 in the manuscript.

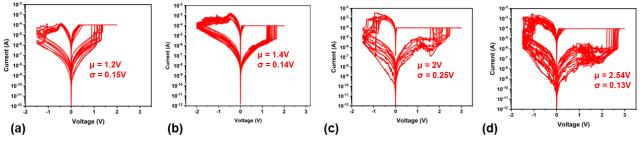

In Fig. 2d, the device cycle-to-cycle variation is much higher than other hBN-based memristors.[6] The range of set voltages is wide, spanning from 1 to 3 V, creating significant difficulties in selecting memristor devices for cross bar arrays. Furthermore, device-to-device variation exacerbates this issue. To understand the cause of this considerable variation, the authors should conduct further analysis.

Thank you for the insightful comment. Fig.2c (updated manuscript number) plots the SET/RESET voltages from 200 IV traces. These traces include multiple cycles collected from different devices. The overall variation of the SET voltage spans between 1V to 3V is not ideal for large cross-bar array applications. To understand the source of this variation, we segregated the data into cycle-to-cycle and device-to-device components. Qualitatively, we observed that the cycle-to-cycle variation is lower than the device-to-device variation. This is evident in Figure. R2.3, where DC IV characteristics collected from four devices are presented. Although the mean SET voltage varies considerably (between 1.2V and 2.54V), the distributions are tightly bound around the mean value with a worst-case standard deviation of 0.25V. This indicates that the device-to-device variation is the dominant cause of variation for these memristors.

Figure R2.3 DC IV characteristics collected from four different memristor devices.

We speculate that the electrode surface roughness contributes to the higher device-to-device variation among these devices. Evaporated metal electrodes typically have a surface roughness of about 1-2nm [11-13]. The effect of this roughness on the switching characteristics should be lower in memristors with thicker switching layer (>5nm). This could potentially explain the reduced variation observed in the memristors studied in [6], where 18-layer hBN (~6.6nm thick) was utilized to fabricate the devices. However, as the switching layer thickness scales down, it is easier for filaments to propagate vertically and form around weak spots with bumps/hillocks. Therefore, the surface roughness of the electrodes will largely determine the location and voltage of the breakdown. These variations can be reduced with industry-standard tools that can achieve lower surface roughness, which is difficult to achieve with university equipment.

In the study on dynamic filament formation (see Fig. 4 and Supplementary Fig. 10), the authors employed a conventional model that takes into account the effects of temperature, the heat equation, and the Arrhenius relationship for filament growth. It should be noted, however, that this model was originally developed for oxide memristors. [7,8] As such, it is unclear how the model in this work differs from the one used for metal oxide, and how it specifically contributes to understanding the filament growth dynamics in hBN.

Thank you for the comment. We agree that the Arrhenius model was originally developed for oxide memristors. The corresponding references have been duly cited in the manuscript (references 55-57) and the supplementary information (references S18-S19). This universal phenomenological model satisfactorily captures the growth dynamics in memristors such as OxRRAMs (Oxide RRAM) and CBRAMs (conductive bridge RAM). Therefore, in this study, we employ the same model with modifications to capture the behavior of our 2D memristors under ultra-fast voltage pulse stresses.

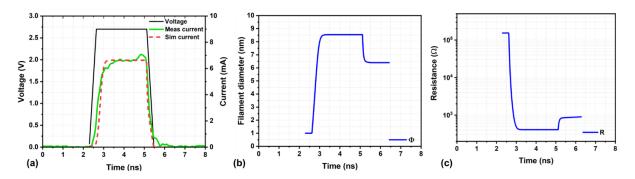

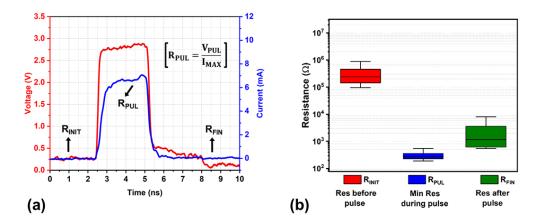

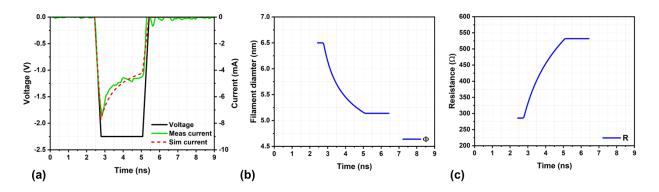

The models presented in [7,8] consider filament formation and dissolution as independent events i.e., during a SET process, all the equations only model filament expansion. However, in reality, formation and dissolution proceed simultaneously (determined by voltage and temperature), albeit at different rates. For example, as the filament begins to widen, the temperature generated in the filament increases, which promotes outward diffusion of the metal ions from the filament. Since the memristors in this study have an ultra-thin switching layer (<2.5nm), very low resistance filaments ( $200\Omega - 500\Omega$ ) are formed during the SET process. These low-resistance filaments generate high filament temperatures that promote dissolution resulting in filament narrowing. This phenomenon of filament narrowing was evidently observed in our devices (Fig.R2.4). For this study, we measured the resistance of the device before ( $R_{INIT}$ ), after ( $R_{FIN}$ ), and during the pulse ( $R_{PUL}$ ). The resistance distributions of  $R_{INIT}$ ,  $R_{PUL}$ , and  $R_{FIN}$  (Fig.R2.4b) show that the memristor resistance reduces during the SET pulse and again increases after the pulse suggesting a reduction in filament cross-section.

Figure R2.4 (a) Voltage and current pulse waveforms during a SET operation. (b) Resistance distribution of R<sub>INIT</sub>, R<sub>PUL</sub>, R<sub>FIN</sub>. The R<sub>PUL</sub> was estimated as the resistance value calculated at the maximum current magnitude during the pulse. The resistance value is calculated at the maximum current magnitude during the pulse (R<sub>PUL</sub>) and immediately before (R<sub>INIT</sub>) and after (R<sub>FIN</sub>) the pulse via applying a small DC bias V=100mV.

The Arrhenius models (Eq.R2.1) [7,8] can only capture filament expansion during the SET process and vice versa during the RESET process. Therefore, the final resistance estimated by these models will need to be revised.

$$\frac{d\Phi}{dt} = Ae^{\left(-\frac{Ea0-aqV}{kT_{CF}}\right)} \tag{R2.1}$$

To account for filament narrowing, we include a second term that captures the dynamics of filament dissolution (Eq.R2.2).

Note that the activation energy  $E_a$  required for metal ion out-diffusion from the filament differs from activation energy  $E_{a0}$  for filament formation (bond breaking and ion hopping). As the voltage pulse ramps up, the first term dominates, and the filament expands. After reaching a certain filament width the higher current flowing through the device generates higher temperature. Here, the filament growth rate is balanced by the filament dissolution rate, and the filament diameter saturates. However, during the voltage pulse falling transition, the growth rate (determined by V,  $T_{CF}$ ) decreases faster than the dissolution rate (determined only by  $T_{CF}$ ), thereby resulting in the narrowing of the filament.

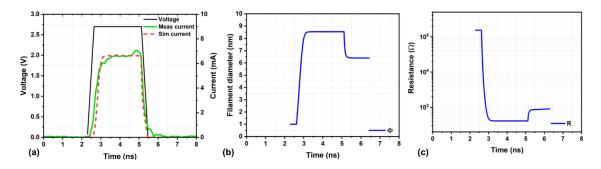

Figure R2.5 (a) Voltage and current pulse waveforms during a SET operation. The model current closely traces the measured current. Calculated time evolution of (b) filament diameter (c) memristor resistance.

A self-consistent electro-thermal solver using the proposed model clearly captures the filament narrowing (Fig.R2.5b,c). The filament expands to ~9nm in diameter and narrows to ~6.5nm after pulse termination. The memristor resistance change closely matches the resistance values presented in Fig.R2.4b. We believe that this joule heating driven filament narrowing will be observed in other 2D memristors as well, and therefore the proposed equations can be used to model them.

We have added additional text in the supplementary and the main text to highlight how our model differs from the previously published models [7,8].

The authors need to provide a clear explanation of the fundamental reason for the ultra-fast switching behavior observed in their memristor, as compared to other fast-switching memristors discussed in previous studies.[9,10] To achieve this, the authors should provide a detailed explanation in terms of their model and material properties.

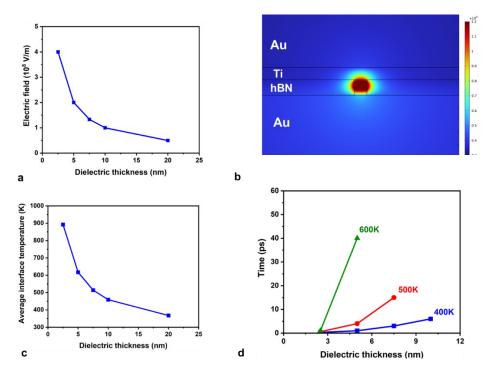

Thank you for the valuable and insightful comment. The memristors in previous studies [9,10] switch faster due to their unique switching mechanism, which is completely different from traditional Oxide RRAMs or CBRAMs. In [9], the memristor has Pt nanoparticles dispersed across the switching layer, effectively reducing the overall separation between the electrodes, which results in ultra-fast switching. On the other hand, the devices in [10] have a conducting channel in both ON and OFF states with different chemical compositions and therefore switch faster, whereas the switching mechanism in our 2D memristor is based on metal ion diffusion into the switching layer. The applied electric field facilitates the vertical propagation of the filament around weak spots in the dielectric. This initially formed narrow filament connects the electrodes and lowers the resistance of the memristor. The current flowing through this filament generates temperature through the Joule heating phenomenon. The temperature generated in the filament lowers the energy barrier for ion release from the electrode and further propels the filament growth. To understand the fundamental reason for the ultra-fast switching in our devices, we perform transient thermal analysis using finite element based physics solvers (COMSOL). To summarize the results, the characteristic properties aiding the ultra-fast switching in 2D hBN memristors are:

1. Ultra-thin switching layer

2. High thermal conductivity of 2D hBN layers

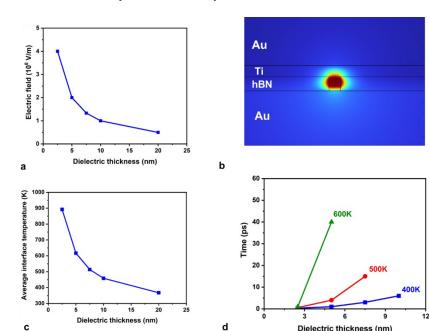

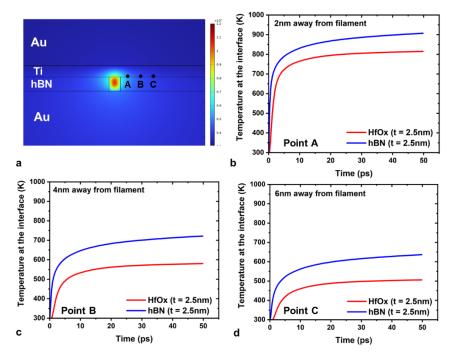

Figure R2.6 (a) Electric field vs dielectric thickness for V=1V. (b) Snapshot of the COMSOL model showing the metallic filament and electrodes. The temperature profile shows the highest temperature at the center of the filament. (c) Temperature reaching the interface vs dielectric thickness (d) time taken for the interface to reach 400K, 500K, 600K as a function of dielectric thickness.

#### Ultra-thin switching layer

Oxide memristors (commercial or university demonstrations) typically have a thicker switching layer (5nm-20nm) in comparison to the memristors in this study (< 2.4nm). The thinner switching layer significantly increases the local electric field across the dielectric, which promotes faster resistance switching. Fig.R2.6a shows the electric field increase inside the switching layer as the dielectric thickness reduces.

From the Arrhenius model (Eq.R2.1,2), we see that the filament growth dynamics depend on the temperature in addition to the applied voltage. The critical physical process that determines the switching speed of the device is the metal ion release [7] which is determined by the Ti/hBN interface temperature ( $T_{INT}$ ). Note that this temperature is different from the filament temperature ( $T_{CF}$ ). The current passing through the device generates temperature in the filament ( $T_{CF}$ ) through joule heating. This temperature is highest at the center of the filament (vertically) and lowers towards the electrodes, as seen in Fig.R2.6b. This nature of the temperature profile has been reported in several previous studies [14-16]. Most studies approximate  $T_{CF} \sim T_{INT}$  for simplicity in analytical modeling.

Using the COMSOL model, we study the  $T_{INT}$  dependence on dielectric thickness, as shown in Fig.R2.6c. It is evident that as the dielectric thickness reduces, steady-state  $T_{INT}$  increases. In addition, Fig.R2.6d plots the time taken for temperature build-up at the interface as a function of dielectric thickness. We plot the time taken to reach 400K, 500K, and 600K for comparison. The  $T_{INIT}$  for thinner dielectric (such as the devices in this study) reaches 600K in less than 1ps, whereas thicker dielectric ~5nm takes about 40ps. The faster temperature build-up at the interface promotes faster metal ion release, which creates a positive feedback loop: higher  $T_{INT} \rightarrow$  lower R  $\rightarrow$  higher  $T_{INT}$ . This positive feedback loop promotes faster switching in devices with a thinner dielectric layer.

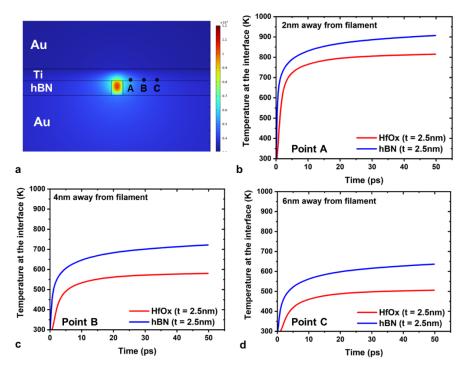

Figure R2.7 (a) Snapshot of COMSOL model showing three points of interest A,B,C. Transient interface temperature at (b) point A (c) point B (d) point C.

#### High thermal conductivity of 2D hBN

Based on the previous discussion, the obvious subsequent question would be - "Will the oxide RRAMs with thinner dielectric layer switch as fast as the 2D memristors?" To answer this question, we simulated two devices – one with an  $HfO_x$  layer and the other with 2D hBN, with identical switching layer thicknesses (2.5nm).

In addition to thickness, another physical property that determines the switching speed of the devices is the thermal conductivity of the switching layer. The in-plane thermal conductivity of hBN (k ~ 100-200 W/mK) [17-19] is significantly higher than oxides (k ~ 0.5-2 W/mK) typically used for memristors (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, TaO<sub>x</sub>) [20-22]. On the other hand, the out-of-plane thermal conductivity is comparable (5-10 mW/K) to the oxides. The high thermal conductivity quickly spreads the heat from the filament to the surroundings, which heats a larger cross-section of the interface. Fig.R2.7a shows three points on the interface at 2nm,4nm, and 6nm away from the filament. Temperature transients at these points (Fig.R2.7b,c,d) highlight this effect. Evidently, T<sub>INT</sub> increases rapidly for hBN compared to HfO<sub>x</sub>. This effect is especially more pronounced as we move away from the filament (points B, C). Since a larger cross-section of the interface is heated, the probability of ion release increases, which results in faster filament expansion. Therefore, 2D materials that typically have higher thermal conductivity promote faster switching compared to oxide RRAMs with identical layer thickness.

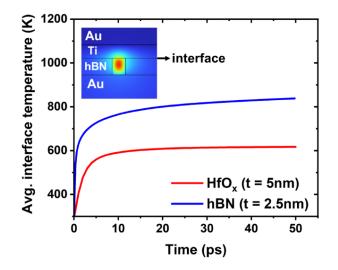

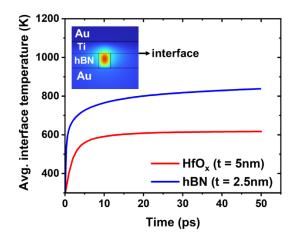

Overall, the 2D memristors benefit from having an ultra-thin switching layer as well as high thermal conductivity compared to TMO memristors. Fig.R2.8 shows the  $T_{INT}$  for hBN devices with 2.5nm thickness and HfOx devices with 5nm thickness (typical thickness for TMO memristors). Clearly, the temperature rises rapidly for the hBN devices resulting in ultra-fast switching.

This explanation for ultra-fast switching observed in 2D memristors has been added as Supplementary Figure.16 in the manuscript.

Figure R2.8 Average transient interface temperature for hBN with thickness=2.5nm and HfOx with thickness=5nm

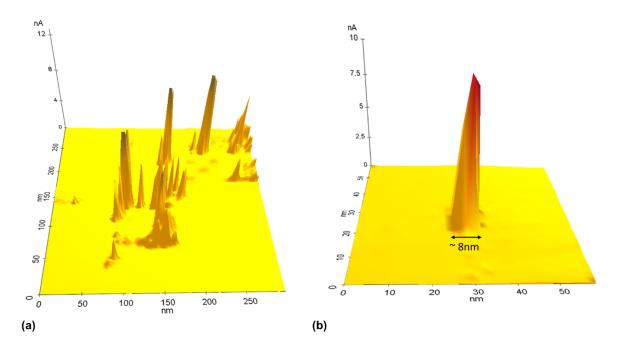

It would be beneficial if the authors could compare the fitted filament diameter obtained from their model with experimental results obtained from techniques such as C-AFM or HRTEM, which can directly measure the filament diameter.

Thank you for the comment. Obtaining the filament diameter through HRTEM is difficult as the probability that the FIB cut exactly passes through the filament is low; unfortunately, even after extensive searching across the FIB cuts, we did not observe filaments in our experiments. Moreover, all the elements involved in our devices (B,N,Ti) have relatively smaller atomic weights that do not produce discernible differences in contrast. Although some discontinuities in the layered hBN film are observed, these can, at best, be characterized as some defects or amorphous regions rather than as conductive filaments.

Figure R2.9 TEM images showing single-atom defects (arrows) and few atom wide amorphous regions (dashed circles).

Even if a filament existed in the FIB cut (typical depth ~ 100nm), it may not be visible in the TEM image unless its dimension is comparable to the depth. Since the 2D memristors have an ultrathin switching layer, narrow filaments can carry large currents compared to the thicker TMO memristors. Therefore, such large filament cross-section typically are not created in 2D memristors (typical filament dimension ~10-20nm [23]). The low contrast of Ti combined with the small dimension makes filament imaging in 2D memristors very challenging. All the previous studies (2D materials or otherwise) that have successfully imaged filaments through HRTEM have Ag, Au, or some other heavy elements that can produce sufficient contrast [1-2,23-24]. Other noted studies [25-26] in the field using hBN and Ti material system report defects/amorphous regions similar to Fig.R2.9.

At this time, unfortunately, the conductive AFM at our facility is not functional and would need several months before replacement parts can arrive.

However, our model's filament diameter matches closely with the experimental filament diameter (~10nm) obtained through HRTEM and CAFM published in previous study on 2D hBN memristors [23].

The authors should discuss more metrics or guidelines for measuring the pulse characteristics of their memristor. In Figures 4 and 5, the authors have presented statistical analysis of the transient pulse response and established correlations between switching ratio, switching time, and switching energy. It shows that the switching energy and switching time is highly related to the switching ratio before/after pulse. To better understand the performance of their ultra-fast switching device, the authors should discuss key performance metrics for fast-switching devices and the differences between normal endurance (with pulse widths of tens of microseconds) and ultra-fast pulse endurance (with sub-nanosecond

Thank you for the valuable comment. Based on our experience, we have listed the following guidelines and metrics for testing memristors with ultra-fast pulses.

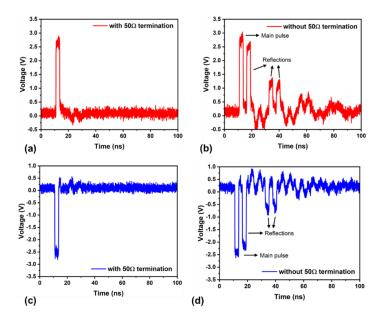

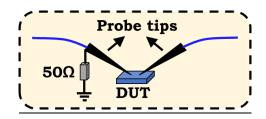

#### Signal Reflections

Characterization of the memristors in the sub-nanosecond regime requires the fast pulse to be delivered through a transmission line setup using specialized RF cables with matching impedance (50 $\Omega$ ). The pulse delivered to the device-under-test (DUT) needs to be monitored for further analysis. This can be achieved by sampling the input transmission line through a pick-off tee. In addition to using RF cables, the transmission line needs to be properly terminated with a 50 $\Omega$  resistor, placed as close as possible to the DUT, ideally on the probe tips, as shown in Fig.R2.10. This termination resistor minimizes reflections and ensures maximum power transfer to the DUT.

Figure R2.10 Test setup schematic showing the  $50\Omega$  termination placed near the probe tips.

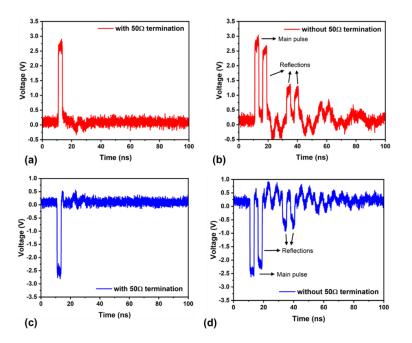

Figure R2.11 Transient waveform for (a) SET pulse with  $50\Omega$  resistor (b) SET pulse without  $50\Omega$  resistor (c) RESET pulse with  $50\Omega$  resistor (d) RESET pulse without  $50\Omega$  resistor.

The 50 $\Omega$  termination resistor effectively suppresses reflections, as seen in Fig.R2.11a,c for SET and REST pulses, respectively. Whereas the reflections are significant when the 50 $\Omega$  resistor was not soldered onto the probe tips, as seen in Fig.R2.11b,d. Such reflections would result in random programming of the memristor. Therefore, all the experiments presented in this work were conducted with the 50 $\Omega$  termination on the probe tips ensuring minimal reflected power.

#### Test setup parasitics

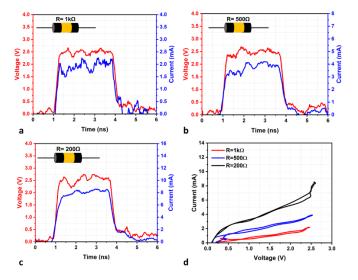

Figure R2.12 Applied voltage pulse (red trace) and measured current (blue trace) across a discrete surface mount resistor with the resistance (a)  $1k\Omega$  (b)  $500\Omega$  (c)  $200\Omega$ . (d) I-V plots of the pulses are shown in (a),(b),(c).

The test setup needs to be vetted thoroughly for parasitics, reflections, and noise sources before proceeding to test memristors. If noise appears in the voltage pulses, each segment of the transmission line needs to be tested in isolation with a  $50\Omega$  termination. In addition, any unintended parasitic capacitance in the setup will produce a delayed current response that could be mistaken as resistive switching. The parasitics in the setup can be identified by applying voltage pulses to standalone resistors (SMD or other) and verifying the response. For example, we observed hysteresis when voltage pulses were applied to the memristors. To ensure that the hysteresis originated from memristors and not system parasitics, we tested the response of resistors. Fig.R2.12 shows that no significant hysteretic window is observed, suggesting that the hysteresis can be attributed to the resistive switching of the memristor.

#### Sanity checks for confidence

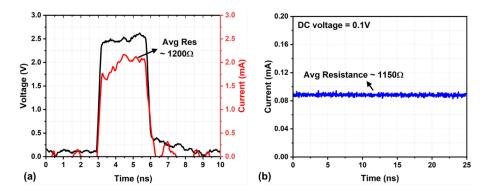

In our experiments, we observed that the resistance of the memristor during the SET pulse is lower than the resistance after the pulse. As explained in the methods section, the resistance during the pulse is directly measured by the oscilloscope, whereas the resistance before/after the pulse is measured through a current amplifier in the branched DC path. Therefore, any additional resistance in the DC path can increase the resistance after the pulse. To confirm that the DC path does not have any parasitic resistance, we applied the voltage pulse to a standalone resistor and measured the resistance. Fig.R2.13 shows that the resistance during and after the pulse measured close to  $1.2k\Omega$ . Therefore, the resistance increase observed after the pulse in Fig.5c (main text) is indeed a characteristic feature of the memristors associated with joule heating. Such sanity checks at every stage are necessary to ensure the correct interpretation of the experimental observations.

Figure R2.13 SET pulse applied to discrete resistor, (a) Voltage and current waveforms (b) DC current measured before and after the pulse

#### Switching time

Switching time is the primary performance metric for fast-switching memristors intended for highfrequency applications. The switching time of a memristor can be characterized by measuring the current response to the voltage pulse. When characterizing the switching time, some reports do not consider the voltage pulse rise time. In addition, few studies define switching time as the duration required to reach 50% of the final resistance level. Although such characterization techniques provide an attractive switching time estimate, we believe that this does not reflect a realistic scenario. For example, some signals switch faster up to 50% resistance level but may slow down later, which will not be captured by 50% definition. Therefore, we recommend including the voltage pulse rise time as well as defining the switching speed as the time taken for the current signal to settle to ~90% of its final resistance state.

#### Endurance Cycling

Pulse testing in the sub-nanosecond regime is tricky (test setup and analysis) and complicated. Therefore, most studies typically characterize the switching speed based on a single experiment. Characterizing the memristor speed based on a single cycle is unreliable and potentially misleading. It is difficult to ascertain that the observed fast response is associated with a reversible switching process. For example, a device shorted (failed) by the fast pulse will produce a current signature similar to SET. Likewise, a device whose current leads are damaged due to excessive current (electromigration) will produce a signature similar to RESET. Therefore, the switching speed of the device should only be characterized by considering subsequent cycling data. In this regard, only two research articles show repeatable switching with 10 cycles [9] and 20 cycles [27] using ultra-short voltage pulses. The fact that many studies do not show cycling data may suggest that those devices do not switch consistently. In addition, cycling experiments provide statistical data on the switching time of the memristors, which is crucial to understand the variations in the switching time.

#### Cycling with wider pulses

To understand the impact of pulse width on endurance cycling, we measured our devices with 100ns voltage pulses (Fig.R2.14a). We observe that the devices cycle for about 60-80 cycles (Fig.R2.14b) before getting shorted. Although it may seem like the cycling performance of the device degrades with wider pulses, such an interpretation would be premature. Rather than the pulse width, the endurance in our experiments is limited by the test setup and device configuration. The primary concern here (both for narrow and wide pulses) is the absence of a current limiting

mechanism which results in excess metal ion diffusion into the switching layer. The excess metal ions form wide filaments in the ultra-thin switching layer, which the RESET pulse cannot dissolve. A similar failure mechanism has also been observed with the DC characterization of the devices. Therefore, it is critical to limit the metal ion diffusion into the memristor either through a barrier layer or an external current-limiting device. A very recent study [28] reported high endurance of ~10<sup>6</sup> cycles in the 1T1M (1transistor-1memristor) bitcell hBN switching layer. In that study, the standalone devices without CMOS transistors exhibited only 100 cycles, whereas devices with transistors exhibited a million cycles. This promising result suggests that the current limiting mechanism is critical to improving endurance in 2D memristor devices.

Figure R2.14 (a) Pulse voltage and current waveforms (b) Cycling data with 100ns voltage pulses

The authors demonstrate 600-cycle endurance with ultra-fast pulses, which is higher than other fast memristors' endurance results. However, it is important to note that other memristors can achieve endurance up to 108 cycles with pulse widths of microseconds. Therefore, to prove the stability of their device, the authors should provide endurance results with a higher cycle number.

Thank you for the comment. We want to answer this question on endurance through the following sub-sections,

#### Endurance in 2D memristors

The endurance in 2D memristors has been a concern, mainly attributed to the ultra-thin switching layer. Transition metal oxide (TMO) based memristors typically have a switching layer thickness ranging between 5nm-20nm [29-31]. On the contrary, 2D memristors typically have ultra-thin switching layers, sometimes even scaled down to monolayer thickness. The reduced vertical separation between metal electrodes enhances the electric field, which results in reduced control over the metal ion migration into the switching layer and subsequent filament formation. Moreover, as the thickness of the switching layer reduces, the impact of bottom/top electrode roughness plays a significant role in determining the overall device performance. In the following table, we have listed the reported endurance in 2D memristors along with the thickness of the switching layer.

|           | Switching layer stack    | Thickness (nm) | Cycles endurance |

|-----------|--------------------------|----------------|------------------|

| [32]      | Au/hBN/Au                | 0.33           | 50               |

| [33]      | Au/MoS₂/Au               | 0.65           | 20               |

| [34]      | Au/MoS₂/Au               | 0.65           | 150              |

| [35]      | Ag/hBNO <sub>x</sub> /Gr | 0.9            | 100              |

| [36]      | Au/ReSe <sub>2</sub> /Au | 1              | 200              |

| [37]      | Cu/MoS <sub>2</sub> /Au  | 1.4            | 20               |

| [38]      | Ti/hBN/Au                | 2.4            | 100              |

| [39]      | Ti/hBN/Au                | 2.4            | 100              |

| [40]      | Ti/hBN/Ni                | 3.96           | 100              |

| [41]      | Ti/hBN/Au                | 4.3            | 50               |

| [42]      | Ti/hBN/Au                | 4.95           | 250              |

| [43]      | Ti/hBN/Gr                | 5              | 1000             |

| [44]      | Au/MoS <sub>2</sub> /Au  | 5              | 120              |

| [45]      | Au/hBN/Au                | 6              | 50               |

| [46]      | Pd/WS <sub>2</sub> /Pt   | 6.45           | 15               |

| [47]      | Ti/hBN/Au                | 6.6            | 1200             |

| [48]      | Ti/MoTe₂/Au              | 7              | 600              |

| This work | Ti/hBN/Au                | 2.64           | 600              |

| This work | Ti/hBN/Au                | 1.32           | 100              |

From the table, we see that the 2D memristors with switching layer thickness <5nm, typically exhibit <250 cycles endurance. Some memristors [43,47] exhibit about 1000 cycle endurance with >5nm switching layer thickness. Our devices exhibit on-par performance with 600 cycles for thicker ( $T_{hBN}$ ~ 2.64nm) memristors and 100 for thinner ( $T_{hBN}$ ~ 1.32nm) memristors.

On the other hand, only two research studies report high endurance (~10<sup>7</sup>) using thicker 2D memristors [49-50]. Many studies report low endurance even with thicker 2D memristors [51-53].

#### Role of Current Compliance (CC)

A recent study [28] (suggested by the reviewer in previous comments) reported high endurance of ~ $10^6$  cycles in the 1T1M (1transistor-1memristor) bitcell with just ~6.6nm thick switching layer. In that study, the standalone devices without CMOS transistors exhibited only 100 cycles, whereas devices with transistors exhibited a million cycles. This promising result suggests that the adjoining selector device can improve endurance in 2D memristor devices.

The characterization setup utilized in this study cannot support external current compliance (CC) for high-frequency pulse testing. For the frequency range studied in this article, the external CC device (resistor, diode or transistor) must be located within <1cm distance from the DUT (device under test) to be considered as a lumped circuit element. Therefore, the only possible option is to have a CC device fabricated monolithically, like in [28]. Without current compliance, most of our devices get shorted during testing, which cannot be recovered.

We have tested multiple devices but unfortunately could not get better endurance cycling than 600 cycles with the 2.7ns pulses. However, we believe that having a 1T1M configuration would improve the endurance of our devices as well.

### There are some typos in the manuscript. (Line 81, the SET should be transition to lower resistance instead of lower conductance)

Thank you for pointing out the typo. We have corrected the sentence. We have thoroughly scanned the manuscript for typos.

## The image quality is poor in the manuscript, some of the images cannot be viewed clearly. (Figure 2g, 2h)

We have updated the figures 2g,2h with better quality images and increased the plot texts for improved readability.

## Scale bar labeling is confusing. In Supplementary Fig. 3a, the sample electrode width seems to be larger than 2 um. However, the maximum electrode width is 2 um in this work.

Thank you for pointing that out, this would have missed our attention. There was a mistake in generating the scale bar. We have updated the figure with the correct scale bar.

#### References

- [1] Yang, Y., Gao, P., Li, L., Pan, X., Tappertzhofen, S., Choi, S., Waser, R., Valov, I. and Lu, W.D., 2014. Electrochemical dynamics of nanoscale metallic inclusions in dielectrics. *Nature communications*, 5(1), p.4232.

- [2] Yang, Y., Gao, P., Gaba, S., Chang, T., Pan, X. and Lu, W., 2012. Observation of conducting filament growth in nanoscale resistive memories. *Nature communications*, *3*(1), p.732.

- [3] Lanza, M., Palumbo, F., Shi, Y., Aguirre, F., Boyeras, S., Yuan, B., Yalon, E., Moreno, E., Wu, T. and Roldan, J.B., 2022. Temperature of conductive nanofilaments in hexagonal boron nitride based memristors showing threshold resistive switching. *Advanced Electronic Materials*, *8*(8), p.2100580.

- [4] Zhu, K., Liang, X., Yuan, B., Villena, M.A., Wen, C., Wang, T., Chen, S., Hui, F., Shi, Y. and Lanza, M., 2019. Graphene–boron nitride–graphene cross-point memristors with three stable resistive states. ACS applied materials & interfaces, 11(41), pp.37999-38005.

- [5] Qian, F., Chen, R.S., Wang, R., Wang, J., Xie, P., Mao, J.Y., Lv, Z., Ye, S., Yang, J.Q., Wang, Z. and Zhou, Y., 2022. A leaky integrate-and-fire neuron based on hexagonal boron nitride (h-BN) monocrystalline memristor. *IEEE Transactions on Electron Devices*, 69(11), pp.6049-6056.

- [6] Chen, S., Mahmoodi, M.R., Shi, Y., Mahata, C., Yuan, B., Liang, X., Wen, C., Hui, F., Akinwande, D., Strukov, D.B. and Lanza, M., 2020. Wafer-scale integration of two-dimensional materials in highdensity memristive crossbar arrays for artificial neural networks. *Nature Electronics*, *3*(10), pp.638-645.

- [7] Huang, P., Liu, X.Y., Chen, B., Li, H.T., Wang, Y.J., Deng, Y.X., Wei, K.L., Zeng, L., Gao, B., Du, G. and Zhang, X., 2013. A physics-based compact model of metal-oxide-based RRAM DC and AC operations. *IEEE transactions on electron devices*, 60(12), pp.4090-4097.

- [8] Ielmini, D., 2011. Modeling the universal set/reset characteristics of bipolar RRAM by field-and temperature-driven filament growth. *IEEE Transactions on Electron Devices*, 58(12), pp.4309-4317.

- [9] Choi, B.J., Torrezan, A.C., Norris, K.J., Miao, F., Strachan, J.P., Zhang, M.X., Ohlberg, D.A., Kobayashi, N.P., Yang, J.J. and Williams, R.S., 2013. Electrical performance and scalability of Pt dispersed SiO2 nanometallic resistance switch. *Nano letters*, *13*(7), pp.3213-3217.

- [10] Choi, B.J., Torrezan, A.C., Strachan, J.P., Kotula, P.G., Lohn, A.J., Marinella, M.J., Li, Z., Williams, R.S. and Yang, J.J., 2016. High-speed and low-energy nitride memristors. *Advanced Functional Materials*, 26(29), pp.5290-5296.

- [11] Chen, G. and Hui, P., 1999. Thermal conductivities of evaporated gold films on silicon and glass. *Applied physics letters*, 74(20), pp.2942-2944.

- [12] Yang, Z., Liu, C., Gao, Y., Wang, J. and Yang, W., 2016. Influence of surface roughness on surface plasmon resonance phenomenon of gold film. *Chinese Optics Letters*, 14(4), p.042401.

- [13] Stenzel, O., Wilbrandt, S., Stempfhuber, S., Gäbler, D. and Wolleb, S.J., 2019. Spectrophotometric characterization of thin copper and gold films prepared by electron beam evaporation: thickness dependence of the Drude damping parameter. *Coatings*, *9*(3), p.181.

- [14] Niraula, D. and Karpov, V.G., 2017. Heat transfer in filamentary RRAM devices. IEEE Transactions on Electron Devices, 64(10), pp.4106-4113.

- [15] Ielmini, D., Nardi, F. and Cagli, C., 2011. Physical models of size-dependent nanofilament formation and rupture in NiO resistive switching memories. *Nanotechnology*, 22(25), p.254022.

- [16] Larentis, S., Nardi, F., Balatti, S., Gilmer, D.C. and Ielmini, D., 2012. Resistive switching by voltagedriven ion migration in bipolar RRAM—Part II: Modeling. *IEEE Transactions on Electron Devices*, 59(9), pp.2468-2475.

- [17] Jo, I., Pettes, M.T., Kim, J., Watanabe, K., Taniguchi, T., Yao, Z. and Shi, L., 2013. Thermal conductivity and phonon transport in suspended few-layer hexagonal boron nitride. *Nano letters*, 13(2), pp.550-554.

- [18] Alam, M.T., Bresnehan, M.S., Robinson, J.A. and Haque, M.A., 2014. Thermal conductivity of ultrathin chemical vapor deposited hexagonal boron nitride films. *Applied Physics Letters*, 104(1).

- [19] Jana, M. and Singh, R.N., 2018. Progress in CVD synthesis of layered hexagonal boron nitride with tunable properties and their applications. *International Materials Reviews*, 63(3), pp.162-203.

- [20] Panzer, M.A., Shandalov, M., Rowlette, J.A., Oshima, Y., Chen, Y.W., McIntyre, P.C. and Goodson, K.E., 2009. Thermal properties of ultrathin hafnium oxide gate dielectric films. *IEEE Electron Device Letters*, 30(12), pp.1269-1271.

- [21] Cappella, A., Battaglia, J.L., Schick, V., Kusiak, A., Lamperti, A., Wiemer, C. and Hay, B., 2013. High Temperature Thermal Conductivity of Amorphous Al2 O 3 Thin Films Grown by Low Temperature ALD. Advanced Engineering Materials, 15(11), pp.1046-1050.

- [22] Landon, C.D., Wilke, R.H., Brumbach, M.T., Brennecka, G.L., Blea-Kirby, M., Ihlefeld, J.F., Marinella, M.J. and Beechem, T.E., 2015. Thermal transport in tantalum oxide films for memristive applications. *Applied Physics Letters*, 107(2).

- [23] Shi, Y., Liang, X., Yuan, B., Chen, V., Li, H., Hui, F., Yu, Z., Yuan, F., Pop, E., Wong, H.S.P. and Lanza, M., 2018. Electronic synapses made of layered two-dimensional materials. *Nature Electronics*, 1(8), pp.458-465.

- [24] Dong, Z., Hua, Q., Xi, J., Shi, Y., Huang, T., Dai, X., Niu, J., Wang, B., Wang, Z.L. and Hu, W., 2023. Ultrafast and Low-Power 2D Bi2O2Se Memristors for Neuromorphic Computing Applications. *Nano Letters*, 23(9), pp.3842-3850.

- [25] Roldan, J.B., Maldonado, D., Aguilera-Pedregosa, C., Moreno, E., Aguirre, F., Romero-Zaliz, R., García-Vico, A.M., Shen, Y. and Lanza, M., 2022. Spiking neural networks based on two-dimensional materials. *npj 2D Materials and Applications*, 6(1), p.63.

- [26] Pan, C., Ji, Y., Xiao, N., Hui, F., Tang, K., Guo, Y., Xie, X., Puglisi, F.M., Larcher, L., Miranda, E. and Jiang, L., 2017. Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride. *Advanced functional materials*, 27(10), p.1604811.

- [27] Chen, Z., Huang, W., Zhao, W., Hou, C., Ma, C., Liu, C., Sun, H., Yin, Y. and Li, X., 2019. Ultrafast Multilevel Switching in Au/YIG/n-Si RRAM. Advanced Electronic Materials, 5(2), p.1800418.

- [28] Zhu, K., Pazos, S., Aguirre, F., Shen, Y., Yuan, Y., Zheng, W., Alharbi, O., Villena, M.A., Fang, B., Li, X. and Milozzi, A., 2023. Hybrid 2D–CMOS microchips for memristive applications. *Nature*, 618(7963), pp.57-62.

- [29] Wong, H.S.P., Lee, H.Y., Yu, S., Chen, Y.S., Wu, Y., Chen, P.S., Lee, B., Chen, F.T. and Tsai, M.J., 2012. Metal–oxide RRAM. *Proceedings of the IEEE*, 100(6), pp.1951-1970.

- [30] Ye, C., Wu, J., He, G., Zhang, J., Deng, T., He, P. and Wang, H., 2016. Physical mechanism and performance factors of metal oxide based resistive switching memory: a review. *Journal of Materials Science & Technology*, 32(1), pp.1-11.

- [31] Kumar, D., Aluguri, R., Chand, U. and Tseng, T.Y., 2017. Metal oxide resistive switching memory: materials, properties and switching mechanisms. *Ceramics International*, *43*, pp.S547-S556.

- [32] Wu, X., Ge, R., Chen, P.A., Chou, H., Zhang, Z., Zhang, Y., Banerjee, S., Chiang, M.H., Lee, J.C. and Akinwande, D., 2019. Thinnest nonvolatile memory based on monolayer h-BN. Advanced Materials, 31(15), p.1806790.

- [33] Kim, M., Ge, R., Wu, X., Lan, X., Tice, J., Lee, J.C. and Akinwande, D., 2018. Zero-static power radiofrequency switches based on MoS2 atomristors. *Nature communications*, 9(1), p.2524.

- [34] Ge, R., Wu, X., Kim, M., Shi, J., Sonde, S., Tao, L., Zhang, Y., Lee, J.C. and Akinwande, D., 2018. Atomistor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. *Nano letters*, 18(1), pp.434-441.