## **High-Level Synthesis for FPGAs: From Prototyping to Deployment**

Jason Cong<sup>1,2</sup>, *Fellow, IEEE*, Bin Liu<sup>1,2</sup>, Stephen Neuendorffer<sup>3</sup>, *Member, IEEE*, Juanjo Noguera<sup>3</sup>, Kees Vissers<sup>3</sup>, *Member, IEEE* and Zhiru Zhang<sup>1</sup>, *Member, IEEE*

<sup>1</sup>AutoESL Design Technologies, Inc. <sup>2</sup>University of California, Los Angeles <sup>3</sup>Xilinx, Inc.

Abstract—Escalating System-on-Chip design complexity is pushing the design community to raise the level of abstraction beyond RTL. Despite the unsuccessful adoptions of early generations of commercial high-level synthesis (HLS) systems, we believe that the tipping point for transitioning to HLS methodology is happening now, especially for FPGA designs. The latest generation of HLS tools has made significant progress in providing wide language coverage and robust compilation technology, platform-based modeling, advancement in core HLS algorithms, and a domain-specific approach. In this paper we use AutoESL's AutoPilot HLS tool coupled with domain-specific system-level implementation platforms developed by Xilinx as an example to demonstrate the effectiveness of state-of-art C-to-FPGA synthesis solutions targeting multiple application domains. Complex industrial designs targeting Xilinx FPGAs are also presented as case studies, including comparison of HLS solutions versus optimized manual designs.

Index Terms—Domain-specific design, field-programmable gate array (FPGA), high-level synthesis (HLS), quality of results (QoR).

#### I. INTRODUCTION

THE RAPID INCREASE of complexity in System-on-a-Chip (SoC) design has encouraged the design community to seek design abstractions with better productivity than RTL. Electronic system-level (ESL) design automation has been widely identified as the next productivity boost for the semiconductor industry, where HLS plays a central role, enabling the automatic synthesis of high-level, untimed or partially timed specifications (such as in C or SystemC) to a low-level cycle-accurate register-transfer level (RTL) specifications for efficient implementation in ASICs or FPGAs. This synthesis can be optimized taking into account the performance, power, and cost requirements of a particular system.

Despite the past failure of the early generations of commercial HLS systems (started in the 1990s), we see a rapidly growing demand for innovative, high-quality HLS solutions for the following reasons:

• Embedded processors are in almost every SoC: With the coexistence of micro-processors, DSPs, memories and custom logic on a single chip, more software elements are involved in the process of designing a modern embedded system. An automated HLS flow allows designers to specify design functionality in highlevel programming languages such as C/C++ for both embedded software and customized hardware logic on the SoC. This way, they can quickly experiment with

- different hardware/software boundaries and explore various area/power/performance tradeoffs from a single common functional specification.

- Huge silicon capacity requires a higher level of abstraction: Design abstraction is one of the most effective methods for controlling complexity and improving design productivity. For example, the study from NEC [90] shows that a 1M-gate design typically requires about 300K lines of RTL code, which cannot be easily handled by a human designer. However, the code density can be easily reduced by 7X to 10X when moved to high-level specification in C, C++, or SystemC. In this case, the same 1M-gate design can be described in 30K to 40K lines of lines of behavioral description, resulting in a much reduced design complexity.

- Behavioral IP reuse improves design productivity: In addition to the line-count reduction in design specifications, behavioral synthesis has the added value of allowing efficient reuse of behavioral IPs. As opposed to RTL IP which has fixed microarchitecture and interface protocols, behavioral IP can be retargeted to different implementation technologies or system requirements.

- Verification drives the acceptance of high-level specification: Transaction-level modeling (TLM) with SystemC [107] or similar C/C++ based extensions has become a very popular approach to system-level verification [35]. Designers commonly use SystemC TLMs to describe virtual software/hardware platforms, which serve three important purposes: early embedded software development, architectural modeling and exploration, and functional verification. The wide availability of SystemC functional models directly drives the need for SystemC-based HLS solutions, which can automatically generate RTL code through a series of formal constructive transformations. This avoids slow and error-prone manual RTL re-coding, which is the standard practice in the industry today.

- Trend towards extensive use of accelerators and heterogeneous SoCs: Many SoCs, or even CMPs (chip multi-processors) move towards inclusion of many accelerators (or algorithmic blocks), which are built with custom architectures, largely to reduce power compared to using multiple programmable processors. According to ITRS prediction [109], the number of on-chip accelerators will reach 3000 by 2024. In FPGAs, custom

architecture for algorithmic blocks provides higher performance in a given amount of FPGA resources than synthesized soft processors. These algorithmic blocks are particularly appropriate for HLS.

Although these reasons for adopting HLS design methodology are common to both ASIC and FPGA designers, we also see additional forces that push the FPGA designers for faster adoption of HLS tools.

- Less pressure for formal verification: The ASIC manufacturing cost in nanometer IC technologies is well over \$1M [109]. There is tremendous pressure for the ASIC designers to achieve first tape-out success. Yet formal verification tools for HLS are not mature, and simulation coverage can be limited for multi-million gate SOC designs. This is a significant barrier for HLS adoption in the ASIC world. However, for FPGA designs, in-system simulation is possible with much wider simulation coverage. Design iterations can be done quickly and inexpensively without huge manufacturing costs.

- Ideal for platform-based synthesis: Modern FPGAs embed many pre-defined/fabricated IP components, such as arithmetic function units, embedded memories, embedded processors, and embedded system buses. These pre-defined building blocks can be modeled precisely ahead of time for each FPGA platform and, to a large extent, confine the design space. As a result, it is possible for modern HLS tools to apply a platform-based design methodology [51] and achieve higher quality of results (QoR).

- More pressure for time-to-market: FPGA platforms are often selected for systems where time-to-market is critical, in order to avoid long chip design and manufacturing cycles. Hence, designers may accept increased performance, power, or cost in order to reduce design time. As shown in Section IX, modern HLS tools put this tradeoff in the hands of a designer allowing significant reduction in design time or, with additional effort, quality of result comparable to hand-written RTL.

- Accelerated or reconfigurable computing calls for C/C++ based compilation/synthesis to FPGAs: Recent advances in FPGAs have made reconfigurable computing platforms feasible to accelerate many high-performance computing (HPC) applications, such as image and video processing, financial analytics, bioinformatics, and scientific computing applications. Since RTL programming in VHDL or Verilog is unacceptable to most application software developers, it is essential to provide a highly automated compilation/synthesis flow from C/C++ to FPGAs.

As a result, a growing number of FPGA designs are produced using HLS tools. Some example application domains include 3G/4G wireless systems [38][81], aerospace applications [75], image processing [27], lithography simulation [13], and cosmology data analysis [52]. Xilinx is also in the process of incorporating HLS solutions in their Video Development Kit [116] and DSP Develop Kit [97] for

all Xilinx customers.

This paper discusses the reasons behind the recent success in deploying HLS solutions to the FPGA community. In Section II we review the evolution of HLS systems and summarize the key lessons learned. In Sections IV-VIII, using a state-of-art HLS tool as an example, we discuss some key reasons for the wider adoption of HLS solutions in the FPGA design community, including wide language coverage and robust compilation technology, platform-based modeling, advancement in core HLS algorithms, improvements on simulation and verification flow, and the availability of domain-specific design templates. Then, in Section IX, we present the HLS results on several real-life industrial designs and compare with manual RTL implementations. Finally, in Section X, we conclude the paper with discussions of future challenges and opportunities.

#### II. EVOLUTION OF HIGH-LEVEL SYNTHESIS FOR FPGA

In this section we briefly review the evolution of high-level synthesis by looking at representative tools. Compilers for high-level languages have been successful in practice since the 1950s. The idea of automatically generating circuit implementations from high-level behavioral specifications arises naturally with the increasing design complexity of integrated circuits. Early efforts (in the 1980s and early 1990s) on high-level synthesis were mostly research projects, where multiple prototype tools were developed to call attention to the methodology and to experiment with various algorithms. Most of those tools, however, made rather simplistic assumptions about the target platform and were not widely used. Early commercialization efforts in the 1990s and early 2000s attracted considerable interest among designers, but also failed to gain wide adoption, due in part to usability issues and poor quality of results. More recent efforts in high-level synthesis have improved usability by increasing input language coverage and platform integration, as well as improving quality of results.

## A. Early Efforts

Since the history of HLS is considerably longer than that of FPGAs, most early HLS tools targeted ASIC designs. A pioneering high-level synthesis tool, CMU-DA, was built by researchers at Carnegie Mellon University in the 1970s [29][71]. In this tool the design is specified at behavior level using the ISPS (Instruction Set Processor Specification) language [4]. It is then translated into an intermediate dataflow representation called the Value Trace [79] before producing RTL. Many common code-transformation techniques in software compilers, including dead-code elimination, constant propagation, redundant sub-expression elimination, code motion, and common sub-expression extraction could be performed. The synthesis engine also included many steps familiar in hardware synthesis, such as datapath allocation, module selection, and controller generation. CMU-DA also supported hierarchical design and included a simulator of the original ISPS language. Although many of the methods used were very preliminary, the

innovative flow and the design of toolsets in CMU-DA quickly generated considerable research interest.

In the subsequent years in the 1980s and early 1990s, a number of similar high-level synthesis tools were built, mostly for research. Examples of academic efforts include the ADAM system developed at the University of Southern California [37][46], HAL developed at Bell-Northern Research [72], MIMOLA developed at University of Kiel, Germany [62], the Hercules/Hebe high-level synthesis system (part of the Olympus system) developed at Stanford University [24][25] [55], the Hyper/Hyper-LP system developed at University of California, Berkeley [10][77]. Industry efforts include Cathedral/Cathedral-II and their successors developed at IMEC [26], the IBM Yorktown Silicon Compiler [11] and the GM BSSC system [92], among many others. Like CMU-DA, these tools typically decompose the synthesis task into a few steps, including code transformation, module selection, operation scheduling, datapath allocation, and controller generation. Many fundamental algorithms addressing these individual problems were also developed. For example, the list scheduling algorithm and its variants are widely used to solve scheduling problems with resource constraints [70]; the forcedirected scheduling algorithm developed in HAL [73] is able to optimize resource requirements under a performance constraint; the path-based scheduling algorithm in the Yorktown Silicon Compiler is useful to optimize performance with conditional branches [12]. The Sehwa tool in ADAM is able to generate pipelined implementations and explore the design space by generating multiple solutions [69]. The relative scheduling technique developed in Hebe is an elegant way to handle operations with unbounded delay [56]. Conflictgraph coloring techniques were developed and used in several systems to share resources in the datapath [57][72].

These early high-level tools often used custom languages for design specification. Besides the ISPS language used in CMD-DA, a few other languages were notable. HardwareC is a language designed for use in the Hercules system [54]. Based on the popular C programming language, it supports both procedural and declarative semantics and has built-in mechanisms to support design constraints and interface specifications. This is one of the earliest C-based hardware synthesis languages for high-level synthesis and is interesting to compare with similar languages later. The Silage language used in Cathedral/Cathedral-II was specifically designed for the synthesis of digital signal processing hardware [26]. It has built-in support for customized data types, and allows easy transformations [77][10]. The Silage language, along with the Cathedral-II tool, represented an early domain-specific approach in high-level synthesis.

These early research projects helped to create a basis for algorithmic synthesis with many innovations, and some were even used to produce real chips. However, these efforts did not lead to wide adoption among designers. A major reason is that the methodology of using RTL synthesis was not yet widely accepted at that time and RTL synthesis tools were not yet mature. Thus, high-level synthesis, built on top of RTL synthesis, did not have a sound foundation in practice. In

addition, simplistic assumptions were often made in these early systems—many of them were "technology independent" (such as Olympus), and inevitably led to suboptimal results.

With improvements in RTL synthesis tools and the wide adoption of RTL-based design flows in the 1990s, industrial deployment of high-level synthesis tools became more practical. Proprietary tools were built in major semiconductor design houses including IBM [5], Motorola [58], Philips [61], and Simens [6]. Major EDA vendors also began to provide commercial high-level synthesis tools. In 1995, Synopsys announced Behavioral Compiler [88], which generates RTL implementations from behavioral HDL code and connects to downstream tools. Similar tools include Monet from Mentor Graphics [33] and Visual Architect from Cadence [43]. These tools received wide attention, but failed to widely replace RTL design. One reason is due to the use of behavioral HDLs as the input language, which is not popular among algorithm and system designers.

### B. Recent efforts

Since 2000, a new generation of high-level synthesis tools has been developed in both academia and industry. Unlike many predecessors, most of these tools focus on using C/C++ or C-like languages to capture design intent. This makes the tools much more accessible to algorithm and system designers compared to previous tools that only accept HDL languages. It also enables hardware and software to be built using a common model, facilitating software/hardware co-design and co-verification. The use of C-based languages also makes it easy to leverage the newest technologies in software compilers for parallelization and optimization in the synthesis tools.

In fact, there has been an ongoing debate on whether C-based languages are proper choices for HLS [31][78]. Despite the many advantages of using C-based languages, opponents often criticize C/C++ as languages only suitable for describing sequential software that runs on microprocessors. Specifically, the deficiencies of C/C++ include the following:

- (i) Standard C/C++ lack built-in constructs to explicitly specify bit accuracy, timing, concurrency, synchronization, hierarchy, etc., which are critical to hardware design.

- (ii) C and C++ have complex language constructs, such as pointers, dynamic memory management, recursion, polymorphism, etc., which do have efficient hardware counterparts and lead to difficulty in synthesis.

To address these deficiencies, modern C-based HLS tools have introduced additional language extensions and restrictions to make C inputs more amenable to hardware synthesis. Common approaches include both restriction to a synthesizable subset that discourages or disallows the use of dynamic constructs (as required by most tools) and introduction of hardware-oriented language extensions (HardwareC [54], SpecC [34], Handel-C [95]), libraries (SystemC [107]), and compiler directives to specify concurrency, timing, and other constraints. For example, Handel-C allows the user to specify clock boundaries explicitly in the source code. Clock edges and events can also be explicitly specified in SpecC and SystemC. Pragmas and

directives along with a subset of ANSI C/C++ are used in many commercial tools. An advantage of this approach is that the input program can be compiled using standard C/C++ compilers without change, so that such a program or a module of it can be easily moved between software and hardware and co-simulation of hardware and software can be performed without code rewriting. At present, most commercial HLS tools use some form of C-based design entry, although tools using other input languages (e.g., BlueSpec [102], Esterel [30], Matlab [42], etc.) also exist.

Another notable difference between the new generation of high-level synthesis tools and their predecessors is that many tools are built targeting implementation on FPGA. FPGAs have continually improved in capacity and speed in recent years, and their programmability makes them an attractive platform for many applications in signal processing, communication, and high-performance computing. There has been a strong desire to make FPGA programming easier, and many high-level synthesis tools are designed to specifically target FPGAs, including ASC [64], CASH [9], C2H from Altera [98], DIME-C from Nallatech [112], GAUT [22], Handel-C compiler (now part of Mentor Graphics DK Design Suite) [95], Impulse C [74], ROCCC [87][39], SPARK [41][40], Streams-C compiler [36], and Trident [82][83], . ASIC tools also commonly provide support for targeting an FPGA tool flow in order to enable system emulation.

Among these high-level synthesis tools, many are designed to focus on a specific application domain. For example, the Trident compiler, developed at Los Alamos National Lab, is an open-source tool focusing on the implementation of floating-point scientific computing applications on FPGA. Many tools, including GAUT, Streams-C, ROCCC, ASC, and Impulse C, target streaming DSP applications. Following the tradition of Cathedral, these tools implement architectures consisting of a number of modules connected using FIFO channels. Such architectures can be integrated either as a standalone DSP pipeline, or integrated to accelerate code running on a processor (as in ROCCC).

As of 2010, major commercial C-based high-level synthesis tools include AutoESL's AutoPilot [94] (originated from UCLA xPilot project [17]), Cadence's C-to-Silicon Compiler [3][103], Forte's Cynthesizer [65], Mentor's Catapult C [7], NEC's Cyber Workbench [89][91], and Synopsys Synphony C [115] (formerly Synfora's PICO Express, originated from a long range research effort in HP Labs [49]).

## C. Lessons Learned

Despite extensive development efforts, most commercial HLS efforts have failed. We believe that past failures are due to one or several of the following reasons:

Lack of comprehensive design language support: The

first generation of the HLS synthesis tools could not

synthesize high-level programming languages. Instead,

untimed or partially timed behavioral HDL was used.

Such design entry marginally raised the abstraction

level, while imposing a steep learning curve on both

software and hardware developers.

Although early C-based HLS technologies have considerably improved the ease of use and the level of design abstraction, many C-based tools still have glaring deficiencies. For instance, C and C++ lack the necessary constructs and semantics to represent hardware attributes such as design hierarchy, timing, synchronization, and explicit concurrency. SystemC, on the other hand, is ideal for system-level specification software/hardware co-design. However, it is foreign to algorithmic designers and has slow simulation speed compared to pure ANSI C/C++descriptions. Unfortunately, most early HLS solutions commit to only one of these input languages, restricting their usage to niche application domains.

- Lack of reusable and portable design specification: Many HLS tools have required users to embed detailed timing and interface information as well as the synthesis constraints into the source code. As a result, the functional specification became highly tool-dependent, target-dependent, and/or implementation-platform dependent. Therefore, it could not be easily ported to alternative implementation targets.

- Narrow focus on datapath synthesis: Many HLS tools focus primarily on datapath synthesis, while leaving other important aspects unattended, such as interfaces to other hardware/software modules and platform integration. Solving the system integration problem then becomes a critical design bottleneck, limiting the value in moving to a higher-level design abstraction for IP in a design.

- Lack of satisfactory quality of results (QoR): When early generations of HLS tools were introduced in the mid-1990s to early 2000s, the EDA industry was still struggling with timing closure between logic and physical designs. There was no dependable RTL to GDSII foundation to support HLS, which made it difficult to consistently measure, track, and enhance HLS results. Highly automated RTL to GDSII solutions only became available in late 2000s (e.g., provided by the IC Compiler from Synopsys [114] or the BlastFusion/Talus from Magma [111]). Moreover, many HLS tools are weak in optimizing real-life design metrics. For example, the commonly used algorithms mainly focus on reducing functional unit count and latency, which do not necessarily correlate to actual silicon area, power, and performance. As a result, the final implementation often fails to meet timing/power requirements. Another major factor limiting quality of result was the limited capability of HLS tools to exploit performance-optimized and power-efficient IP blocks on a specific platform, such as the versatile DSP blocks and on-chip memories on modern FPGA platforms. Without the ability to match the QoR achievable with an RTL design flow, most designers were unwilling to explore potential gains in design productivity.

- Lack of a compelling reason/event to adopt a new design methodology: The first-generation HLS tools

were clearly ahead of their time, as the design complexity was still manageable at the register transfer level in late 1990s. Even as the second-generation of HLS tools showed interesting capabilities to raise the level of design abstraction, most designers were reluctant to take the risk of moving away from the familiar RTL design methodology to embrace a new unproven one, despite its potential large benefits. Like any major transition in the EDA industry, designers needed a compelling reason or event to push them over the "tipping point," i.e., to adopt the HLS design methodology.

Another important lesson learned is that tradeoffs must be made in the design of the tool. Although a designer might wish for a tool that takes any input program and generates the "best" hardware architecture, this goal is not generally practical for HLS to achieve. Whereas compilers for processors tend to focus on local optimizations with the sole goal of increasing performance, HLS tools must automatically balance performance and implementation cost using global optimizations. However, it is critical that these optimizations be carefully implemented using scalable and predictable algorithms, keeping tool runtimes acceptable for large programs and the results understandable by designers. Moreover, in the inevitable case that the automatic optimizations are insufficient, there must be a clear path for a designer to identify further optimization opportunities and execute them by rewriting the original source code.

Hence, it is important to focus on several design goals for a high-level synthesis tool:

- 1. Capture designs at a bit-accurate, algorithmic level in C code. The code should be readable by algorithm specialists.

- 2. Effectively generate efficient parallel architectures with minimal modification of the C code, for parallelizable algorithms.

- Allow an optimization-oriented design process, where a designer can improve the performance of the resulting implementation by successive code modification and refactoring.

- Generate implementations that are competitive with synthesizable RTL designs after automatic and manual optimization.

We believe that the tipping point for transitioning to HLS methodology is happening now, given the reasons discussed in Section I and the conclusions by others [14][84]. Moreover, we are pleased to see that the latest generation of HLS tools has made significant progress in providing wide language coverage and robust compilation technology, platform-based modeling, and advanced core HLS algorithms. We shall discuss these advancements in more detail in the next few sections.

# III. CASE STUDY OF STATE-OF-ART OF HIGH-LEVEL SYNTHESIS FOR FPGAS

AutoPilot is one of the most recent HLS tools, and is representative of the capabilities of the state-of-art commercial

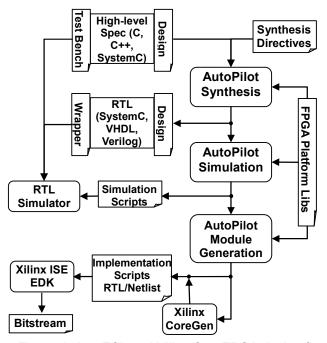

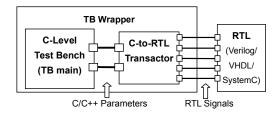

HLS tools available today. Figure 1 shows the AutoESL AutoPilot development flow targeting Xilinx FPGAs. AutoPilot accepts synthesizable ANSI C, C++, and OSCI SystemC (based on the synthesizable subset of the IEEE-1666 standard [113]) as input and performs advanced platform-based code transformations and synthesis optimizations to generate optimized synthesizable RTL.

AutoPilot outputs RTL in Verilog, VHDL or cycle-accurate SystemC for simulation and verification. To enable automatic co-simulation, AutoPilot creates test bench wrappers and transactors in SystemC so that designers can leverage the original test framework in C/C++/SystemC to verify the correctness of the RTL output. These SystemC wrappers connect high-level interfacing objects in the behavioral test bench with pin-level signals in RTL. AutoPilot also generates appropriate simulation scripts for use with 3<sup>rd</sup>-party RTL simulators. Thus designers can easily use their existing simulation environment to verify the generated RTL.

Figure 1. AutoESL and Xilinx C-to-FPGA design flow.

In addition to generating RTL, AutoPilot also creates synthesis reports that estimate FPGA resource utilization, as well as the timing, latency and throughput of the synthesized design. The reports include a breakdown of performance and area metrics by individual modules, functions and loops in the source code. This allows users to quickly identify specific areas for QoR improvement and then adjust synthesis directives or refine the source design accordingly.

Finally, the generated HDL files and design constraints feed into the Xilinx RTL tools for implementation. The Xilinx ISE tool chain (such as CoreGen, XST, PAR, etc.) and Embedded Development Kit (EDK) are used to transform that RTL implementation into a complete FPGA implementation in the form of a bitstream for programming the target FPGA platform.

#### IV. SUPPORT OF HIGH-LEVEL PROGRAMMING MODELS

#### A. Robust support of C/C++ based synthesis

Comprehensive language coverage is essential to enabling wide acceptance of C/C++ based design and synthesis. The reasons are twofold:

- Reduced verification effort: A broad synthesizable subset minimizes the required code changes to convert the reference C source into a synthesizable specification. This effectively improves the design productivity and reduces or eliminates the additional verification effort to ensure equivalence between the synthesizable code and the original design.

- Improved design quality: Comprehensive language support allows designers to take full advantage of rich C/C++ constructs to maximize simulation speed, design modularity and reusability, as well as synthesis QoR.

However, it is quite challenging to compile an input specification in software C language, which is known for its highly flexible syntax and semantic ambiguities, into a well-structured and well-optimized hardware described in HDL.

Table 1. Useful language features for effective C/C++based design and synthesis.

| Language | Constructs                        | Benefits                                                                  |  |  |

|----------|-----------------------------------|---------------------------------------------------------------------------|--|--|

| C        | Arbitrary-precision integer types | Bit-accurate design<br>QoR                                                |  |  |

|          | Floating-point types              | Floating-point arithmetic                                                 |  |  |

|          | Function calls                    | Modular design hierarchy                                                  |  |  |

|          | Pointers                          | Efficiency and flexibility                                                |  |  |

|          | Structs & unions                  | Data encapsulation                                                        |  |  |

| C++      | Fixed-point types                 | Fixed-point arithmetic Accuracy-cost tradeoff                             |  |  |

|          | Templates                         | Parameterizable design                                                    |  |  |

|          | Classes                           | Object-oriented modeling (encapsulation, inheritance, polymorphism, etc.) |  |  |

| SystemC  | Modules & processes               | Coarse-grained concurrency                                                |  |  |

|          | Clocks                            | Custom protocol<br>Multi-clock design                                     |  |  |

|          | TLM                               | Fast simulation                                                           |  |  |

In fact, many early C-based synthesis tools only handle a very limited language subset, which typically includes the native integer data types (e.g., *char*, *short*, *int*, etc.), one-dimensional arrays, *if-then-else* conditionals, and *for* loops. Such language coverage is far from sufficient to allow complex large-scale designs. As shown in Table 1, supporting more advanced language features in C, C++ and SystemC is critical to raising the level of design abstraction and enabling efficient high-level synthesis.

AutoPilot accepts three standard C-based design entries in ANSI C, C++ and SystemC. It provides robust synthesis

technologies to efficiently handle different aspects of the C/C++ language, such as data type synthesis (for both primitive and composite types), pointer synthesis, memory synthesis, control synthesis, loop synthesis, modular hierarchy synthesis (for function, class, and concurrent modules), and interface synthesis (for function parameters and global variables).

Designers can fully control the data precisions of a C/C++ specification. AutoPilot directly supports single- and double-precision floating-point types and efficiently utilizes the floating-point IPs provided by the FPGA platforms. Common floating-point math routines (e.g., square root, exponentiation, logarithm, etc.) can be mapped to high-quality platform-specific IPs.

In addition, AutoPilot has the capabilities to simulate and synthesize arbitrary-precision integers ( $ap\_int$ ) and fixed-point data types ( $ap\_fixed$ ). The arbitrary-precision fixed-point ( $ap\_fixed$ ) data types support all common algorithmic operations. With this library, designers can explore the accuracy and cost tradeoff by modifying the resolution and fixed-point location and experimenting with various quantization and saturation modes.

AutoPilot also supports the OCSI synthesizable subset [113] for SystemC synthesis. Designers can make use of SystemC bit-accurate data types (sc\_int/sc\_uint, sc\_bigint/sc\_biguint, and sc\_fixed/sc\_ufixed) to define the data precisions. Multi-module hierarchical designs can be specified and synthesized with multiple concurrent processes running inside each module.

## B. Use of state-of-the-art compiler technologies

AutoPilot tightly integrates the LLVM compiler infrastructure [59][110] to leverage leading-edge compiler technologies. LLVM features a GCC-based C/C++ front end called *llvm-gcc* and a newly developed source code front end for C/C++ and Object C/C++ called *Clang*, a virtual instruction set based on a type-safe static single-assignment (SSA) form [23], a rich set of code analyses and transformation passes, and various back ends for common target machines.

AutoPilot uses the *llvm-gcc* front end to obtain an intermediate representation (IR) based on the LLVM instruction set. On top of this IR, AutoPilot performs a variety of compiler transformations to aggressively optimize the input specification. The optimization focuses on reducing code complexity and redundancy, maximizing data locality, and exposing parallelism.

In particular, the following classes of transformations and analyses have shown to be very useful for hardware synthesis:

- SSA-based code optimizations such as constant propagation, dead code elimination, and redundant code elimination based on global value numbering [2].

- Expression rewriting such as strength reduction and arithmetic simplification to replace expensive operations and expressions with simpler ones (e.g.,  $x^0/2^n = x & (2^n 1)$ , 3\*x-x = x << 1).

- Range analysis and bitwidth analysis [80][21] that

extract and propagate the value range information throughout the program to reduce bitwidths of variables and operations.

- Sophisticated alias analysis and memory dependence analysis [50] that analyzes data and control dependences to discover parallelism between pointer and array accesses.

- Memory optimizations such as memory reuse, array scalarization, and array partitioning [19] to reduce the number of memory accesses and improve memory bandwidth.

- Loop transformations such as unrolling, loop fusion, and loop rotation to expose loop-level parallelism [50].

- Function optimizations such as inlining and pointer-toscalar argument promotion to enable code optimization across the function boundaries.

It is worth noting that the LLVM-based IR is in a languageagnostic format. In other words, the code can be optimized without considering the source language. As a result, the same set of analyses and optimizations on this representation can be shared and taken advantage of by many different language front ends.

Furthermore, unlike other conventional C/C++ compilers, which are typically designed to optimize with the native data types (e.g., *char*, *short*, *int*, *long*, etc.), LLVM and AutoPilot compilation and transformation procedures are fully bit accurate. This is a significant advantage for hardware synthesis since bit-level redundancy and parallelism can be well optimized and well exploited [93].

#### V. PLATFORM-BASED APPROACH

### A. Platform modeling for Xilinx FPGAs

AutoPilot uses detailed target platform information to carry out informed and target-specific synthesis and optimization. The platform specification describes the availabilities and characteristics of important system building blocks, including the available computation resources, memory resources, and communication interfaces on a given Xilinx FPGA device.

Component pre-characterization is involved in the modeling process. Specifically, it characterizes the delay, area, and power for each type of hardware resource, such as arithmetic units (e.g., adders and multipliers), memories (e.g., RAMs, ROMs, and registers), steering logic (multiplexors), and interface logic (e.g., FIFOs and bus interface adapters). The delay/area/power characteristic curves are derived by varying the bit widths, number of input and output ports, pipeline intervals, and latencies. The resulting characterization data is then used to make implementation choices during synthesis.

Notably, the cost of implementing hardware on FPGAs is often different from that for ASIC technology. For instance, most designs include multiplexors to route data to different points in a design, share hardware resources, and initialize the state of the system. On FPGAs, multiplexors typically have the same cost and delay as an adder (approximately one LUT/output). In some cases, however, a multiplexor can merge with other logic, such as a downstream adder or

multiplexor, resulting in no additional hardware cost. In contrast, in ASIC technology, multiplexors are typically significantly less expensive than adders and other arithmetic operations and this cost cannot typically be eliminated by technology mapping. As a result, understanding the cost and delay of multiplexing operations is critical to building optimized FPGA designs.

FPGA technology also features heterogeneous on-chip resources, including not only LUTs and flip flops but also other prefabricated architecture blocks such as DSP48s and Block RAMs. Understanding the tradeoff between these heterogeneous resources is critical for efficient FPGA mapping. For instance, in FPGAs logic functions are significantly more expensive relative to memory than in ASIC technology, since logic functions must be implemented using LUTs and flip flops in the FPGA fabric whereas memory is usually implemented using Block RAMs which exist as customized SRAM cells in the FPGA. Furthermore, smaller memories and shift registers may be more efficiently mapped to LUT cells or flip flops in the FPGA than to Block RAM, adding additional complexity for memory characterization.

Such FPGA-specific platform information is carefully modeled for each and every FPGA device families, and considered by AutoPilot during synthesis for performance and area tradeoff. In addition, AutoPilot has the capability of detecting certain computation patterns and mapping a group of operations to platform-specific architecture blocks, such as DSP48 blocks, or pre-defined customer IPs.

## B. Integration with Xilinx toolset

In order to raise the level of design abstraction more completely, AutoPilot attempts to hide details of the downstream RTL flow from users as much as possible. Otherwise, a user may be overwhelmed by the details of vendor-specific tools such as the formats of constraint and configuration files, implementation and optimization options, or directory structure requirements.

As shown in Figure 1, AutoPilot implements an end-to-end C-to-FPGA synthesis flow integrated with the Xilinx toolset in several areas:

- **ISE integration**: AutoPilot automatically generates scripts and constraints for Xilinx ISE from the high-level constraints entered in AutoPilot. AutoPilot can also directly invoke ISE from within the tool to execute the entire C-to-FPGA flow and extract the exact resource utilization and the final timing from the ISE reports. For advanced users who are familiar with the Xilinx tool flow, AutoPilot also provides options to tune the default implementation and optimization settings, such as I/O buffer insertion, register duplication/balancing, and place-and-route effort.

- CoreGen integration: AutoPilot can automatically generate optimized IP blocks, such as memories, FIFOs, and floating-point units, using Xilinx Core Generator (CoreGen). In some cases, the CoreGen implementations are superior to the comparable functions implemented through logic synthesis

resulting in better QoR. The resulting CoreGen netlists are also incorporated and encapsulated without further user intervention.

• EDK integration: The hardware modules synthesized by AutoPilot can also be integrated into Xilinx EDK environment for system-level hardware/software codesign and exploration. Specifically, AutoPilot is capable of generating various bus interfaces, such as Xilinx Fast Serial Link (FSL) and Processor Local Bus (PLB) for integrating with MicroBlaze and PowerPC processors and Xilinx Native Port Interface (NPI) for integrating with external memory controllers. AutoPilot instantiates these interfaces along with adapter logic and appropriate EDK meta-information to enable a generated module can be quickly connected in an EDK system.

## VI. ADVANCES IN SYNTHESIS AND OPTIMIZATION ALGORITHMS

In this section we highlight some recent algorithmic advancement in HLS that we believe are important factors in improving the quality of results of the latest HLS tools and helping them to produce results that are competitive with manual designs.

## A. Efficient mathematical programming formulations to scheduling

Classical approaches to the scheduling problem in highlevel synthesis use either conventional heuristics such as list scheduling [1] and force-directed scheduling [73], which often lead to sub-optimal solutions, due to the nature of local optimization methods, or exact formulations such as integerlinear programming [45], which can be difficult to scale to large designs. Recently, an efficient and scalable system of difference constraint (SDC) based linear-programming formulation for operation scheduling has been proposed [15]. Unlike previous approaches where using  $O(m \times n)$  binary variables to encode a scheduling solution with n operations and m steps [45], SDC uses a continuous representation of time with only O(n) variables: for each operation i, a scheduling variable  $s_i$  is introduced to represent the time step at which the operation is scheduled. By limiting each constraint to integer-difference form, i.e.,

$$s_i - s_j \le d_{ij}$$

where  $d_{ij}$  is an integer. It is shown that a totally unimodular constraint matrix can be obtained. A totally unimodular matrix defined as a matrix whose every square submatrix has a determinant of 0 or  $\pm 1$ . A linear program with a totally unimodular constraint matrix is guaranteed to have integral solutions. Thus, an optimal integer solution can be obtained without expensive branch-and-bound procedures.

Many commonly encountered constraints in high-level synthesis can be expressed in the form of integer-difference constraints. For example, data dependencies, control dependencies, relative timing in I/O protocols, clock frequencies, and latency upper-bounds can all be expressed precisely. Some other constraints, such as resource usage,

cannot directly fit into the form. In such cases, approximations can be made to generate pair-wise which can then be expressed as integer-difference constraints. Other complex constraints can be handled in similar ways, using approximations or other heuristics. Thus, this technique provides a very flexible and versatile framework for various scheduling problems, and enables highly efficient solutions with polynomial time complexity.

# B. Soft constraints and applications for platform-based optimization

In a typical synthesis tool, design intentions are often expressed as constraints. While some of these constraints are essential for the design to function correctly, many others are not. For example, if the estimated propagation delay of a combinational path consisting of two functional units is 10.5 ns during scheduling, while the required cycle time is 10 ns, a simple method would forbid the two operations to execute in one clock cycle. However, it is possible that a solution with a slight nominal timing violation can still meet the frequency requirement, considering inaccuracy in interconnect delay estimation and various timing optimization procedures in later design stages, such as logic refactoring, retiming, and interconnect optimization. In this case, strict constraints eliminate the possibility of improving other aspects of the design with some reasonable estimated violations. In addition. inconsistencies in the constraint system can occur when many design intentions are added—after all, the design is often a process of making tradeoffs between conflicting objectives.

A solution to the above problems is proposed in [20] using soft constraints in the formulation of scheduling. The approach is based on the SDC formulation discussed in the preceding subsection, but allows some constraints to be violated. Consider the scheduling problem with both hard constraints and soft constraints formulated as follows.

minimize

$$c^T s$$

linear objective

subject to  $G s \le p$  hard constraints

$H s \le q$  soft constraints

Here G and H corresponds to the matrices representing hard constraints and soft constraints, respectively, and they are both totally unimodular as shown in [15]. Let  $H_j$  be the jth row of H, for each soft constraint  $H_j s \leq q_j$ , we introduce a violation variable  $v_j$  to denote the amount of violation and transform the soft constraint into two hard constraints as

$$H_{j}s - v_{j} \le q_{j}$$

$$-v_{i} \le 0$$

At the same time, we introduce a penalty term  $\phi_j(v_j)$  to the objective function, to minimize the cost for violating the *j*th soft constraint. The final formulation becomes the following.

minimize

$$c^T s + \sum_j \phi_j(v_j)$$

subject to  $Gs \leq p$

$Hs - v \leq q$

$-v \leq 0$

It can be shown that the new constraint matrix is also totally unimodular. If the amount of penalty is a convex function of the amount of violation, the problem can be solved optimally within polynomial time. Otherwise, convex approximations can be made in an iterative manner [20].

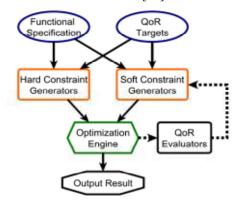

Figure 2. The structure of a scheduler using both hard constraints and soft constraints.

The overall flow of a scheduler using this method is shown in Figure 2. Hard constraints and soft constraints are generated based on the functional specification and QoR targets. The constraints are fed to an optimization engine that uses a mathematical programming solver. The soft constraints can be updated, based on existing results and possibly new design intentions. The use of soft constraints provides a way to handle multiple conflicting design intentions simultaneously, leading to efficient global optimization using a mathematical programming framework. This approach offers a powerful yet flexible framework to address various considerations in scheduling.

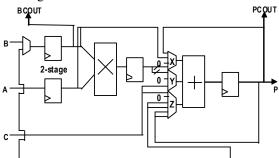

Figure 3. The Xilinx DSP48E block.

To illustrate the use of soft constraints in high-level synthesis for FPGAs, we apply it to the problem of efficient utilization of built-in fabrics on FPGA platforms. Take the DSP48E block in Xilinx Virtex 5 FPGAs for example: each of the DSP48E blocks (sketched in Figure 3) contains a multiplier and post-adder. allowing implementations of multiplication and multiply-accumulation. To fit the pattern of a DSP block, it is preferable that the operations are scheduled following certain relative cycle distances. Specifically, the addition should occur one cycle after the multiplication finishes to be mapped to the post-adder. In the constraint system, it is  $s_+ - s_\times \le l_\times$ , where  $l_\times$  is the number of stages the multiplication takes. These preferences can be nicely modeled by soft constraints as they are not required for

a correct implementation but highly preferred to achieve good OoR on FPGAs.

#### C. Pattern mining for efficient sharing

A typical target architecture for HLS may introduce multiplexers when functional units, storage units or interconnects are shared by multiple operations/variables in a time-multiplexed manner. However, multiplexers (especially large ones) can be particularly expensive on FPGA platforms. Thus, careless decisions on resource sharing could introduce more overhead than benefit. In [16] a pattern-based approach for resource sharing is proposed. The method tries to extract common structures or patterns in the data-flow graph, so that different instances of the same pattern can share resources with little overhead. The approach tolerates small variations on port, bitwidth, operation types, etc., by using the graph editing distance as a metric to measure the similarity of two patterns. A systematic method for subgraph enumeration is developed which avoids generating redundant subgraphs. Pruning techniques are proposed based on characteristic vectors and locality-sensitive hashing. Instances of the same pattern are scheduled in the same way and conflicts are avoided when possible so that they can share resources, leading to resource reductions. This technique has been extended to pattern extraction and sharing in CDFGs [18].

#### D. Memory analysis and optimizations

While application-specific computation platforms such as FPGAs typically have considerable computational capability, their performance is often limited by available communication or memory bandwidth. Typical FPGAs, such as the Xilinx Virtex series, have a considerable number of block RAMs. Using these RAMs effective is critical to meet performance target in many designs. This often requires partitioning elements of an array across multiple physical memory blocks to enable simultaneous access to different elements of the array.

In [19] a technique for automatic memory partitioning is proposed to increase throughput and reduce power for pipelined loops. It tightly integrates front-end transformations and operation scheduling in an iterative algorithm and has the ability to handle irregular array access, in addition to affine accesses. An example of memory partition is shown in Figure 4. Consider a loop that accesses array A with subscripts i,  $2 \times i + 1$ , and  $3 \times i + 1$ , in the ith iteration. When the array is partitioned into two banks, the first contains elements with even indices and the second contains those with odd indices. If the loop is targeted to be pipelined with the initiation interval of one, i.e., a new loop iteration starts every clock cycle, the schedule in (b) will lead to port conflicts, because (i+1) mod 2  $= (2 \times (i+1)+1) \mod 2 = (3 \times i+1) \mod 2$ , when i is even; this will lead to three simultaneous accesses to the first bank. On the other hand, the schedule in (c) can guarantee at most two simultaneous accesses. Because  $(i+2) \mod 2 \neq (3 \times i+1) \mod 2$ for any i, R1 and R3 will never access the same bank in the same cycle. The method in [19] presents a theorem to capture all possible reference conflicts under cyclic partitioning in a data structure called a conflict graph. Then, an iterative

algorithm is used to perform both scheduling and memory partitioning guided by the conflict graph.

Figure 4. An example of memory partitioning and scheduling for throughput optimization.

#### VII. ADVANCES IN SIMULATION AND VERIFICATION

Besides the many advantages of automated synthesis, such as quick design space exploration and automatic complex architectural changes like pipelining, resource sharing and scheduling, HLS also enables a more efficient debugging and verification flow at the higher abstraction levels. Since HLS provides an automatic path to implementable RTL from behavioral/functional models, designers do not have to wait until manual RTL models to be available to conduct verification. Instead, they can develop, debug and functionally verify a design at an earlier stage with high-level programming languages and tools. This can significantly reduce the verification effort due to the following reasons:

- (i) It is easier to trace, identify and fix bugs at higher abstraction levels with more compact and readable design descriptions.

- (ii) Simulation at the higher level is typically orders of magnitude faster than RTL simulation, allowing more comprehensive tests and greater coverage.

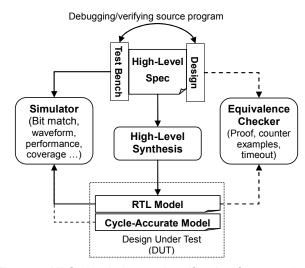

Figure 5 captures a typical simulation and verification framework offered by state-of-the-art C-based HLS tools. In this flow designers usually start from high-level specification in C/C++ or SystemC. They use software programming and debugging tools, such as GCC/GDB, Valgrind, or Visual Studio, to ensure that the design is sufficiently tested and verified against a properly constructed test bench. Once the input description to HLS is clean, designers can focus on the synthesis aspects and generate one or multiple versions of RTL code to explore the QoR tradeoffs under different

performance, area, and power constraints. To confirm the correctness of the final RTL designers can use the automatic co-simulation and/or formal equivalence checking provided by this framework.

Figure 5. HLS simulation and verification framework.

#### A. Automatic co-simulation

At present, simulation is the still prevalent technique to check if the resulting RTL complies with the high-level specification. To reduce effort spent on RTL simulation, the latest HLS technologies have made important improvements on automatic co-simulation [86][8][3], allowing direct reuse of the original test framework in C/C++ to verify the correctness of the synthesized RTL.

Figure 6. Automatic RTL test bench generation and connection in AutoPilot.

As an example, Figure 6 shows a block diagram describing how AutoPilot bridges a behavioral test bench (TB) and RTL with automatically constructed transactor and wrapper in SystemC. A C-to-RTL transactor is created to connect highlevel interfacing constructs (such as parameters and global variables) with pin-level signals in RTL. This step involves data type synthesis as well as interface synthesis since the transactor needs to correctly translate various C/C++ data types and handle different interface protocols such as handshaking, streaming, and memory mapped I/O. Additionally, a SystemC wrapper is generated that combines the C-level test bench and transactor. This wrapper also includes additional control logic manage communication between the testing module and the RTL design under test (DUT). For instance, a pipelined design may require that the test bench feed input data into the DUT at a

fixed rate.

This style of automatic co-simulation also helps designers avoid the timing-consuming manual creation of an RTL test bench. Along with the use of instrumentation and code coverage tools, this flow can provide additional performance and code coverage analyses on the RTL output. Many HLS tools also generate alternative cycle-accurate models (typically in SystemC) of the synthesized design that can be more quickly simulated than HDL.

### B. Equivalence Checking

While formal equivalence checking tools for RTL-to-RTL and RTL-to-gate comparisons have been in production use for years, high-level to RTL checking is still an evolving technology.

Nevertheless, promising progress on C-to-RTL equivalence checking has been made in recent years, especially from industry. For instance, the Sequential Logic Equivalence Checker from Calypto [105] can identify mismatches between a synthesizable C/C++/SystemC model and an RTL design without the need of a test bench. This tool has been integrated in several commercial HLS flows. Synopsys has also presented their Hector tool in [53], which integrates multiple bit-level and word-level equivalence checking techniques, such as ATPG, BDD, SAT, and SMT to address the system level to RTL formal verification problem.

An excellent survey of the sequential equivalence checking (SEC) techniques is given in [63], with discussions of their usage in the real-word high-level synthesis flows. As mentioned in this article, the current SEC technology can handle moderate design size with gate count between 500-700K gates and tolerate latency differences between high-level and RTL models on the order of hundreds of clock cycles. Beyond this range, further design partitioning is required to help the checker to reduce the verification complexity.

Currently, formal equivalence checking plays a supporting role in the verification flow for HLS. This is particularly true for FPGA designs, where in-system simulation is possible with much wider simulation coverage. Design iterations can be performed quickly and inexpensively without huge manufacturing cost.

## VIII. INTEGRATION WITH DOMAIN-SPECIFIC DESIGN PLATFORMS

In the end, the time-to-market of an FPGA system design is dependent on many factors, such as availability of reference designs, development boards, and in the end, FPGA devices themselves. Primarily, HLS only addresses one of these factors: the ability of a designer to capture new algorithms and implement an RTL architecture from the algorithm. Reducing the overall time-to-market requires not only reducing the design time, but also integrating the resulting design into a working system. This integration often includes a wide variety of system-level design concerns, including embedded software, system integration, and verification [104]. Hence, it is crucial that such integration can be performed as easily and as quickly as possible.

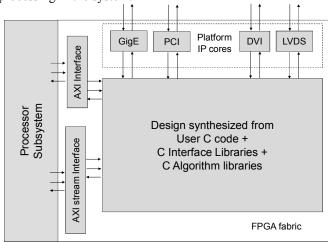

A view of an integrated design is shown in Figure 7. The interface cores (marked GigE, PCI, DVI, and LVDS in the figure) are implemented in low-level RTL code and are provided as encapsulated intellectual property (IP) cores. These cores tend to have tight requirements on circuit architecture in order to function correctly, and often have specific timing constraints, placement requirements, and instantiated architectural primitives. As a result, these cores are not easily amenable to high-level synthesis and form part of the system infrastructure of a design. Note, however, that these cores represent a small portion of the overall design synthesized in the FPGA, where system designers are not likely to have significant differentiating ability.

A second key part of system infrastructure is the processor subsystem shown on the left of Figure 7. Subsystem PSS is responsible for executing the relatively low-performance processing in the system.

Figure 7. Block diagram showing an algorithmic block integrated with a processor and I/O.

The portion of a design generated using HLS represents the bulk of the FPGA design and communicates with the system infrastructure through standardized wire-level interfaces, such as AXI4 memory-mapped and streaming interfaces [96] shown in Figure 7. These interfaces are abstracted in the C code to appropriate application-level interfaces, which can be simulated at a functional level in C code. In order to understand this abstract architecture model, we show some concrete examples of domain-specific design platforms that we used to build FPGA systems, one for cognitive radio designs and another for video applications.

## A. High-level design of cognitive radios project

Cognitive radio systems typically contain both computationally intensive processing with high data rates in the radio processing, along with complex, but relatively low-rate processing to control the radio processing. Such systems can be elegantly described and quickly simulated in algorithmic C code, enabling opportunities to improve the system-level management algorithms. However, efficiently building such systems in FPGAs can be complex, since they

involve close interaction between the processing code that must be implemented in the FPGA fabricto provide adequate performance, and the control code that would typically be implemented in an embedded processor. Although HLS provides a path to implementing the radio processing efficiently in FPGA logic, efficient interaction with the processor is an important part of the overall system complexity.

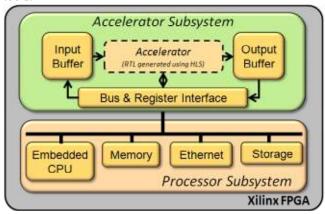

The target template architecture, shown in Figure 8, is divided in two subsystems: a processor subsystem and an accelerator subsystem. The processor subsystem contains standard hardware modules and is capable of running a standard embedded operating system, such as Linux. These modules include the embedded CPU (e.g., PowerPC or MicroBlaze), memory controller to interface to external DRAM, and I/O modules (e.g., Ethernet). The processor subsystem is responsible for two main tasks: executing the software runtime system in charge of the application control at runtime, and executing computationally non-intensive components in the application. The accelerator subsystem is used for implementing components with high computational requirements in hardware. In order to transfer data into and out of the accelerator subsystem, the accelerator block is connected to on-chip memories (i.e., standard interfaces). These on-chip memories are used as a shared-memory communication scheme between hardware and software components. The bus interface logic implements a DMA functionality to efficiently move data. A set of interface registers, accessible from software, is used for controlling hardware execution and accessing component parameters. The accelerator block is synthesized using the high-level synthesis

Figure 8. Radio processing architecture template.

To program the architecture, the application is captured as a pipeline of concurrent components or actors. Each actor conceptually executes either in the processor subsystem, or in the accelerator subsystem. Actors executing in the accelerator system also include a small proxy component executing in the processor, which is responsible for data transfer and synchronization with the FPGA hardware generated through HLS. This allows the component implementation to be completely abstracted, and a designer can implement individual components without knowing about the

implementation details of other components or how they are logically interconnected. The composition of actors and the dataflow between them is described in an XML file, enabling new compositions to be easily described. Components also expose a configuration interface with multiple parameters, allowing them to be reconfigured in an executing system by user-defined control code executing in the processor subsystem.

#### B. Video Starter Kit

Video processing systems implemented in FPGA include a wide variety of applications from embedded computer-vision and picture quality improvement to image and video compression. These systems also target a variety of end-markets ranging from television studio equipment to industrial imaging and consumer equipment, such as HDTVs and digital cameras. Typically these systems include two significant pieces of complexity. First, they must communicate by standardized interfaces, such as HD-SDI, HDMI, or V-by-one, with other equipment in order to be demonstrated. Secondly, they often perform inter-frame processing, which almost always requires a large frame-buffer implemented in cheap external memory, such as DDR2 SDRAM.

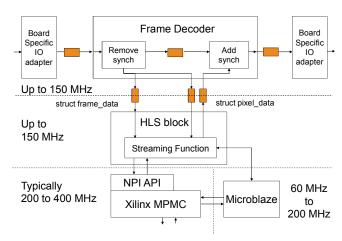

To address these complexities and make it relatively straightforward for designers to implement video processing applications and demonstrate them in real-time on development boards, we have leveraged a portable platform methodology. This platform is derived from the Xilinx EDK-based reference designs provided with the Xilinx Spartan 3ADSP Video Starter Kit and has been ported to several Xilinx Virtex 5 and Spartan 6 based development boards, targeting high-definition HD video processing with pixel clocks up to 150 MHz. A block diagram is shown in Figure 9.

Figure 9. Video processing architecture template.

Incoming video data is received using board and protocol specific interface adapters and formatted as a non-handshaked stream of RGB video data, with horizontal and vertical synchronization and data enable signals. When a board uses an external decoder chip which formats digital video in this way, such as the Spartan 3ADSP video Starter Kit, the IO adapter can often be very simple, requiring almost no FPGA logic. In

other cases, such as on the Xilinx University Program Atlys board [117] which implements HDMI interfaces entirely in FPGA logic, the interface logic can be more significantly complex.

The incoming video data is analyzed by the Frame Decoder block to determine the frame size of the incoming video, which is passed to the application block, enabling different video formats to be processed. The frame size, represented by *struct frame\_data*, is sent to the application block first, followed by the given number of active video pixels without synchronization signals, represented by *struct pixel\_data*. The synchronization signals themselves are encoded and delayed, before being reassembled with the processed video data and sent to the output video interface. This delay accommodates non-causal spatial filters with up to a small number of lines of delay, without requiring the output video to be shifted. Longer processing delays can be accommodated internally to the application block by a frame buffer by outputting the previously processed frame.

The application is typically partitioned between the Application Block, which is generated using HLS and the Microblaze control processor. In video systems, the control processor often handles processing that occurs at the frame rate (typically 60 or 120 frames per second for the majority of consumer video equipment), and can receive data analyzed from the incoming video, and generate parameter updates to the processing core. Simple processing tasks can be computed in the vertical blanking interval, while more complex tasks may require the entire frame time to compute, meaning that analysis of frame n is computed during the arrival of frame n+1 and the results used to update frame n+2.

The Application Block itself is capable of processing video pixels at the full rate of the incoming video data, typically as a streaming dataflow pipeline generated from multiple loops in C code. To meet the pixel-rate requirements of HDTV systems, the Application Block typically process one new pixel per clock cycle in consumer grade FPGAs, such as the Xilinx Spartan 6 family. Video line buffers are synthesized directly from embedded FPGA memories, expressed as arrays in C code.

The interface to external memory used for frame buffers is implemented using the Xilinx Multi-ported Memory Controller (MPMC) [118] which provides access to external memory to the Application Block and to the Microblaze control processor, if necessary. The MPMC provides a consistent user-level interface through the Native-Port Interface (NPI) [118] to a variety of memory technologies, abstracting the FPGA-architecture specific details of interfacing with correct timing to a particular external memory technology. NPI requires applications to explicitly specify large bursts in order to maximize memory bandwidth to burst-oriented memory technologies, such as DDR2 SDRAM. The RTL code generated by AutoPilot can leverage these bursts to directly implement video frame buffers and other patterns of memory accesses without a separate DMA engine.

#### IX. DESIGN EXPERIENCE AND RESULTS

In this section we summarize some recent design experiences using HLS for FPGA designs in the two application domains discussed in the preceding section and discuss the experimental results, especially in terms of the quality of results of HLS as compared to manual designs.

## A. Summary of BDTI HLS Certification

Xilinx has worked with BDTI Inc. [99] to implement an HLS Tool Certification Program [100]. This program was designed to compare the results of an HLS Tool and the Xilinx Spartan 3 FPGA that is part of the Video Starter Kit, with the result of a conventional DSP processor and with the results of a good manual RTL implementation. There were two applications used in this Certification Program, an optical flow algorithm, which is characteristic for a demanding image processing application and a wireless application (DQPSK) for which a very representative implementation in RTL was available. The results of the certification of the AutoPilot tool from AutoESL are available on the BDTI website [101].

Table 2. Quality of results for BDTI optical flow workflow operating point 2: maximum throughput, 1280x720 progressive scan. (Table reproduced from [101])

| Platform                                                                                | Chip<br>Unit Cost<br>(Qty<br>10K) | Maximum<br>Frames per<br>Second<br>(FPS) | Cost per<br>FPS<br>(Lower is<br>Better) |

|-----------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------|-----------------------------------------|

| AutoESL AutoPilot<br>plus Xilinx RTL<br>tools targeting the<br>Xilinx XC3D3400A<br>FPGA | \$26.65                           | 183 fps                                  | \$0.14                                  |

| Texas Instruments software development tools targeting TMS320DM6437 DSP processor       | \$21.25                           | 5.1 fps                                  | \$4.20                                  |

Results showing the maximum performance for the optical flow algorithm are shown in Table 2, comparing comparably priced consumer-grade FPGA and DSP targets. The AutoPilot implementation achieved approximately 30 times better throughput per dollar than the optimized DSP implementation. In addition, BDTI qualitatively assessed the "extent of modifications to the source code" necessary to implement the optical flow algorithm. The DSP processor implementation rated "fair", while the AutoPilot implementation rated "good", indicating that less source code modification was necessary to achieve high performance when using AutoPilot.

Results for the DQPSK application are shown in Table 3, comparing the quality of results of the AutoPilot implementation with a manual RTL implementation. After optimization, including both significant source code refactoring and careful use of tool directives, the AutoPilot implementation achieved slightly lower resource usage than the RTL implementation. It is worth noting that the handwritten RTL made use of optimized Xilinx CoreGen IP blocks

where applicable.

BDTI also assessed overall ease of use of the DSP tool flow and the FPGA tool flow, combining HLS with the low-level implementation tools. They concluded that the DSP tool flow was still significantly easier to use, primarily due to difficulties installing the FPGA tools and a lack of sufficient platform infrastructure that can be accessed without in-depth knowledge of the FPGA tool flow. In the future, we believe that these issues will be solved as shown in Section VIII.

Table 3. Quality of results for DQPSK receiver workload: 18.75 MSamples/second input data at 75MHz clock speed. (Table reproduced from [101])

| Platform                                                                             | Chip Resource Utilization (Lower is Better) |

|--------------------------------------------------------------------------------------|---------------------------------------------|

| AutoESL AutoPilot plus<br>Xilinx RTL tools targeting<br>the Xilinx XC3D3400A<br>FPGA | 5.6%                                        |

| Hand-written RTL code using Xilinx RTL tools targeting the Xilinx XC3SD3400A FPGA    | 5.9%                                        |

#### B. Sphere Decoder

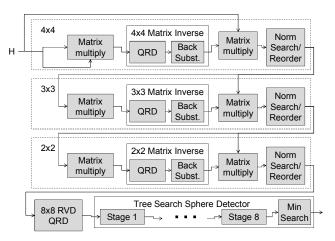

Xilinx has implemented a sphere decoder for a multi-input multi-output (MIMO) wireless communication system using AutoPilot [67][85]. The algorithm [28] consists largely of moderate-throughput linear algebra operations, such as matrix-matrix multiply, matrix inverse, QR decomposition, and vector-norm computations implemented on small-dimension matrices. The application exhibits a large amount of parallelism, since the operations must be executed on each of 360 independent subcarriers which form the overall communication channel and the processing for each channel can generally be pipelined. However, in order to reach an efficient high-utilization design, the implementation makes extensive use of resource sharing and time-division multiplexing, with the goal of simultaneously reducing resource usage and end-to-end processing latency.

The algorithm was originally implemented in Matlab, which was converted to an algorithmic C model totaling approximately 4000 lines of code. The C model was further modified to generate an efficient implementation with AutoPilot. This code was converted to run through AutoPilot in a matter of days and optimized over a period of approximately three man-months. The resulting HLS code for the application makes heavy use of C++ templates to describe arbitrary-precision integer data types and parameterized code blocks used to process different matrix sizes at different points in the application. Various AutoPilot-specific #pragma directives were used, primarily to express the layout of arrays in memory blocks, to direct the unrolling and scheduling of loops to the appropriate level of parallelism, and to guide the scheduling algorithms to share operators and minimize resource usage. Most of the code included no explicit specification of the RTL structure, although in one case it was necessary to include a #pragma directive to force the RTL micro-architecture of a C function and to force the selection of a particular multiplier library element.

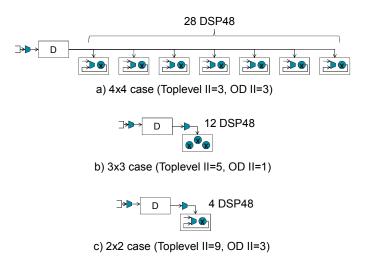

The end architecture consists of 25 independent actors in a streaming dataflow architecture, shown in Figure 10. Each actor is separated by synthesized streams or double buffers from neighboring components, enabling them to execute concurrently. The portions marked "4x4", "3x3" and "2x2" perform the same algorithm on matrices of decreasing size, and are collectively termed the "channel preprocessor". These portions are implementing using parameterized C++ templates, targeted by AutoPilot at different  $II^{-1}$  (3 in the 4x4 case, 5 in the 3x3 case and 9 in the 2x2 case), enabling optimized resource sharing decisions to be made automatically. The remainder of the design operates at II=1, with all resource sharing described in the C code.

Figure 10. Architecture of the sphere decoder application.

Table 4 below summarizes the results, comparing the overall AutoPilot-based implementation with a previously reported RTL-style implementation built using Xilinx System Generator. Both designs were implemented as standalone cores using ISE 12.1, targeting Xilinx Virtex 5 speed grade 2 at 225 MHz. Using AutoPilot Version 2010.07.ft, we were able to generate a design that was smaller than the reference implementation in less time than a hand RTL implementation by refactoring and optimizing the algorithmic C model.

Design time for the RTL design was estimated from work logs by the original authors of [28], and includes only the time for an algorithm expert and experienced tool user to enter and verify the RTL architecture in System Generator. Design time for the AutoPilot design was extracted from source code control logs. It reflects the time taken by a tool expert who is not a domain expert to take a piece of unfamiliar code, implement a first version in the tool, refactor the code to reflect a desired target architecture, reverse engineer the original RTL code to discover that algorithmic improvements were made in the RTL implementation that were not reflected back in the algorithmic model, and perform design exploration.

<sup>&</sup>lt;sup>1</sup> II denotes initiation interval of the pipeline. II=1 means the design accepts new inputs and produces new outputs at every clock cycle.

In both cases, multiple people worked on the design in parallel. Given the significant time familiarizing ourselves with the application and structure of the code, we believe that an application expert familiar with the code would be able to create such a design at least twice as fast.

Table 4. Sphere decoder implementation results.

| Metric                | RTL expert | AutoPilot<br>expert | Diff. (%) |  |

|-----------------------|------------|---------------------|-----------|--|

| Dev. time (man-weeks) | 16.5       | 15                  | -9%       |  |

| LUTs                  | 32,708     | 29,060              | -11%      |  |

| Registers             | 44,885     | 31,000              | -31%      |  |

| DSP48s                | 225        | 201                 | -11%      |  |

| 18K BRAMs             | 128        | 99                  | -26%      |  |