### Novel Approaches Toward Area- and Energy-Efficient Embedded Memories

### THÈSE Nº 6074 (2014)

#### PRÉSENTÉE LE 7 FÉVRIER 2014

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE CIRCUITS POUR TÉLÉCOMMUNICATIONS PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

### PAR

### Pascal Andreas MEINERZHAGEN

acceptée sur proposition du jury:

Prof. D. Atienza Alonso, président du jury Prof. A. P. Burg, Prof. Y. Leblebici, directeurs de thèse Prof. C. Enz, rapporteur Prof. A. Fish, rapporteur Prof. J. Rodrigues, rapporteur

## Acknowledgments

ous support, guidance through the world of digital VLSI circuits, systems, and applications, providing an excellent research environment, providing the possibility of manufacturing a large number of test chips in various technology nodes, guidance and support to build up a chip measurement lab, and his steady encouragement to publish at and attend conferences. He was always available and willing to advise and support me, even at late hours and on weekends, face to face or remotely. I would also like to thank my thesis co-advisor Prof. Dr. Yusuf Leblebici who was available for several insightful and pathbreaking discussions and generously provided his lab facilities for chip measurements. Many thanks to both of them. Many thanks go to Prof. Dr. Joachim Rodrigues from Lund University for his initiative to use standard-cell based memories in sub- $V_{\rm T}$  systems, for his guidance through the world and challenges of sub- $V_{\rm T}$  circuit and system design, for continuing pushing the optimization of sub-V<sub>T</sub> memories, providing the possibility of manufacturing a large number of chips in ST65nm CMOS, and for hosting me at Lund University several times. Many special thanks go to Prof. Dr. Alexander Fish, who not only provided me with many technical advises and insights into the fields of several emerging memory technologies and advanced adaptive bulk biasing schemes for CMOS memory arrays, but also taught me various important lessons concerning the writing of journal papers and research proposals. In addition, I am grateful to Prof. Dr. Christian Enz for kindly serving as an internal expert in my PhD defense committee. I am truly grateful to a number of individuals I met during the first two years of my PhD curriculum at the the Integrated Systems Laboratory (IIS) at ETHZ. Prof. Dr. Hubert Käslin and Dr. Norbert Felber provided useful comments and critical feedback during review meetings of various early design ideas; in addition, Hubert provided excellent EDA and PDK support through the Microelectronics Design Center (DZ), while Norbert provided valuable guidance concerning the use of test boards and an industrial digital tester, as well as funding for the tapeout of several student projects. Dr. Frank Gürkaynak and Beat Muheim from the DZ at ETHZ provided a truly excellent EDA and PDK support without which it would have hardly been possible to manufacture and measure many of the prototype chips covered in this thesis; with their tremendous patience and kindness, they even helped me not only with the standard digital design flow, but also with many special needs like separate power domains and special power pads. Frank even helped us measure chips on their equipment at ETHZ while we were already at EPFL. Dr. Jürg Treichler advised me in many questions in the domain of analog IC design and also co-advised many of my students working on the analog aspects

First of all, I am deeply grateful to my thesis advisor Prof. Dr. Andreas Burg for his continu-

of digital memory circuits; beyond that, Jürg always had the right script or advise to fix any potential problem. Dr. Christoph Studer generously provided the baseline LDPC decoder design which was used as application example for the use of standard-cell based memories in this thesis. I enjoyed many interesting discussions with Dr. Luca Henzen about cryptographic systems and their memory requirements. Christoph Roth worked with me on the integration of standard-cell based memories into his LDPC decoder architecture and, even after we left ETHZ, he was still available to support us while we evaluated the idea of using refresh-free dynamic memories in the LDPC decoder. Onur Andic pioneered the work on multilevel gaincell memories and designed a complete multilevel GC-eDRAM array, while Markus Schulz taped out the first single-bit-per-cell gain-cell array. I would also like to thank Dario Carnelli, Schekeb Fateh, and Dr. Christian Benkeser for several interesting technical discussions. I am also grateful to many other colleagues I collaborated with at ETHZ, as well as MSc and BSc students and interns I supervised at the IIS at ETHZ. Many thanks to all of them.

I am deeply grateful to many individuals at which I met at EPFL. Dr. Alain Vachoux from the Microelectronics Systems Laboratory (LSM) provided a continuous support with EDA tools and PDKs. Many thanks go to Christian Senning as a colleague and for his excellent support and help with the IT infrastructure in our Telecommunications Systems Laboratory (TCL) at EPFL. Moreover, I would like to thank Dr. Georgios Karakonstantis for his friendship and many interesting technical discussions and collaborations. Furthermore, Jeremy Constantin, Dr. Pavle Belanovic, Alexios Balatsoukas-Stimming, and Nicholas Preyss brought more life to our lab by organizing lunch groups and many social events. I am also grateful to all MSc and BSc students as well as interns which I have advised at EPFL for the countless design tasks and simulations they have carried out. In particular, Rashid Iqbal analyzed the impact of voltage scaling on gain-cell memories and even taped out a test chip, while Muhammad Umer Khalid proposed and evaluated a replica column for fast read and write access to multilevel gain-cell memories under PVT variations. Andrea Bonetti did a truly excellent job by designing a dynamic storage cell and taping out a full LDPC decoder chip containing dynamic standardcell based memories in a short time. Ibrahim Kazi designed non-volatile flip-flop topologies and optimized them for subthreshold operation. My special thanks also go to Dr. Pierre-Emmanuel Gaillardon from the Integrated Systems Laboratory (LSI) at EPFL and to Dr. Davide Sacchetto from LSM at EPFL for interesting and truly enriching collaborations in the field of emerging memory technologies, and the integration of such emerging devices into CMOS circuits. Moreover, I am thankful to Radisav Cojbasic, Nikola Katic, Alessandro Cevrero, and Clemens Nyffeler from LSM at EPFL for many interesting technical as well as non-technical discussions and coffee breaks. I am also grateful to Dr. Ahmed Dogan, an alumni of the Embedded Systems Laboratory (ESL) at EPFL for providing interesting applications for our  $\mathrm{sub}$ - $V_{\mathrm{T}}$  memories in the field of biomedical signal processing, and for the collaboration in the field of standard-cell library characterization. Many thanks to all of them.

I am very grateful to several individuals from Lund University, Sweden which I had the chance to visit several times during my PhD curriculum. I am deeply grateful to Yasser Sherazi for an amazingly efficient and productive collaboration on the comparative analysis of sub- $V_{\rm T}$  standard-cell based memories, and for teaching me their sub- $V_{\rm T}$  characterization flow.

Moreover, I am addressing many thanks to Oskar Andersson and Babak Mohammadi for various great collaborations on the design, manufacturing, and measurement of many sub- $V_{\rm T}$  memories based on custom-designed standard-cells. Many thanks to all of them.

I am also deeply grateful to several people from Ben-Gurion University and Bar-Ilan University, Israel, which I could both visit several times during the completion of my PhD studies. I am truly and deeply grateful to Adam (Adi) Teman, who I extensively collaborated with in the field of gain-cell memories during the last years of my PhD curriculum, which resulted in many great contributions to this thesis; Adi taught me many circuit techniques for use in CMOS memory arrays, how to prioritize tasks and get work done efficiently, as well as a positive and healthy attitude toward research, teaching, networking, and life. I am also grateful to Anatoli Mordakhay who devised and measured several gain-cell test circuits. I would also like to thank Robert Giterman who helped us tremendously with the measurement of various gain-cell eDRAM test chips and who continued research into low-power gain-cell memories. Many thanks to all of them.

In addition, I would like to truly thank a number of individuals from Intel Labs, Intel Corporation who, in numerous truly enriching discussions provided me with a fresh view on my PhD work from and industry perspective, and helped me to identify future industry-relevant research directions. First of all, I would like to thank my direct advisor Dr. Jaydeep Kulkarni, who dedicated an amazing amount of his time to me (up to three 1:1 meetings per week), and from whom I learned tons in the field of analog and digital IC design, particularly in the field of power management and SRAM. Second, I would like to thank my manager James (Jim) Tschanz, who, in many personal meetings, helped me understand the relevance of my research in a larger context and taught me tons on the activities and the structure of Intel. Furthermore, I am deeply grateful to Dr. Vivek De for the unique possibility to carry out a truly enriching and unforgettable internship in his Circuit Research Laboratory (CRL). In addition, I would like to thank Dr. Ulrich Bretthauer who served as my Intel mentor and showed me the Intel Braunschweig Laboratories. Moreover, I would like to thank Dr. Dinesh Somasekhar, Dr. Muhammad Khellah, Dr. Badarinath Kommandur, and Dr. Anant Deval, for various technical discussions and valuable feedback on our work. Last but not least, I thank my colleagues Dr. Amin Khajeh, Alicia Klinefelter, Rangharajan Venkatesan, and Farah Yahya for the many interesting, technical discussions and social activities.

Finally, I would like to truly and deeply thank my parents Andreas and Anita Meinerzhagen, as well as my sisters Manuela Bregy-Meinerzhagen and Sarah Meinerzhagen for their continuous support during many years; they often helped me remember what really matters in life, beyond work, and helped me gain perspectives for future professional development. I truly enjoyed playing with my godson Loan Bregy, and of course also with Jael and Enea, as a delighting relief and change from my work and everyday life. Many thanks to all of them. I am also truly and deeply grateful to my girlfriend Maricel Montezuma for her continuous support, her unconditional love, the many nice moments she gifted me, and for always being here for me when I needed her. Many thanks to her.

Lausanne, January 15, 2014

Pascal Meinerzhagen

### **Abstract**

Embedded memories consume an increasingly dominant share of the overall area and power of very large scale integration (VLSI) systems-on-chip (SoCs) targeted toward applications ranging from microprocessors, to wireless communications, to biomedical implants. Static random-access memory (SRAM) is the predominant embedded memory technology used in most VLSI SoCs, while conventional embedded dynamic-random access memory (eDRAM) is sometimes used for higher storage density. Unfortunately, SRAM encounters several design challenges when operated at ultra-low supply voltages or if implemented in aggressively scaled complementary metal-oxide-semiconductor (CMOS) technologies, while conventional eDRAM based on the 1-transistor-1-capacitor (1T-1C) bitcell is incompatible with standard digital CMOS technologies. This thesis investigates and proposes interesting alternatives to SRAMs and eDRAMs for the implementation of embedded memories, namely standard-cell based memories (SCMs) and gain-cell based eDRAM (GC-eDRAM).

SCMs can be synthesized from commercial standard-cell libraries (SCLs) and function reliably in any VLSI system, even if operated at ultra-low voltages or when implemented in aggressively scaled CMOS nodes, where conventional 6-transistor (6T)-bitcell SRAM would fail. This thesis presents an extensive comparative analysis of possible SCM topologies based on commercial SCLs and identifies the border in storage capacity up to which SCMs are still smaller than SRAM macrocells, despite the larger storage cell (latch or flip-flop), due to less peripheral circuits. In addition, the enormous benefits of the design and integration of custom standardcells to meet the specific needs of various VLSI SoCs with very different memory requirements are demonstrated and verified by various application examples and the manufacturing and measurement of several test chips. For example, all internal memories of a low-density paritycheck (LDPC) decoder, extensively used in wireless communications, can be implemented as refresh-free, dynamic SCMs (D-SCMs) due to frequent and periodic write updates; the use of custom-designed dynamic latches instead of commercial static latches leads to dramatic area savings. Moreover, subthreshold (sub-V<sub>T</sub>) SCMs are especially interesting for ultra-low power VLSI systems such as biomedical implants due to the lack of good sub-V<sub>T</sub> SRAM macrocell compilers; silicon measurements show that the design of a single ultra-low leakage standardcell and its integration into the SCM compilation flow lead to unprecedentedly low leakage power and access energy per bit. Finally, a non-volatile flip-flop topology, based on emerging ReRAM device technology, which can operate and wake-up at sub-V<sub>T</sub> voltages is proposed for future low-power VLSI SoCs with zero standby leakage.

GC-eDRAM is an interesting alternative to both SRAM and conventional 1T-1C eDRAM, since

it combines the main advantages of both SRAM and eDRAM, while it avoids most of their drawbacks. In fact, a gain-cell, built from 2-4 MOS transistors, is smaller than any SRAM bitcell and exhibits less leakage current, while it is fully compatible with standard digital CMOS technology, and allows for non-destructive read (as opposed to 1T-1C eDRAM). Moreover, any gain-cell can simultaneously and independently be optimized for robust read and write access (as opposed to both 6T SRAM and 1T-1C eDRAM) and allows for two-port memory implementations at virtually no overhead compared to single-port implementations. The main drawback of GC-eDRAM is the degraded retention time compared to 1T-1C eDRAM and the need for periodic, power-consuming refresh cycles. In this thesis, the impact of supply voltage scaling on the behavior of 2-transistor (2T)-bitcell GC-eDRAM is analyzed in detail; counter to intuition, the retention time of GC-eDRAM can be improved by voltage scaling for given memory access statistics and a given write bit-line (WBL) control scheme, identifying near-threshold (near-V<sub>T</sub>) GC-eDRAMs as an interesting and feasible memory type for use in low-power, medium-performance VLSI SoCs. Furthermore, two novel techniques to further improve the retention time and reduce the data retention power of near- $V_{\rm T}$  GCeDRAM are proposed and verified by silicon measurements: 1) reverse body biasing (RBB) of the storage array for reduced subthreshold conduction of the write transistor; and 2) replica techniques for optimum refresh timing under varying environmental conditions (processvoltage-temperature) and for varying write-access disturb frequencies. Moreover, as a highdensity counterpart to large 8–14 transistor (8–14T) sub- $V_T$  SRAM bitcells, the feasibility of  $\text{sub-}V_{\text{T}}$  GC-eDRAM is investigated for the first time; we find that  $\text{sub-}V_{\text{T}}$  operation is a viable option leading to sufficiently high array availability for read and write access in a mature CMOS node, while we recommend near- $V_T$  operation in aggressively scaled nodes due to increased parametric variations and lower achievable storage node capacitance. Finally, the feasibility of multilevel gain-cells is investigated for the first time; such multilevel GC-eDRAM is identified as convenient means to trade circuit reliability for the benefit of higher storage density in error-resilient VLSI systems (such as many wireless communications systems).

**Keywords:** Embedded memories, VLSI systems, SoC, ASIC, CMOS, SRAM, eDRAM, standard-cell based memory, dynamic storage cells, voltage scaling, near-threshold operation, subthreshold operation, ultra-low power, reliability, non-volatile memory, ReRAM, OxRAM, gaincells, gain-cell based eDRAM (GC-eDRAM), retention time improvement, refresh power reduction, body biasing, replica techniques, technology scaling, multilevel gain-cell

## Zusammenfassung

Integrierte Datenspeicherbausteine verbrauchen einen stetig wachsenden Anteil des Flächenbedarfs und des gesamten Energieverbrauchs von VLSI Systemen (SoCs) welche in Mikroprozessoren, drahtlosen Kommunikationssystemen, biomedizinischen Implantaten und für viele andere Anwendungen gebraucht werden. Die meisten dieser VLSI Systemen bedienen sich der dominanten und meist genutzten SRAM Speichertechnologie, welche nur selten durch konventionelle eDRAM Technologie ersetzt wird um höhere Speicherdichten zu erreichen. Leider ist es problematisch SRAM Speichereinheiten zuverlässig mit tiefen Versorgungsspannungen zu betreiben oder in den modernsten, extrem skalierten CMOS Technologieprozessen zu implementieren. Zudem ist die konventionelle eDRAM Technologie, welche auf der 1-Transistor-1-Kondensator (1T-1C) Speicherzelle beruht, nicht gänzlich kompatibel mit normalen, digitalen CMOS Technologien. Diese Dissertation untersucht Speicherbausteine basierend auf Standardzellen (SCMs) und eDRAM basierend auf so gennanten "Gain-Cells" (GC-eDRAM) als vielversprechende Alternativen zu den konventionellen SRAM und 1T-1C eDRAM Technologien und schlägt viele konkrete Implementierungen in verschiedenen CMOS Technologien vor.

In der Tat können SCMs mit Hilfe von kommerziell zugänglichen Standardzellenbibliotheken (SCLs) einfach synthetisiert und in einem beliebigen VLSI System zuverlässig in Betrieb genommen werden, sogar bei extrem tiefen Versorgungsspannungen oder in stark skalierten CMOS Technologien wo konventionelles SRAM (basierend auf der 6T-Speicherzelle) normalerweise nicht mehr zuverlässig funktionieren würde. Diese Dissertation präsentiert eine detaillierte Studie und einen umfangreichen Vergleich von vielen möglichen SCM Topologien welche auf kommerziellen SCLs basieren; ausserdem wird genau untersucht, bis zu welcher Speicherkapazität SCMs flächenmassig noch kleiner sind als SRAM Speichereinheiten, trotz der grösseren Speicherzelle (bistabile Kippschaltung anstelle der 6T SRAM-Zelle) und dank weniger Peripherieschaltungen. Zudem wird anhand von verschiedenen Anwendungsbeispielen und durch das Ausmessen von mehreren fabrizierten Mikrochips aufgezeigt, wie die Spezialanfertigung und Integration von eigens entwickelten Standardzellen gezielt die teilweise sehr unterschiedlichen Speicherbedürfnisse verschiedener VLSI SoCs befriedigen können und eine bestimmte Kennzahl (wie etwa die Siliziumfläche oder den Energieverbrauch) massgebend verbessern können. Beispielsweise können alle internen Speicherelemente von einem LDPC Dekoder, ein Bauteil welches oft in der drahtlosen Kommunikation gebraucht wird, als dynamische SCMs (D-SCMs) implementiert werden-sogar ohne die übliche, periodische, energieverbrauchende Refresh-Operation-, dank der häufigen und periodischen Schreibzugriffen. Die so eingesetzten, eigens dafür entwickelten dynamischen Speicherzellen führen zu einer signifikanten Reduktion des Flächenbedarfs im Vergleich zu den kommerziellen, statischen Speicherzellen. Ein weiteres Anwendungsbeispiel sind VLSI Systeme mit extrem geringem Energieverbrauch ("ultra-low power VLSI SoCs") wie etwa biomedizinische Implantate, wo der Einsatz von zuverlässigen sub- $V_{\rm T}$  SCMs besonders interessant und praktisch ist, da es keine guten Kompiler für sub- $V_{\rm T}$  SRAM Makrozellen gibt<sup>1</sup>. Messungen von eigens dafür hergestelleten Mikrochips zeigen, dass die Entwicklung und Integration von einer einzigen Standardzelle gekennzeichnet durch einen sehr tiefen Leckstrom, zu der tiefsten jemals in einer 65 nm CMOS Technologie gemessenen Leistungsaufnahme im Standby-Modus und zum tiefsten Energieverbrauch für Lese- und Schreibzugriffe führen. Schlussendlich werden in dieser Dissertation auch zum ersten Mal Flip-Flops vorgestellt welche mit sub- $V_{\rm T}$  Versorgungsspannungen auskommen und dank neuartigen ReRAM Speicherelementen ihre Daten sogar nach der Entfernung der Versorgunsspannung beibehalten, wodurch zukünftige VLSI Systeme mit bereits geringem Energieverbrauch sogar in einen Standby-Modus ganz ohne Stromverbrauch versetzt werden können.

Die zweite in dieser Dissertation untersuchte Art von Speichertechnologien, namentlich GCeDRAM, kombiniert die meisten Vorteile von SRAM und konventioneller eDRAM Technologie, während die meisten Nachteile von diesen konventionellen Technologien vermieden werden. In der Tat besteht eine "Gain-Cell" (GC) aus 2-4 MOS Transistoren, ist damit wesentlich kleiner und hat weniger Leckströme als alle bekannten SRAM Speicherzellen, kann direkt in jeder digitalen CMOS Technologie gebaut werden (ohne zusätzliche Prozessschritte) und hat einen nicht-destruktiven Lesezugriff (im Gegensatz zu der 1T-1C eDRAM Technologie). Zudem kann jede GC gleichzeitig und unabhängig für zuverlässige Lese- und Schreibzugriffe optimiert werden (was bei 6T SRAM und 1T-1C eDRAM Speicherzellen nicht möglich ist) und erlaubt auch das Bauen von Speichermakrozellen mit einem separaten Lese- und Schreibzugang, welche nur unwesentlich grösser sind als Makrozellen mit einem einzigen Zugang. Der bedeutendste Nachteil von GC-eDRAMs ist die kurze Datenspeicherzeit verglichen mit 1T-1C eDRAM und die daraus folgenden, frequenten, periodischen, energieverbrauchenden Refresh-Operationen. Diese Dissertation präsentiert Forschungsergebnisse, welche den Einfluss einer verringerten Versorgungsspannung auf das Verhalten von GC-eDRAM, basierend auf einer 2T Speicherzelle, aufzeigen; entgegen allen Erwartungen kann die Datenspeicherzeit durch eine Verringerung der Versorgungsspannung gesteigert werden, falls kritische Schaltungsknoten, namentlich die "write bit-lines" (WBLs), dank seltenen Lesezugriffen gezielt kontrolliert werden können. Diese Analyse zeigt, dass near-V<sub>T</sub> GC-eDRAM eine interessante und durchaus realisierbare Speichertechnologie für energie-effiziente VLSI Systeme mit mittelmässig hohem Datendurchsatz darstellen<sup>2</sup>. Des Weiteren werden zwei neuartige Methoden vorgeschlagen und durch Messungen von entsprechenden Mikrochips bestätigt, um die Datenspeicherzeiten von near-V<sub>T</sub> GC-eDRAM weiter zu verlängern. Erstens wird gezeigt, dass "reverse body biasing"

$<sup>^{1}</sup>$ Der Begriff "sub- $V_{T}$ " bezieht sich auf extrem tiefe Versorgungsspannungen, welche unter der Schwellenspannung ( $V_{T}$ ) der Transistoren liegen.

<sup>&</sup>lt;sup>2</sup>Der Begriff "near- $V_T$ " bezieht sich auf tiefe Versorgungsspannungen, welche nur leicht über der Schwellenspannung ( $V_T$ ) der Transistoren liegen.

(RBB) den unerwünschten Leckstrom durch den Lesezugrifftransistoren der GC reduziert. Zweitens kann der ideale Zeitpunkt für eine Refresh-Operation durch eine Replika-Technik bestimmt werden, sogar bei Prozess-, Spannungs- und Temperaturvariationen und für unterschiedlich häufige auftretende Störungen durch Lesezugriffe. Des Weiteren wird zum ersten Mal die Machbarkeit von sub- $V_{\rm T}$  GC-eDRAM untersucht, welcher mit nur 2 Transistoren pro Speicherzelle eine bedeutend höhere Speicherdichte aufweisen kann als sub- $V_T$  SRAM Zellen, welche auf 8–14 Transistoren basieren. Unsere Analysen zeigen, dass GC-eDRAM im sub- $V_{

m T}$ Bereich betrieben werden kann falls auf ältere CMOS Technologien zurückgegriffen wird, während die Versorgungsspannung nur bis in den near- $V_T$  Bereich verringert werden sollte für die modernsten, stark skalierten CMOS Technologien um eine genügend hohe Verfügbarkeit für Lese- und Schreibzugriffe zu erreichen. Schlussendlich untersucht diese Dissertation zum ersten Mal die Machbarkeit von GC-eDRAMs, welche mehrere Bits pro Zelle speichern ("multilevel GC-eDRAM"). Es wird aufgezeigt dass solche multilevel GC-eDRAMs eine angebrachte Speichertechnologie darstellen um höhere Speicherdichten zu erreichen in fehlertoleranten VLSI Systemen (wie zum Beispiel drahtlose Kommunikationssysteme), welche eine kleine Anzahl von Schaltungsfehlern tolerieren können.

**Schlüsselwörter:** Integrierte Speicher, VLSI Systeme, SoC, ASIC, CMOS, SRAM, eDRAM, Standardzellenspeicher (SCM), dynamische Speicherzellen, Spannungsreduktion, near-threshold Operation, subthreshold Operation, ultra-tiefer Energieverbrauch, Zuverlässigkeit, nichtflüchtige Speicher, ReRAM, OxRAM, "gain-cells", GC-eDRAM, Datenspeicherzeiterhöhung, Reduktion der Datenspeicherleistungsaufnahme, "body biasing", Replikatechnik, Technologieskalierung, mehrstufige gain-cell

### Résumé

Les mémoires embarquées consomment une part de plus en plus importante de la surface totale et de la consommation des systèmes sur puces (System-on-Chip SoC) VLSI (Very Large Scale Integration) au sein d'un large domaine d'applications telles que les microprocesseurs, les systèmes de communications sans fil ou encore les implants biomédicaux. La technologie mémoire prédominante dans la plupart des systèmes VLSI est la SRAM, tandis que la technologie eDRAM conventionnelle s'utilise quelquefois pour atteindre des densités de stockage plus élevées. Malheureusement, la technologie SRAM se voit confrontée à plusieurs défis en cas d'opération à des tensions d'alimentation très basse et/ou de sa réalisation dans des technologies CMOS très avancées, alors que la technologie eDRAM conventionnelle basée sur la cellule 1-transistor-1-condensateur (1T-1C) n'est pas entièrement compatible avec les technologies CMOS numériques standards. Cette thèse de doctorat analyse et propose des nouvelles technologies pour l'implémentation des mémoires embarquées, avec notamment des mémoires à cellules de standard (SCMs) et des mémoires dynamiques basées sur des cellules à gain (GC-eDRAM).

Les mémoires SCM peuvent être synthétisées à partir de bibliothèques de cellules standard (Standard Cell Libraries SCLs) commerciales et fonctionnent de manière fiable dans tous les systèmes VLSI, même à des tension d'alimentation très basses et dans les technologie CMOS les plus avancées, où les mémoires SRAM conventionnelles, s'appuyant sur la cellule à 6 transistors, cessent de fonctionner correctement. Cette thèse de doctorat présente une analyse comparative approfondie des topologies SCM basées sur des SCLs commerciales et identifie les limites en terme de capacité de stockage pour laquelle les SCMs présentent un gain en surface par rapport à un équivalent SRAM. Bien que la cellule élémentaire soit plus grande (bascule bistable au lieu de la cellule SRAM 6T), le gain en vient de la réduction des besoins en circuits périphériques. En outre, plusieurs exemples d'application ainsi que la fabrication et des mesures de plusieurs puces de prototype montrent les avantages énormes qui résultent de la conception et de l'intégration des cellules standard faites sur mesure afin de répondre aux besoins spécifiques de différentes classes de systèmes VLSI. Par exemple, toutes les mémoires internes d'un décodeur LDPC (un dispositif qui est fréquemment utilisé dans les systèmes de communication sans fil), peuvent être implémentées comme des SCMs dynamiques (D-SCMs) grâce aux accès d'écriture fréquents et périodiques. En effet, l'utilisation des cellules de stockage dynamiques faites sur mesure donne lieu à une remarquable réduction de surface en comparaison de l'utilisation des cellules de stockage statiques commerciales. De plus, les SCM travaillant sous le seuil (sub- $V_{\rm T}$ ) sont particulièrement intéressantes pour les systèmes VLSI de

très faible puissance (ultra-low power VLSI systems) tels que les implants biomédicaux puisque de bons compilateurs de mémoires SRAM sub- $V_{\rm T}$  ne sont normalement pas disponibles. En effet, les mesures sur prototypes montrent que la conception et l'intégration dans la procédure de compilation SCM d'une seule cellule standard caractérisée par un courant de fuite très bas offrent une consommation au repas (stand-by) et l'énergie d'accès normalisée les plus basses jamais mesurées dans une technologie CMOS 65nm. Finalement, cette thèse de doctorat propose une nouvelle topologie de bascule bistable rémanente (non volatile), basée sur une technologie ReRAM émergente, qui peut être alimentée par une tension très faible (dans le domaine sub- $V_{\rm T}$ ) pour toutes les opérations régulières (sauf écriture de la partie rémanente). Cette bascule bistable rémanente permettra des modes stand-by sans aucun courant de fuite dans les futurs systèmes VLSI.

La technologie de mémoire GC-eDRAM proposée unit les avantages principaux des technologies SRAM et eDRAM conventionnelles, tout en évitant la plupart de leurs inconvénients. En fait, une cellule à gain (Gain-Cell GC), construite avec 2-4 transistors MOS, est plus compacte et présente un courant de fuite plus faible que n'importe quelle cellule SRAM, tandis qu'elle est entièrement compatible avec les technologies CMOS numériques standards et permet des accès en lecture non destructifs (ce qui n'est pas le cas pour la technologie eDRAM conventionnelle). De plus, il est possible d'optimiser une cellule à gain indépendamment pour des accès en lecture et des accès en écriture fiables en même temps, ce qui n'est pas possible ni pour les cellules SRAM, ni pour les cellules eDRAM 1T-1C conventionnelles. Aussi, les cellules à gain permettent de facilement construire des mémoires à double ports avec un très faible surcoût en surface par rapport à des mémoires à port unique. Toutefois, le désavantage principal des mémoires GC-eDRAM est le temps de rétention de données réduit par rapport aux mémoires eDRAM conventionnelles et donc la nécessité de cycles de rafraîchissement (refresh cycles) périodiques consommant de l'énergie. Dans cette thèse de doctorat, le comportement des GC-eDRAM, basée sur une cellule de stockage à deux transistors, est analysé en détail dans des conditions d'utilisation à faible tensions d'alimentation : contrairement à toutes attentes, le temps de rétention de données peut être augmenté par une réduction de la tension d'alimentation, au cas où quelques noeuds particuliers (notamment les write bit-lines WBLs) peuvent être librement contrôlés grâce à des accès en écriture peu fréquents. Cette analyse fait émerger les GC-eDRAMs near-V<sub>T</sub> comme un type de mémoire pertinent pour les systèmes VLSI à faible consommation et débit de données moyen. En outre, deux nouvelles techniques pour améliorer encore plus le temps de rétention et pour réduire la consommation des GC-eDRAMs near-V<sub>T</sub> sont proposées et vérifiées par mesure de puces de prototype : 1) la technique de "reverse body biasing" (RBB) réduit le courant de fuite du transistor à accès en écriture avec succès; et 2) l'utilisation de cellules répliques permet de trouver l'instant idéal pour les cycles de rafraîchissement même pour des circonstances environnementales (procédés de fabrications, tension, et température) fluctuantes et sous influence de différentes fréquences de perturbation par accès en écriture. Par ailleurs, cette thèse de doctorat étudie pour la première fois la possibilité d'alimenter des GC-eDRAM avec des tensions ultra basses (se trouvant dans le domaine sub- $V_T$ ), afin de proposer une alternative aux cellules SRAM sub- $V_T$  avec 8–14 transistors, pour les densité de stockage élevées. Nous constatons que l'alimentation avec des tensions sub- $V_{\rm T}$  est possible pour implémentation des GC-eDRAMs dans des technologies CMOS mûres et entraîne une disponibilité suffisante pour les accès à la mémoire, tandis que nous recommandons des tensions d'alimentation se trouvant dans le domaine near- $V_{\rm T}$  pour l'implémentation des GC-eDRAMs dans les technologies CMOS les plus avancées. Finalement, la faisabilité des cellules à gain à multiples niveaux (multilevel gain-cell) est évaluée pour la première fois ; ce genre de mémoire est identifié comme une solution optimale pour augmenter la densité de stockage, au prix d'une fiabilité plus basse. Cette perte de fiabilité est acceptable dans les systèmes VLSI naturellement résistants à quelques erreurs matérielles (comme, par exemple, beaucoup de systèmes de communication sans fil).

**Mots-clés:** Mémoires intégrées, systèmes VLSI, SoC, ASIC, CMOS, SRAM, eDRAM, mémoire à cellules standards (SCM), cellules de stockage dynamique, reduction de tension d'alimentation, opération near-threshold, opération subthreshold, consommation ultra-basse, fiabilité, mémoire rémanente (non volatile), ReRAM, OxRAM, cellule à gain ("gain-cell"), GC-eDRAM, amélioration du temps de rétention de données, réduction de la puissance de rafraîchissement, "body biasing", techniques de répliques, réduction de technologie, cellule de gain de différents niveaux

## **Contents**

| A  | cknov  | wledgments                                                         | iii   |

|----|--------|--------------------------------------------------------------------|-------|

| Al | ostra  | ct (English/Deutsch/Français)                                      | vii   |

| Ta | ıble o | of contents                                                        | xix   |

| Li | st of  | figures                                                            | xxvi  |

| Li | st of  | tables                                                             | xxvii |

| 1  | Intr   | roduction                                                          | 1     |

|    | 1.1    | Increasing Need for Embedded Memories in VLSI SoCs                 | 1     |

|    | 1.2    | Memory Requirements of Various VLSI Systems                        | 5     |

|    | 1.3    | Brief Review of the State of the Art                               | 6     |

|    | 1.4    | Contributions                                                      | 8     |

|    | 1.5    | Thesis Outline                                                     | 11    |

|    | 1.6    | Selected Publications                                              | 12    |

| 2  | Star   | ndard-Cell Based Memories (SCMs) for High-Performance VLSI Systems | 15    |

|    | 2.1    | Introduction                                                       | 16    |

|    | 2.2    | SCMs Based on Commercial Standard-Cell Libraries (SCLs)            | 19    |

|    |        | 2.2.1 SCM Architectural Choices and Comparison                     | 19    |

|    |        | 2.2.2 Application Example: Low-Power LDPC Decoder                  | 26    |

|    | 2.3    | High-Density Dynamic SCMs (D-SCMs)                                 | 29    |

|    |        | 2.3.1 Integration of Custom-Designed Dynamic Latches               | 29    |

|    |        | 2.3.2 Application Example: LDPC Decoder with Refresh-Free D-SCMs   | 34    |

|    | 2.4    | Conclusions                                                        | 43    |

| 3  | Ultı   | ra-Low-Power Standard-Cell Based Memories (SCMs)                   | 47    |

|    | 3.1    | Challenges and Review of Prior-Art Low-Voltage SRAM Design         | 48    |

|    | 3.2    | SCMs Based on Commercial SCLs Operated in Sub- $V_T$ Regime        | 50    |

|    |        | 3.2.1 Sub- $V_{\rm T}$ Design and Modeling Flow                    | 51    |

|    |        | 3.2.2 Sub- $V_T$ SCM Architecture Evaluation                       | 54    |

|    |        | 3.2.3 Reliability Analysis                                         | 61    |

|    |        | 3.2.4 Comparison with Sub- $V_T$ SRAM Designs                      | 63    |

### **Contents**

|   | 3.3 | Ultra-Low Leakage Sub- $V_{\rm T}$ SCMs                                    |

|---|-----|----------------------------------------------------------------------------|

|   |     | 3.3.1 Ultra-Low Leakage Standard-Cell Design 6                             |

|   |     | 3.3.2 Silicon Measurements of 4 kb Sub- $V_{\rm T}$ SCM                    |

|   |     | 3.3.3 Comparison with Prior-Art Sub- $V_{\rm T}$ Memories                  |

|   | 3.4 | ReRAM-Based Non-Volatile Flip-Flop (NVFF) Topologies                       |

|   |     | 3.4.1 ReRAM Manufacturing Process and Switching Characteristics            |

|   |     | 3.4.2 Non-Volatile Flip Flop Architecture and Operation                    |

|   |     | 3.4.3 Simulation Results                                                   |

|   | 3.5 | Conclusions                                                                |

| 4 | Gai | -Cell Based eDRAMs (GC-eDRAMs) 8                                           |

|   | 4.1 | Introduction to GC-eDRAM                                                   |

|   |     | 4.1.1 Advantages and Drawbacks of GC-eDRAM                                 |

|   |     | 4.1.2 Review of GC-eDRAM Target Applications and Circuit Techniques 9      |

|   | 4.2 | GC-eDRAMs Operated at Scaled Supply Voltages                               |

|   |     | 4.2.1 2T Low-Voltage GC-eDRAM Array Architecture                           |

|   |     | 4.2.2 Operation Principle                                                  |

|   |     | 4.2.3 Impact of Supply Voltage Scaling on Retention Time                   |

|   |     | 4.2.4 Macrocell Implementation Results                                     |

|   |     | 4.2.5 Conclusions                                                          |

|   | 4.3 | Near- $V_{ m T}$ GC-eDRAM Implementations with Extended Retention Times 10 |

|   |     | 4.3.1 Impact of Body Biasing (BB) on the Retention Time                    |

|   |     | 4.3.2 GC-eDRAM with BB: Silicon Measurements                               |

|   |     | 4.3.3 Replica Technique for Optimum Refresh Timing                         |

|   |     | 4.3.4 Replica GC-eDRAM: Silicon Measurements                               |

|   | 4.4 | Aggressive Technology and Voltage Scaling (to Sub- $V_{ m T}$ Domain)      |

|   |     | 4.4.1 Introduction                                                         |

|   |     | 4.4.2 Two-Transistor (2T) Sub- $V_{ m T}$ Gain-Cell Design                 |

|   |     | 4.4.3 Macrocell Implementation in 0.18 μm CMOS                             |

|   |     | 4.4.4 Macrocell Implementation in 40 nm CMOS                               |

|   |     | 4.4.5 Conclusions                                                          |

|   | 4.5 | Multilevel GC-eDRAM (MLGC-eDRAM)                                           |

|   |     | 4.5.1 Multilevel GC-eDRAM Design                                           |

|   |     | 4.5.2 Reliability/Failure Analysis                                         |

|   |     | 4.5.3 Replica Techniques for Frequency Guardband Reduction 15              |

|   |     | 4.5.4 Implementation Results                                               |

|   |     | 4.5.5 Conclusions and Outlook                                              |

| 5 | Con | clusions 15                                                                |

|   | 5.1 | Standard-Cell Based Memories (SCMs)                                        |

|   | 5.2 | Gain-Cell Based eDRAMs (GC-eDRAMs)                                         |

|   | 5.3 | Outlook: SCMs and GC-eDRAMs in Future Applications                         |

|                                           | Contents |

|-------------------------------------------|----------|

| <b>A</b> Analytical Sub- $V_{ m T}$ Model | 169      |

| B Glossary                                | 171      |

| Bibliography                              | 187      |

| Curriculum Vitae                          | 189      |

# List of Figures

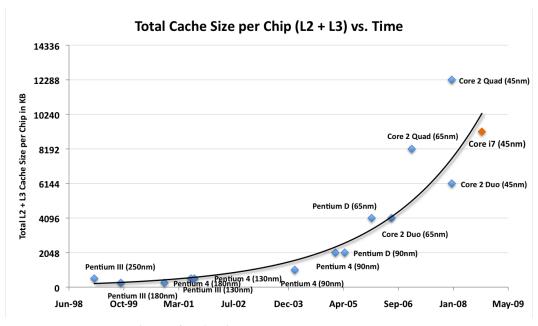

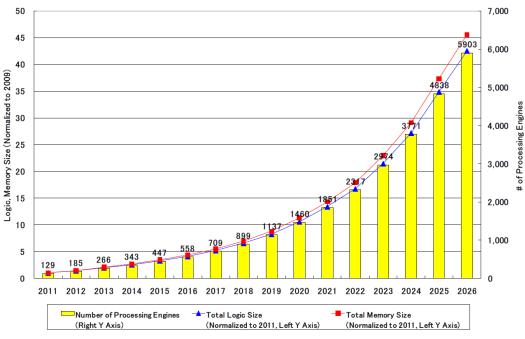

| 1.1 | (a) Past; and (b) predicted future evolution of embedded memory size                                                                                                                                                                                                                                                 | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

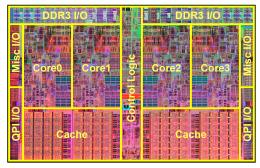

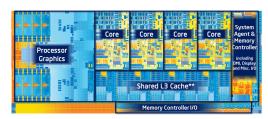

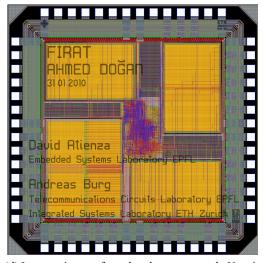

| 1.2 | Layout pictures and/or chip microphotographs of high-end microprocessors (a–b), a baseband transceiver (c), and a low-power processor for biomedical signals (d). All these VLSI SoCs require a significant amount of embedded memories, which are visible as regular tiles in the layout                            | 3  |

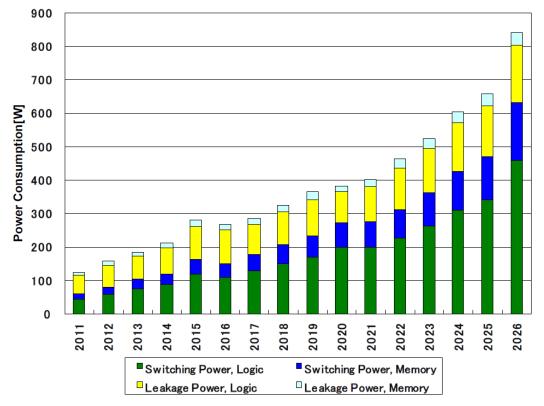

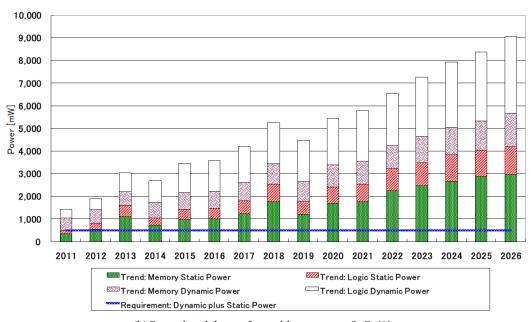

| 1.3 | Predicted power breakdowns of VLSI SoCs for (a) stationary; and (b) portable consumer electronics [1]                                                                                                                                                                                                                | 4  |

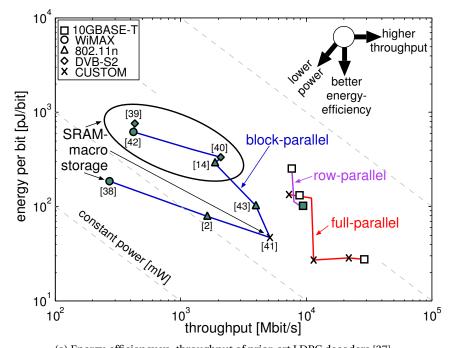

| 2.1 | (a) Energy-efficiency and throughput; and (b) area-efficiency and time per bit of state-of-the-art LDPC decoder implementations as of 2011                                                                                                                                                                           | 18 |

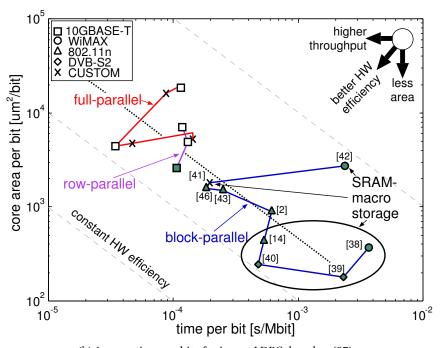

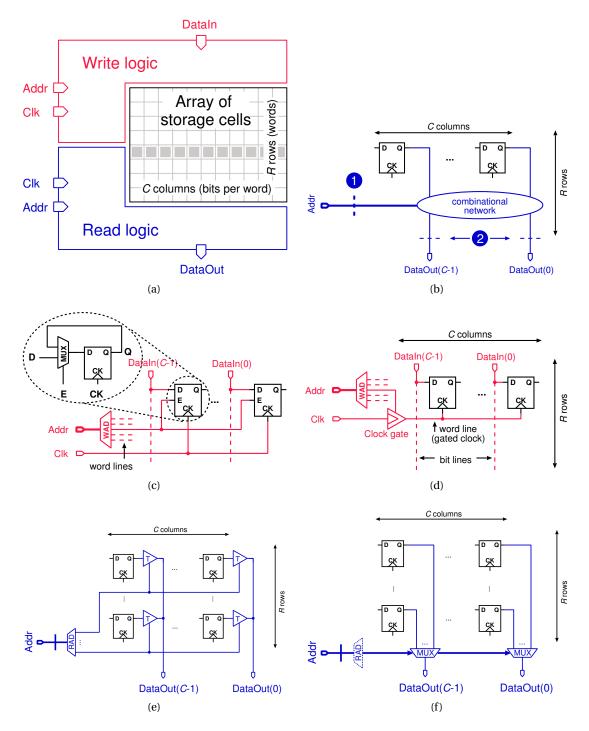

| 2.2 | (a) Building blocks of a generic standard-cell based memory architecture. (b) Achieving typical one-cycle read latency. (c) Write logic relying on enable flipflops, and (d) basic flip-flops in conjunction with clock-gates. (e) Read logic relying on tri-state buffers, and (f) CMOS multiplexers                | 20 |

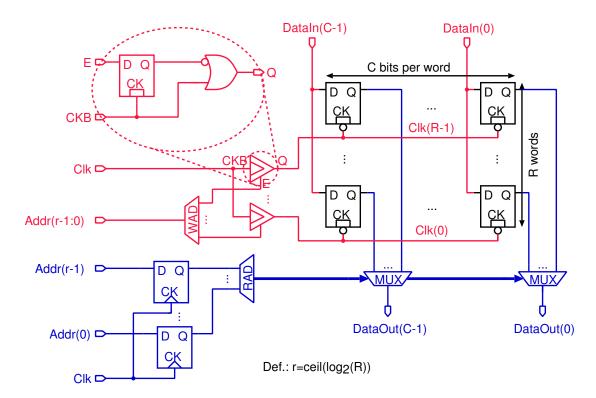

| 2.3 | Schematic of latch based SCM with clock-gates for the write logic and multiplexers for the read logic                                                                                                                                                                                                                | 24 |

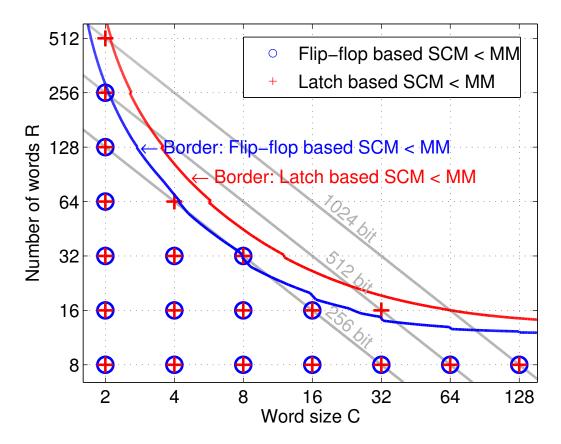

| 2.4 | Flip-flop and latch based SCMs versus SRAM memory macros (MM): sampled data points and intersection lines of regression functions                                                                                                                                                                                    | 25 |

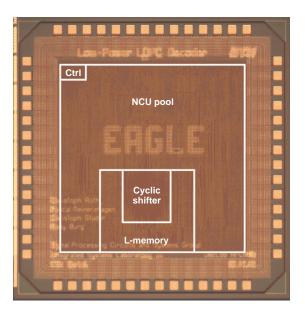

| 2.5 | Layout of SCM based low-power LDPC decoder in 0.13 µm CMOS technology. The Q- and the R-memory are located on the left-hand and right-hand side, respectively, while the T-memory is located in the middle, merged with and surrounded by combinational logic blocks                                                 | 27 |

| 2.6 | Modified SCM architecture with in-word clock-gating to support different LDPC code configurations                                                                                                                                                                                                                    | 28 |

| 2.7 | Chip microphotograph of the fabricated LDPC decoder using static SCMs $$                                                                                                                                                                                                                                             | 29 |

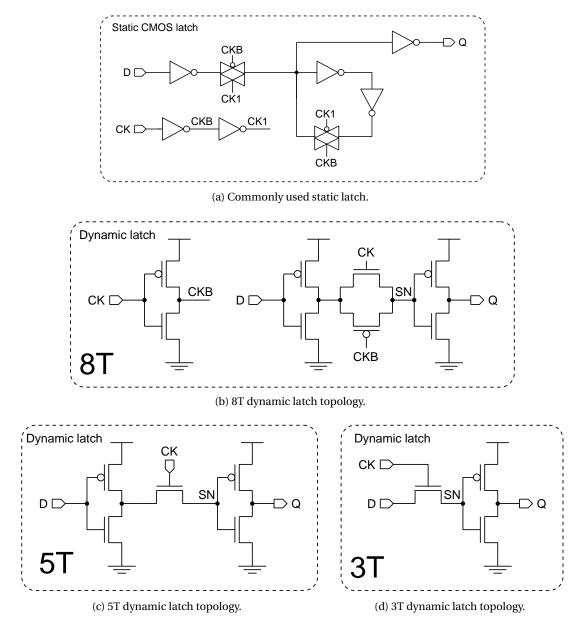

| 2.8 | (a) Conventional static latch topology used in most commercial SCLs. In newer SCLs for aggressively scaled CMOS nodes, it is increasingly more common to replace the inverter followed by a transmission-gate with a tri-state inverter for lower leakage; and various dynamic latch topologies, consisting of (b) 8 |    |

|     | transistors, (c) 5 transistors, and (d) 3 transistors, respectively                                                                                                                                                                                                                                                  | 31 |

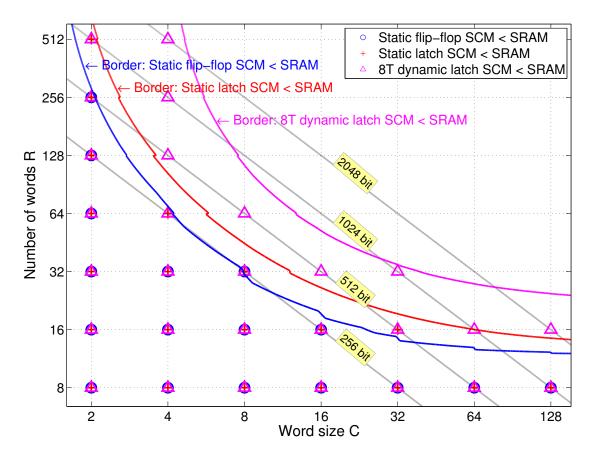

| 2.9  | Area efficiency of 1) static flip-flop SCM (blue); 2) static latch SCM (red); and 3) 8T dynamic latch SCM (magenta) compared to 6T-bitcell SRAM macrocells. SCM implementations below the blue, red, and magenta lines are smaller than                                                                                                        |          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | corresponding SRAM macrocells                                                                                                                                                                                                                                                                                                                  | 35       |

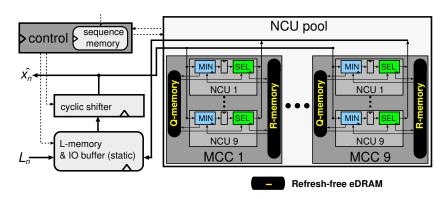

| 2.10 | Architecture of the quasi-cyclic LDPC decoder with refresh-free dynamic memories (highlighted in yellow)                                                                                                                                                                                                                                       | 37       |

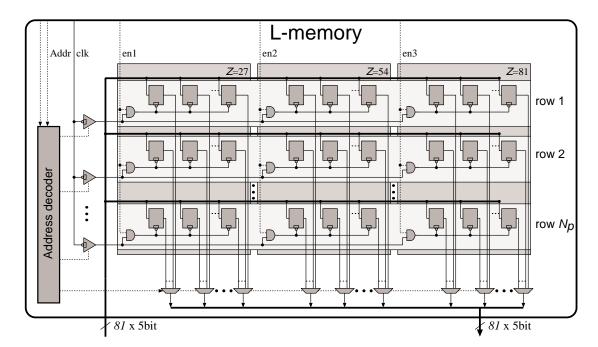

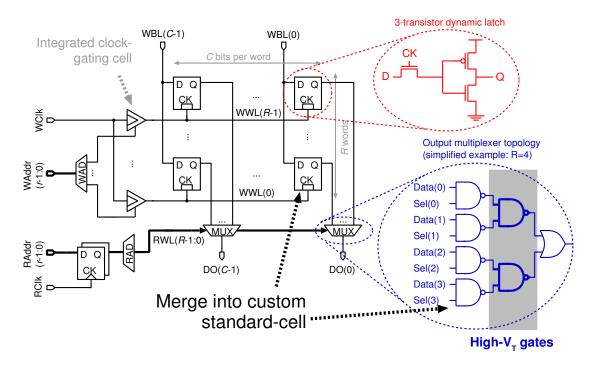

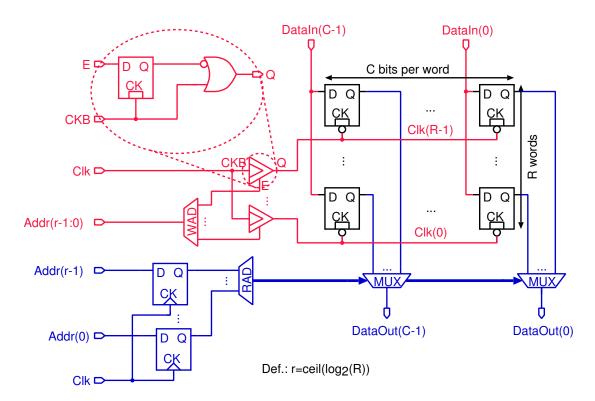

| 2.11 | Architecture of dynamic standard-cell based memory (D-SCM)                                                                                                                                                                                                                                                                                     | 38       |

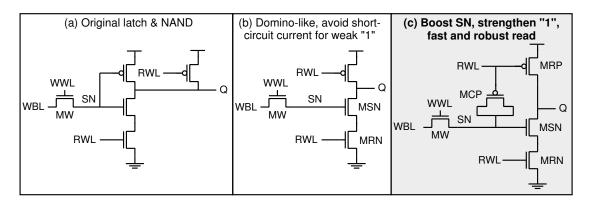

| 2.12 | Design exploration of custom standard-cells combining dynamic latch and NAND functionality                                                                                                                                                                                                                                                     | 40       |

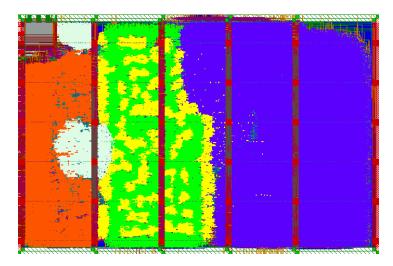

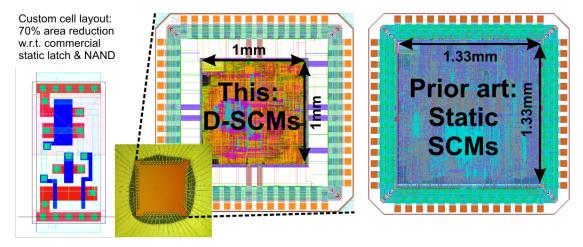

| 2.13 | (Left) Layout of custom standard-cell; (Middle) Chip microphotograph and layout picture of the proposed LDPC decoder using D-SCMs; and (Right) Layout picture of the same LDPC decoder explicatives using static SCMs.                                                                                                                         | 40       |

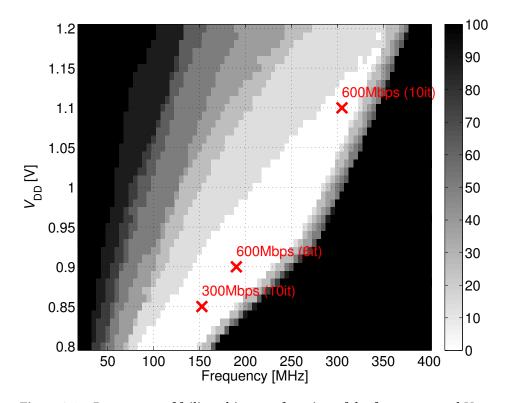

| 2 14 | picture of the same LDPC decoder architecture using static SCMs Percentage of failing chips as a function of the frequency and $V_{\rm DD}$                                                                                                                                                                                                    | 40<br>42 |

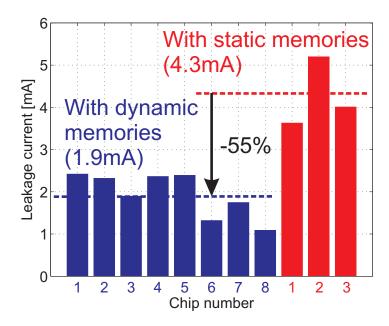

|      | Leakage current comparison of the proposed QC-LDPC decoder implementation based on D-SCMs (8 measured dies, blue bars) with the same decoder                                                                                                                                                                                                   |          |

|      | architecture using static SCMs (3 measured dies, red bars) [2]                                                                                                                                                                                                                                                                                 | 43       |

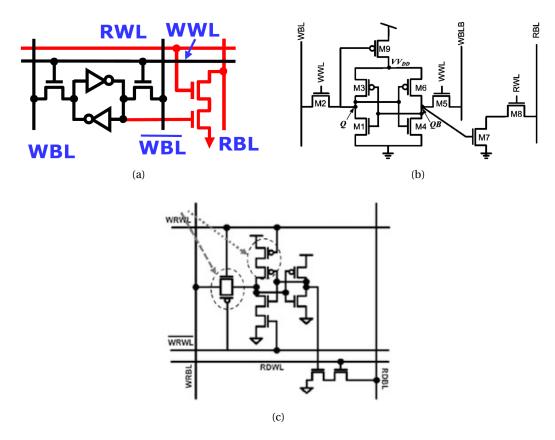

| 3.1  | Robust low-voltage SRAM bitcells: (a) 8T [3], (b) 9T [4], and (c) 10T [5]                                                                                                                                                                                                                                                                      | 50       |

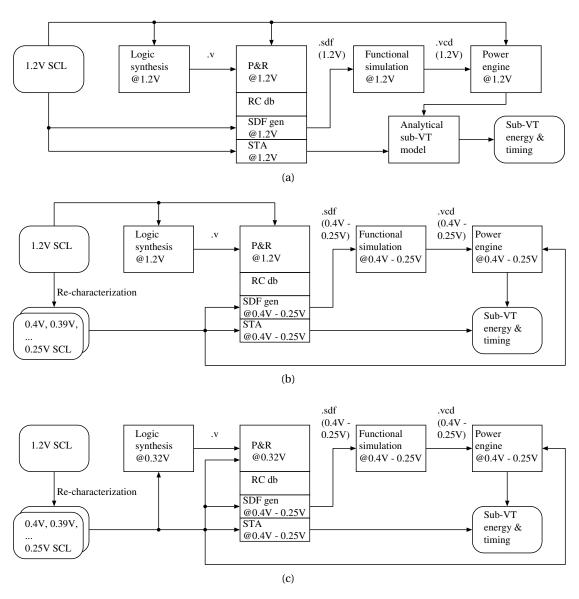

| 3.2  | Sub- $V_{\rm T}$ design and analysis flows: (a) Above- $V_{\rm T}$ synthesis, STA, and power analysis. Analytical sub- $V_{\rm T}$ model. (b) Above- $V_{\rm T}$ synthesis. Sub- $V_{\rm T}$ STA and power                                                                                                                                     |          |

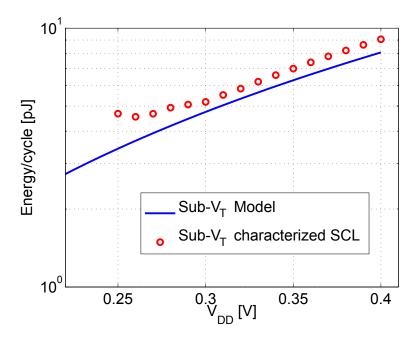

| 3.3  | analysis. (c) Sub- $V_T$ synthesis, STA, and power analysis                                                                                                                                                                                                                                                                                    | 53       |

|      | quency of 1kHz                                                                                                                                                                                                                                                                                                                                 | 54       |

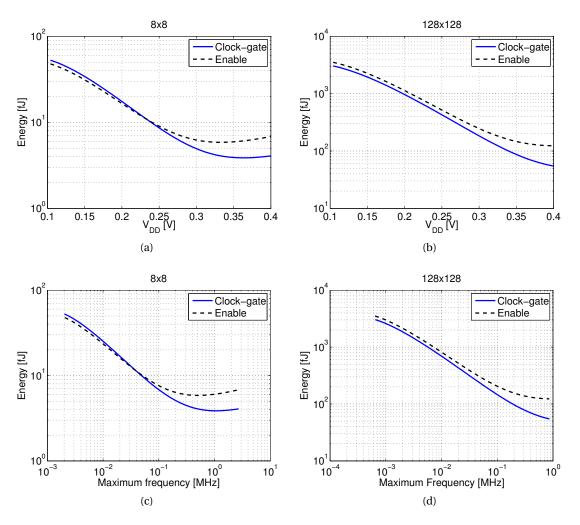

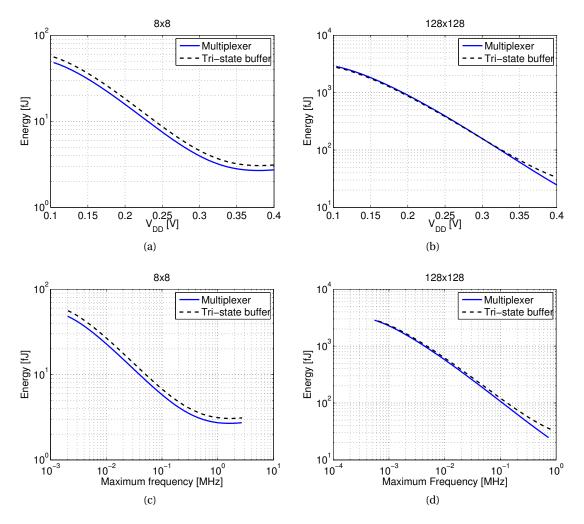

| 3.4  | Energy versus $V_{\rm DD}$ for different write logic implementations, namely <i>enable flip-flops</i> and <i>basic flip-flops in conjunction with clock-gates</i> , assuming a multiplexer based read logic, for (a) $R=8$ and $C=8$ as well as for (b) $R=128$ and $C=128$ . Energy versus maximum achievable frequency for the same memory   |          |

|      | architectures and sizes is shown in (c) and (d) $\hdots$                                                                                                                                                                                                                                                                                       | 55       |

| 3.5  | Energy versus $V_{\rm DD}$ for different read logic implementations, namely <i>tri-state</i> buffers and multiplexers, assuming a clock-gate based write logic and latches as storage cells, for (a) $R=8$ and $C=8$ as well as for (b) $R=128$ and $C=128$ . Energy versus maximum achievable frequency for the same memory architectures and |          |

|      | sizes is shown in (c) and (d) $\dots$                                                                                                                                                                                                                                                                                                          | 56       |

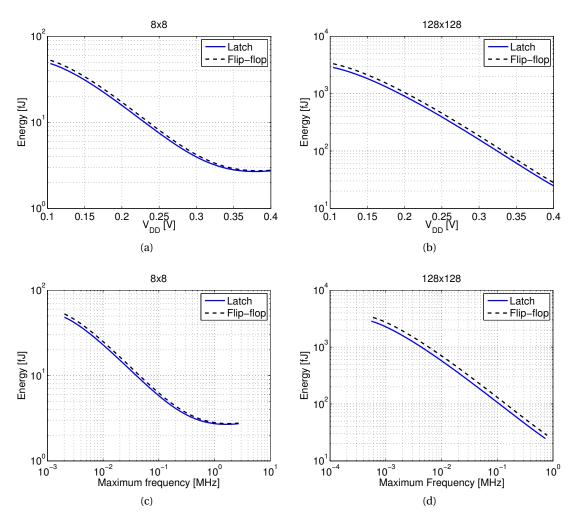

| 3.6  | Energy versus $V_{\rm DD}$ for different storage cell implementations, namely <i>latches</i> and <i>flip-flops</i> , assuming a clock-gate based write logic and a multiplexer based read logic, for (a) $R=8$ and $C=8$ as well as for (b) $R=128$ and $C=128$ . Energy                                                                       |          |

|      | versus maximum achievable frequency for the same memory architectures and sizes is shown in (c) and (d)                                                                                                                                                                                                                                        | 57       |

| 3.7  | Best-practice sub- $V_T$ SCM topology: latch based SCM with clock-gates for the                                                                                                                                                                                                                                                                | 31       |

| 5.1  | write logic and multiplexers for the read logic                                                                                                                                                                                                                                                                                                | 60       |

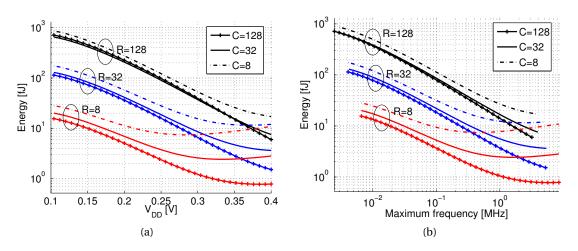

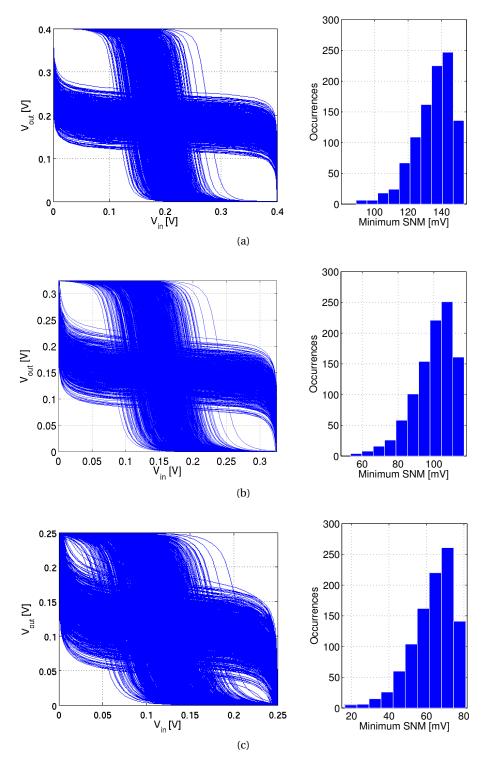

| 3.8  | Energy versus $V_{\rm DD}$ (a) and energy versus frequency (b) for the <i>latch multiplexer clock-gate</i> architecture for different memory configurations                                                                                            | 60  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

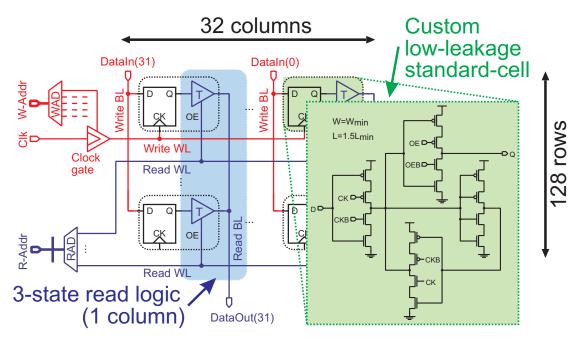

| 3.9  | Simplified schematic of the latch used in the best sub- $V_{ m T}$ SCM architecture $$ . $$                                                                                                                                                            | 63  |

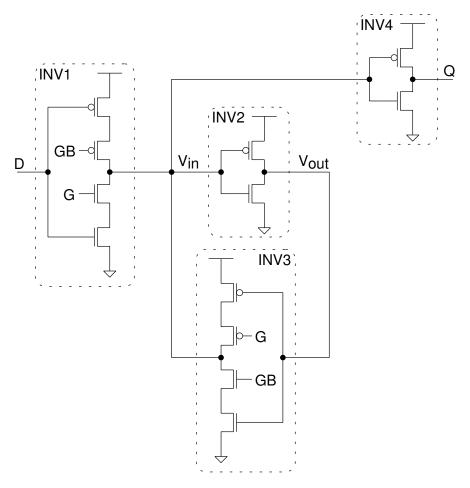

| 3.10 | Butterfly curves (left) and distribution of minimum hold SNM (right) of the latch used in the best sub- $V_{\rm T}$ SCM architecture for (a) $V_{\rm DD} = 400\mathrm{mV}$ , (b) $V_{\rm DD} = 325\mathrm{mV}$ , and (c) $V_{\rm DD} = 250\mathrm{mV}$ | 64  |

| 3.11 | Energy versus $V_{\rm DD}$ (a) and energy versus frequency (b) for the <i>latch multiplexer clock-gate</i> architecture for $R=256$ , $C=128$ and for $R=128$ , $C=256$ . The red triangle corresponds to [6]                                          | 67  |

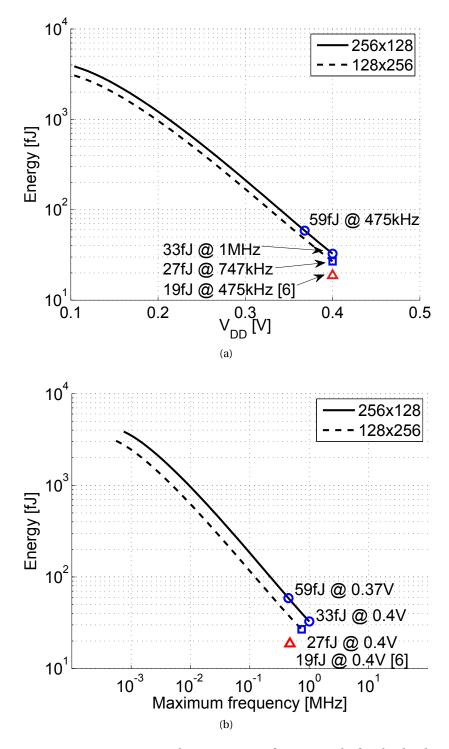

| 3.12 | Architecture of ultra-low-leakage 4 kb standard-cell based memory (SCM): the write logic uses clock-gates, while the 3-state inverters used for the read functionality are integrated in the low-leakage latch design                                  | 69  |

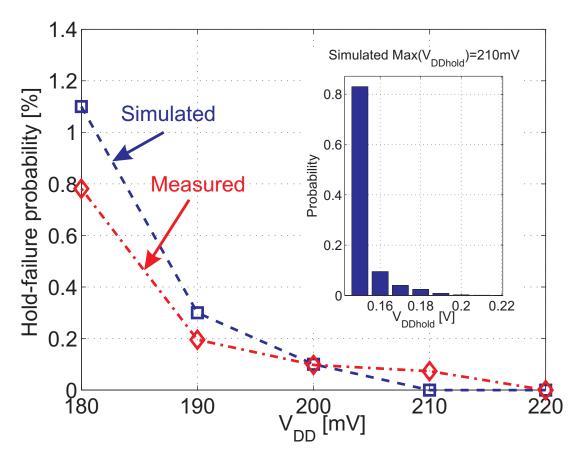

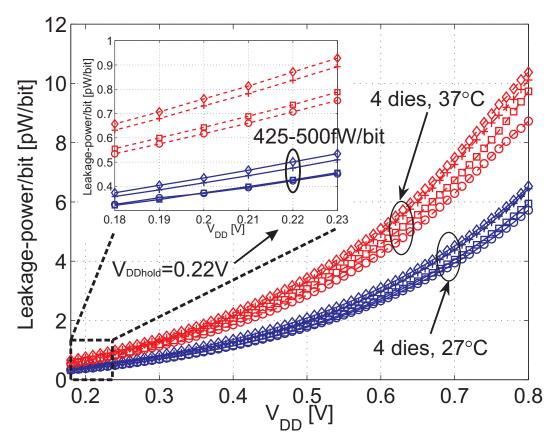

| 3.13 | Simulated and measured hold failure probability versus $V_{\rm DD}$ . Inset: Simulated distribution of $V_{\rm DDhold}$                                                                                                                                | 72  |

| 2 14 | Chip microphotograph and zoomed-in layout of sub- $V_T$ SCM test chip; the 4 kb                                                                                                                                                                        | 12  |

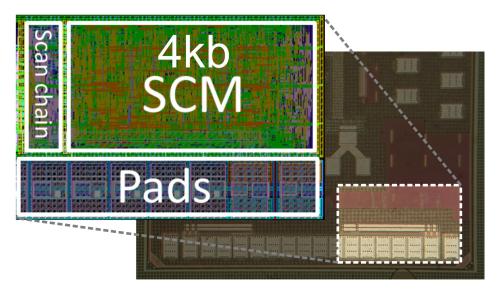

| 3.14 | SCM block, the test interface, and the I/O pads are highlighted                                                                                                                                                                                        | 73  |

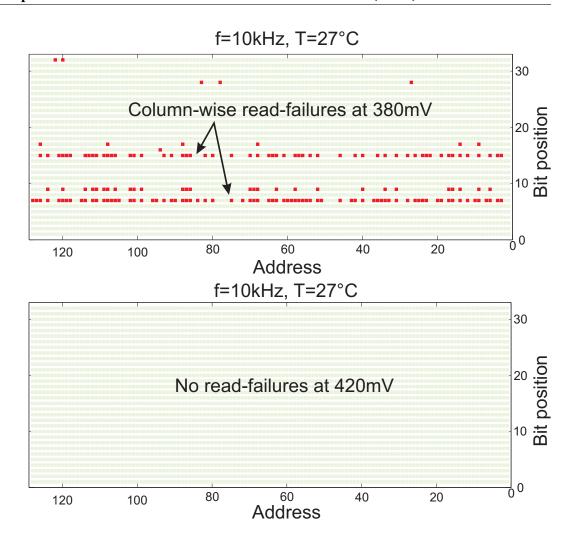

| 3.15 | Measured error maps for $V_{\rm DD}$ of 380 mV (top) and 420 mV (bottom)                                                                                                                                                                               | 74  |

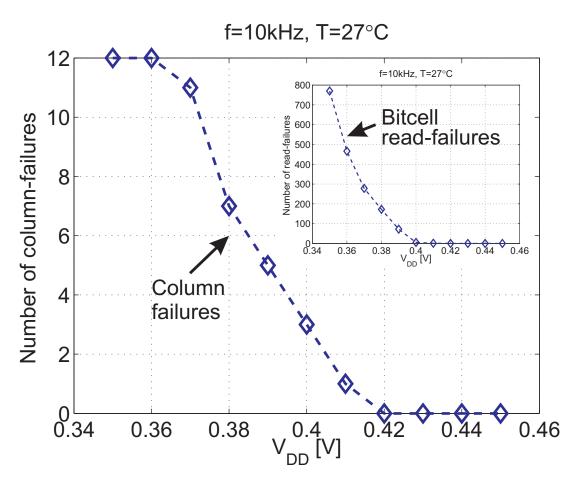

|      | Measured number of inoperative columns versus $V_{\rm DD}$ . Inset: Total number of                                                                                                                                                                    |     |

|      | read-failures versus $V_{\mathrm{DD}}$                                                                                                                                                                                                                 | 75  |

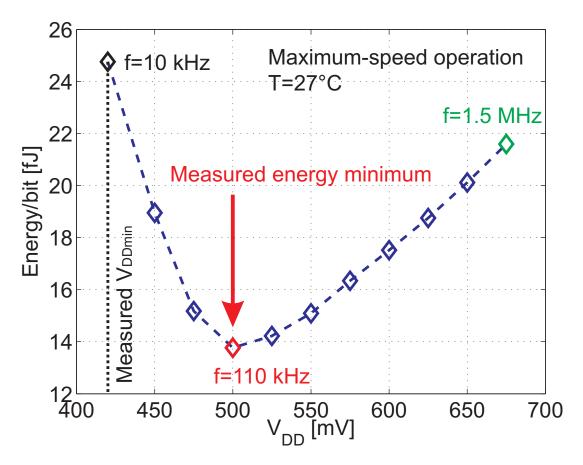

| 3.17 | Measured energy per bit-access                                                                                                                                                                                                                         | 76  |

| 3.18 | Measured leakage power per bit, including overhead of peripheral circuits, mea-                                                                                                                                                                        |     |

|      | sured for 4 dies, at 27 and 37 °C. Inset: Zoom around $V_{\rm DDhold}$                                                                                                                                                                                 | 77  |

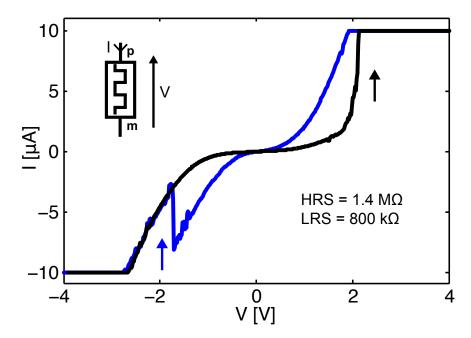

| 3.19 | $1.5\mu\text{m}^2\text{Al/TiO}_2/\text{Al}\text{ReRAM}$ stack switching under $10\mu\text{A}$ current compliance [7]                                                                                                                                   | 79  |

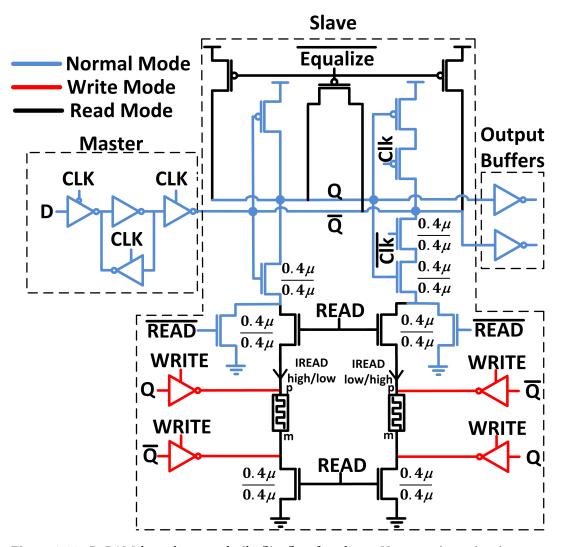

| 3.20 | ReRAM-based non-volatile flip-flop for above- $V_T$ operation; circuit parts are                                                                                                                                                                       |     |

|      | highlighted in colors according to their activation for different operating modes                                                                                                                                                                      | 80  |

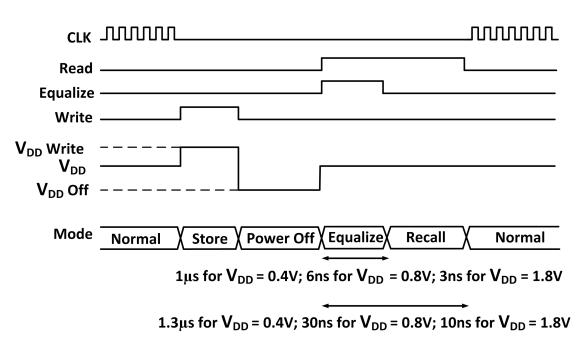

|      | Control signals sequence for ReRAM read and write operations                                                                                                                                                                                           | 82  |

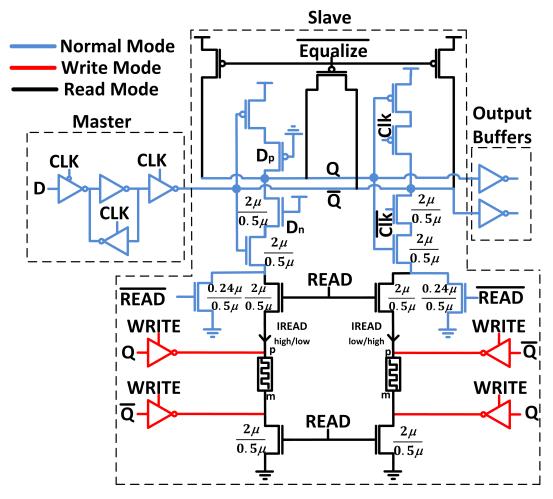

| 3.22 | ReRAM-based non-volatile flip-flop optimized for robust sub- $V_T$ operation; circuit parts are highlighted in colors according to their activation for different                                                                                      |     |

|      | operating modes                                                                                                                                                                                                                                        | 83  |

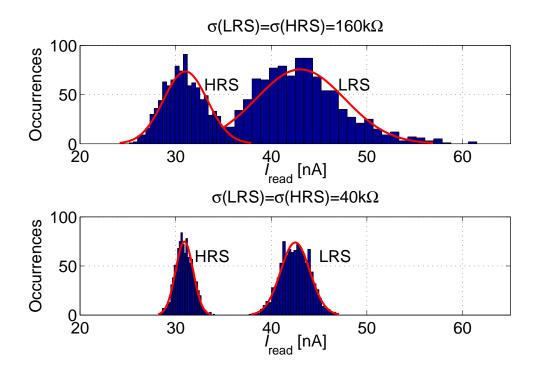

| 3.23 | Statistical distribution of the discharge current ( $I_{\text{read}}$ ) through the two branches of the slave latch of the sub- $V_{\text{T}}$ -optimized non-volatile flip-flop, for 0.4 V, given                                                     | 0.5 |

| 0.04 | for two different standard deviations of the ReRAM's resistance                                                                                                                                                                                        | 85  |

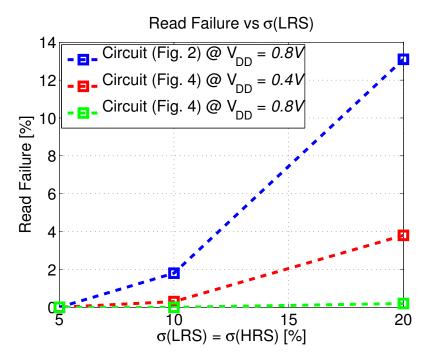

| 3.24 | Read failure probability for a ReRAM resistance's standard deviation of 5%, 10%, and 20% of the nominal LRS value. Parametric variations of MOS transistors are                                                                                        | 0.0 |

| 2.25 | also accounted for, according to statistical distributions provided by the foundry                                                                                                                                                                     | 86  |

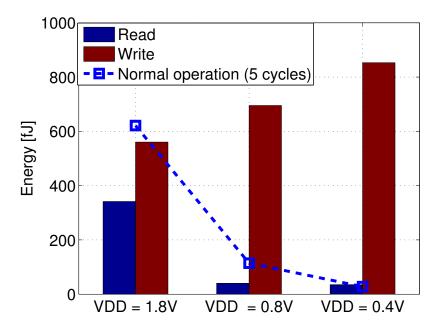

| 3.23 | Energy for read, write and five clock cycles of normal operation of the sub- $V_T$ - optimized non-volatile flip-flop                                                                                                                                  | 86  |

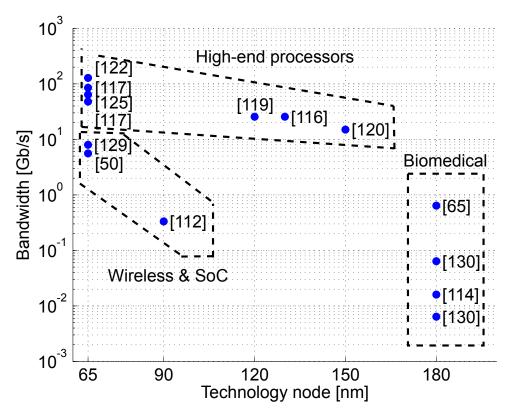

| 4.1  | Bandwidth vs. technology node of several published GC-eDRAM implementations                                                                                                                                                                            | 94  |

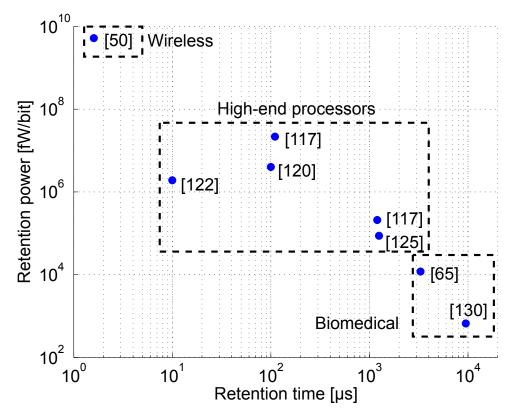

| 4.2  | Retention power vs. retention time for several published GC-eDRAM implemen-                                                                                                                                                                            |     |

|      | tations                                                                                                                                                                                                                                                | 95  |

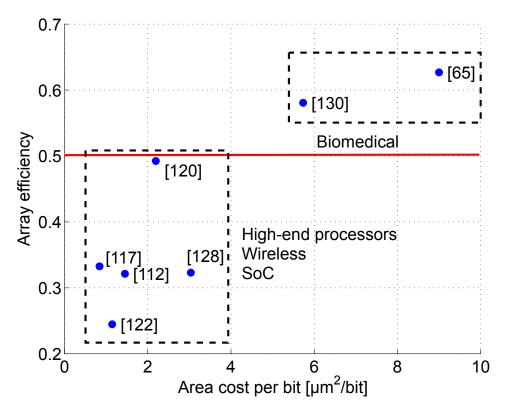

| 4.3  | Array efficiency vs. area cost per bit (ACPB) for several published GC-eDRAM                                                                                                                     |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | implementations                                                                                                                                                                                  | 96  |

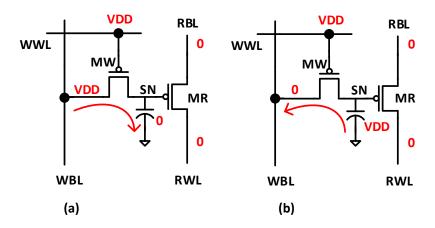

| 4.4  | 2-PMOS gain-cell; worst write bit-line (WBL) state for retention of (a) logic '0'                                                                                                                |     |

|      | and (b) logic '1'                                                                                                                                                                                | 102 |

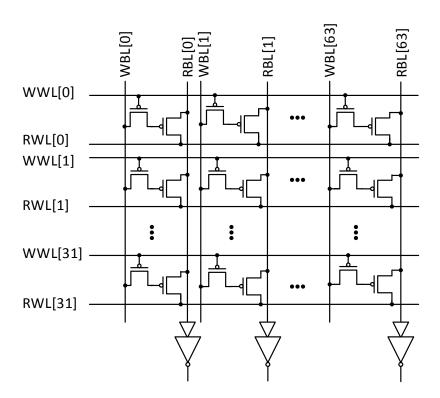

| 4.5  | 2T-bitcell GC-eDRAM storage array with area-efficient sense inverters                                                                                                                            | 103 |

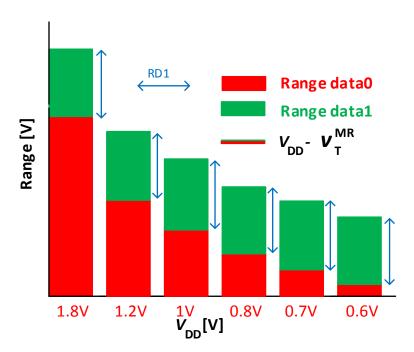

| 4.6  | Storage ranges (voltage ranges) for data '0' and '1' versus main supply voltage $V_{\rm DD}$                                                                                                     | 106 |

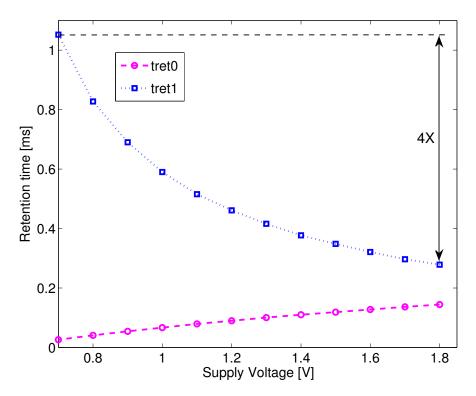

| 4.7  | Retention time versus $V_{\mathrm{DD}}$ for worst-case WBL state (always opposite to stored                                                                                                      |     |

|      | data)                                                                                                                                                                                            | 107 |

| 4.8  | WBL control for enhanced retention time                                                                                                                                                          | 108 |

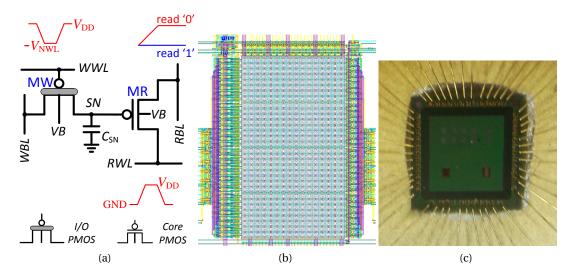

| 4.9  | (a) 2T gain-cell design and basic operation, (b) layout of 2 kb GC-eDRAM macro-                                                                                                                  |     |

|      | cell, and (c) microphotograph of test chip $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                        | 112 |

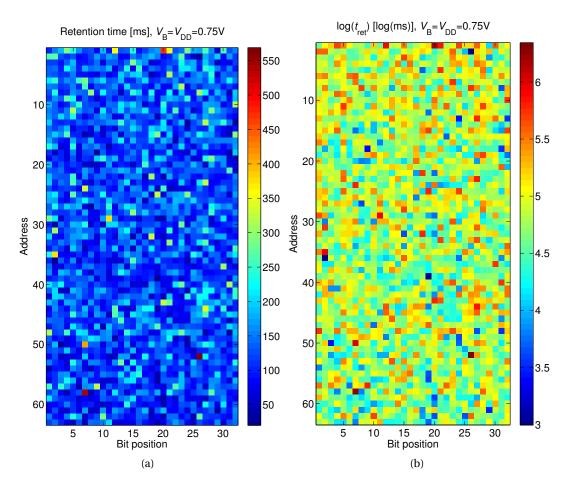

| 4.10 | (a) Retention time ( $t_{\text{ret}}$ ) map of 2 kb 2T gain-cell array with standard body bias                                                                                                   |     |

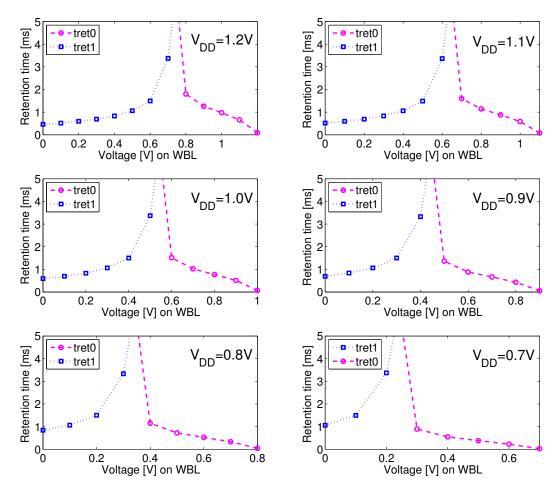

|      | and $\alpha_{	ext{disturb}}$ =25% at room temperature, and (b) map of $\log(t_{ret})$                                                                                                            | 114 |

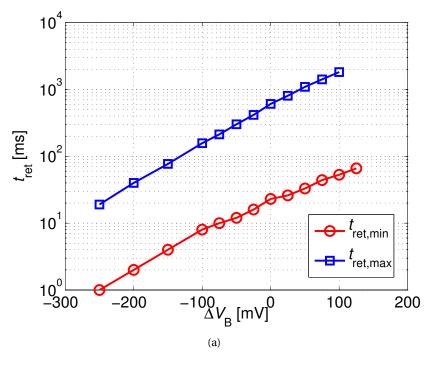

| 4.11 | $V_{\rm DD} = 750\mathrm{mV}$ with $\alpha_{\rm disturb} = 25\%$ at room temperature: (a) Minimum ( $t_{\rm ret,min}$ )                                                                          |     |

|      | and maximum ( $t_{\rm ret,max}$ ) retention times across the entire 2 kb array, as a function                                                                                                    |     |

|      | of $\Delta V_{\rm B}$ , and (b) retention time distributions of 2048 measured gain-cells for                                                                                                     |     |

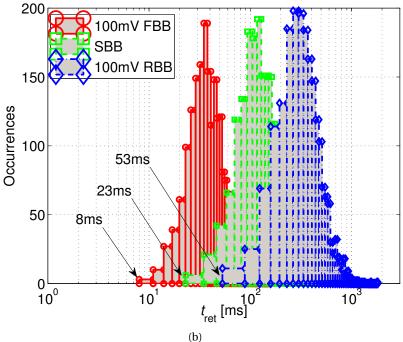

|      | 100 mV FBB, standard body biasing (SBB), and 100 mV RBB                                                                                                                                          | 115 |

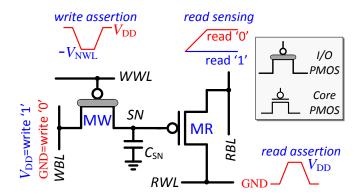

| 4.12 | Schematic of the all-PMOS 2T gain cell with I/O write transistor (MW), including                                                                                                                 |     |

|      | waveforms for write and read operations                                                                                                                                                          | 117 |

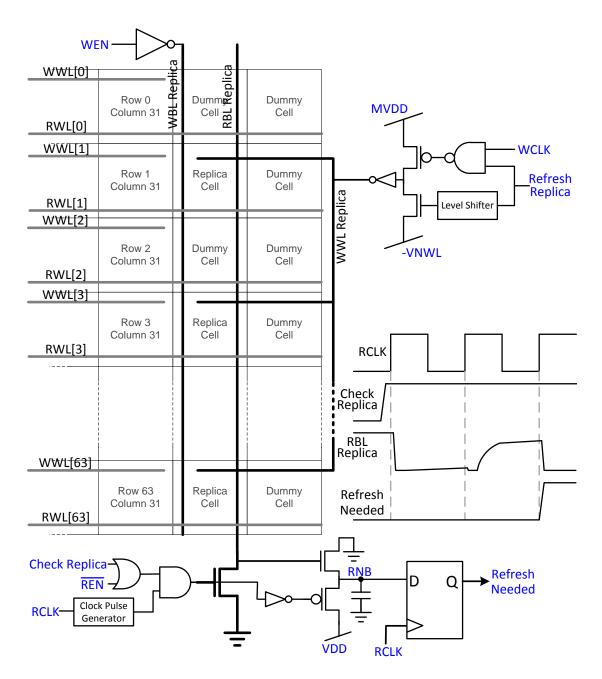

| 4.13 | Schematic illustration of the read and write circuitry for operation and control                                                                                                                 |     |

|      | of the proposed replica technique, including timing diagrams                                                                                                                                     | 119 |

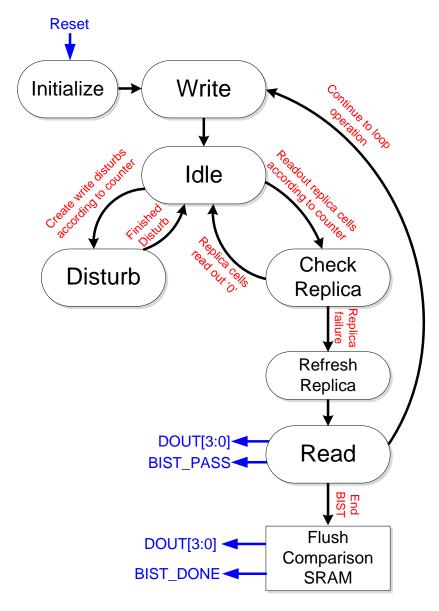

|      | State machine of the test controller                                                                                                                                                             | 121 |

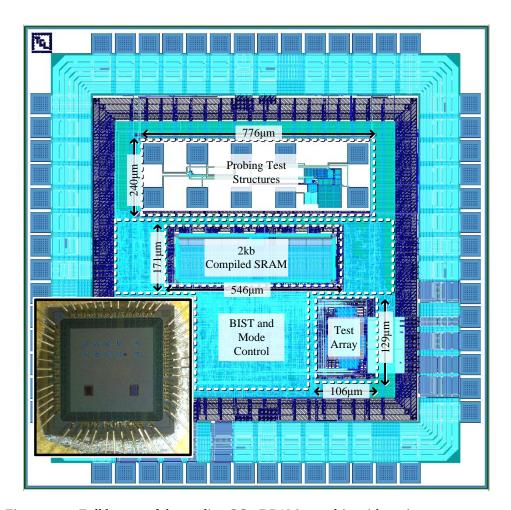

|      | Full layout of the replica GC-eDRAM test chip with major components                                                                                                                              | 122 |

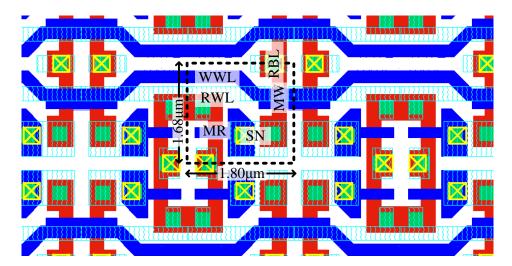

| 4.16 | Small section of the GC-eDRAM array layout showing the dimensions of the unit                                                                                                                    |     |

|      | cell                                                                                                                                                                                             | 123 |

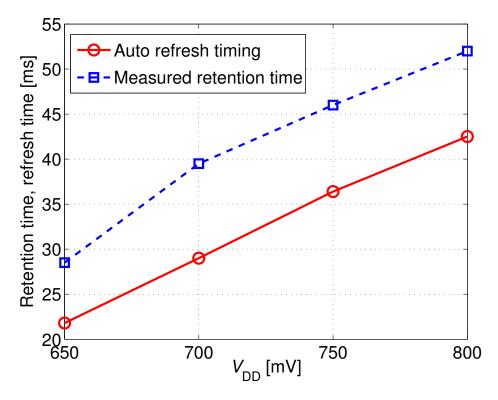

| 4.17 | Automatic refresh timing vs. measured retention time for a range of supply                                                                                                                       |     |

|      | voltages                                                                                                                                                                                         | 123 |

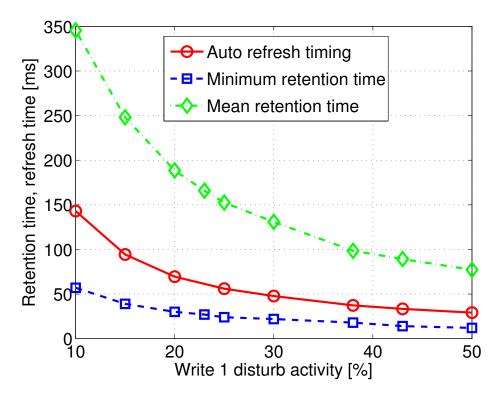

| 4.18 | Automatic refresh timing vs. measured retention time for a varying degree of                                                                                                                     |     |

|      | write disturbs                                                                                                                                                                                   | 124 |

| 4.19 | Dynamic power consumption of 2 kb GC-eDRAM array as a function of the write                                                                                                                      | 105 |

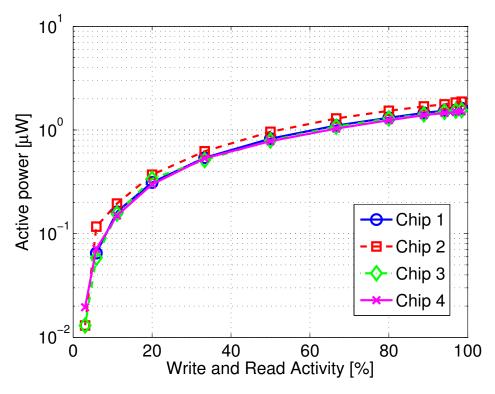

|      | and read activity factor for several measured chips                                                                                                                                              | 125 |

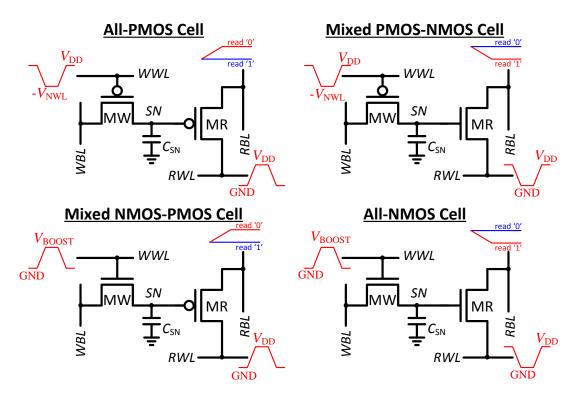

|      | 2T gain-cell implementation options including the schematic waveforms                                                                                                                            | 129 |

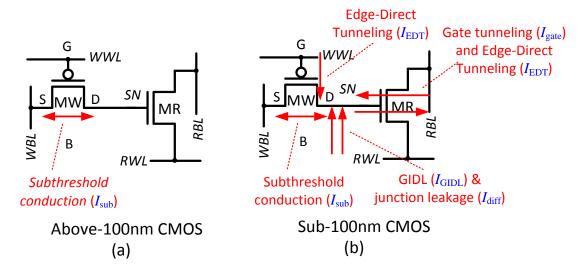

| 4.21 | Leakage components which are considered for the choice of the best-practice                                                                                                                      |     |

|      | write and read transistor implementations, for (a) mature CMOS nodes, and (b)                                                                                                                    | 120 |

| 4.00 | scaled CMOS nodes                                                                                                                                                                                | 130 |

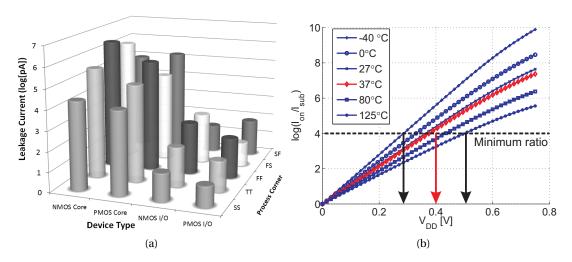

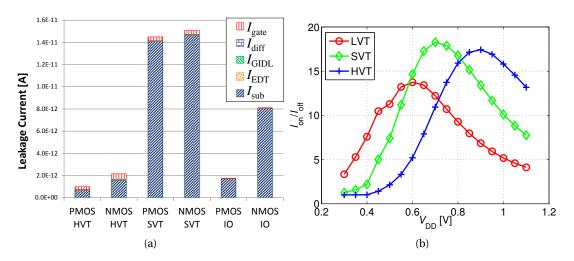

| 4.22 | (a) Subthreshold conduction of different transistor types in an 0.18 $\mu$ m node, and (b) I/O PMOS $I_{\rm on}/I_{\rm sub}$ current ratio as a function of $V_{\rm DD}$ for the typical-typical |     |

|      | (TT) process corner at different temperatures                                                                                                                                                    | 132 |

| A 22 | (a) Worst-case retention time estimation of 0.18 $\mu$ m sub- $V_T$ gain-cell with $V_{DD}$ =                                                                                                    | 102 |

| 4.23 | 400 mV. (b) Best-practice gain-cell for sub- $V_{\rm T}$ operation in 0.18 $\mu$ m CMOS                                                                                                          | 133 |

|      | 100 m. (b) Dest-practice gain-cent of sub-v1 operation in 0.10 µm CNOS                                                                                                                           | 100 |

| 4.24 | (a) Leakage components of various devices in the considered 40 nm node at a                                                 |     |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|      | near- $V_{\rm T}$ supply voltage of 600 mV. (b) Worst-case $I_{\rm on}({\rm weak'1'})/I_{\rm off}({\rm weak'0'})$ of        |     |

|      | MR, implemented with LVT, SVT, and HVT devices. Both plots were simulated                                                   | 104 |

|      | under typical conditions                                                                                                    | 134 |

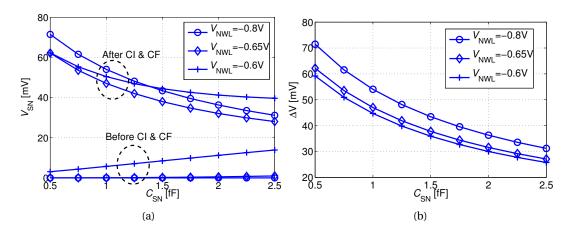

| 4.25 | Following a write '0' operation: (a) $V_{\rm SN}$ before and after closing MW, as a function                                |     |

|      | of $C_{\rm SN}$ and $V_{\rm NWL}$ . (b) $\Delta V$ due to charge injection from MW and due to capacitive                    |     |

|      | coupling from WWL to SN                                                                                                     | 136 |

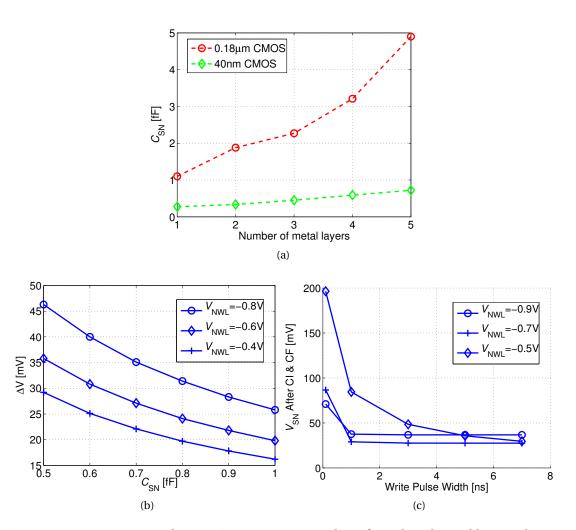

| 4.26 | (a) Storage node capacitance versus number of employed metal layers. (b) $\Delta V$                                         |     |

|      | due to CI and CF, as a function of $C_{\rm SN}$ and $V_{\rm NWL}$ , for $V_{\rm DD} = 700{\rm mV}$ . (c) $V_{\rm SN}$ after |     |

|      | CI and CF versus write pulse width                                                                                          | 137 |

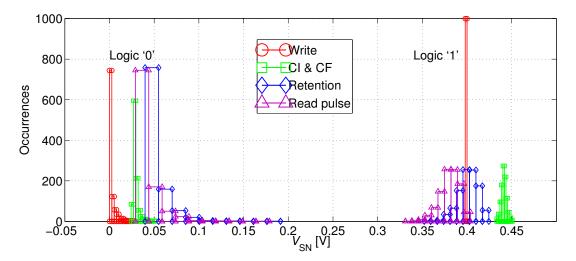

| 4.27 | Distribution of the SN voltage of a logic '0' and a logic '1' at critical time points:                                      |     |

|      | 1) [circles] directly after a 1 $\mu$ s write access (before turning off MW); 2) [squares]                                  |     |

|      | after turning off MW; 3) [diamonds] after a 40 ms retention period under worst-                                             |     |

|      | case WBL conditions; and 4) [triangles] during a read operation $\ \ldots \ \ldots \ \ldots$                                | 138 |

| 4.28 | Distribution of RBL voltage ( $V_{\rm RBL}$ ) after read '1' [circles] and read '0' [diamonds]                              |     |

|      | operations and distribution of the trip-point $V_{\rm M}$ of the read buffer [squares], for                                 |     |

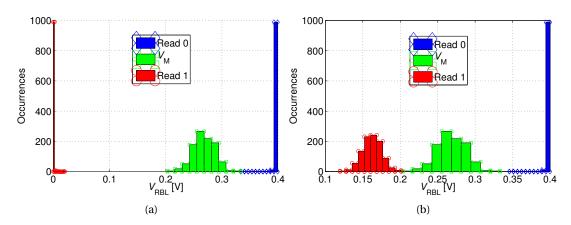

|      | (a) favorable and (b) unfavorable read '1' conditions $\ldots \ldots \ldots \ldots$                                         | 139 |

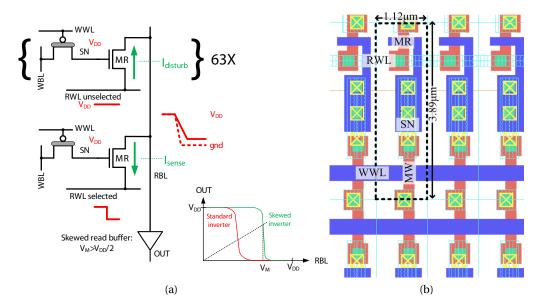

| 4.29 | 180 nm gain-cell array: (a) Worst-case for read '1' operation: all cells in the same                                        |     |

|      | column store data '1'. To make the '1' operation more robust, the sense inverter                                            |     |

|      | is skewed, with a trip-point $V_{\rm M} > V_{_{\rm DD}}/2$ . (b) Zoomed-in layout                                           | 140 |

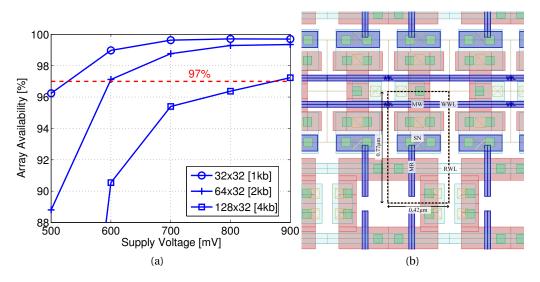

| 4.30 | 40 nm gain-cell array: (a) array availability as a function of supply voltage and                                           |     |

|      | array size; and (b) zoomed-in layout                                                                                        | 141 |

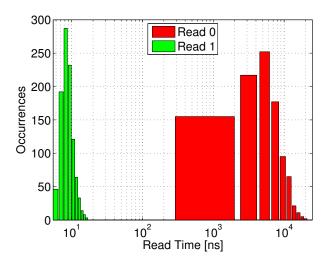

| 4.31 | Read access time distribution for the GC-eDRAM implementation in 40 nm                                                      |     |

|      | CMOS: RBL discharge time for correct data '1' sensing, and undesired RBL                                                    |     |

|      | discharge time till sensing threshold through leakage for data '0' $\dots \dots$                                            | 142 |

| 4.32 | Sense amplifier connected to the gain cell being read and to the reference gain                                             |     |

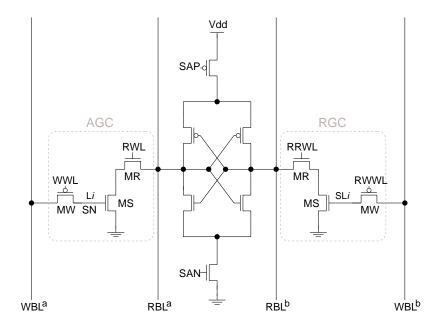

|      | cell; the multilevel gain-cell topology is shown in the gray box                                                            | 147 |

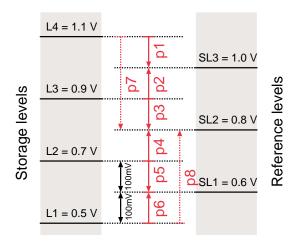

| 4.33 | Allocation of storage and reference levels                                                                                  | 147 |

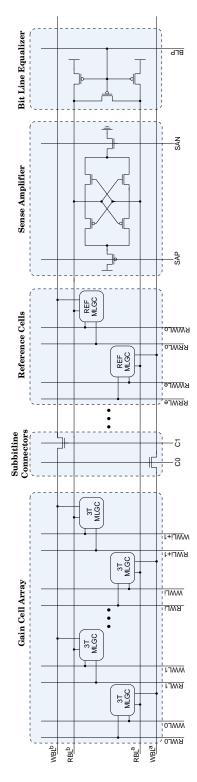

| 4.34 | Multilevel GC-eDRAM macrocell architecture                                                                                  | 149 |

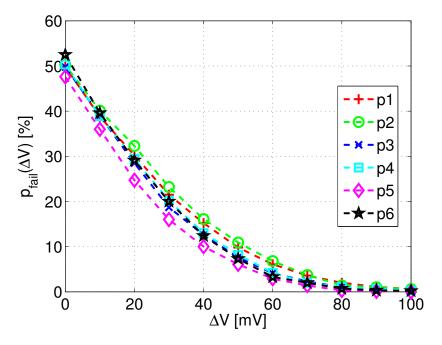

| 4.35 | Read failure probability $p_{\text{fail}}$ as a function of $\Delta V$ under <i>worst</i> -case conditions                  |     |

|      | (defined in Table 4.5)                                                                                                      | 151 |

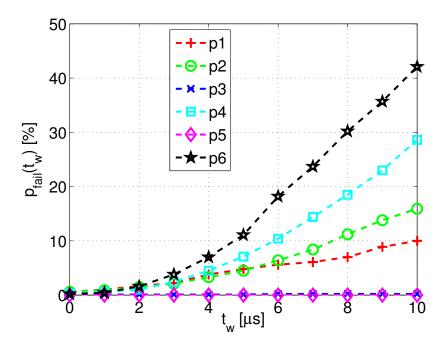

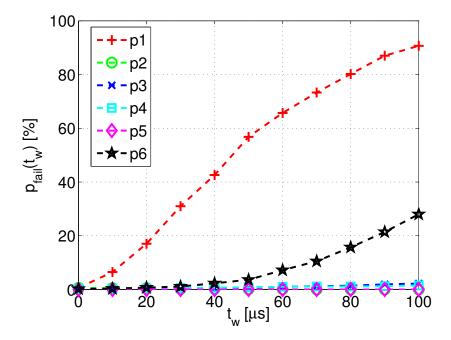

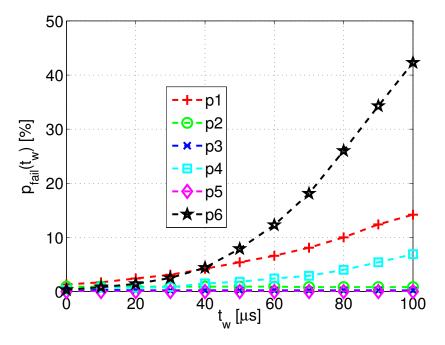

| 4.36 | Read failure probability $p_{\mathrm{fail}}(t_{\mathrm{w}})$ as a function of the time upon write $t_{\mathrm{w}}$ under    |     |

|      | worst-case conditions (defined in Table 4.5)                                                                                | 152 |

| 4.37 | Read failure probability $p_{\mathrm{fail}}(t_{\mathrm{w}})$ as a function of the time upon write $t_{\mathrm{w}}$ under    |     |

|      | bad conditions (defined in Table 4.5)                                                                                       | 153 |

| 4.38 | Read failure probability $p_{\mathrm{fail}}(t_{\mathrm{w}})$ as a function of the time upon write $t_{\mathrm{w}}$ under    |     |

|      | <i>typical</i> conditions (defined in Table 4.5)                                                                            | 153 |

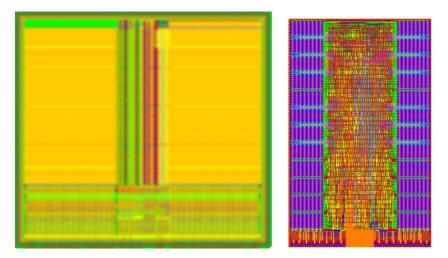

| 4.39 | Commercially available SRAM macrocell (left) and proposed multilevel GC-                                                    |     |

|      | eDRAM macrocell (right)                                                                                                     | 156 |

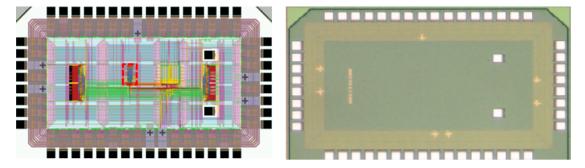

| 4.40 | Layout picture (left) and microphotograph (right) of multilevel GC-eDRAM test                                               |     |

|      | chip; the multilevel GC-eDRAM macrocell described in this section is highlighted                                            |     |

|      | by a dashed red line in the layout picture                                                                                  | 156 |

|      |                                                                                                                             |     |

## **List of Tables**

| 1.1 | Memory requirements of different classes of VLSI SoCs                                       | 7   |

|-----|---------------------------------------------------------------------------------------------|-----|

| 2.1 | Flip-flop based SCM, CG write logic, 0.13 µm CMOS: area and power for multi-                |     |

|     | plexer and 3-state read logic for different configurations $R \times C$                     | 23  |

| 2.2 | Flip-flop based SCM, CG write logic, $R = 16$ , $C = 128$ : area and power for multi-       |     |

|     | plexer and 3-state read logic for different technologies and standard cell libraries        | 23  |

| 2.3 | Area and power of SCM vs. SRAM based decoder                                                | 26  |

| 2.4 | Comparison of quasi-cyclic (QC)-LDPC decoder implementations                                | 29  |

| 2.5 | Memory sizes, retention times, and update rates                                             | 37  |

| 2.6 | Comparison with prior-art LDPC decoder implementations                                      | 43  |

| 3.1 | Standard-cell area $A_{SC}$ and area $A_{P\&R}$ of fully placed and routed latch and flip-  |     |

|     | flop arrays for different configurations $R \times C$ , clock-gate based write logic, and   |     |

|     | multiplexer based read logic                                                                | 59  |

| 3.2 | Comparison of sub- $V_{\rm T}$ memories                                                     | 65  |

| 3.3 | Read bit-line (RBL) delay, TT corner, 27 °C                                                 | 71  |

| 3.4 | Comparison with prior-art sub- $V_{\rm T}$ memories in 65 nm CMOS                           | 76  |

| 4.1 | Overview of gain-cell circuit techniques according to target applications                   | 97  |

| 4.2 | Comparison of low-voltage GC-eDRAM storage arrays                                           | 109 |

| 4.3 | Measurement setup for GC-eDRAM test chip with adaptive body bias control                    | 113 |

| 4.4 | Figures of merit for $0.18\mu\text{CMOS}$ and $40\text{nm}$ CMOS ultra-low voltage GC-eDRAM |     |

|     | macrocells                                                                                  | 14  |

| 4.5 | Definition of operating conditions                                                          | 15  |

| 4.6 | Total access times for different PVT conditions                                             | 155 |

## 1 Introduction

### 1.1 Increasing Need for Embedded Memories in VLSI SoCs