# This document is downloaded from DR-NTU, Nanyang Technological University Library, Singapore.

| Title     | Antenna-in-package design for wirebond interconnection to highly integrated 60-GHz radios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Author(s) | Zhang, Yue Ping; Wai, L. L.; Chua, Kai Meng; Sun, Mei;<br>Liu, Duixian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Citation  | Zhang, Y. P., Wai, L. L., Chua, K. M., Sun, M., & Liu, D. (2009). Antenna-in-package design for wirebond interconnection to highly-integrated 60-GHz radios. IEEE Transactions on Antennas and Propagation. 57(10), 2842 -2852.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Date      | 2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| URL       | http://hdl.handle.net/10220/6267                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Rights    | © 2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. http://www.ieee.org/portal/site This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. |  |  |  |  |  |

# Antenna-in-Package Design for Wirebond Interconnection to Highly Integrated 60-GHz Radios

Y. P. Zhang, M. Sun, K. M. Chua, L. L. Wai, and Duixian Liu, Senior Member, IEEE

Abstract—This paper first presents a quasi-cavity-backed, guard-ring-directed, substrate-material-modulated slot antenna. The antenna, intended for use in highly integrated 60-GHz radios, is deliberately designed to exhibit capacitive input impedance to suit low-cost wire-bonding packaging and assembly technique. The antenna implemented in a thin cavity-down ceramic ball grid array (CBGA) package in low-temperature cofired ceramic (LTCC) technology has achieved an acceptable impedance bandwidth from 59 to 65 GHz with an estimated efficiency of 94%. At millimeter-wave (mm-wave) frequency 60 GHz, one of key challenges is how to realize low-loss interconnection between a radio chip and an antenna using wire-bonding technique. This paper then addresses this issue in the framework of antenna-in-package (AiP) design at 60 GHz and proposes a new solution to the challenge. Detailed wirebond design method and results are given. A major concern with AiP is the risk of the antenna coupling to the radio chip. This paper also evaluates this unwanted coupling and shows that the coupling from the in-package antenna to the on-chip inductor is lower than 30 dB for the worst case. These results clearly demonstrate the feasibility and promise of the elegant AiP technology for emerging high-speed short-range 60-GHz wireless communications.

Index Terms—Antenna in package (AiP), low-temperature cofired ceramic (LTCC), 60-GHz radio.

# I. INTRODUCTION

N IEEE standards group, 802.15.3c, is defining specifications for 60-GHz radios to use a few gigahertz of unlicensed spectrum to enable very high-data-rate applications such as high-speed Internet access, streaming content downloads, and wireless data bus for cable replacement. The targeted data rate for these applications is greater than 2 Gb/s [1].

The 60-GHz radios have been typically designed as an assembly of several microwave monolithic integrated circuits (MMICs) in gallium arsenide (GaAs) semiconductor technology. They have been used for Gigabit Ethernet (1.25 Gb/s) bridges between local area networks [2]. A recent work has

Manuscript received June 26, 2008; revised April 08, 2009. First published August 04, 2009; current version published October 07, 2009.

Y. P. Zhang and M. Sun are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore (e-mail: eypzhang@ntu.edu.sg; sunmei@ntu.edu.sg).

K. M. Chua and L. L. Wai are with the Singapore Institute of Manufacturing Technology, Singapore 638075, Singapore (e-mail: kmchua@SIMTech.a-star.edu.sg).

D. Liu is with the IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 USA (e-mail: duixian@us.ibm.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TAP.2009.2029290

pushed up the data rate to 1.5 Gb/s with simple amplitude shift-keying (ASK) modulation using single-chip transmitter (Tx) and receiver (Rx) MMICs in a 0.15-μm GaAs process [3]. It should be mentioned that the data rate of 1.5 Gb/s is limited by the measurement system and the same MMICs are especially well suited for transmission and reception of 60-GHz signals at data rates of several Gb/s [3]. However, it is generally believed that the 60-GHz radios in GaAs MMICs are rather bulky [2] and expensive [2], [3]. In order for 60-GHz radios to have mass deployment and meet consumer marketplace requirements, the cost and size of any solution thus have to be cheap and compact. That means Si (silicon), not the GaAs used today [1]. In fact, designs towards low-cost highly integrated 60-GHz radios have been carried out in Si technologies. Floyd et al. have demonstrated the first 60-GHz fully integrated radio transmitter and receiver chipset in a 0.13-\mu m silicon-germanium (SiGe) technology [4]. However, CMOS is the lowest cost and highest integration option. Today, bulk CMOS at nodes 130, 90, and 65 nm are capable of power gain at 60 GHz. Razavi has demonstrated a 60-GHz radio transceiver chip in a 130-nm CMOS [5] and Toshiya et al. a 60-GHz receiver chip in a 90-nm CMOS [6]. Building-block circuits in a 65-nm CMOS have also been designed and characterized [7]. As CMOS scales, it is expected that future bulk CMOS at nodes 45 and 22 nm will provide higher power gain at 60 GHz with lower power consumption.

An antenna plays a key role in a radio as it has independent properties that affect the radio as a whole. Antenna designs for highly integrated radios operating at 60 GHz or above are shifting from conventional discrete designs to antenna-on-chip (AoC) and antenna-in-package (AiP) solutions [8]–[20]. This is because the antenna form factor at 60 GHz is on the order of millimeters or less, which opens up new integration options on a chip or in a package. Zhang et al. evaluated the AoC solution for 60-GHz radio on a silicon substrate and found that both inverted-F and quasi-Yagi on-chip antennas have very poor radiation efficiency, about 5% due to the low resistivity and high permittivity of the silicon substrate [8]. Micromachining techniques and proton implantation process have been proposed to reduce silicon substrate loss so as to improve the AoC radiation efficiency [9], [10]. However, use of them has deviated from mainstream silicon technology, which undoubtedly increases the cost of the total solution. Nevertheless, the realization of a truly single-chip 60-GHz radio and avoidance of transmission loss due to interconnect are yet encouraging particularly circuit designers to explore the integration of an antenna (or antennas) with other circuits on a single chip [6], [12], [13]. The AiP solution was originally proposed and demonstrated at frequencies below 6 GHz [14], [15]. Recently, it has

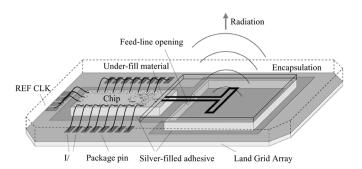

Fig. 1. Conceptional drawing of AiP by IBM.

begun to receive great attention among 60-GHz radio developers, for example, the IBM researchers have demonstrated a complete AiP solution for 60-GHz radios in a land grid array package using plastic mould injection technology, and showed that a folded dipole antenna suspended in a metal cavity has very good radiation efficiency of about 90% [16]–[18]. The Toshiba engineers have demonstrated another AiP solution, which connects the chip 60-GHz input and output pads to the metal plate on the chip mounting substrate with bonding wires to form a three-dimensional triangular loop. The three-dimensional triangular loop creates distance between the chip and the strong electric current, thereby minimizing deterioration of efficiency [19]. The low-temperature cofired ceramic (LTCC) and liquid crystal polymer (LCP) processes have been added to the short list of technologies capable of realizing mm-wave wireless systems [20]. In this paper, we present a novel wirebond AiP in LTCC technology for highly integrated 60-GHz radios. The design, fabrication, and test of the AiP with an emphasis on the antenna part are described in Section II. Detailed wirebond design method and results are discussed in Section III. Unwanted coupling of the antenna to the radio chip in the AiP is evaluated in Section IV. Finally, we conclude the paper in Section V with an outline of future developments.

#### II. ANTENNA-IN-PACKAGE

Driven by the great potential of the high-speed short-range wireless communications in the 60-GHz band, several AiP designs based on different packaging materials and technologies have been demonstrated. In this section, we first review them and then focus on our wirebond AiP in LTCC. Given that the AiP should be a chip-scale package, we are required to achieve such specifications as wider impedance bandwidth from 59 to 64 GHz, broader beamwidth with peak gain equal to or larger than 6 dBi, and radiation efficiency equal to or better than 80% at the central frequency 61.5 GHz.

## A. Mini-Review of 60-GHz AiP Designs

Fig. 1 shows the conceptional drawing of the AiP in a land grid array (LGA) by IBM [16]–[18]. As shown, standard wire bonding is used, except for the 60-GHz signal between the chip and the antenna. The antenna is constructed from a fused silica (SiO<sub>2</sub>) substrate, which is bonded to a covar metal frame using

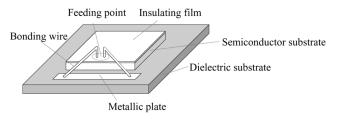

Fig. 2. Conceptional drawing of AiP by Toshiba.

a thermosetting adhesive. A chemical etching and photolithography process was used for frame fabrication. The antenna is flipped to the chip using a thermal compression flip-chip bonding technique. Simultaneously, the antenna frame is attached to the package base using a silver-filled adhesive. This way, the antenna is suspended in air below the silica superstrate and the metallic base plate of the package acts as a reflecting ground. The spacing between the radiating element and the ground influences the bandwidth of the antenna and is defined by the thickness of the cover frame, which serves two purposes. First, it provides the mechanical support for the antenna, and second, it provides a well-controlled electromagnetic (EM) environment, making the antenna performance less sensitive to the surrounding package- and PCB-level dielectric and metal layers. In this configuration, the folded-dipole antenna achieves 7-dBi gain (in package) at 60 GHz and over 10% impedance bandwidth. Review of this AiP shows that use of the frame decouples the design of the antenna from the exact physical properties of the package, simplifies simulation and modeling complexity, and avoids any unknown shapes or encapsulants in close proximity to the radiating element. Special care, however, is required for the antenna feed line and flip-chip bonding that interface the chip to the antenna. A dedicated opening, an encapsulation prior to the mounting of the antenna, and a ball height of 30  $\mu$ m (100  $\mu$ m for mass production) make it difficult to fabricate and assemble this AiP.

Fig. 2 shows the conceptional drawing of the AiP by Toshiba [19]. It is seen that the feeding point on the chip is connected to the metal plate on the package substrate with bonding wires to form a three-dimensional triangular loop. As the antenna element is directly connected to the feeding point on the high-loss silicon chip, there is no feeder loss. The three-dimensional triangular loop creates distance between the semiconductor chip and the strong electric current, thereby minimizing deterioration of efficiency. Moreover, by widening the metal plate on the package substrate there is greater tolerance of wire displacement occurring during the manufacturing process. Furthermore, since no special process is required for connecting the bonding wires, extra work in the manufacturing process due to changes in the structure of the antenna is minimal. Although this AiP solution is cheap, the antenna gain -0.3 dBi is quite low and needs to be improved by adding a parasitic element on the package substrate. It is also difficult, if not impossible, for 60-GHz radios where more antennas are required.

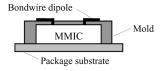

Fig. 3 shows the conceptional drawing of the AiP by the Micro Radio Group at Nanyang Technological University

Fig. 3. Conceptional drawing of AiP by NTU.

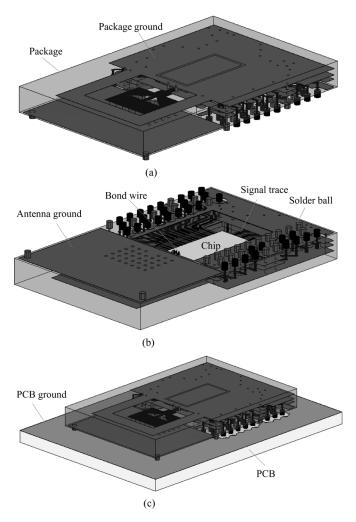

Fig. 4. Partially transparent views of the AiP: (a) top, (b) bottom, and (c) landing on the PCB.

(NTU), Singapore. It has the same advantages and disadvantages as the AiP solution by Toshiba.

In addition, it should be mentioned that there have been some important works similar to AiP for system-on-package or multichip solutions of 60-GHz radios in ceramic and plastic (Teflon and LCP) packages [20]–[27].

## B. An AiP Design in LTCC

An international team consisting of researchers from NTU, Singapore Institute of Manufacturing Technology (SIMTech), and IBM has been working closely over the last three years to develop the AiP solutions in LTCC targeted to the IBM 60-GHz radio chip set with mass production capability [28], [29]. Fig. 4 shows the top and bottom partially transparent views of the AiP for the Rx chip of size  $3.55 \times 1.75 \times 0.46$  mm<sup>3</sup>. As shown, the AiP features standard wire bonding. A three-tier cavity facilitates chip mounting and efficient utilization of available space

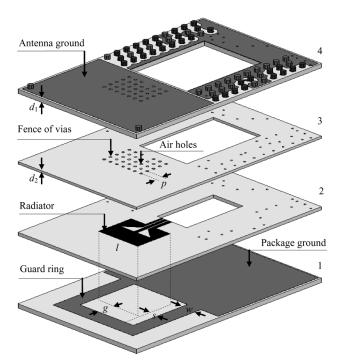

Fig. 5. Exploded view and dimensions of the AiP. The outer ring of vias is the fence of vias and the inner rings of vias are air holes.

for signal routing and also to enable reduced parasitic from wire bonding. The radio chip is adhered to the cavity base of the package ground plane. This configuration will contribute to the shielding of the chip from the antenna. The signals from the chip are connected to the antenna through bondwires in a ground–signal–ground (G-S-G) configuration. The other signals from the chip are connected to the outside PCB by the bondwires, signal traces, vias, and solder balls. The ground planes in five layers are all connected by vias and they are also connected to the outside PCB by solder balls. The AiP has 58 input/outputs with a JEDEC (Joint Electronic Device Engineering Council) standard solder ball pitch of 0.65 mm. Two dummy solder balls are attached to the two corners of the AiP, respectively, for the finishing touch on the system PCB.

Fig. 5 shows the dimensions of the AiP in FERRO A6 LTCC  $(\varepsilon_r = 5.9 \text{ and } \delta = 0.002)$ . Note there are four cofired laminated ceramic layers for the package. The first ceramic layer is 0.385 mm thick, the second ceramic layer is 0.285 mm thick with an opening  $3.8 \times 2 \text{ mm}^2$ , the third layer is 0.21 mm thick with an opening  $5 \times 3.2 \text{ mm}^2$ , and the fourth layer is 0.385 mm thick with an opening  $5 \times 3.8 \text{ mm}^2$ . These openings form the three-tier cavity that can house the 60-GHz radio Rx chip. There are also four metallic layers for the AiP. The top buried layer provides the metallization for the package ground plane and antenna guard ring, the second buried layer the metallization for the slot radiator and signal traces, the third buried layer the metallization for the signal traces, and the bottom exposed layer the metallization for the antenna ground plane and solder ball pads. The size of the whole AiP is  $12.5 \times 8 \times 1.265$  mm<sup>3</sup>. It is interesting to note that the antenna uses a triangular slot radiator to avoid warpage in LTCC fabrication. The l of the triangular slot is chosen to be one guided wavelength  $\lambda q$  to have broader bandwidth. A ground-plane reflector and a fence of vias

Fig. 6. Photo of the AiP.

Fig. 7. Illustration of the AiP on the fixture for testing.

are introduced. The fence of vias shorts the outer metal edge of the slot radiator to the reflector to form a quasi-cavity to create a well-controlled EM environment for the radiator of the AiP. The quasi-cavity is similar to the metal cavity used in [16], [24] and makes the antenna performance less sensitive to the carried radio chip, PCB dielectric and metallic structures, which is an important design feature for system integration. The depth d of the quasi-cavity is chosen to be  $\lambda g/4$  so that the radiation of the slot in free space can be enhanced by the reflector. The guard ring chosen to be  $\lambda g/2$  wide serves two purposes: one, it helps to suppress the surface wave  $(\lambda g/2)$  opened guard ring as an open circuit to the surface wave) and two, to focus the radiation as a director. The pitch p of vias should ideally be zero to form a wall rather than a fence. Realistically, it should be chosen to satisfy  $\lambda g/10$  [30]. The coplanar waveguide (CPW) feed line is designed to be 50  $\Omega$  with a pitch of 0.25 mm and a line width of 0.1 mm. The ceramic material under the slot radiator is modulated with air holes also to reduce surface wave. Thus, we have realized a novel CPW-fed quasi-cavity-backed, guard-ring-directed, substrate-material-modulated slot antenna with the following optimum values:  $l = 2.064 \text{ mm} \approx \lambda g$ ,  $d = d_1 + d_2 = 0.595 \text{ mm} \approx \lambda g/4, w = 0.925 \text{ mm} \approx \lambda g/2,$  $s = 0.442 \text{ mm}, g = 0.8156 \text{ mm}, p = 0.2 \text{ mm} \approx \lambda g/10.$

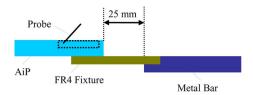

The AiP was fabricated with nine green types, silver and gold metals in a panel size of  $100 \times 100~\text{mm}^2$  by LTCC Boutique Foundry in SIMTech on the NTU campus. Fig. 6 shows the photo of the fabricated AiP. The antenna function of the AiP was tested with a probe-based measurement setup at IBM Thomas J. Watson Research Center, NY. Fig. 7 illustrates the test fixture to hold the AiP for testing.

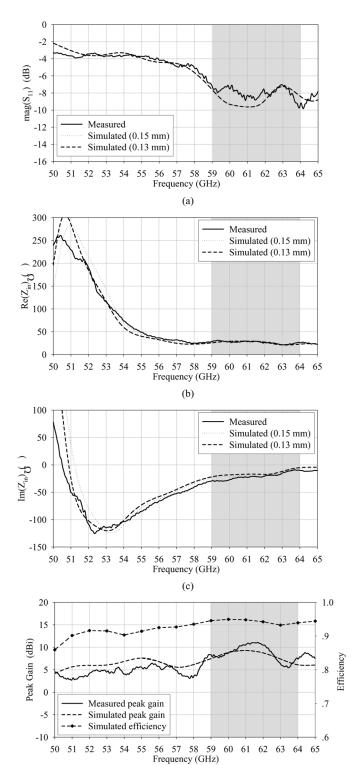

Fig. 8 shows the simulated and measured reflection and impedance of the AiP with the distances of 0.13 and 0.15 mm to account for the difference between the wave-port excitation in the simulation and the probe excitation in the measurement. The distances of 0.13 and 0.15 mm were estimated by inspection using the probe pitch of 0.25 mm as reference. It

Fig. 8. Simulated and measured reflection and impedances of the AiP: (a) magnitude of  $S_{11}$ , (b) real part of the input impedance, (c) imaginary part of the input impedance, and (d) peak gain and efficiency as a function of frequency.

is seen from Fig. 8(a) that the magnitude values of  $S_{11}$  are in good agreement and are lower than -7 dB from 59 to 65 GHz indicating an acceptable matching to a 50- $\Omega$  source at these frequencies. Fig. 8(b) and (c) shows the simulated and measured impedance values from 50 to 65 GHz. They are also in

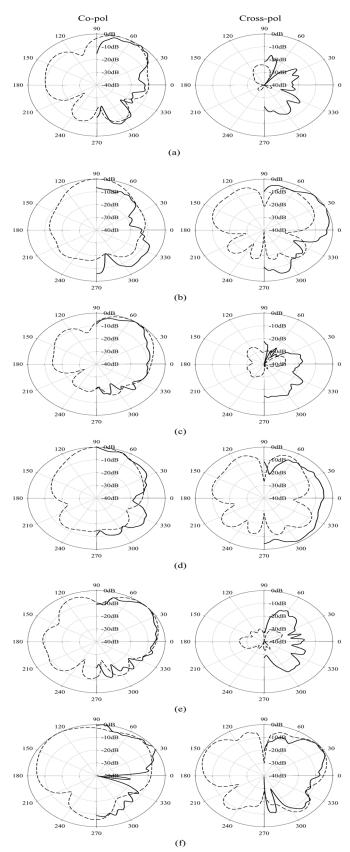

Fig. 9. Simulated (dash line) and measured (solid line) radiation patterns of the AiP: (a) E-plane patterns at 59 GHz; (b) H-plane patterns at 59 GHz; (c) E-plane patterns at 61.5 GHz; (d) H-plane patterns at 61.5 GHz; (e) E-plane patterns at 65 GHz; and (f) H-plane patterns at 65 GHz.

good agreement. As expected, the antenna exhibits capacitive reactance. The matching to the  $50-\Omega$  output impedance of the

Fig. 10. HFSS model of the antenna part of the AiP.

carried 60-GHz radio Rx chip will be improved if the inductive reactance from the bondwire is properly exploited. We will discuss this issue in Section III. The measured and calculated peak gain values for the AiP in the main beam direction are 11 and 9.5 dBi at 61.5 GHz, respectively, with an estimated efficiency of 94%, as shown in Fig. 8(d).

Fig. 9 shows the simulated and measured radiation patterns of the AiP. Due to a limitation of the measurement setup, the measured radiation patterns only extend from 90° to 270°. The simulation was done for only the antenna portion due to compute memory issues. This will not affect the antenna impedance, but it will have some effect on antenna radiation patterns. The simulated and measured radiation patterns of the AiP at 61.5 GHz reveal that the H-plane patterns are similar to, but the E-plane patterns are different from, those of a conventional cavity-backed slot antenna. A shaped-beam pattern can be seen in the co-polar E-plane with the main beam in the directions from 45° to 60°. The shaped-beam pattern in the co-polar E-plane is mainly caused by the package ground, which weakens the radiation of the antenna towards the chip.

The simulation was done in HFSS from Ansoft, Pittsburgh, PA, USA [31]. Fig. 10 shows the HFSS model for the impedance calculation of the antenna part with the wave-port excitation. The measurement of the antenna impedance of the AiP has validated the model, which should be expected as the excellent EM environment has been created in the AiP for the antenna. The design of the antenna from the exact physical properties of the package greatly simplifies simulation and modeling complexity.

#### III. WIREBOND DESIGN FOR THE AIP

At mm-wave frequency 60 GHz, the interconnection between the chip and the package using the wire-bonding technique has been identified as one of key challenges because the discontinuity introduced by the bondwire can significantly affect the performance of the entire radio at mm-wave frequency. Nonetheless, the wire-bonding technique, well established in consumer electronics, remains a very attractive solution since it is robust and inexpensive. In addition, it has the advantage of being tolerant of chip thermal expansion, an important requirement for many applications.

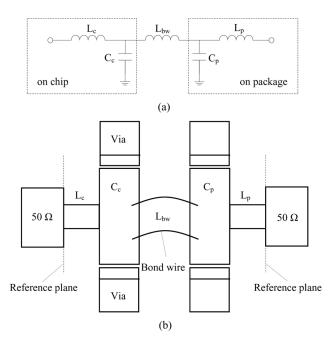

A number of studies on the electrical performance of wire-bonding interconnection have been reported for microstrip and coplanar configurations, indicating that a bondwire

Fig. 11. Budka's bondwire compensation scheme: (a) circuit model and (b) layout.

as a series inductor will increase the loss drastically as the frequency or the length is increased [32]-[34]. In order to improve the high-frequency performance of a bondwire interconnect, efforts have usually focused on reducing the length of the bondwire and also reducing the chip-to-package spacing. However, limitations in manufacturing require longer bondwire lengths and wider chip-to-package spacing to improve the yields of mm-wave chip-package assemblies. Therefore, the goal for mm-wave interconnect design is to maximize bondwire length to improve manufacturability and maximize bond-pad size so that mechanical tolerances are eased. Budka has demonstrated that this is possible with a filter theory approach to interconnect design as shown in Fig. 11 [35]. He has considered the conventional bondwire design as a single-stage low-pass filter while his novel design as a five-stage low-pass filter. Thus, for the same cutoff frequency of the single- and five-stage filter, the center inductor in the five-stage design can have a 3.6 times higher inductance than a single inductor design. This directly translates into a 3.6 times longer bondwire for the same cutoff frequency.

Budka's wirebond design technique enables the use of significantly longer bondwires but the chip must have filter-like compensation on the mm-wave bonding pads. This is usually impossible unless the codesign of the chip and package can be done. Also, Budka's method is not suitable for connecting the radio chip to the antenna because it is difficult to implement the DC blocking capacitor between them.

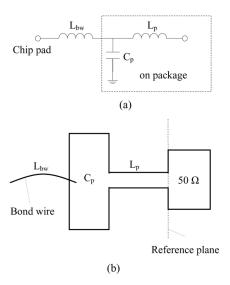

Sun *et al.* have demonstrated a T-network to compensate for the series inductance introduced by the bondwire as shown in Fig. 12 [36]. The inductor  $L_{\rm bw}$  models the bondwire inductance. Inductor  $L_{\rm p}$  and capacitor  $C_{\rm p}$  are realized on package. This compensation network has also been used in [24], but it has two drawbacks. One is the large on-package area required to implement  $L_{\rm p}$  and  $C_{\rm p}$ , and the other is that it is not suitable for

Fig. 12. Bondwire compensation scheme used in [36] and [23]: (a) circuit model and (b) layout.

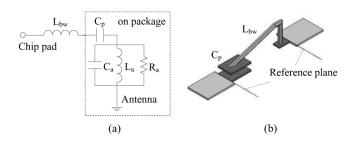

Fig. 13. New compensation scheme: (a) circuit model and (b) layout.

on-package CPW design. Also, Sun's method for connecting the radio chip to the antenna needs to implement the DC blocking capacitor on chip.

Fig. 13 shows the novel bondwire compensation scheme with the suggested structure proposed by Sun and Zhang [37]. As can be seen, a series capacitor is used to tune the inductance of the bondwire to a resonant condition, thus compensating the high inductance of bondwire at the resonant frequency. In the mm-wave frequency range, the form factor of the capacitor for compensation is on the order of tens of femtofarads, making the structure very compact. In addition, the compensation structure enjoys the properties of manufacturing reliability and cost effectiveness. It could be used successfully for the commonly used chip-to-package connections at mm-wave frequencies. This will be very desirable for highly integrated mm-wave wireless devices which call for the properties of miniaturization, manufacturing reliability, and mass-production cost effectiveness.

The compensation design involves the following steps [37]:

- 1) Identify the bondwire to be compensated.

- 2) Identify an operation frequency and bandwidth.

- 3) Model the bondwire to be compensated in the highly integrated device environment first and then simulate the electrical performance of the established model at the operating frequency band. Based on this simulation, the bondwire inductance to be compensated is obtained.

- 4) Construct a bondwire compensation structure as shown in Fig. 13 in the highly integrated device environment. Based

Fig. 14. Wire-bonding configurations: (a) without the compensation capacitor and (b) with the compensation capacitor.

on this structure the capacitor dimensions are estimated to compensate the inductance value calculated at the last step. Model this capacitive compensation structure to combine with the bondwire in the highly integrated device environment first and then optimize the frequency response of the established model to the optimal by just adjusting the bondwire compensation structure.

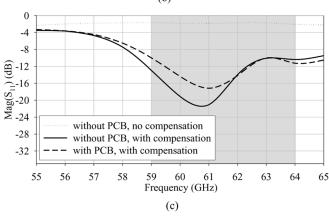

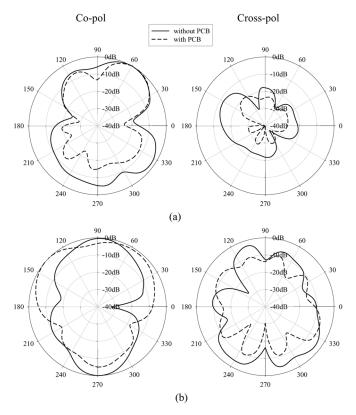

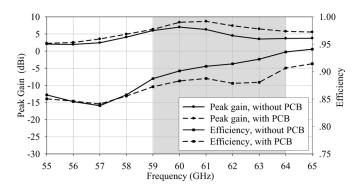

Fig. 14(a) illustrates the wire-bonding configuration of the highly integrated 60-GHz radio Rx chip with the antenna in the AiP. As shown in Fig. 15(a) and (b), the connection of the 400- $\mu$ m-long 25.4- $\mu$ m bondwire will not introduce significant resistance but  $\sim 120$  ohm inductive reactance at the frequency band of interest, 55-65 GHz. Accordingly, the return loss of the antenna degrades greatly as seen in Fig. 15(c). A significant degradation in the magnitude of S<sub>11</sub> to 1.9 dB at 61 GHz is observed. It is obvious that the antenna cannot work with the bondwire connected directly. Based on our compensation scheme, a capacitor in series with the signal bondwire as illustrated in Fig. 14(b) is implemented. Following the above steps, the inductive reactance at the 60-GHz band from 55 to 65 GHz has been compensated successfully as shown in Fig. 15(b). It is also seen from Fig. 15(c) that the magnitude of  $S_{11}$  of the AiP is now lower than -10 dB from 58.5-64.5 GHz, indicating a good matching to the 50- $\Omega$  chip. The other parameters of the antenna performance, such as gain, efficiency, and patterns, are also acceptable after compensation as shown in Figs. 16 and 17. The peak gain is found to be 7 dBi. These results clearly demonstrate that the antenna can work well using the bondwires with our novel bondwire compensation scheme. In addition, as shown in Fig. 8, the measurement and simulation results agree well without bondwires. Therefore, the simulation tool can be trusted to estimate the bondwire connection and compensation scheme as analyzed above. It can be seen that, using our bondwire compensation scheme, the designed AiP provides an extremely compact and elegant solution for communication systems operating at mm-wave frequencies. The scheme is easy to realize by only adding the capacitive coupling part. The compensation structure can be designed separately. Once it is designed well, it can be easily modified for other designs as well.

When the AiP is placed on the system PCB as shown in Fig. 4(c), the PCB board affects the antenna performance. This is confirmed by the simulation of landing the above bondwire-compensated AiP on a 15.7  $\times$  10  $\times$  0.8 mm $^3$  FR4 PCB. It is seen from Fig. 15 that the PCB changes the magnitude of  $S_{11}$  but the 10-dB impedance bandwidth still can cover the 59–64 GHz

Fig. 15. Simulated impedance and magnitude of S<sub>11</sub> of the AiP with bondwires as a function of frequency.

band. It is also seen from Fig. 16 that the PCB improves the AiP radiation in the upper hemisphere and reduces the AiP radiation in the lower semi-sphere. This leads to a high peak gain of 8.7 dBi as shown in Fig. 17, though the radiation efficiency degrades. In simulation, it is also found that the matching performance is insensitive to the further extended PCB, while the gain could be further improved.

Table I lists key data of this work with other AiP designs as well as related antenna solutions for highly integrated 60-GHz radios. We have no intention to compare them because it is difficult to make a fair comparison between the different solutions since they are fabricated in different technologies and meant for different purposes. Nevertheless, we can see from Table I that basic radiating elements such as dipole, slot, and patch are popular in AiP designs and excellent radiation efficiency can be

Fig. 16. Simulated patterns of the AiP with bondwires and compensation: (a) E-plane patterns at 61.5 GHz; (b) H-plane patterns at 61.5 GHz.

Fig. 17. Simulated gain and efficiency of the AiP with bondwires and compensation.

achieved in LTCC. Both wire-bonding and flip-chip techniques are used for interconnecting the antenna to the radio chip. The wirebond needs compensating, while the flip-chip does not. The compensation is usually made in the package not on the chip.

#### IV. EVALUATION OF UNWANTED COUPLING

A major concern with AiP is the risk of the antenna coupling to the radio chip. On-chip passive components such as inductors and capacitors occupy substantial die area and thus are susceptible to the antenna coupling. Here, taking an on-chip inductor as an example, we simulate the coupling from the in-package antenna to the on-chip inductor in terms of the magnitude of the transmission coefficient  $S_{21}$ .

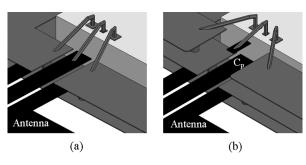

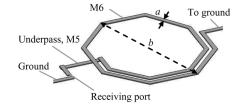

Fig. 18 shows the configuration of the on-chip spiral inductor. It is is implemented using two metal layers, M5 and M6 ( $\sigma$  =

Fig. 18. Inductor configuration in the coupling simulation.

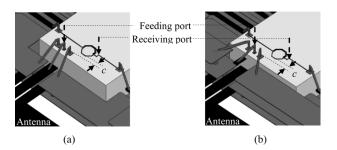

Fig. 19. Coupling simulation setups: (a) without the compensation capacitor and (b) with the compensation capacitor.

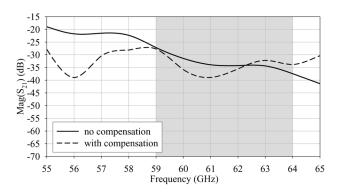

Fig. 20. Simulated  $|S_{21}|$  with c = 0.1 mm.

2.8e + 7 S/m), in a 9- $\mu$ m-thick SiO<sub>2</sub> ( $\varepsilon_r = 4$ ) layer on a 451- $\mu$ m-thick Si ( $\varepsilon_r = 11.9$  and  $\sigma = 10$  S/m) substrate. It has dimensions  $a=10~\mu\mathrm{m}$  and  $b=311~\mu\mathrm{m}$ . Fig. 19(a) and (b) shows the coupling simulation setups without and with the compensation capacitor, respectively. The on-chip inductor has one terminal connected to the package ground by a bondwire and the other terminal together with another grounded bondwire used as the receiving port. The feeding port to the antenna is located on the chip and excites the antenna through the G-S-G bondwires. Fig. 20 shows the simulated  $|S_{21}|$  as a function of frequency from 55 to 65 GHz under the worst condition. Here, we define the worst case as no guard ring and pattern grounded shield are used for the inductor and the distance between the inductor and antenna is the shortest allowed by the on-chip layout rule. Note that the coupling levels are both lower than 27.5 dB over the 60-GHz band for the cases with and without the compensation capacitor, respectively. The lower coupling is the result of good grounding and shielding design in the AiP. It is more interesting to note that the coupling fluctuates with frequency indicating multiple-coupling mechanisms. It is conjectured that there are inductive coupling from the G-S-G bondwires to the inductor, radiative coupling from the antenna to the inductor, and resistive coupling from the antenna feeding port to the in-

| Antennas  | Technology     | Radiator                   | Dimension (mm)           | Bandwidth (GHz)                                                              | Peak Gain (dBi) | Efficiency | Beamwidth    | Interconnection        |

|-----------|----------------|----------------------------|--------------------------|------------------------------------------------------------------------------|-----------------|------------|--------------|------------------------|

| This work | LTCC           | Slot                       | 12.5×8×1.265             | 59-65 ( S <sub>11</sub>  <=-7 dB)                                            | 11              | 94%        | ~30°         | Wirebond               |

| [16]      | Plastic        | Dipole                     | 13×13×2                  | 52-68 ( S <sub>11</sub>  <=-10dB )                                           | 7               | 90%        | 60°          | Flip chip              |

| [19]      | Plastic        | Loop                       | <4×4                     | -                                                                            | -0.4            | -          | >90°         | Wirebond               |

| [20]      | Teflon<br>LTCC | Patch array<br>Patch array | 10×10×1.1<br>10×10×0.45  | 60.9-61.8( S <sub>11</sub>  <=-10dB)<br>59.3-61.3( S <sub>11</sub>  <=-10dB) | 8.5<br>7.17     | >91%<br>-  | ~40°<br>~40° | Flip chip<br>Flip chip |

| [21]      | LTCC           | Patch array                | 10×10×0.3                | -                                                                            | 7               | -          | 36°          | Wirebond               |

| [22]      | LTCC           | Slot                       | 5×4×0.32                 | 62-64 ( S <sub>11</sub>  <=-10dB )                                           | 4               | -          | ~100°        | Flip chip              |

| [23]      | HTCC           | Patch array                | 1×12×0.127<br>5×10×0.127 | 59.2-60.7( S <sub>11</sub>  <=-10dB)<br>59.6-60.5( S <sub>11</sub>  <=-10dB) | 12<br>13        | -          | 20°<br>33°   | Wirebond<br>Wirebond   |

| [24]      | MEMS           | Dipole                     | ~13×6×0.7                | 56-65 ( S <sub>11</sub>  <=-10dB )                                           | 8               | 90%        | ~60°         | Flip chip              |

| [25]      | LTCC           | Slot array                 | -                        | 59-63 ( S <sub>11</sub>  <=-10dB )                                           | 19              | -          | ~10°         | -                      |

| [26]      | LTCC           | Patch array                | <9.6×1.5×0.32            | 55.4-66.8( S <sub>11</sub>  <=-10dB )                                        | 12.6            | -          | ~20°         | -                      |

| [27]      | LCP            | Patch array                | 17.4×2.1×0.15            | 56-65 (VSWR 2:1)                                                             | 12              | -          | ~20°         | -                      |

TABLE I

PERFORMANCE SUMMARY OF THE ANTENNA SOLUTIONS FOR HIGHLY INTEGRATED 60-GHZ RADIOS

ductor receiving port over the low-resistivity chip substrate. To further reduce the coupling, for the on-chip components an understanding of the impact of the process technology, grounding, guarding, shielding, and decoupling is necessary as suggested in [38], while for the in-package antenna, better radiation nulling toward the chip or new AiP structures needs to be devised.

#### V. CONCLUSION

A CPW-fed quasi-cavity-backed, guard-ring-directed, and substrate-material-modulated slot antenna has been designed, fabricated as an AiP in LTCC, and experimentally verified for highly integrated 60-GHz radios. The novel design concept and sophisticated LTCC process have guaranteed excellent performance of the antenna with an estimated efficiency of 94% at 61.5 GHz.

A mini-review of existing AiP designs for highly integrated 60-GHz radios has been given. Low-loss interconnection between the radio chip and the antenna was identified as one of key issues for the AiP designs. Interconnection using wire-bonding technique was particularly challenging as compared with the flip-chip technique and a new wirebond compensation scheme was proposed to overcome the challenge. It was shown from extensive simulations that a bondwire of 350-\mu m length could be used. The length of 350  $\mu$ m was almost a doubled length of the shortest bondwire supported by the current technology and would thus greatly improve the yield of assembly of the chip with the AiP. It was also shown that the AiP gain was reduced by the bondwire but the matching was improved. Furthermore, the risk of the antenna coupling to the radio chip in the AiP was evaluated and found that the coupling from the in-package antenna to the on-chip inductor was lower than 27.5 dB for the worst case.

We are currently working on the other issues such as integration of the AiP with the chipset and realization of an antenna-array-in-package in LTCC. We believe that the antenna design, AiP solution, and wirebond compensation scheme can be used in other technologies such as LCP or at even higher frequency, say, 100 GHz. It is therefore anticipated that the works

presented in this paper are useful and inspiring for those interested in the development of highly integrated mm-wave radios for emerging high-speed short-range wireless communications.

#### ACKNOWLEDGMENT

The first author would like to thank Dr. U. Pfeiffer and Dr. J. Grzyb for their helpful discussions when he visited IBM Thomas J. Watson Center on March 9, 2006.

#### REFERENCES

- S. K. Moore, "Cheap chips for next wireless frontier," *IEEE Spectrum*, pp. 8–9, Jun. 2006.

- [2] K. Ohata et al., "1.25 Gbps wireless Gigabit Ethernet link at 60 GHz-band," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Philadelphia, PA, Jun. 8–13, 2003, pp. 373–376.

- [3] S. E. Gunnarsson et al., "60 GHz single-chip front-end MMICs and systems for multi-Gb/s wireless communication," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1143–1157, May 2007.

- [4] B. Floyd, S. Reynolds, U. Pfeiffer, T. Beukema, J. Grzyb, and C. Haymes, "A silicon 60 GHz receiver and transmitter chipset for broadband communications," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, Feb. 2006, pp. 184–185.

- [5] B. Razavi, "A 60-GHz CMOS receiver front-end," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 17–22, Jan. 2006.

- [6] M. Toshiya et al., "A 60-GHz CMOS receiver with frequency synthesizer," in *IEEE Symp. VLSI Dig. Tech. Papers*, Kyoto, Japan, Jun. 14–16, 2007, pp. 172–173.

- [7] M. Varonen, M. Kärkkäinen, and K. A. I. Halonen, "Millimeter-Wave Amplifiers in 65-nm CMOS," in *Proc. ESSCIRC*, Munich, Germany, Sep. 10–14, 2007, pp. 280–283.

- [8] Y. P. Zhang, L. H. Guo, and M. Sun, "On-chip antennas for 60-GHz radios in silicon technology," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1664–1668, Jul. 2005.

- [9] K. T. Chan, A. Chin, Y. P. Chen, Y. D. Lin, T. S. Duh, and W. J. Lin, "Integrated antennas on Si, proton-implanted Si and Si-on-quartz," in *IEDM Tech. Dig.*, Washington, DC, Dec. 3–5, 2001, pp. 903–906.

- [10] J. G. Kim, H. S. Lee, H. Lee, J. B. Yoon, and S. Hong, "60-GHz CPW-fed post-supported patch antenna using micromachining technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 10, pp. 635–637, Oct. 2005.

- [11] H. R. Chuang, S. W. Kuo, C. C. Lin, and L. C. Kuo, "A 60-GHz millimeter-wave CMOS RFIC-on-chip dipole antenna," *Microw. J.*, vol. 50, no. 1, pp. 144–144, Jan. 2007.

- [12] C. S. Wang, J. W. Huang, S. H. Wen, S. H. Yeh, and C. K. Wang, "A CMOS RF front-end with on-chip antenna for V-band broadband wireless communications," in *Proc. ESSCIRC*, Munich, Germany, Sep. 10–14, 2007, pp. 143–146.

- [13] M. A. T. Sanduleanu and J. R. Long, "CMOS integrated transceiver for 60GHz UWB communication," in *Proc. IEEE Int. Conf. Ultra-Wide*band (ICUWB), Singapore, Sep. 24-26, 2007, pp. 508–513.

- [14] Y. P. Zhang, "Integration of microstrip antenna on ceramic ball grid array package," *Electron. Lett.*, vol. 38, no. 1, pp. 14–16, 2002.

- [15] Y. P. Zhang, "Integration of microstrip antenna on cavity-down ceramic ball grid array package," *Electron. Lett.*, vol. 38, no. 22, pp. 1307–1308, 2002.

- [16] U. Pfeiffer, J. Grzyb, D. Liu, B. Gaucher, T. Beukema, B. Floyd, and S. Reynolds, "A chip-scale packaging technology for 60-GHz wireless chipsets," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 8, pp. 3387–3397, Aug. 2006.

- [17] U. Pfeiffer, J. Grzyb, D. Liu, B. Gaucher, T. Beukema, B. Floyd, and S. Reynolds, "A 60-GHz radio chipset fully-integrated in a low-cost packaging technology," in *Proc. 56th Electron. Compon. Technol. Conf.*, San Diego, CA, Jun. 2, 2006, pp. 1343–1346.

- [18] T. Zwick, D. Liu, and B. Gaucher, "Broadband planar superstrate antenna for integrated millimeter-wave transceivers," *IEEE Trans. Antennas Propag.*, vol. 54, no. 10, pp. 270–2796, Oct. 2006.

- [19] Y. Tsutsumi et al., "A triangular loop antenna mounted adjacent to a lossy Si substrate for millimeter-wave wireless PAN," in Proc. IEEE Antenna Propag. Symp., Honolulu, HI, Jun. 10–15, 2007, pp. 1008–1011.

- [20] T. Seki, K. Nishikawa, I. Toyoda, and K. Tsunekawa, "Millimeter-wave high-efficiency multilayer parasitic microstrip antenna array for system-on-package," NTT Tech. Rev., vol. 3, no. 9, pp. 33–40, Sep. 2005

- [21] Y. C. Lee, W. Chang, and C. S. Park, "Monolithic LTCC SiP transmitter for 60 GHz wireless communication terminals," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Long Beach, CA, Jun. 12–17, 2005, pp. 1015–1018.

- [22] L. Desclos, "V-band double slot antenna integration on LTCC substrate using thick film technology," *Microw. Opt. Technol. Lett.*, vol. 28, no. 5, pp. 354–357, Mar. 2001.

- [23] C. Karnfelt, P. Hallbjorner, H. Zirath, and A. Alping, "High gain active microstrip antenna for 60-GHz WLAN/WPAN applications," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 6, pp. 2593–2603, Jun. 2006.

- [24] N. H. Hoivic et al., "High-efficiency 60 GHz antenna fabricated using low-cost silicon micromachining techniques," in Proc. IEEE Antenna Propag. Symp., Honolulu, HI, Jun. 10–15, 2007, pp. 5043–5046.

- [25] H. Uchimura, N. Shino, and K. Miyazato, "Novel circular polarized antenna array substrates for 60 GHz-band," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Long Beach, CA, Jun. 12–17, 2005, pp. 1875–1878.

- [26] J. Lee, N. Kidera, S. Pinel, J. Laskar, and M. Tentzeris, "Fully integrated passive front-end solutions for a V-band LTCC wireless system," IEEE Antenna Wireless Propag. Lett., vol. 6, pp. 285–288, 2007.

- [27] I. Kim, S. Pinel, J. Laskar, and J. G. Yook, "Circularly & linearly polarized fan beam patch antenna arrays on liquid crystal polymer substrate for V-band applications," in *Asia-Pacific Microwave Conf. Proc.*, Suzhou, Jiangsu, China, Dec. 4–7, 2005, vol. 4.

- [28] Y. P. Zhang, M. Sun, K. M. Chua, L. L. Wai, and D. L. B. Gaucher, "Antenna-in-package in LTCC for 60-GHz radio," in *Proc. IEEE Int. Workshop on Antenna Technology*, Cambridge, U.K., Mar. 21–23, 2007, pp. 279–282.

- [29] Y. P. Zhang, M. Sun, K. M. Chua, L. L. Wai, and D. Liu, "Integration of slot antenna in LTCC package for 60 GHz radios," *Electron. Lett.*, vol. 44, no. 5, pp. 330–331, 2008.

- [30] Y. P. Zhang, "Enhancement of package antenna approach with dual feeds, guard ring, and fence of vias," *IEEE Trans. Adv. Packag.*, vol. 32, no. 3, pp. 612–618, Aug. 2009.

- [31] HFSS. Ansoft, Pittsburgh, PA.

- [32] R. H. Caverly, "Characteristic impedance of integrated circuit bond-wires," *IEEE Trans. Microw. Theory Tech.*, vol. 34, no. 9, pp. 982–984, Sep. 1986.

- [33] G. Baumann et al., "51 GHz front-end with flip chip and wire bond interconnections from GaAs MMICs to a planar patch antenna," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Orlando, FL, May 16–20, 1995, pp. 1639–1642

- [34] T. Krems, W. Haydl, H. Massler, and J. Rudiger, "Millimeter-wave performance of chip interconnections using wire bonding and flip chip," in *IEEE MTT-S Int. Microwave Symp. Dig.*, San Francisco, CA, Jun. 17–21, 1996, pp. 247–250.

- [35] T. P. Budka, "Wide-bandwidth millimeter-wave bondwire interconnects," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 4, pp. 715–718, Apr. 2001.

- [36] Y. Sun, S. Glisic, F. Herzel, K. Schmalz, E. Grass, W. Winkler, and R. Kraemer, "An integrated 60 GHz transceiver front end for OFDM in SiGe: BiCMOS," presented at the Wireless World Research Forum 16, Shanghai, China, Apr. 26–28, 2006.

- [37] M. Sun and Y. P. Zhang, "A new bondwire compensation scheme for mm-wave highly-integrated wireless devices," Nanyang Technical Univ., Singapore, NTU Technical Report, 2007.

- [38] T. Blalack, Y. Leclercq, and C. P. Yue, "On-chip RF isolation techniques," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting*, 2002, pp. 205–211.

Y. P. Zhang received the B.E. and M.E. degrees from Taiyuan Polytechnic Institute and Shanxi Mining Institute of Taiyuan University of Technology, Shanxi, China, in 1982 and 1987, respectively, and the Ph.D. degree from the Chinese University of Hong Kong, Hong Kong, in 1995, all in electronic engineering.

From 1982 to 1984, he worked at Shanxi Electronic Industry Bureau, from 1990 to 1992, the University of Liverpool, Liverpool, U.K., and from 1996 to 1997, City University of Hong Kong. From 1987 to 1990, he taught at Shanxi Mining Institute

and from 1997 to 1998, the University of Hong Kong. He was promoted to a Full Professor at Taiyuan University of Technology in 1996. He is now an Associate Professor and the Deputy Supervisor of Integrated Circuits and Systems Laboratories with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore. He has broad interests in radio science and technology and published widely across seven IEEE societies. He has delivered scores of invited papers/keynote address at international scientific conferences. He has organized/chaired dozens of technical sessions of international symposia.

Dr. Zhang received the Sino-British Technical Collaboration Award in 1990 for his contribution to the advancement of subsurface radio science and technology. He received the Best Paper Award from the Second International Symposium on Communication Systems, Networks and Digital Signal Processing, 18-20 July 2000, Bournemouth, U.K., and the Best Paper Prize from the Third IEEE International Workshop on Antenna Technology, 21–23 March 2007, Cambridge, U.K. He was awarded a William Mong Visiting Fellowship from the University of Hong Kong in 2005. He is listed in Marquis Who's Who, Who's Who in Science and Engineering, Cambridge IBC 2000 Outstanding Scientists of the 21st Century. He serves on the Editorial Board of the International Journal of RF and Microwave Computer-Aided Engineering and was a Guest Editor of the Journal for the special issue RF and Microwave Subsystem Modules for Wireless Communications. He also serves as an Associate Editor of the International Journal of Microwave Science and Technology. He serves on the Editorial Boards of IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES and IEEE Microwave and Wireless Components Letters.

**M. Sun** received the B.E. and M.E. degrees from Hunan University and Beijing Institute of Technology, China, in 2000 and 2003, respectively, and the Ph.D. degree from the Nanyang Technological University (NTU), Singapore, in 2007, all in electronic engineering.

She became a Research Associate in NTU in 2006 and subsequently received a Research Fellowship in 2007. In April 2009, she joined the Institute for Infocomm Research, Singapore, as a Research Fellow. Her research interests include millimeter wave and

Terahertz antenna design.

Dr. Sun was a recipient of the Best Paper Prize from the Third IEEE International Workshop on Antenna Technology, 21–23 March 2007, Cambridge, U.K.

K. M. Chua received the Bachelor degree in science from Nanyang University, Singapore, in 1980 and the Master degree in precision engineering from Nanyang Technology University, Singapore, in 1997.

After working in the electronics industry for 12 years, he joined the Singapore Institute of Manufacturing Technology, Singapore. Currently, he is a Research Scientist in the Multi-functional Substrate Technology Group. He has over 20 years experience in R&D for electronics industry. His main interests include electronics packaging technology, Hybrid thick film manufacturing, SMT assembly, wafer bumping, LTCC development

and reliability analysis.

L. L. Wai received the B.Eng. (Hons) degree in electronics engineering from University of Manchester, Institute of Science and Technology, Manchester, U.K., in 1994.

She is a Senior Research Officer with Singapore Institute of Manufacturing Technology (SIMTech). She is working on the development of design and modeling methodologies for interconnects and embedded passives in high-speed applications.

Ms. Wai is a member of the IEEE CPMT and MTT

Duixian Liu (S'85-M'90-SM'98) received the B.S. degree in electrical engineering from XiDian University, Xi'an, China, in 1982, and the M.S. and Ph.D. degrees in electrical engineering from the Ohio State University, Columbus, in 1986 and 1990, respectively.

From 1990 to 1996, he was with Valor Enterprises Inc., Piqua, OH, initially as an Electrical Engineer and then as the Chief Engineer, during which time he designed an antenna product line ranging from 3 MHz to 2.4 GHz for the company, a very important

factor for the prestigious Presidential "E" Award for Excellence in Exporting in 1994. Since April 1996, he has been with the IBM T. J. Watson Research Center, Yorktown Heights, NY, as a Research Staff Member. He has authored or coauthored approximately 80 journal and conference papers, and edited a book titled Advanced Millimeter-Wave Technologies—Antennas, Packaging and Circuits (Wiley). He has 32 patents issued and 20 patents pending. His research interests are antenna design, chip packaging, electromagnetic modeling, digital signal processing, and communications technology.

Dr. Liu has received three IBM Outstanding Technical Achievement Awards and one Corporate Award, the IBM's highest technical award. He was named Master Inventor in 2007. He is an Associate Editor for the IEEE TRANSACTIONS ON ANTENNAS AND PROPAGATION and a Guest Editor for this Special Issue on Antennas and Propagation Aspects of 60-90 GHz Wireless Communications. He has been an organizer or chair for numerous international conference sessions or special sessions and technical program committee member. He was the general chair of the 2006 IEEE International Workshop on Antenna Technology: Small Antennas and Novel Metamaterials, White Plains, NY. He has served as an external Ph.D. examiner for several universities and external examiner for some government organizations on research grants.