Université d'Ottawa • University of Ottawa

## Fractal Engine:

An Affine Video Processor Core for Multimedia Applications

## Omid Fatemi

#### A Dissertation

Submitted to the School of Graduate Studies and Research in fulfillment of the requirements

for the Degree of

Ph.D. in Electrical and Computer Engineering

Ottawa-Carleton Institute of Electrical Engineering

Department of Electrical Engineering

School of Information Technology and Engineering

University of Ottawa

September, 1999

©Omid Fatemi

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-57040-1

بسم ا... الرحمن رحيم

## In the Name of Allah

To Mahdi (AJ),

#### Acknowledgements

All praise is due to Allah, the Lord of the Worlds, the Beneficent, the Merciful. Who is the creator, who taught with the pen and who taught man what he knew not. And my thanks to his representative in this world, the Imam of the time, Mahdi (AJ) who is the source of all favors and knowledge.

It is my pleasure to acknowledge and thank all persons who have influenced me in the course of this research. First, I express my gratitude to my supervisor Dr. Sethuraman Panchanathan for introducing me to the exciting fields of multimedia, video and image processing, parallel processing and VLSI and for his continued support and encouragement during my thesis work. I would also like to express my gratitude to my co-supervisor Dr. Sunil R. Das for his continuos support.

I would like to thank all the past and present members of the Visual Computing and Communications Laboratory, especially Mahmoud Reza Hashemi for his help and cooperation.

My special thanks are due to all the support staff members of School of Information Technology and Engineering for their help, especially Michele Roy and Lucette Lepage.

The generous financial support of Ministry of Culture and Higher Education of the Islamic Republic of Iran and NSERC that made this research possible is also gratefully acknowledged.

My beloved wife showed constant understanding and support. A mere acknowledgment by no means compensates the hardship she had to go through on the account of my research work.

Last, but not least, special thanks to my dear parents who always supported me in the wonderful world of science and encouraged me in getting over all the difficulties.

## **Fractal Engine**

## An Affine Video Processor Core for Multimedia Applications

#### **Abstract**

The recent advances in VLSI technology, high-speed processor designs, Internet/Intranet implementations, broadband networks (ATM and ISDN) and compression standards are leading to the popularity of multimedia applications. In general, multimedia computing presents challenges from the perspectives of both hardware and software. Each medium in a multimedia environment requires different processes, techniques, algorithms and hardware. Hence, it is crucial to design a generic processor architecture that meets the computing requirements of the various media types. In another word, there is a need for a bottom-up design strategy for meeting the computing needs of multimedia processing.

In this thesis, we propose the design of an affine video processor termed Fractal Engine. We have first derived the fundamental operations involved in visual processing tasks and designed the generic processing elements to map a majority of these operations. We have chosen affine transformations as the target algorithm as it is expected to be increasingly used in many visual-processing applications including latest video coding standard MPEG4. We have chosen fractal block processing (FBP) as a candidate algorithm for the

design of target video processor, since it encompasses a variety of visual processing operations including affine transforms.

Fractal Engine is capable of implementing the gamut of image/video processing algorithms. Fractal Engine is a simple, modular, and scalable architecture that is optimized to execute both low-level and mid-level operations. It is capable of implementing a variety of visual processing tasks. Fractal Engine is an open architecture and is therefore capable of adapting to the processing requirements of a variety of media processing algorithms. The individual modules of the Fractal Engine have been implemented in VHDL. A behavioral model of the circuit has been developed and fully tested by using VHDL simulators. The model is synthesized using BiCMOS .8µ ASIC library cells and Xilinx/Altera FPGAs. We have chosen to demonstrate the real-time execution capability of Fractal Engine by mapping specific visual processing algorithms such as fractal block coding (FBC), vector quantization and motion estimation onto the proposed architecture.

## **Table of Contents**

| <b>TAB</b>  | BLE OF CONTENTS                                     | 2  |

|-------------|-----------------------------------------------------|----|

|             |                                                     |    |

| <u>TAB</u>  | BLE OF FIGURES                                      | 8  |

|             |                                                     |    |

| <u>1 II</u> | NTRODUCTION                                         | 12 |

| 1.1         | MOTIVATION                                          | 14 |

| 1.2         | PROBLEM STATEMENT                                   | 17 |

| 1.3         | OUTLINE OF THE THESIS                               | 18 |

| <u>2 F</u>  | FUNDAMENTAL MULTIMEDIA OPERATIONS                   | 21 |

| 2.1         | VISUAL MEDIA BASICS                                 | 21 |

| IMAG        | GE COMPONENTS                                       | 21 |

| FRAN        | ME RATE                                             | 24 |

| INTE        | RLACED VERSUS PROGRESSIVE SCAN                      | 25 |

| FIDEI       | LITY CRITERIA OF DIGITAL IMAGES AND VIDEO SEQUENCES | 26 |

| 2.2         | DIGITAL IMAGE AND VIDEO PROCESSING CATEGORIES       | 27 |

| ENHA        | ANCEMENT:                                           | 28 |

| REST        | TORATION:                                           | 29 |

| <b>~~</b>   | IDDF00101/                                          | 20 |

| IMAG:       | E/VIDEO ANALYSIS:                           | 31 |

|-------------|---------------------------------------------|----|

| 2.3         | FUNDAMENTAL OPERATIONS IN VISUAL PROCESSING | 32 |

| POINT       | Γ OPERATIONS                                | 33 |

| Loca        | L OPERATIONS                                | 35 |

| LINE        | OPERATIONS                                  | 37 |

| GEOM        | METRIC OPERATIONS                           | 38 |

| BLOC        | K OPERATIONS                                | 39 |

| IMAG        | E OPERATIONS                                | 40 |

| 2.4         | FRACTAL PROCESSING                          | 41 |

| 2.5         | MPEG4 MULTIMEDIA STANDARD                   | 42 |

| Natu        | RAL TEXTURES, IMAGES AND VIDEO              | 47 |

| SYNT        | HETIC OBJECTS                               | 49 |

| 2.6         | SUMMARY                                     | 52 |

| <u>3 RI</u> | EVIEW OF VLSI TECHNOLOGY                    | 54 |

| 3.1         | INTEGRATION                                 | 54 |

| 3.2         | FABRICATION PROCESS                         | 56 |

| 3.2.1       | FULL CUSTOM DESIGN                          | 57 |

| 3.2.2       | GATE ARRAY AND CELL-BASED DESIGN            | 58 |

| 3.2.3       | FIELD PROGRAMMABLE GATE ARRAYS (FPGA)       | 60 |

| 3.2.4       | SELECTED DEVICE                             | 62 |

| 3.3         | DESIGN TOOLS                                | 62 |

| 3.3.1       | VHDL SYNTHESIS                              | 63 |

| 3.3.2       | IC DESIGN METHODOLOGY                       | 65 |

| 3.4         | SUMMARY                                     | 69 |

| 4 D   | ESIGN TRENDS IN MULTIMEDIA ARCHITECTURES | 71 |

|-------|------------------------------------------|----|

| 4.1   | FLEXIBILITY                              | 72 |

| 4.1.1 |                                          |    |

|       | DEDICATED ARCHITECTURES                  |    |

| 4.1.2 | ADAPTED ARCHITECTURES                    | 74 |

| 4.1.3 | PROGRAMMABLE ARCHITECTURES               | 76 |

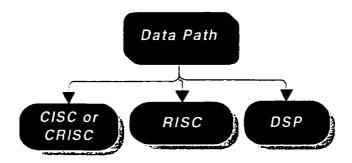

| 4.2   | PROCESSOR SELECTION                      | 78 |

| 4.2.1 | CISC/CRISC                               | 80 |

| 4.2.2 | RISC                                     | 81 |

| 4.2.3 | DSP                                      | 82 |

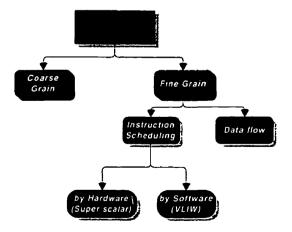

| 4.3   | GRANULARITY                              | 83 |

| 4.3.1 | INSTRUCTION SCHEDULING - SUPER SCALAR    | 84 |

| 4.3.2 | INSTRUCTION SCHEDULING - VLIW            | 84 |

| 4.3.3 | Data flow                                | 85 |

| 4.4   | DATA DISTRIBUTION                        | 85 |

| 4.4.1 | SIMD                                     | 85 |

| 4.4.2 | MIMD                                     | 86 |

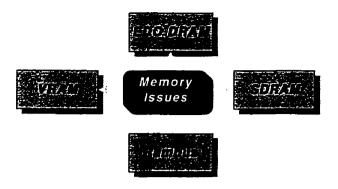

| 4.5   | MEMORY SELECTION                         | 86 |

| 4.5.1 | EDO RAM                                  | 87 |

| 4.5.2 | SDRAM                                    | 87 |

| 4.5.3 | RAMBUS DRAM (RDRAM)                      | 87 |

| 4.5.4 | VRAM                                     | 88 |

| 4.6   | MULTIMEDIA PROCESSORS                    | 88 |

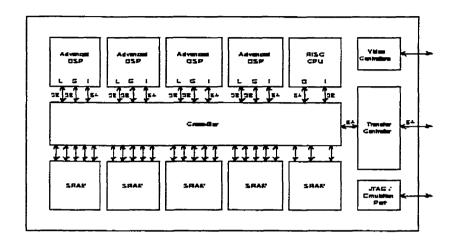

| 4.6.1 | TI MVP                                   | 90 |

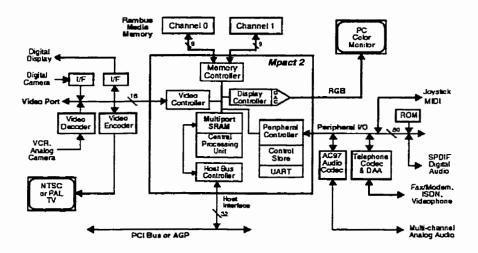

| 4.6.2 | CHROMATIC RESEARCH MPACT 2               | 92 |

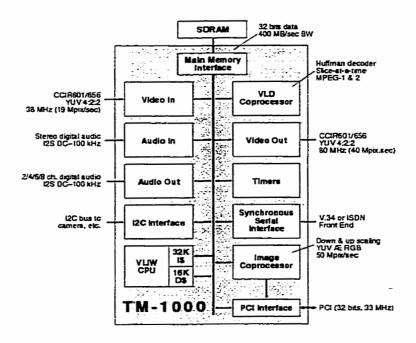

| 4.6.3                                               | PHILIPS TRIMEDIA TM-1000                                                                                                                                | 93                    |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

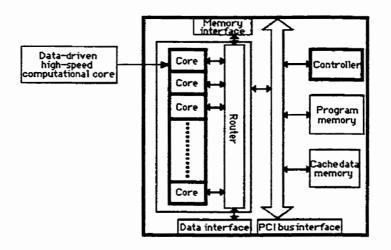

| 4.6.4                                               | V830R/AV BY NEC                                                                                                                                         | 94                    |

| 4.6.5                                               | SHARP DDMP                                                                                                                                              | 95                    |

| 4.6.6                                               | PENTIUM PROCESSOR WITH MMX TECHNOLOGY                                                                                                                   | 96                    |

| 4.6.7                                               | C-CUBE'S VIDEORISC PROCESSOR (VRP)                                                                                                                      | 97                    |

| 4.6.8                                               | L64002 MPEG AUDIO/VIDEO DECODER                                                                                                                         | 98                    |

| 4.6.9                                               | IBM VIDEO INTEGRATION PROCESSOR                                                                                                                         | 100                   |

| 4.6.10                                              | 8x8's Video Communication Processor (VCP)                                                                                                               | 101                   |

| 4.6.11                                              | ARRAY MICROSYSTEMS VIDEO COMPRESSION CHIP-SET                                                                                                           | 102                   |

| 4.7                                                 | ANALYSIS                                                                                                                                                | 103                   |

| 4.8                                                 | SUMMARY                                                                                                                                                 | 107                   |

|                                                     |                                                                                                                                                         |                       |

|                                                     |                                                                                                                                                         |                       |

| <u> 5 AF</u>                                        | FINE TRANSFORM PROCESSOR                                                                                                                                | 109                   |

|                                                     |                                                                                                                                                         |                       |

| 5 AF<br>5.1                                         | FINE TRANSFORM PROCESSOR                                                                                                                                |                       |

|                                                     |                                                                                                                                                         | 110                   |

| 5.1                                                 | AFFINE TRANSFORMS                                                                                                                                       | <b>110</b>            |

| <b>5.1</b><br>5.1.1                                 | AFFINE TRANSFORMS  TRANSLATION                                                                                                                          | 111                   |

| <b>5.1</b><br>5.1.1<br>5.1.2                        | AFFINE TRANSFORMS  TRANSLATION  SCALE                                                                                                                   | 110111112             |

| <b>5.1</b> 5.1.1 5.1.2 5.1.3                        | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR                                                                                                            | 110112112             |

| <b>5.1</b> 5.1.1 5.1.2 5.1.3 5.1.4                  | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR  TRANSPOSITION                                                                                             | 110112112113          |

| <b>5.1</b> 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5            | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR  TRANSPOSITION  ROTATION                                                                                   | 110112112113114       |

| <b>5.1</b> 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5            | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR  TRANSPOSITION  ROTATION  FUNDAMENTAL AFFINE OPERATIONS                                                    | 110112113114115       |

| <b>5.1</b> 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5 <b>5.2</b> | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR  TRANSPOSITION  ROTATION  FUNDAMENTAL AFFINE OPERATIONS  VLSI IMPLEMENTATION OF ATP                        | 110112112113114115118 |

| 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5 5.2 5.3               | AFFINE TRANSFORMS  TRANSLATION  SCALE  SHEAR  TRANSPOSITION  ROTATION  FUNDAMENTAL AFFINE OPERATIONS  VLSI IMPLEMENTATION OF ATP  ARRAY ADDER UNIT (AR) | 110112113114115118119 |

| <u>6 FI</u> | 6 FRACTAL ENGINE                           |      |

|-------------|--------------------------------------------|------|

| 6.1         | Why Fractal?                               | 123  |

| 6.2         | FRACTAL BLOCK PROCESSING                   |      |

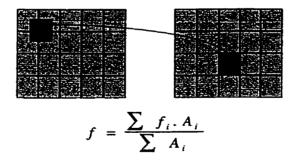

| 6.2.1       | MEAN AND VARIANCE COMPUTATION              | 127  |

| 6.3         | FRACTAL ENGINE                             | 127  |

| 6.3.1       | PROCESSING SECTION                         | 128  |

| 6.3.2       | SCALABILITY                                | 129  |

| 6.4         | EXAMPLE ALGORITHMS                         | 133  |

| 6.4.1       | VECTOR QUANTIZATION (VQ)                   | 133  |

| 6.4.2       | FRACTAL BLOCK CODING (FBC) ALGORITHM       | 135  |

| 6.4.3       | AFFINE TRANSFORM BASED VECTOR QUANTIZATION | 141  |

| 6.4.4       | MOTION ESTIMATION (ME)                     | 146  |

| 6.5         | VHDL IMPLEMENTATION AND TIMING ANALYSIS    | 150  |

| 6.5.1       | VECTOR QUANTIZATION                        | 151  |

| 6.5.2       | FRACTAL BLOCK CODING                       | 152  |

| 6.5.3       | MOTION ESTIMATION                          | 154  |

| 6.5.4       | AFFINE MOTION ESTIMATION                   | 154  |

| 6.6         | SUMMARY                                    | 154  |

|             |                                            | 4.50 |

| 7 A         | UGMENTED FRACTAL ENGINE                    | 150  |

| 7.1         | INTERPOLATION IN DIGITAL IMAGES            | 156  |

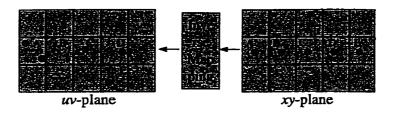

| 7.1.1       | FORWARD MAPPING                            | 157  |

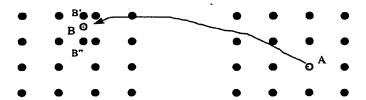

| 7.1.2       | INVERSE MAPPING                            | 159  |

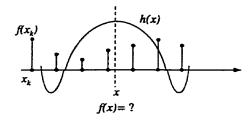

| 7.1.3       | INTERPOLATION                              | 160  |

| 7.1.4       | INTERPOLATION KERNELS                                 | 161         |

|-------------|-------------------------------------------------------|-------------|

| 7.1.5       | EXPERIMENTAL RESULTS                                  | 165         |

| 7.1.6       | INTERPOLATION FILTER IMPLEMENTATION                   | 166         |

| 7.2         | PERIPHERAL SECTION                                    | 171         |

| 7.2.1       | RANDOM ACCESS MEMORY (RAM):                           | 171         |

| 7.2.2       | CONTROL UNIT (CU):                                    | 173         |

| 7.2.3       | CPU-IF MODULE                                         | 173         |

| 7.2.4       | INTELLIGENT MEMORY INTERFACE (IMI):                   | 174         |

| 7.3         | SUMMARY                                               | 175         |

| 8 C         | ONCLUSIONS                                            | 1 <u>77</u> |

| 8.1         | THESIS CONTRIBUTIONS                                  | 178         |

| 8.1.1       | CLASSIFICATION OF VARIOUS MULTIMEDIA OPERATIONS       | 178         |

| 8.1.2       | DESIGN TRENDS IN MULTIMEDIA HARDWARE ARCHITECTURES    | 178         |

| 8.1.3       | HARDWARE / SOFTWARE CO-DESIGN FOR VLSI IMPLEMENTATION | 178         |

| 8.1.4       | AFFINE TRANSFORM PROCESSOR                            | 179         |

| 8.1.5       | FRACTAL ENGINE                                        | 179         |

| 8.2         | PUBLICATIONS                                          | 180         |

| <u>9 FU</u> | JTURE WORK                                            | 181         |

| 9.1         | MULTIMEDIA ALGORITHMS                                 | 181         |

| 9.2         | NEW AFFINE ALGORITHMS                                 | 182         |

| 10 R        | EFERENCES                                             | 184         |

# **Table of Figures**

| Figure 1 - The design approach for the Fractal Engine      | . 19         |

|------------------------------------------------------------|--------------|

| Figure 2- Image Coordinates                                | . 23         |

| Figure 3- Barbara image in 4 different sampling rates      | . 24         |

| Figure 4- Interlaced scan display.                         | . 26         |

| Figure 5- Sharpening effect                                | . 28         |

| Figure 6- Noise removal using image enhancement techniques | . 29         |

| Figure 7- Visual Media Operations                          | . 32         |

| Figure 8- Example point operations                         | . 3 <b>5</b> |

| Figure 9 - An example of an MPEG-4 Scene                   | . 44         |

| Figure 10- IC transistor counts                            | . 56         |

| Figure 11 - Evolution of IC Design Methodology             | . 66         |

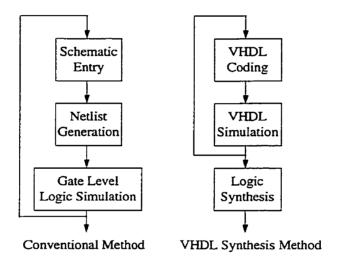

| Figure 12- Comparison of Design Flows                      | . 68         |

| Figure 13 - VLSI Design Process                            | . 69         |

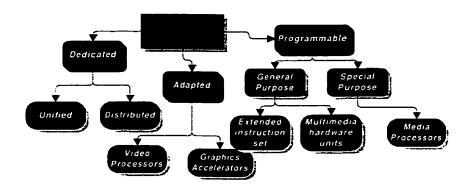

| Figure 14- Multimedia Architecture Trends                  | 72           |

| Figure 15- Distributed implementation example              | . 74         |

| Figure 16- Unified implementation example.                 | . 74         |

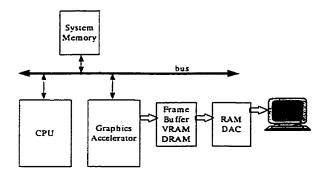

| Figure 17- A typical graphics accelerator system           | . 75         |

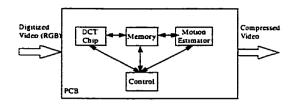

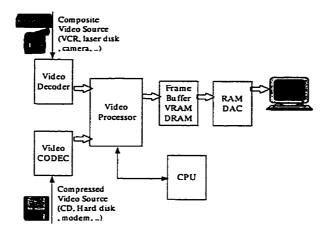

| Figure 18- Video processor implementation                  | . 76         |

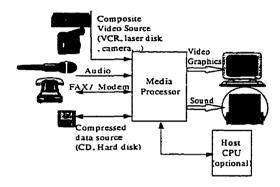

| Figure 19- Typical media processor system                  | . 78         |

| Figure 20- Data path selection                            | 79  |

|-----------------------------------------------------------|-----|

| Figure 21 - Granularity issue in multimedia architectures | 83  |

| Figure 22 - Available DRAM options                        | 87  |

| Figure 23- MVP Block Diagram                              | 91  |

| Figure 24 - Mpact 2 block diagram                         | 92  |

| Figure 25 - Block diagram of TM-1000                      | 94  |

| Figure 26 - Block Diagram of DDMP                         | 96  |

| Figure 27 - Implementation of MMX technology              | 96  |

| Figure 28- L64002 Block Diagram                           | 100 |

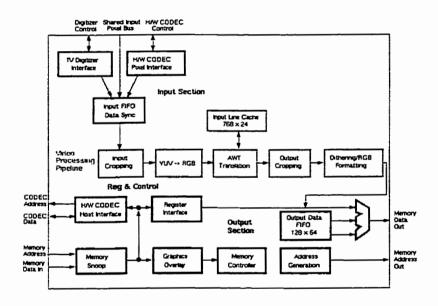

| Figure 29- VIP Block Diagram                              | 101 |

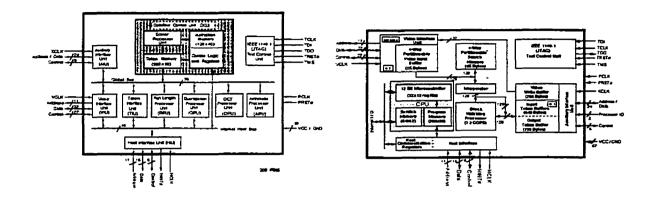

| Figure 30- ICC and MEC block diagram                      | 103 |

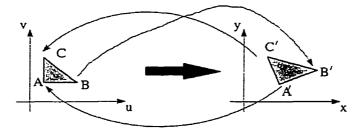

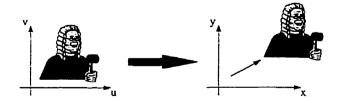

| Figure 31- Spatial Transformation.                        | 109 |

| Figure 32 - General Affine Transformation                 | 110 |

| Figure 33- Translation.                                   | 111 |

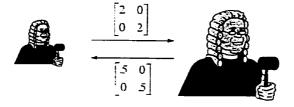

| Figure 34- Scale                                          | 112 |

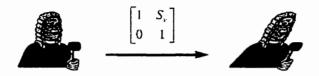

| Figure 35- Shear.                                         | 113 |

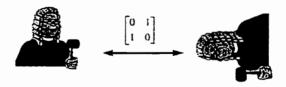

| Figure 36- Transposition.                                 | 113 |

| Figure 37- Rotation procedure.                            | 114 |

| Figure 38- Rotation.                                      | 114 |

| Figure 39 - Example of isometric transforms               | 117 |

| Figure 40- Affine Module Block Diagram                    | 118 |

| Figure 41- Accumulation and Summation Cells               | 119 |

| Figure 42- Array Adder for 4x4 blocks                     | 120 |

| Figure 43-Basic Transposer Cell                                     | 121 |

|---------------------------------------------------------------------|-----|

| Figure 44- 4x4 Transposer Module                                    | 122 |

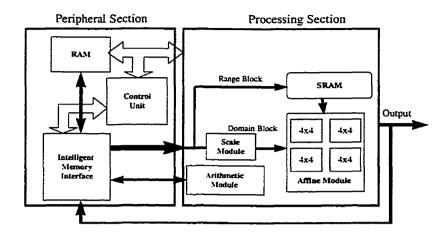

| Figure 45- Fractal Engine Block Diagram                             | 128 |

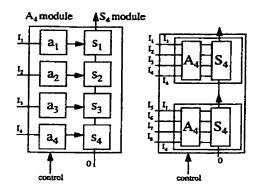

| Figure 46- 4-element and 8-element Array Adder                      | 130 |

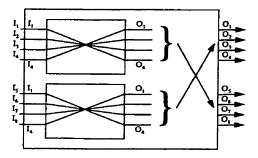

| Figure 47- Reflector Module                                         | 130 |

| Figure 48-8x8 Transposer Unit                                       | 131 |

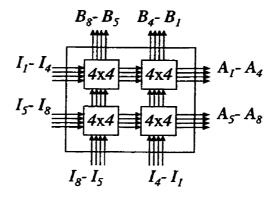

| Figure 49- Affine Module for 4x4 blocks                             | 132 |

| Figure 50- Affine module for 8x8 blocks                             | 132 |

| Figure 51- Scalable Affine Module                                   | 133 |

| Figure 52 - Data flow in Fractal Engine for VQ Implementation       | 134 |

| Figure 53 - Processing Section of Fractal Engine for VQ execution   | 135 |

| Figure 54- Data flow in Fractal Engine for FBC Implementation.      | 137 |

| Figure 55- Processing Section in 8x8 mode for Execution.            | 138 |

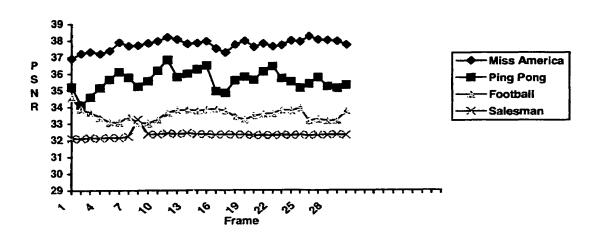

| Figure 56 - Performancce chart of ATVQ                              | 144 |

| Figure 57 - Processing Section of Fractal Engine for ATVQ execution | 145 |

| Figure 58 - Data flow diagram of Fractal Engine for ATVQ            | 145 |

| Figure 59 – Data flow diagram of Fractal Engine in ME process       | 148 |

| Figure 60 - Data flow diagram of Fractal Engine in AME execution    | 149 |

| Figure 61- Forward mapping                                          | 157 |

| Figure 62- Four corner mapping                                      | 158 |

| Figure 63- Area mapping                                             | 159 |

| Figure 64- Inverse mapping                                          | 160 |

| Figure 65- 1-D Interpolation.                                       | 161 |

| Figure 66- Nearest Neighbor Interpolation.           | 162 |

|------------------------------------------------------|-----|

| Figure 67- Linear interpolation.                     | 163 |

| Figure 68- 2D Area Based Interpolation.              | 164 |

| Figure 69 - Basic accumulator cell                   | 167 |

| Figure 70 - 12 bit, 3 level-pipelined accumulator    | 168 |

| Figure 71 - Scalable accumulator                     | 169 |

| Figure 72 - Block diagram of an 8-bit multiplier     | 170 |

| Figure 73 - A multiplication example                 | 171 |

| Figure 74 - Burst transfer example for a 66MHz clock | 175 |

## 1 Introduction

The recent advances in VLSI technology[1]-[2], high-speed processor designs[3], Internet/Intranet implementations[4], broadband networks[5] (ATM and ISDN) and compression standards [6] (JPEG [7], MPEG [8], H.261, H.263 and G.273) are leading to the popularity of multimedia applications. Example applications include Multimedia Information Systems [9], Digital Libraries [10], Remote Sensing and Natural Resources Management [11] and Geographic Information System [12].

A variety of media processing techniques are typically used in multimedia processing environments to capture, store, manipulate and transmit multimedia objects such as text, handwritten data, audio objects, still images, 2D/3D graphics, animation and full-motion video. Example techniques include speech analysis and synthesis, character recognition, audio compression, graphics animation, 3D rendering, image enhancement and restoration, image/video analysis and editing, and video transmission.

Visual media in a multimedia system contains a significant amount of information, and correspondingly involves a large volume of data in contrast to the other media types. Uncompressed digital video requires 250 Mb/s to support studio quality transmission of NTSC images (480 lines x 720 pixels/line x 24 bits/pixel x 30 frames/s)[13]. Even a simpler application such as video telephony (240 lines x 360 pixel/line x 16 bits/pixel x 10) requires 14 Mb/s to transmit the digital video signal in raw format. The bandwidth and storage requirements of visual information typically make it difficult to manage the data in its raw form. However, there is considerable redundancy in video data, both from

an information theoretic viewpoint as well as from the perspectives of structural content and human perception. A number of image and video compression standards, e.g., MPEG-1[14], MPEG-2[15], MPEG-4[16],[17], H.261[18], and H.263[19] have been recently proposed to compress the visual data for a variety of transmission and/or storage applications. There is ongoing research and standardization efforts targeted towards future multimedia applications with the objective of integrating compression and content access functionality, including MPEG-7[20]. These techniques and standards will involve execution of complex video processing tasks in real-time. The challenges can range from waveform coding implementations to scene modeling and understanding. For example, the principal objective of model-based image coding [21], [22] or intelligent image coding is to understand the scene by modeling the objects in order to achieve a higher level representation. In addition, there is an increasing interest in 3-D image and video processing[23], [24]. An important processing task in most of these situations is affine transformation[25], which includes operations such as rotation, transposition, scaling and translation. For example, intelligent motion estimation in a video sequence requires extraction of the motion of objects and camera operations, which could be represented using affine parameters.

In general, multimedia computing presents challenges from the perspectives of both hardware and software. Each media in a multimedia environment requires different processes, techniques, algorithms and hardware. Hence, it is crucial to design a generic processor architecture that meets the computing requirements of the various media types. The complexity, variety of techniques and tools, and the high computation, storage and

I/O bandwidths associated with visual processing pose several challenges, particularly from the viewpoint of real-time implementation.

Real-time implementation goal is the principal reason for the slant of most media processor development[26] towards visual processing. Several processing solutions ranging from multimedia extensions to general purpose processors such as the Intel MMX[27], programmable DSP architectures such as the TI-MVP [28], Media processors like the Philips TriMedia processor[29], and special purpose architectures such as the C-Cube MPEG decoder chip-sets[30] have been proposed to implement a variety of multimedia (particularly visual) processing operations. A detailed categorization of available multimedia processing strategies is required in order to propose the optimum architecture for target applications. In this thesis, we have designed a high performance visual signal processor (VSP) called Fractal Engine, which is optimized to execute a variety of both mid-level and low-level visual operations.

#### 1.1 Motivation

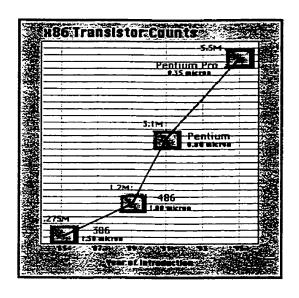

The implementation of video processing algorithms or in general multimedia algorithms demands systems of large computational capability with efficient VLSI implementation of the various media processing algorithms. Real time video compression requires processing power in the range of 100 MOPS to 100000 MOPS. The envisaged mass application of digital multimedia demands fast and reduced size implementations, which are potentially feasible due to recent advances in VLSI technology[31] specifically in the areas of high density, and fast circuit implementations. VLSI technologies have now advanced to the point where, for some applications, the processing power and memory

required to perform these tasks can be incorporated into a few silicon chips. Individual transistors switch faster and therefore circuits perform operations at a higher speed. The transistors occupy less space and therefore more complicated design can be integrated into a single chip. It is required to study various options in VLSI design and select the best environment for target applications.

The advent of hardware description languages such as VHDL (VHSIC Hardware Description Language)[32] and re-configurable high density FPGAs[33] (Field Programmable Gate Array) such as Altera[34] and Xilinx[35] have not only facilitated rapid prototyping of digital designs, but also serve the needs for programmable and reconfigurable hardware design. Thus it makes possible quick assembly of pre-designed generic processing elements into architectures that can be dedicated to execute specific algorithms or a class of algorithms under the assumption that the generic processing elements were designed to accommodate a variety of media processing requirements. A specific configuration can also be chosen from a universal architecture using external control signals assuming that the target processor is capable of organizing the generic processing elements into various configurations. Hence, enabling VLSI technology should be thoroughly studied and the best possible combinations of HDLs, ASICs (Application Specific Integrated Circuits) and FPGAs have to be selected.

The main focus of the researchers for video processor design is the optimization of lowlevel operations such as multiplication and accumulation. However, these developments are not sufficient to overcome all the problems in implementing multimedia applications. There is clearly a need for a bottom-up design strategy for meeting the computing needs

of multimedia processing. We need to derive the basic operations involved in a variety of image and video processing operations such as enhancement, restoration, compression and analysis of images and video sequences. It is required to derive mid-level and highlevel operations in visual domain and design scalable and modular architectures for these requirements. Since Fractal Block Processing (FBP)[36] encompasses a majority of image processing operations[37],[38], including summation/accumulation, image addition / subtraction, translation, stretching, shifting, scaling, rotation and pattern matching, we have chosen this as the candidate algorithm for the design of the generic video processing element. We note that the operations of translation, stretching, shifting, scaling and rotation termed as affine transforms[39] are particularly important and are extremely powerful in visual processing tasks such as image analysis and understanding motion in video. It is our belief that most of the complex processing operations involved in the next generation of visual processing tasks will involve some form of affine transformation. We note that there is hardly any architectural solutions that emphasize affine transform implementation in the context of general purpose video processing. The choice of Fractal block processing as the candidate algorithm in our generic processing element design is therefore based on the following two premises: (i) it contains a reasonable super-set of the variety of processing tasks (including affine transformations) typically found in visual (and multimedia) processing, and (ii) it is a computationally intensive procedure and hence presents challenges from the perspective of real-time implementation. Another important requirement in the design of multimedia processor architectures is scalability. For example, visual processing tasks typically operate on a variety of image sizes, resolutions, and frame rates, and it is therefore crucial to design

the generic processing element to be scalable. For a problem of complexity X which is executed using N units in T seconds, scalability implies the following: (i) T/M seconds will be required to solve the problem using NM units, and/or (ii) A problem of complexity XM is solved in T seconds using NM units. The first type of scalability requires a flexible control design while the second type of scalability requires that the feature of scalability be incorporated in the design of individual modules.

An important factor in designing a high performance video processor is to adopt the promising features in existing architectures. This necessitates full investigation of a variety of existing processors ranging from general purpose processors to dedicated hardware modules used in multimedia applications.

#### 1.2 Problem Statement

In this thesis, we propose the design of generic processing elements based on the derivation of the fundamental visual processing operations in Fractal block processing. An Affine Transform Processor (ATP), which is the core processor, and further a visual signal processor based on ATP core are designed. The processor termed Fractal Engine is capable of implementing the gamut of image/video processing algorithms. Fractal Engine is a simple, modular, and scalable architecture that is optimized to execute both low-level and mid-level operations. It is capable of implementing a variety of visual processing tasks, including spatial filtering, contrast enhancement, frequency domain operations, histogram calculation, geometric transforms, indexing, vector quantization, fractal block coding, shot boundary detection, motion estimation, and camera operation detection.

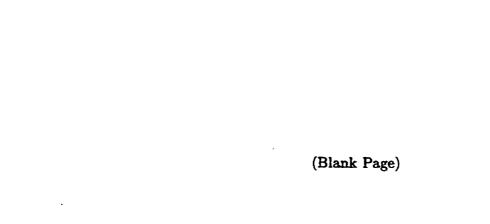

Fractal Engine is an open architecture and is therefore capable of adapting to the processing requirements of a variety of media processing algorithms. The individual modules of the Fractal Engine have been implemented in VHDL. A behavioral model of the circuit has been developed and fully tested by using VHDL simulators. The model is synthesized using BiCMOS .8µ ASIC library cells[40] and Xilinx/Altera FPGAs. We have chosen to demonstrate the real-time execution capability of Fractal Engine by mapping specific visual processing algorithms such as fractal block coding (FBC)[41], vector quantization[42] and motion estimation[43] onto the proposed architecture. The steps adopted in the design of the Fractal Engine are presented in Figure 1.

#### 1.3 Outline of the Thesis

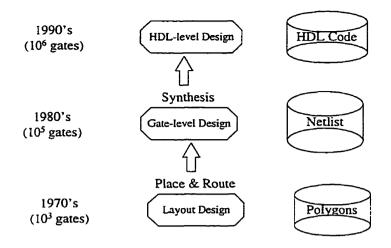

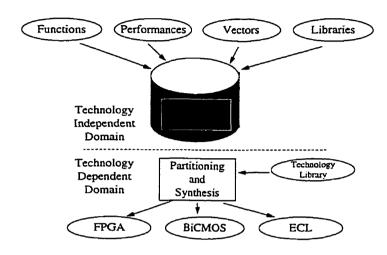

The thesis is organized as follows. Chapter 2 presents the fundamental operations in visual media processing. All of the visual algorithms are classified to four major categories and six different classes. The basic operations of all groups are then introduced. We propose that a general affine transformation is a mid-level fundamental operation which involves low-level operations in image/video processing algorithms. MPEG4 is used as an example to demonstrate the validity of our categorization. In chapter 3, different aspects of enabling VLSI technology are reviewed. The different options for VLSI implementation of video signal processors are then discussed. Hardware description languages, logic synthesizers, and behavior compilers for multimedia purposes are then explained and the necessary tools in our design methodology are introduced. The design trends in multimedia processor architectures are detailed in chapter 4.

Figure 1 - The design approach for the Fractal Engine

It is concluded that dedicated modules are suitable for critical units while programmable modules are required to facilitate the adaptation of the architecture for various algorithms.

The individual modules of the proposed ATP core are presented in chapter 5, where basic

operations in affine transformation are introduced and an optimal scalable architecture is proposed. The detailed design of the Fractal Engine which is optimized. for executing fractal block processing algorithm is presented in chapter 6. The mapping of example algorithms onto the Fractal Engine and area/timing analysis are also discussed in this chapter. Since Fractal Engine is an open architecture, we have demonstrated the implementation of new algorithms such as generalized affine transform operations and interpolation filter in chapter 7. The design is based on the augmentation in terms of flexibility and programmability in Fractal Engine. Finally, conclusions and directions for future work are presented in Chapter 8 followed by the references.

## 2 Fundamental Multimedia Operations

We note that a critical analysis of image and video tasks will result in the derivation of the set of generic operations, which are typically employed in a variety of multimedia applications. In this chapter, we first present the fundamentals of visual media processing. We then summarize the various categories of operations in image and video processing followed by the derivation of the generic operations for visual processing and a brief introduction to affine transforms and fractal processing. The last section introduces MPEG4, the new standard for multimedia applications. The principal objective is to demonstrate that the candidate algorithm chosen for the design of the target architecture encompasses a majority of the visual operations as well as presents challenges from the perspective of real-time implementation.

#### 2.1 Visual Media Basics

Video sequences are essentially a collection of individual frames (images). Hence, the main part of this section deals with the definitions for digital images.

#### **Image Components**

A digital image is composed of discrete points with a quantized value assigned to each point. In the case of gray-scale images this value represents the gray level of the point. However, for color images, the quantized value represents the color component values of the point.

A digital image is created from a continuos-tone image after the two steps of sampling and quantization[44]. In the sampling process, the brightness values of particular positions are sampled. In the quantization process, the sampled value is quantized to a fixed length integer value which is usually 8-bits for gray-scale images and 24-bits for color images. The 24-bit quantization known as true color representation consists of 3 independent 8-bit integer values describing the intensity of basic colors red, green and blue. This representation is known as RGB format. In the case of gray scale images, this value describes only the intensity value corresponding to the brightness of the point. A quantized sample representing the brightness value for a specific position in the image is called a *pixel* or a picture element. The combination of sampling and quantization processes is referred to as *image digitization*.

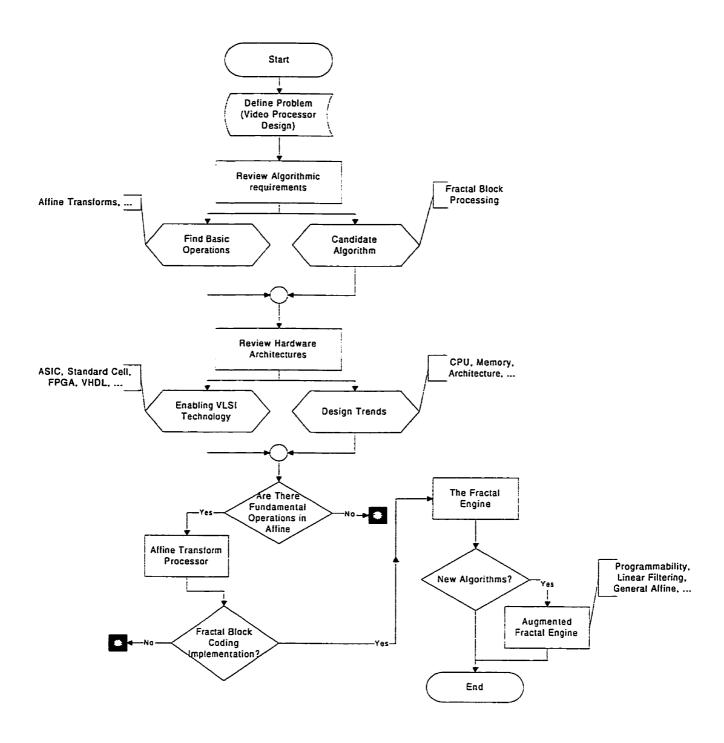

An image is generally sampled into a rectangular array of pixels. Each pixel has an (x,y) coordinate which describes its location in the image. The x-axis is the horizontal axis from left to right while the y-axis is the vertical axis from top to bottom as shown in Figure 2. The origin or location (0,0) is in the upper left corner of the image in this representation. As an example, the pixel at location (50, 120) is marked in the Figure 2.

The number of columns or rows in an image (M and N respectively for an MxN image) indicates the *spatial resolution* of the image which is directly related to the quality of the image. Spatial resolution describes how many pixels are in the image. The more pixels in the image, the better its quality and the larger its storage size. The number of pixels in a digital image depends on how finely the image is sampled, or divided into discrete pixels.

Figure 2- Image Coordinates

It is the sampling rate, which determines the number of pixels for a known physical size. For example, 200 dpi (dot per inch) means that there are 200 pixels in an inch. The maximum sampling rate is set by the digitizing device such as scanner, digital camera, etc. From sampling theorem, the necessary sampling rate so that the digital image adequately resolves all spatial details of the original continuous-tone image, is at least twice as fast as the highest spatial frequency contained in the image (Nyquist rate).

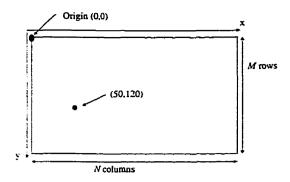

If sampling occurs at a lower rate than that required by the sampling theorem, the higher spatial frequency details will be lost in the digital image. Hence, the digital image will appear to be not as sharp as the original image. In Figure 3, four different sampling rates are employed to generate the illustrated digital pictures. It is clear that the picture (D) doesn't contain all the details of the picture (A) and the details of the picture are lost due to pixel blocking effect.

On the other hand, if sampling occurs at a higher rate than Nyquist rate, extra pixels will be created which theoretically do not contribute to improving image quality. However, they can be used in future manipulations such as image resampling/interpolation and feature extraction.

Figure 3- Barbara image in 4 different sampling rates.

#### Frame Rate

This parameter which is employed in video sequences determines the temporal resolution while the sampling rate determines the spatial resolution. The higher the frame rate, the more accurate is the motion representation in a digitized video sequence.

Frame rate is a sampling terminology, which is applied to digital and other non-digital forms of sequential image acquisition and display such as broadcast television. It is often expressed as the number of frames per second (fps). For example, if the frame rate of a system is 30 frames per second, an image frame is acquired (or displayed) every 1/30<sup>th</sup> of a second. If an object being imaged moves across the image frame at a faster rate, it may never be captured in an individual image. Once again, we note that it is essential that the frame rate is at least twice as fast as the highest frequency of motion in the video sequence.

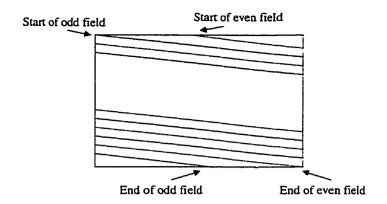

#### Interlaced Versus Progressive Scan

The concept of frame rate for image display relates how often an image is updated on the viewing display. Since the normal display mechanism is a video display monitor, images must be repeatedly refreshed. The rate at which images are refreshed can cause display flicker, and therefore human eye fatigue. Display flicker also depends on how the image is scanned on the display monitor. Common broadcast television equipment uses a technique known as *interlaced* scan[45] display, as shown in Figure 4. This means that the odd-numbered lines of the image are displayed first, followed by the even-numbered lines. The effect is to interleave, in time, the two interlaced halves of the image, one after another. Interlacing gives the impression to the observer that a new frame is present twice as often as it really is. This technique was used originally for television broadcast signals since the display could be refreshed less frequently without noticeable image flickering (although some minor line-to-line flicker does occur at certain instances). Systems using a standard commercial broadcast television display monitor for image display typically have a 30 frame per second frame rate and interlaced scan.

In motion image sequences, interlaced scan displays can show noticeable motion defects because the odd and even halves of each image are separated in time by one-half the frame rate. The result is a tearing effect that appears on objects with fast motion through the image frame.

Figure 4- Interlaced scan display.

In the non-interlaced method known as *progressive* method[46], the entire image is displayed in one pass. In this case, the frame rate must be twice that of an equivalent interlaced display, or image flickering will be noticeable. Progressive scan eliminates line-to-line flicker and motion artifacts in displayed images. Systems using a progressive scan display monitor for image display typically have a 72 frame per second frame rate.

#### Fidelity Criteria of Digital Images and Video Sequences

Fidelity criteria are applied to measure image quality and for comparing the performance of different processing techniques. There are two types of criteria[38] that are used for evaluation of image quality, subjective and quantitative. The subjective criteria use human feeling about an image (or video sequence). Quantitative measures, try to describe or compare the image/video quality by an analytic formula.

Mean square criterion is often used in image processing. It refers to the average (or sum) of squares of the error between two images (u and u') and it could be described in three different formats as follow:

Average least square:

$$\sigma_{ls}^2 = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} |u(m,n) - u'(m,n)|^2$$

Mean square error:

$$\sigma_{ms}^2 = \frac{1}{MN} E[|u(m,n) - u'(m,n)|^2]$$

Average mean square:

$$\sigma_a^2 = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} E[|u(m,n) - u'(m,n)|^2]$$

where the size of the image is MxN and E[] represents the mathematical expectation. In many applications the mean square error is expressed in terms of a signal-to-noise ratio (SNR), which is defined in decibels (dB) as follows:

$$SNR = 10 \log_{10} \sigma^2 / \sigma_e^2 \qquad \sigma_e = \sigma_a, \sigma_{ms}, \sigma_{ls}$$

where  $\sigma^2$  is the variance of the original image.

The alternative formula for SNR, called peak-to-peak SNR (PSNR) is defined as:

$$PSNR = 10 \log_{10} \frac{(\text{peak - to - peak value of the reference image})^2}{\sigma_e^2} \qquad \sigma_e = \sigma_a, \sigma_{ms}, \sigma_{ls}$$

### 2.2 Digital Image and Video Processing Categories

Visual media processing involves operations to enhance, restore, compress and analyze images and video sequences. Whatever the operation, a similar set of steps are followed: A digital technique is applied to a digital image or video to form a digital result, such as a processed image/video, a compressed bit-stream or a list of extracted features. The four main categories of image/video processing tasks are now presented.

#### **Enhancement:**

The quality enhancement is the primary goal in digital signal processing systems. Many enhancement techniques are introduced to compensate for the effects of a specific (known or estimated) degradation process for 2-D signals known as images. This approach, known as image restoration, will be discussed in the next section. In image enhancement methods, little or no attempt is made to estimate the actual degradation process that has occurred on the picture. These include methods of modifying the intensity value, contrast enhancement, edge enhancement, deblurring, and smoothing or removing noise. These methods assume that certain general properties of the picture are degraded and attempt to resolve these problems. For example, increasing the contrast is a reasonable enhancement operation due to the attenuation of the picture, or deblurring is reasonable as shown in Figure 5 because degradation usually blurs and smoothing is justifiable, since noise is generally added to the original picture as shown in Figure 6.

Figure 5- Sharpening effect

Figure 6- Noise removal using image enhancement techniques.

Image enhancement employs local correlation between adjacent pixels to enhance the image quality.

#### **Restoration:**

Picture restoration is applied on images that have been degraded in the presence of one or more sources of corruption. There are different kinds of degradations based on the affected area. *Point degradations* only alter the intensity value or the color of individual pixels while *spatial degradations* blur an area of the image. Other types generate *temporal degradation* in video sequences. For example, the pictures obtained in remote sensing and astronomy are degraded by atmospheric turbulence, aberrations of the optical system and relative motion between the camera and the object. In image restoration, it is assumed that the degraded image is a convolved version of the original image by the degradation function plus additive noise. The goal is to obtain as good an estimate as possible of the original picture. Obviously, any such estimation procedure requires some form of knowledge concerning the degradation function. As a result, frequency domain correlation is used to restore visual information. Examples include inverse filtering, pseudo inverse filtering, etc.

### **Compression:**

The aim of digital data compression is to represent the data by as few bits as possible for the purpose of transmission or storage. The bandwidth and storage requirements of visual data typically make it impossible to handle visual (digital) data in its raw form and hence, a number of compression techniques have been developed.

Visual data compression methods fall into two common categories. In the first kind, called *lossless* compression, the data could be restored completely after the compression process. In this method, the redundancy of the image is exploited using source-coding techniques[101] such as Huffman coding and arithmetic coding. In the second category, called *lossy* techniques, higher compression rate is achieved at the expense of loosing some insignificant information in the decoding stage. This compression technique results in some distortion. Efficient compression techniques tend to minimize the distortion perceived by human visual system.

Different image and video compression techniques[74] remove the existing redundancy in different domains and hence, can be classified as follows:

### Spatial based

In this class of compression techniques, the existing correlation within an image such as predictability, randomness and smoothness is exploited. ADPCM (adaptive differential pulse code modulation), vector quantization and fractal block coding techniques are typical examples of this category.

#### Temporal based

In this category, the existing correlation within a video sequence and between the consecutive frames of the same shot is exploited and the redundancy is removed. Motion estimation[95],[99] is the basic operation for these techniques.

## Frequency based or transform coding

In transform coding techniques, a block of data is transformed so that a large fraction of its total energy is condensed into a small part of the transformed data which are quantized independently. DCT (discrete cosine transform)[75] and DWT (discrete wavelet transform)[94],[97] are typical digital transforms employed in this technique.

We note that the objective in all categories is to exploit the spatio-temporal correlation in an image or video to reduce the redundancy and represent the data in a compressed form.

#### Image/Video Analysis:

Semantic correlation of the pixels is used for image and video understanding. Recently, there is a tendency to represent multimedia objects using general object based representations which provides content-based functionalities. The objective of model-based image representation[21] or intelligent image understanding is to understand the scene by modeling the objects, yielding a higher level representation. Applications of model based image representation and image analysis include, automatic vehicle driving, medical inspection, mobile robot navigation, mail sorting, label reading, global model construction and low-bandwidth image coding. Semantic correlation of the pixels is used for image and video understanding. Example operations involved in image and video

analysis include, image segmentation, feature extraction, object classification, indexing, scene cut detection, etc.

It can be deduced from the summary of the different categories of operations listed above that the principal task is to exploit the different forms of correlations present in the visual data. The individual operations encountered in visual processing are detailed in the following section.

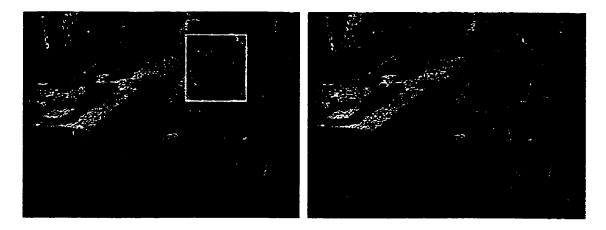

## 2.3 Fundamental Operations in Visual Processing

The fundamental operations in the four major categories of visual processing tasks are listed below. The objective is to select the candidate algorithm, which will be employed in the design of a high performance video processor. The selected kernel algorithm needs to be represented by a majority of such operations. We now propose the categorization of all individual operations in six classes as shown in Figure 7. The individual operations of each class are detailed.

Figure 7- Visual Media Operations

Ahmad

**Point operations**

The resulting gray level at a pixel depends only on the input gray level of one point

(usually the gray level of the same point before applying the operation). Such operations

are used for gray scale manipulation and for segmentation by pixel classification. The

extension of these operations include dual image operations where the output level of a

pixel depends only on the set of input levels from the pixels at the same position. For

example, we may want to take the difference between two pictures. The operations in this

category are:

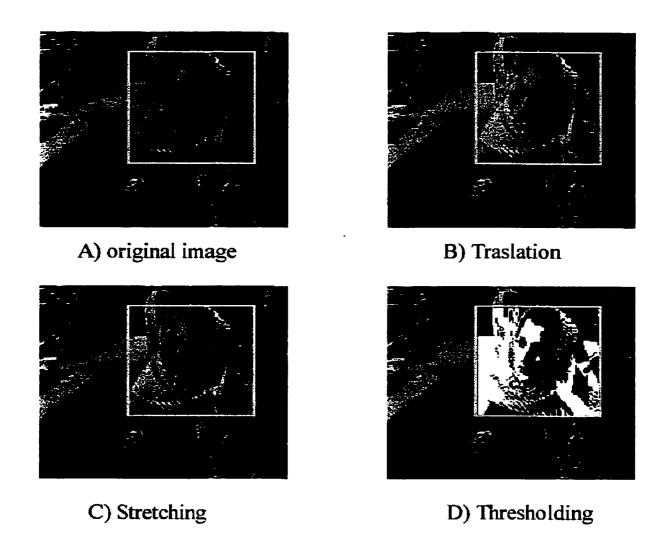

**Translation**

Description: Each image pixel is added to a constant translation factor.

$O(x,y) = I(x,y) + t_f$

Where O(x,y) is the output image, I(x,y) is the input image and  $t_f$  is the translation factor.

Applications: Brightening or darkening the image (an example is shown in Figure 8-B).

Category: Single-image.

Stretching

Description: Each image pixel is multiplied by a constant stretch factor  $(s_f)$ .

$O(x,y) = I(x,y) * s_f$

Applications: Increasing or decreasing the contrast of the image (an example is shown in

Figure 8-C).

Category: Single-image.

**Thresholding**

Description: Each image pixel is evaluated to be above or below a predetermined

threshold value  $(t_v)$ . If the pixel brightness is less than the threshold, the resulting pixel

brightness is set to 0, otherwise it is set to the maximum value (e.g. 255 for 8 bit values).

O(x,y) = 0 if  $I(x,y) < t_v$

O(x,y) = 255 if  $I(x,y) \ge t_v$

Applications: Creating a very high contrast image, segmenting the image by highlighting

an object of interest and separating it from its background (an example is shown in Figure

8-D).

Category: Single-image.

Image Subtraction / Addition

Description: One image is subtracted from or added on a pixel by pixel basis to a second

image.

$O(x,y) = I_1(x,y) \pm I_2(x,y)$

Applications: Removing common background image information, determining object

motion, Averaging over images of the same scene to reduce random noise, merging two

images.

Category: Dual-image.

Figure 8- Example point operations

### Local operations

The output of these operations depends only on the gray values in a neighborhood of a particular pixel. Such operations are used for noise cleaning, edge and local feature detection, etc. The following operations belong to this category:

## Image Masking

Description: A finite impulse response (FIR) filter or mask is applied to the image to perform a spatial image processing operation.

O = m \* I

where \* indicates masking operation.

Applications: Low-pass filtering, unsharp masking, high-pass filtering, edge enhancement

and line detection.

Category: dual-image.

Median Filtering

Description: The filter is a ranking filter, where for example the fifth-ranked pixel

brightness value is selected as the output pixel brightness from a 3x3 input group of

pixels.

O(x,y) = f(I)

where f is the nonlinear ranking and selecting function and I is the input group of pixels.

Applications: Removing impulse noise spikes from an image.

Category: single-image.

Morphological operations such as erosion and dilation

Description: The erosion operation reduces the size of bright objects on a dark

background in an image and the dilation operation increases the size of bright objects on a

dark background in an image (morphological process).

Applications: Image analysis, outlining, thinning, skeletonization and edge detection.

Category: single-image.

Line operations

The inputs to these operations are pixel values which reside across a vertical or horizontal

line. Such operations are typically used in raster scan images. A typical example

operation is the grouping of one's and zero's in a line for run-length coding. Example

operations in this category include:

Run Length Coding

Description: Across each line of an image, pixel values are sequentially compared and

grouped together into runs of identical brightness.

Applications: image compression.

Category: Single image.

Differential Pulse-Code Modulation (DPCM) Coding

Description: Each pixel value is replaced by the difference value of it and its neighbor

and then represented by a lower-resolution value.

Applications: Lossy image compression.

Category: single-image.

Line segmentation

Description: Each line in an image is scanned and the white intervals are recognized to

segment each line from the image.

Application: Text recognition.

Category: single-image.

Geometric operations

These operations are performed on a set of pixels defined by a geometrical transformation

or around a neighborhood of a specified point. This class includes the following

operations:

Up and Down Sampling

Description: Portion of image is resampled for another spatial resolution.

Applications: Image enhancement, zooming in and out, and image size adjustment.

Category: single-image.

Shifting

Description: The spatial location of image pixels is shifted linearly.

$I(x,y) \rightarrow O(x',y')$  where  $x'=x+T_x$  and  $y'=y+T_y$

Applications: Geometric adjustment of the location of an image.

Category: single-image.

Scaling

Description: The spatial size of image pixels is expanded or reduced linearly.

$I(x,y) \rightarrow O(x',y')$  where  $x'=x.S_x$  and  $y'=y.S_y$

Applications: Geometric adjustment of the size of an image.

Category: single-image.

Rotation

Description: The image is rotated linearly about the origin.

$I(x,y) \rightarrow O(x',y')$  where  $x'=x.cos(\theta)+y.sin(\theta)$  and  $y'=-x.sin(\theta)+y.cos(\theta)$

Applications: Geometric adjustment of an image.

Category: single-image.

**Block operations**

A rectangular block of pixels with a typical size of 4x4, 8x8 or 16x16 are grouped

together and processed. These operations may result in another block, a single value or a

vector of data. Example operations are:

Fourier Transform

Description: An image is transformed to frequency domain by a discrete Fourier

transform operation.

$O(u,v) = \mathcal{F}(I(x,y))$

where 7 is the Fourier transform.

Applications: Frequency filtering, removing periodic noise patterns and energy

compacting.

Category: single-image.

Discrete Cosine Transform (DCT) Coding

Description: Pixel blocks (8x8 pixels) are discrete cosine transformed and then the

frequency components are quantized.

$O(u,v) = \mathcal{D}(I(x,y))$

where  $\mathcal{D}$  is the discrete cosine transform.

Applications: Lossy image compression.

Category: single-image.

Pattern Matching

Description: A block of image is compared to a set of blocks in terms of Euclidean

distance to determine the best match between the blocks.

Applications: Documentation analysis, object recognition, vector quantization, motion

estimation and fractal image compression.

Category: dual-image.

**Image operations**

The input for these operations consists of the intensity value of all the pixels (or the main

part) of an image. Typical examples of these operations include:

Image Covariance and Correlation

Description: Image is modeled by random field representation.

$Cov(u(m, n), u(m', n')) = E[(u(m, n) - \mu(m, n))(u(m', n') - \mu(m', n'))], \mu(m, n) = E[u(m, n)]$

Applications: Image modeling and template matching.

Category: single-image.

Histogram calculation

Description: The relative frequency of each gray level in the image is calculated. The

graph of the frequency as a function of gray levels is called the histogram of image.

$p_f(z) = number of pixels with gray level equal to z.$

Applications: Image segmentation, measurement of textual properties and image

comparison.

Category: single-image.

Huffman Coding

Description: Pixel values are replaced with variable-length codes based on their

frequencies of occurrence in the image.

Applications: image compression.

Category: single image.

Mean square error / SNR computation.

Description: An image is compared to a reference image with these quantitative criteria.

$MSE = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} |u(m,n) - u'(m,n)|^2$ ,  $SNR = 10 \log_{10} \sigma^2 / MSE$

Applications: image comparison.

Category: Dual image.

2.4 Fractal Processing

The principal task in all of four different categories of image operations is to exploit the

high correlation present in the visual data. Two new mathematical entities, namely

Fractals[41] and Wavelet Transforms[96], have been recently introduced to exploit the

correlation and self-similarities within an image or a sequence of images. Wavelet

transformation belongs to the category of transform coding techniques, which attempt to

exploit the correlation in an alternate domain rather than spatial domain. On the other

hand, Fractal processing extracts existing self-similarity and self-affine content within the image.

A majority of the processing operations listed above is accommodated in Fractal Block Processing (FBP)[38]. FBP is a computationally intensive procedure and involves operations such as, summation/accumulation, image addition/subtraction, translation, stretching, shifting, scaling, rotation and pattern matching. We have therefore chosen FBP as the candidate algorithm for the design of the generic video processing element which is detailed in chapter 6 of this thesis. The basic operations in FBP which are affine transformations are discussed in chapter 5.

## 2.5 MPEG4 Multimedia Standard

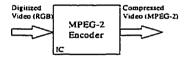

An emerging standard that is expected to become popular in visual domain processing (as well as other domains such as Audio) is MPEG4[16], [17]. MPEG4 is the third standard in a series developed by the Motion Picture Expert Group. The first two standards MPEG1[8], [14] and MPEG2[15] address the coding and compression of frame based video sequences and audio. MPEG1 was primarily used for Video-CD's with a resolution of 352x240. MPEG2 operated on a higher resolution (704x480) and has added support for interlaced video. Later, higher levels of resolution were specified so that MPEG2 could support HDTV. MPEG2 now supports all resolutions and frame rates defined by ATSC for digital television. MPEG4 was finalized in October 1998 as an ISO/IEC 14496 standard. MPEG4 differs from the previous standards in a number of ways. The new standard allows interactivity, high compression and accessibility to the video content. Video information in MPEG4 is no more specified as compressed frames but as

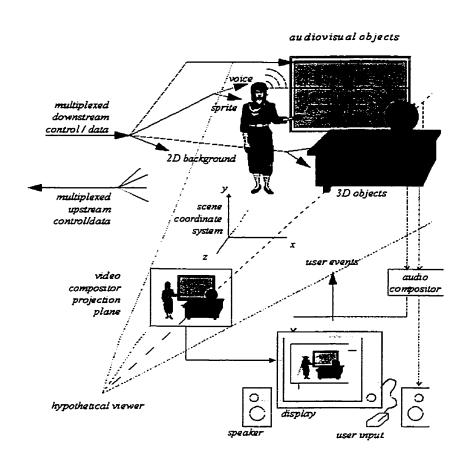

compressed Video Objects (VO). In this section, by introducing this standard, we show the validity of our categorization introduced in this chapter. We note that the operations involved in affine transformations, motion estimation and wavelet transforms will form important components in MPEG4. MPEG4 achieves a high performance by providing standardized ways to:

- represent units of aural, visual or audiovisual content, called "media objects". These media objects can be of natural or synthetic origin; this means they could be recorded with a camera or microphone, or generated with a computer as shown in Figure 9.

- describe the composition of these objects to create compound media objects that form audiovisual scenes:

- multiplex and synchronize the data associated with media objects, so that they can be transported over network channels.

- interact with the audiovisual scene generated at the receiver's end.

In addition,

(1) MPEG4 uses object based coding as opposed to frame and channel based coding of previous standards. MPEG4 also defines how interactivity between user and objects can be employed, in contrast to previous standards which allowed very limited interactivity. Objects in MPEG4 are very important because they allow content based interactivity. Objects are coded independently but grouped together to form a scene. Interactivity is enabled by the representation of a scene as a collection of objects or the composition. When the viewer selects or points to an object, actions that are

predefined for the object can occur. An object in MPEG4 is a component of a scene or the final audio-video presentation. Objects can be simple or compound.

Figure 9 - An example of an MPEG-4 Scene

(2) MPEG4 allows the coding of objects as arbitrary shaped images or rectangular images. Previous standards can code only rectangular area. In MPEG4, arbitrary shapes are generated by coding a rectangular area and then adding a shape layer or mask which defines the exact shape of the video object.

- (3) MPEG4 provides different coding methods (also called toolboxes) for coding different types of material. Computer generated or synthetic material can be coded using methods that are more appropriate to that format. MPEG1 and MPEG2 only addressed coding of natural material such as video or film. Normal video objects are usually coded using DCT based compression methods in MPEG4 similar to those used in MPEG1 and MPEG2. The DCT based coding methods are optimized for natural images that contain many shades of colors and smooth variations that normally occur in the real world. Computer generated images can have very few colors and many sharp transitions. DCT based coding methods do not compress these types of images. MPEG4 provides alternate methods of coding images that are computer generated. These objects are called synthetic objects to differentiate them from natural video and audio objects. Since computer generated objects can be created from sending commands to a rendering engine, one of the most efficient methods of compressing computer generated objects is to compress the commands to the rendering engine such as a text imager, 2D and 3D graphics rendering engine or sound generators.

- (4) Because of the independent coding of objects in MPEG4, a means to combine objects in a scene is required. This is called composition and applies to both audio and video objects. Composition is the layering of objects to produce the final displayed image. Since objects can overlap depending on their size and position, it is required to determine which object is visible at any point in the displayed image. Further more, if a gray scale mask is used, the object being composited allows some of the underlying

objects to be visible as well. MPEG4 allows 3D **affine transformations** on each object before it is composited. This means that each object may be translated, scaled and rotated in 3D space before composition. The affine transformation parameters for each object can be modified during the presentation. Composition is defined by a scene description object in the MPEG4 bitstream. The scene is expressed as a hierarchy of nodes, which represent objects. The scene specifies audio-video composition as well as relationships between objects and the actions that can occur for each object.

- (5) MPEG4 is designed to be an evolving standard. As new methods of coding are developed, they can be integrated in existing MPEG4 decoders so that they can decode new material, coded using the new algorithms.

- (6) MPEG4 broadens applications from mainly two-way videophone appliances to a number of conceivable video communication or video entertainment devices.

- (7) Since MPEG4 specifies the coding of natural and synthetic audio-video sources as independent objects, additional objects can be added to the mainstream without requiring the decoding and re-encoding. All the objects are combined in the decoder to form the final audio and video presentation.

We note that the novelty of MPEG4 resides in object based techniques. Affine transformations are among appropriate toolkits to achieve object based processing. Fractal processing is also an appropriate candidate for coding synthetic objects in a scene.

Wavelet coding is used to code texture information. In the next section, we present visual coding techniques, which are introduced in MPEG4 standard.

### ☐ Coding of Visual Objects

Visual objects can be either of natural or of synthetic origin. Different coding techniques are employed for different visual objects. In this section, we show that our proposed candidate algorithm encompasses a majority of coding techniques in MPEG4 standard.

#### 2.5.1 Natural Textures, Images and Video

The tools for representing natural video in the MPEG4 visual standard aim at providing standardized core technologies allowing efficient storage, transmission and manipulation of textures, images and video data for multimedia environments.

The visual part of the MPEG4 standard will provide a toolbox containing tools and algorithms bringing solutions to natural visual objects. It will give an efficient representation of visual objects of arbitrary shape, with the goal to support so-called content-based functionalities. Next to this, it will support most functionalities already provided by MPEG-1 and MPEG-2, including the provision to efficiently compress standard rectangular sized image sequences at varying levels of input formats, frame rates, pixel depth, bit-rates, and various levels of spatial, temporal and quality scalability.

## Support for Conventional and Content-Based Functionalities

The MPEG-4 Video standard will support the decoding of conventional rectangular images and video as well as the decoding of images and video of arbitrary shapes.

The coding of conventional images and video is achieved similar to MPEG-1/2 coding and involves motion prediction/compensation followed by DCT based texture coding. We recall from section 2.4 that fractal/affine processing employs a super set of these operations.

Global motion compensation is based on the transmission of static "sprite" which is a possibly large still image describing panoramic background and motion vectors. For each consecutive image in a sequence, only 8 global motion parameters describing camera motion are coded to reconstruct the object. These parameters represent the appropriate affine transform of the sprite transmitted in the first frame.

### Coding of Textures and Still Images

Efficient Coding of visual textures and still images is supported by the visual texture mode of the MPEG4. This mode is based on wavelet transform that provides very high coding efficiency over a very wide range of bitrates. Together with high compression efficiency, it also provides spatial and quality scalabilities (up to 11 levels of spatial scalability and continuous quality scalability) and also arbitrary-shaped object coding. The wavelet formulation provides a scalable bitstream coding in the form of an image resolution pyramid for progressive transmission and temporal enhancement of still images. The coded bitstream is also intended for downloading the image resolution hierarchy into the terminal to be formatted as 'bitmap texture' as used in 3D rendering systems. This technology provides resolution scalability to deal with a wide range of viewing conditions more typical of interactive applications and the mapping of imagery into 2D and 3D virtual worlds.

#### Scalable Coding of Video Objects

MPEG4 supports the coding of images and video objects with spatial and temporal scalability, both with conventional rectangular as well as with arbitrary shape. Scalability refers to the ability to only decode a part of a bitstream and reconstruct images or image sequences with:

reduced decoder complexity and thus reduced quality;

reduced spatial resolution;

reduced temporal resolution;

equal temporal and spatial resolution but with reduced quality.

This functionality is desired for progressive coding of images and video over heterogeneous networks, as well as for applications where the receiver is not willing or capable of displaying the full resolution or full quality images or video sequences.

#### 2.5.2 Synthetic Objects

Synthetic objects form a subset of the larger class of computer graphics such as:

- a synthetic description of human face and body

- ⇒ The shape, texture and expressions of the face are generally controlled by the bitstream containing instances of Facial Definition Parameter (FDP) sets and/or Facial Animation Parameter (FAP) sets. Upon construction, the Face object contains a generic face with a neutral expression. This face can already be rendered.

- animation streams of the face and body

- ⇒ The rendered face is capable of receiving the animation parameters from the bitstream, which will produce animation of the face including expressions, speech, etc. Body Animation is being designed into the MPEG4 fabric to work in a thoroughly integrated manner with face/head animation.

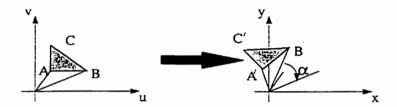

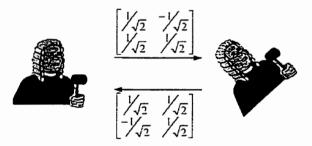

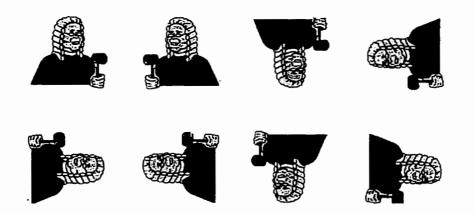

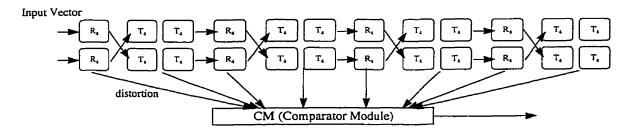

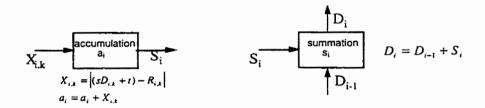

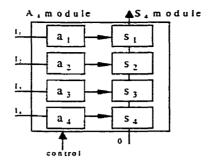

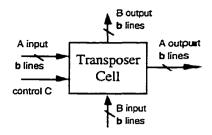

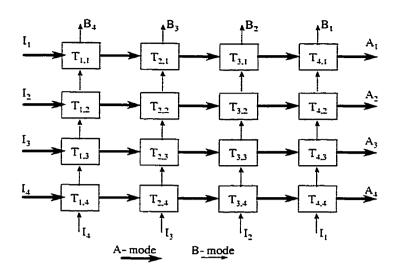

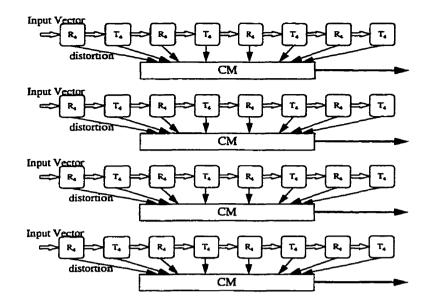

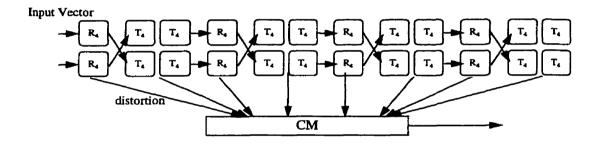

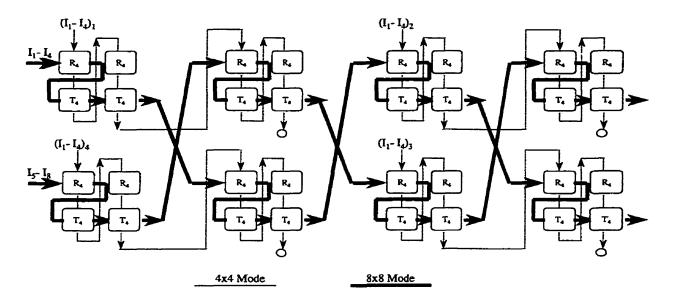

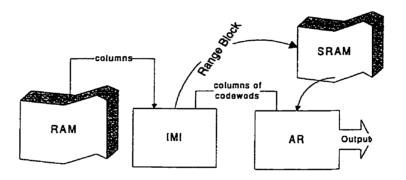

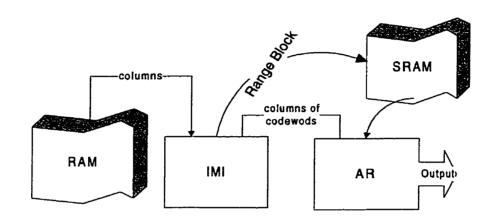

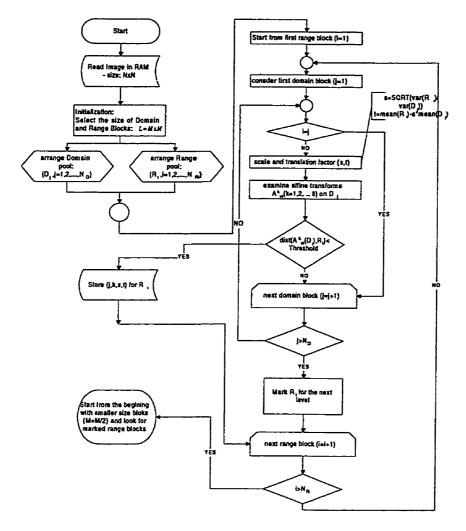

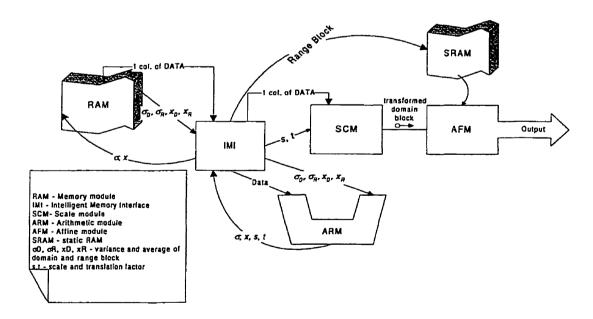

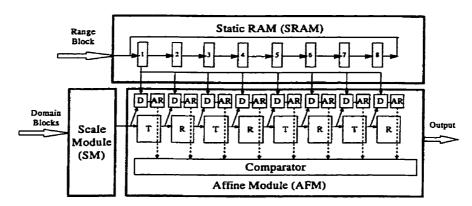

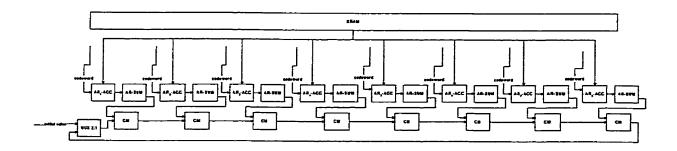

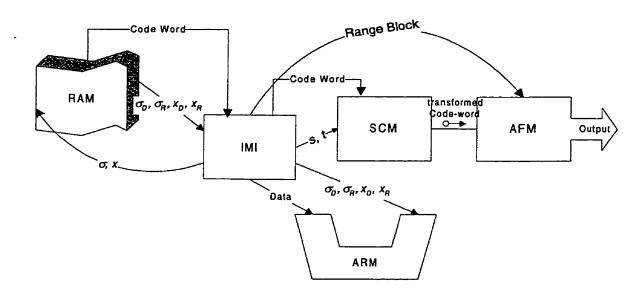

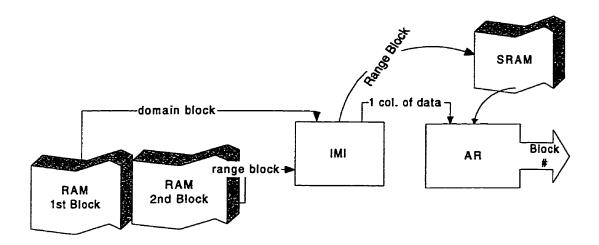

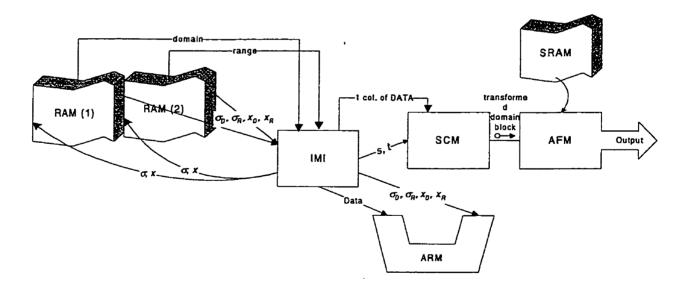

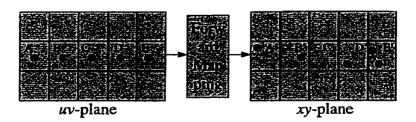

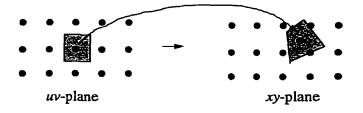

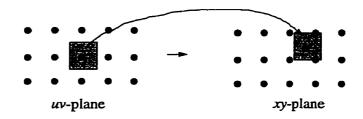

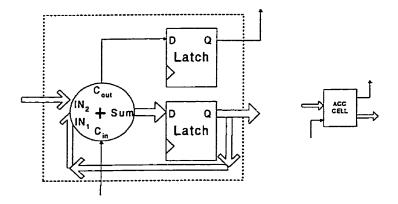

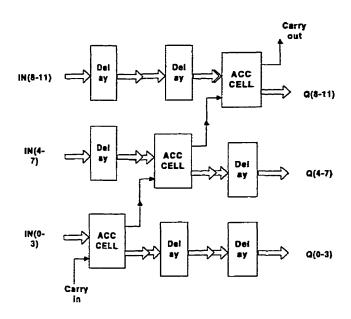

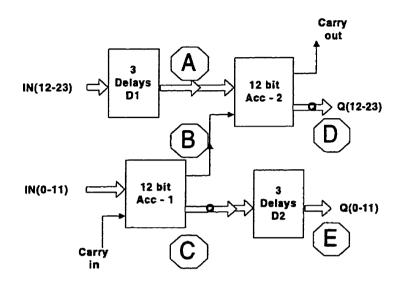

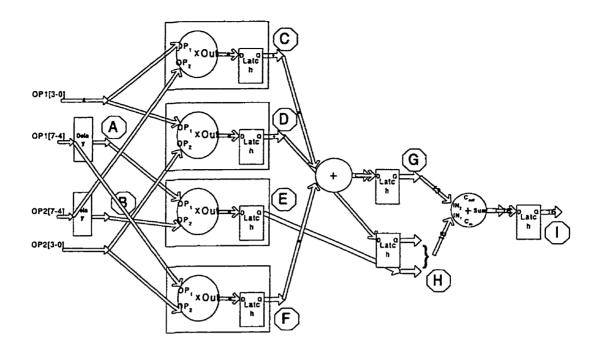

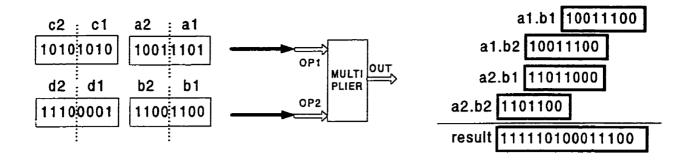

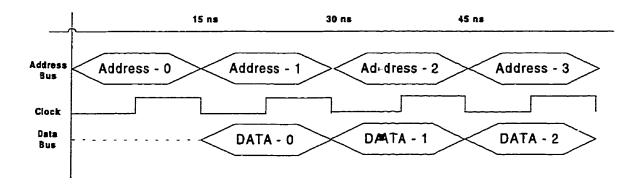

- static and dynamic mesh coding with texture mapping