# Test and Debug Solutions for 3D-Stacked Integrated Circuits

by

Sergej Deutsch

Department of Electrical and Computer Engineering Duke University

| Date:                              |

|------------------------------------|

| Approved:                          |

|                                    |

|                                    |

|                                    |

|                                    |

| Krishnendu Chakrabarty, Supervisor |

|                                    |

|                                    |

|                                    |

| Pankaj Agarwal                     |

| 1 anna 118an wan                   |

|                                    |

|                                    |

|                                    |

| Rolf Drechsler                     |

|                                    |

|                                    |

|                                    |

| Nan Jokerst                        |

|                                    |

|                                    |

|                                    |

| Hisham Massoud                     |

| nisham wassoud                     |

|                                    |

|                                    |

|                                    |

| James Morizio                      |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

## ABSTRACT

# Test and Debug Solutions for 3D-Stacked Integrated Circuits

by

Sergej Deutsch

Department of Electrical and Computer Engineering Duke University

| Approved:                          |  |

|------------------------------------|--|

| Krishnendu Chakrabarty, Supervisor |  |

| Pankaj Agarwal                     |  |

| Rolf Drechsler                     |  |

| Nan Jokerst                        |  |

| Hisham Massoud                     |  |

| James Morizio                      |  |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

Copyright © 2015 by Sergej Deutsch All rights reserved except the rights granted by the Creative Commons Attribution-Noncommercial Licence

# Abstract

Three-dimensional (3D) stacking using through-silicon vias (TSVs) promises higher integration levels in a single package, keeping pace with Moore's law. TSVs are small copper or tungsten vias that go vertically through the substrate of a die and provide vertical interconnects to a die stacked on top. TSV-based interconnects have benefits in terms of performance, interconnect density, and power efficiency.

Testing has been identified as a showstopper for volume manufacturing of 3D-stacked integrated circuits (3D ICs). A number of challenges associated with 3D test need to be addressed before 3D ICs can become economically viable. This dissertation provides solutions to new challenges related to 3D test content, test access, diagnosis and debug.

Test content specific to 3D ICs targets defect that occur during TSV manufacturing and stacking process. One example is the effect of thermo-mechanical stress due to TSV fabrication process on the surrounding logic gates. In this dissertation, we analyze these effects and their consequences for delay testing. We provide quantitative results showing that the use of TSV-stress oblivious circuit models for test generation leads to considerable reduction in delay-test quality. We propose a test flow that uses TSV-stress aware circuit models to improve test quality.

Another example of 3D-specific test challenge is the testability of TSVs. In this dissertation, we focus on TSV test prior to die bonding, as access to TSVs is limited at this stage. We propose a non-invasive method for pre-bond TSV test that does

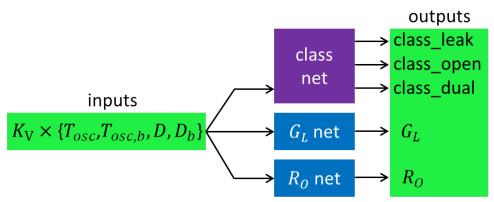

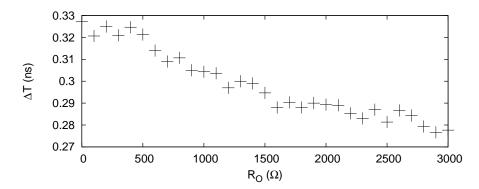

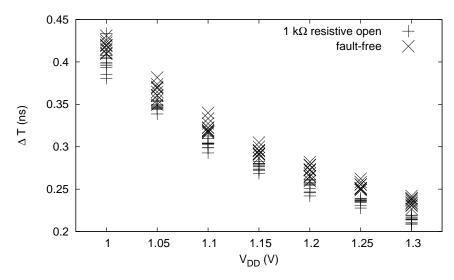

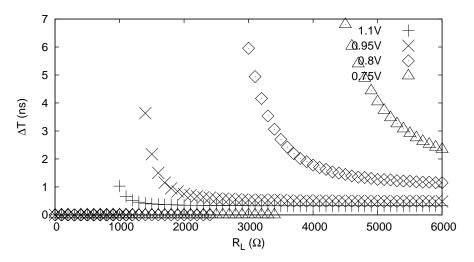

not require TSV probing. The method uses ring oscillators and duty-cycle detectors in order to detect variations in propagation delay of gates connected to a single-sided TSV. Based on the measured variations, we can diagnose the TSV and predict the size of resistive-open and leakage faults using a regression model based on artificial neural networks. In addition, we exploit different voltage levels to increase the robustness of the test method.

In order to efficiently deliver test content to structures under test in a 3D stack, 3D design-for-test (DfT) architectures are needed. In this dissertation, we discuss existing 3D-DfT architectures and their optimization. We propose an optimization approach that takes uncertainties in input parameters into account and provides a solution that is efficient in the presence of input-parameter variations and minimizes test time, therefore reducing test cost.

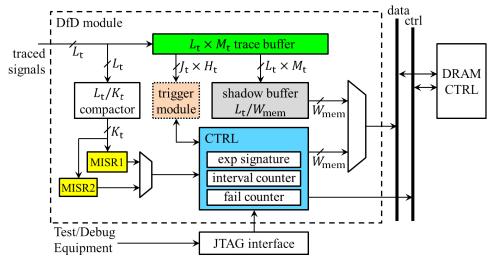

Post-silicon debug is a major challenge due to continuously increasing design complexity. Traditional debug methods using signal tracing suffer from the limited capacity of on-chip trace buffers that only allow for signal observation during a short time window. This dissertation proposes a low-cost debug architecture for massive signal tracing in 3D-stacked ICs with wide-I/O DRAM dies. The key idea is to use available on-chip DRAM for trace-data storage, which results in a significant increase of the observation window compared to traditional methods that use trace buffers. In addition, the proposed on-chip debug circuitry can identify erroneous segments of observed data by using compact signatures that are stored in the DRAM a priori. Only failing intervals are off-loaded from a temporary trace buffer into DRAM, allowing for a more efficient use of the memory, resulting in a larger observation window.

In summary, this dissertation provides solutions to several challenges related to 3D test and debug that need to be addressed before volume manufacturing of 3D ICs can be viable.

# Contents

| $\mathbf{A}$ | bstra  | act                                        | iv  |

|--------------|--------|--------------------------------------------|-----|

| Li           | ist of | Tables                                     | ix  |

| Li           | ist of | Figures                                    | X   |

| $\mathbf{A}$ | ckno   | wledgements                                | xiv |

| 1            | Inti   | roduction                                  | 1   |

|              | 1.1    | Introduction to 3D Integration Using TSVs  | 4   |

|              | 1.2    | 3D Test Flow                               | Ę   |

|              | 1.3    | 3D DfT Architectures and Optimization      | 10  |

|              | 1.4    | Defects due to TSV Manufacturing           | 14  |

|              | 1.5    | Pre-Bond TSV Test                          | 17  |

|              | 1.6    | Post-Silicon Debug Using Signal Tracing    | 20  |

| 2            | TSV    | V Stress-Aware ATPG                        | 23  |

|              | 2.1    | Related Prior Work                         | 25  |

|              |        | 2.1.1 SDD Testing and SDQL                 | 25  |

|              |        | 2.1.2 Mobility Variation due to TSV Stress | 26  |

|              | 2.2    | Methodology                                | 27  |

|              |        | 2.2.1 TSV Stress-Aware Model Generation    | 28  |

|              |        | 2.2.2 TSV-Stress-Aware ATPG                | 30  |

|              | 2.3    | Case Study                                 | 31  |

|   |             | 2.3.1  | Test Vehicles                                                                     | 31 |

|---|-------------|--------|-----------------------------------------------------------------------------------|----|

|   |             | 2.3.2  | ATPG Results                                                                      | 33 |

|   | 2.4         | Conclu | asion                                                                             | 37 |

| 3 |             |        | ss Pre-Bond TSV Test and Diagnosis Using Ring Oscilla-<br>Multiple Voltage Levels | 39 |

|   | 3.1         | Pre-Bo | ond TSV Test Method                                                               | 41 |

|   |             | 3.1.1  | TSV Fault Model                                                                   | 41 |

|   |             | 3.1.2  | Ring Oscillators with TSVs                                                        | 43 |

|   |             | 3.1.3  | Duty-Cycle Detectors                                                              | 46 |

|   |             | 3.1.4  | DfT Infrastructure for On-Chip Measurement                                        | 49 |

|   | 3.2         | Regres | ssion Model Based on Artificial Neural Networks                                   | 51 |

|   | 3.3         | Simula | ation Results                                                                     | 56 |

|   |             | 3.3.1  | Resistive-Open Faults                                                             | 56 |

|   |             | 3.3.2  | Leakage Faults                                                                    | 59 |

|   |             | 3.3.3  | Duty-Cycle Detector                                                               | 61 |

|   |             | 3.3.4  | Regression Model for Inferring Fault Size                                         | 62 |

|   |             | 3.3.5  | DfT Area Cost and Test Time Estimations                                           | 67 |

|   | 3.4         | Conclu | asions                                                                            | 69 |

| 4 | Uno<br>ture |        | ty-Aware Robust Optimization of Test-Access Architec-                             | 71 |

|   | 4.1         |        | tain Parameters in Optimization of 3D Test Architecture and cheduling             | 74 |

|   | 4.2         | Relate | ed Prior Work                                                                     | 77 |

|   |             | 4.2.1  | Overview of Robust Optimization                                                   | 77 |

|   |             | 4.2.2  | Simulated Annealing                                                               | 80 |

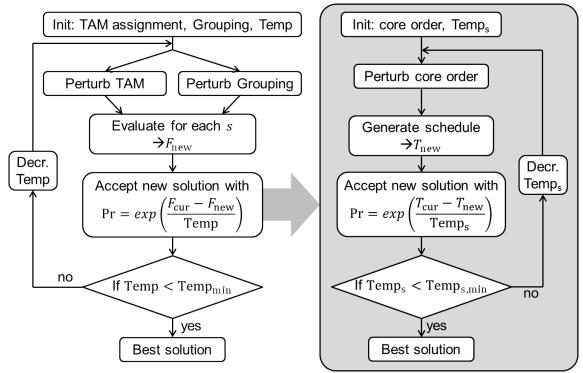

|   | 4.3         | Robus  | t Optimization of 3D Test Architecture                                            | 81 |

|                  |                  | 4.3.1 Mathematical Model for Robust Co-Optimization of Test Architecture and Test Scheduling |                                                                       | 83  |

|------------------|------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|

|                  |                  | 4.3.2                                                                                        | Heuristic Method for Robust Optimization Based on Simulated Annealing | 89  |

|                  | 4.4              | Simula                                                                                       | ation Results                                                         | 94  |

|                  | 4.5              | Conclu                                                                                       | asion                                                                 | 100 |

| 5                | Mas              | ssive S                                                                                      | ignal Tracing Using On-Chip DRAM for Silicon Debug                    | 103 |

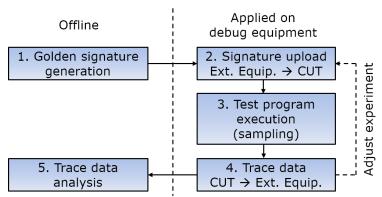

|                  | 5.1              | Propo                                                                                        | sed Debug Framework                                                   | 105 |

|                  |                  | 5.1.1                                                                                        | Multiple-Input Signature Register (MISR)                              | 108 |

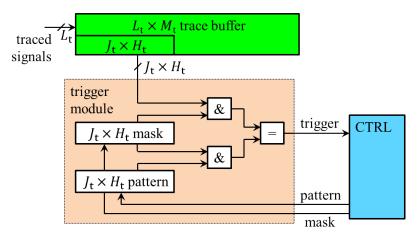

|                  |                  | 5.1.2                                                                                        | Trigger Module                                                        | 109 |

|                  |                  | 5.1.3                                                                                        | Trace Buffer and Shadow Buffer                                        | 112 |

|                  |                  | 5.1.4                                                                                        | Control Logic                                                         | 113 |

|                  |                  | 5.1.5                                                                                        | Interface with DRAM: Challenges, Limitations, and Solutions           | 115 |

|                  |                  | 5.1.6                                                                                        | Analysis of Compression Effectiveness                                 | 117 |

|                  | 5.2              | Simula                                                                                       | ation Results                                                         | 122 |

|                  |                  | 5.2.1                                                                                        | DfD Implementation and Simulation                                     | 122 |

|                  |                  | 5.2.2                                                                                        | Comparison with Method Proposed in [75]                               | 124 |

|                  |                  | 5.2.3                                                                                        | Comparison with Method Proposed in [74]                               | 127 |

|                  | 5.3              | Conclu                                                                                       | asion                                                                 | 128 |

| 6                | Con              | clusio                                                                                       | ns                                                                    | 130 |

|                  | 6.1              | Future                                                                                       | e Research Directions                                                 | 132 |

| $\mathbf{B}^{i}$ | Bibliography 133 |                                                                                              |                                                                       | 133 |

| Bi               | iogra            | phy                                                                                          |                                                                       | 144 |

# List of Tables

| 2.1 | Design statistics for the benchmarks                                                                 | 32  |

|-----|------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Defective parts per million for various designs                                                      | 35  |

| 2.3 | Pattern count for various designs                                                                    | 36  |

| 3.1 | Truth table for TEST CTRL output specification                                                       | 51  |

| 4.1 | Solutions of the LP problem for (a) $s1$ , (b) $s2$ , and (c) taking both $s1$ and $s2$ into account | 80  |

| 4.2 | Design parameters of some of the benchmark SoCs used in simulations.                                 | 97  |

| 4.3 | Input parameters and resulting test times for the SoC benchmarks                                     | 99  |

| 5.1 |                                                                                                      | 106 |

| 5.2 | Comparison of debug-session time with prior work [75]                                                | 125 |

| 5.3 | Comparison of debug-session time with prior work [74]                                                | 128 |

# List of Figures

| 1.1  | Packaged 3D IC on a board                                                                        | 5  |

|------|--------------------------------------------------------------------------------------------------|----|

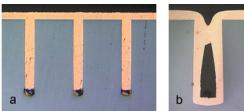

| 1.2  | SEM photographs of (a) TSVs and (b) micro-bumps (source IMEC).                                   | 6  |

| 1.3  | Typical TSV and micro-bump dimensions                                                            | 6  |

| 1.4  | TSV fabrication steps in IMEC's process                                                          | 7  |

| 1.5  | Wafer thinning and stacking steps in imec process                                                | 7  |

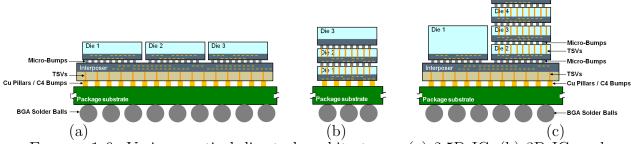

| 1.6  | Various vertical die stack architectures: (a) 2.5D IC, (b) 3D IC, and (c) 5.5D IC [14]           | 8  |

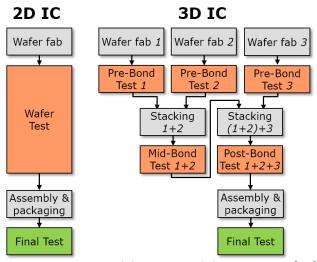

| 1.7  | 2D (a) and 3D (b) test flows [18]                                                                | 9  |

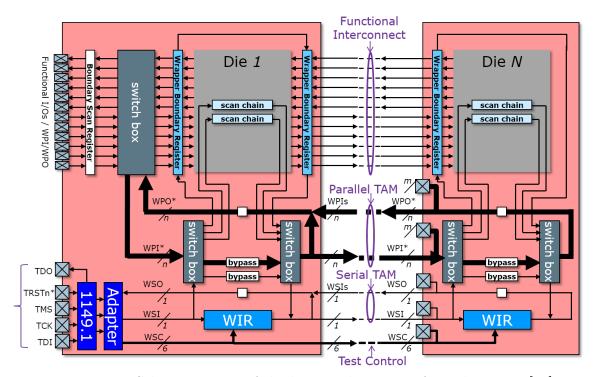

| 1.8  | Schematic view of the logic-on-logic 3D DfT architecture [14]                                    | 11 |

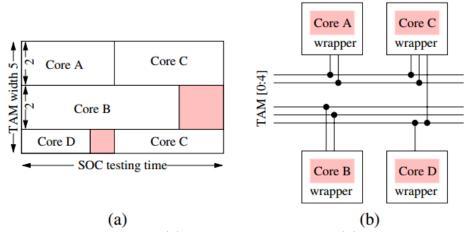

| 1.9  | An illustration of (a) rectangle packing and (b) the corresponding TAM design [28]               | 12 |

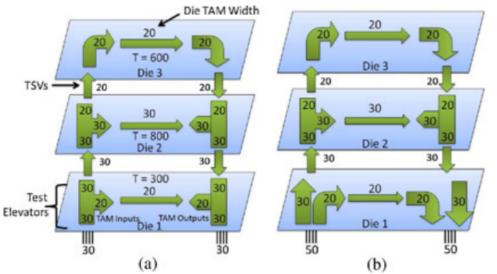

| 1.10 | An example of a 3D test architecture with (a) serial TAM and (b) parallel test architecture [32] | 13 |

| 1.11 | TSV plating defects: (a) voids, (b) pinch-off [33]                                               | 14 |

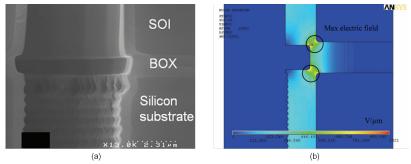

| 1.12 | (a) BOX undercut, (b) Simulated electric field [35]                                              | 15 |

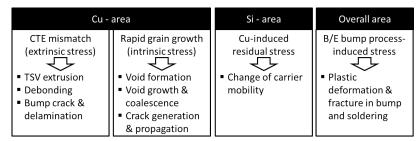

| 1.13 | TSV stress types and their induced failures [36]                                                 | 16 |

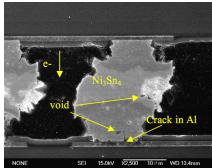

| 1.14 | Crack in a micro-bump due to mechanical stress [36]                                              | 16 |

| 1.15 | Micro-bump failure after current stress test [42]                                                | 17 |

| 1.16 | Traditional signal-tracing architecture                                                          | 21 |

| 2.1  | Delay distribution $F_D(t_s)$                                                                    | 25 |

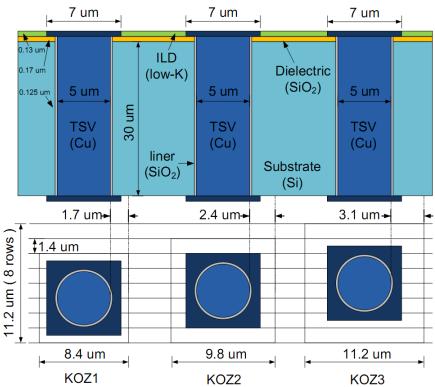

| 2.2  | The TSV structure and three different KOZ sizes used in our studies.                             | 28 |

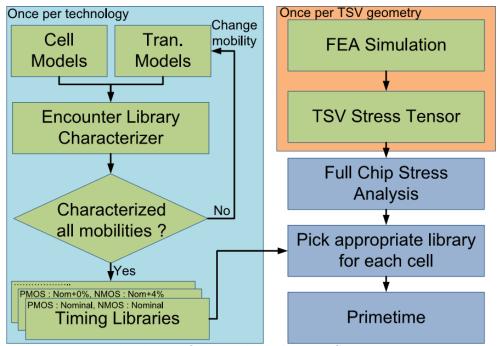

| 2.3  | The design flow used to obtain TSV-stress-aware timing                                                                                                                                                                                                                                            | 29 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4  | ATPG tool flow                                                                                                                                                                                                                                                                                    | 32 |

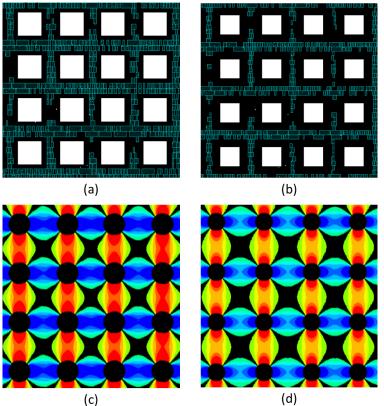

| 2.5  | (a,b) Layout screenshots for KOZ1 and KOZ3 of benchmark des_perf. White rectangles indicate TSVs, and blue indicates standard cells. (c,d) The corresponding PMOS mobility maps. Black indicates TSVs. Green, red and blue represent nominal, positive, and negative mobility change respectively | 33 |

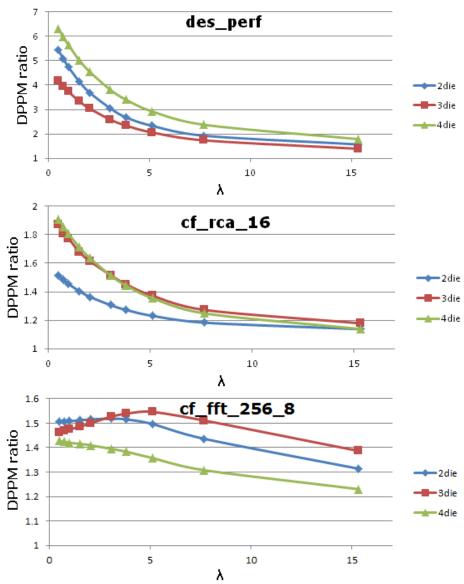

| 2.6  | DPPM ratio as function of $\lambda$                                                                                                                                                                                                                                                               | 37 |

| 3.1  | Voids in 10 $\mu$ m x 60 $\mu$ m TSVs [46]                                                                                                                                                                                                                                                        | 40 |

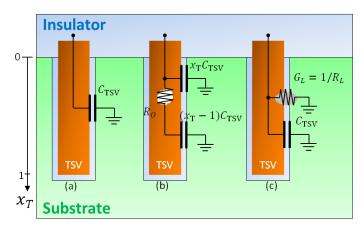

| 3.2  | TSV models: (a) fault-free, (b) micro-void, (c) pinhole                                                                                                                                                                                                                                           | 40 |

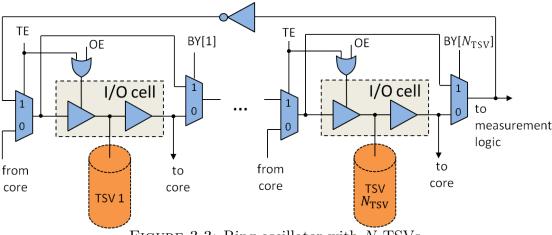

| 3.3  | Ring oscillator with $N$ TSVs                                                                                                                                                                                                                                                                     | 43 |

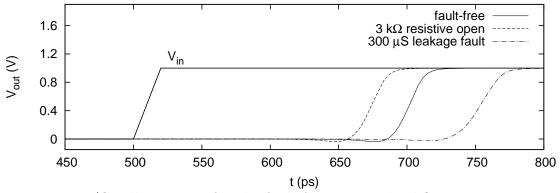

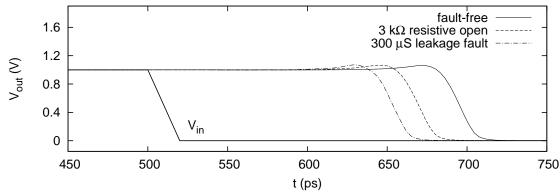

| 3.4  | I/O-cell rise time for the fault-free case and 3 k $\Omega$ resistive-open and 300 $\mu$ S leakage faults                                                                                                                                                                                         | 46 |

| 3.5  | I/O-cell fall time for the fault-free case and 3 k $\Omega$ resistive-open and 300 $\mu S$ leakage faults                                                                                                                                                                                         | 46 |

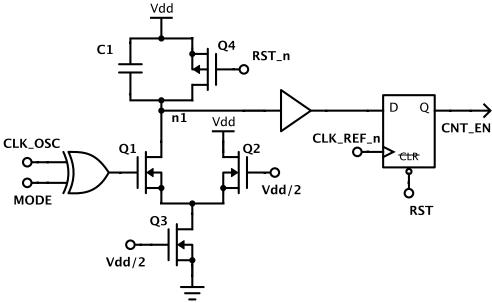

| 3.6  | Schematic of the duty-cycle detector                                                                                                                                                                                                                                                              | 49 |

| 3.7  | Pre-bond TSV test DfT infrastructure                                                                                                                                                                                                                                                              | 50 |

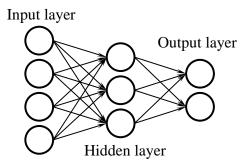

| 3.8  | Example of a generic three-layer ANN                                                                                                                                                                                                                                                              | 53 |

| 3.9  | Regression model based on ANNs                                                                                                                                                                                                                                                                    | 56 |

| 3.10 | $\Delta T$ as a function of $R_O$ at location $x_{\rm T}=0.5$ and at 1.1 V supply voltage.                                                                                                                                                                                                        | 58 |

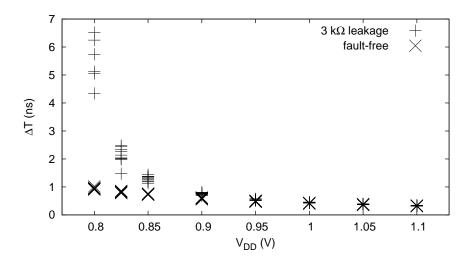

| 3.11 | $\Delta T$ as a function of supply voltage in (a) fault-free case and (b) in case of 1 k $\Omega$ resistive open at $x_{\rm T}=0.5$                                                                                                                                                               | 59 |

| 3.12 | $\Delta T$ as a function of $R_L$ at different voltage levels                                                                                                                                                                                                                                     | 60 |

| 3.13 | $\Delta T$ as a function of supply voltage in (a) fault-free case, and (b) in case of 3 k $\Omega$ (333.3 $\mu$ S) leakage fault                                                                                                                                                                  | 61 |

| 3.14 | Confusion matrix for class net                                                                                                                                                                                                                                                                    | 63 |

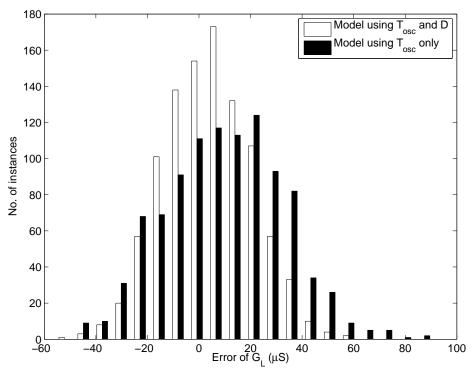

| 3.15 | Error histograms of $G_{\rm L}$ -net and $G_{\rm L}$ -net_r at $G_{\rm L}=100~\mu{\rm S}.$                                                                                                                                                                                                        | 64 |

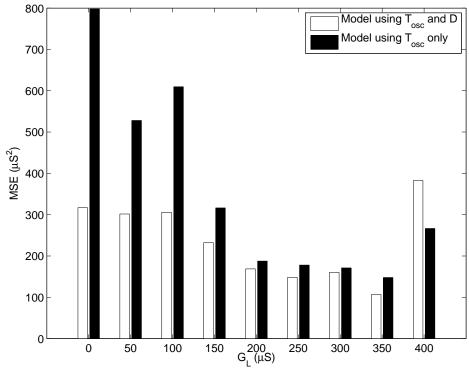

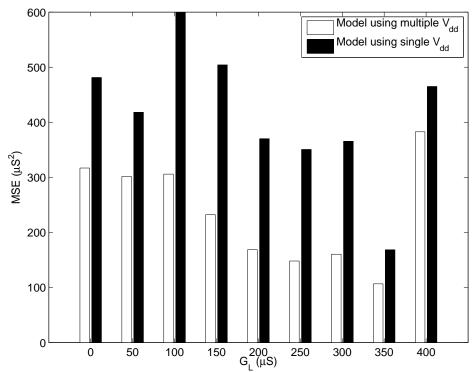

| 3.16 | MSE of $G_{\rm L}$ -net and $G_{\rm L}$ -net_r for different values of $G_{\rm L}$                                                                                                                                                                                                                | 65 |

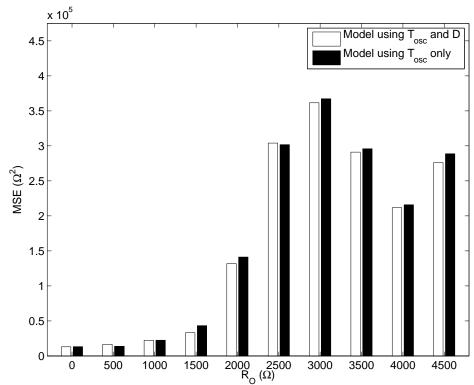

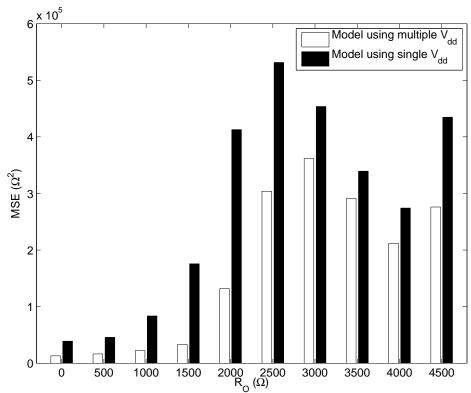

| 3.17 | MSE of $R_{\rm O}$ -net and $R_{\rm O}$ -net_r for different values of $R_{\rm O}$                                                                                                                                                                                                                | 66 |

| 3.18 | MSE of $G_{\rm L}$ -net using multiple vs. single $V_{\rm dd}$                                                                                                                                   | 67   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.19 | MSE of $R_{\rm O}$ -net using multiple vs. single $V_{\rm dd}$                                                                                                                                   | 68   |

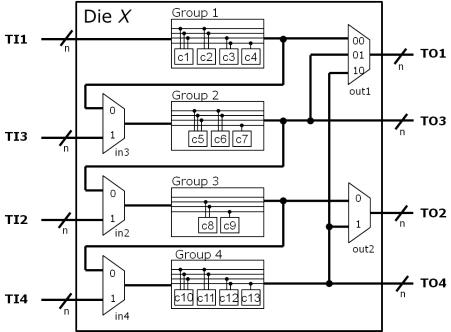

| 4.1  | Die-level architecture with reconfigurable multiple-width TAM                                                                                                                                    | 75   |

| 4.2  | Mathematical programming model for non-robust test architecture optimization                                                                                                                     | 85   |

| 4.3  | SA-based Robust Optimization Flow                                                                                                                                                                | 90   |

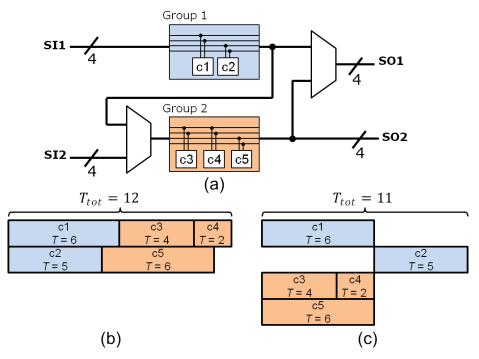

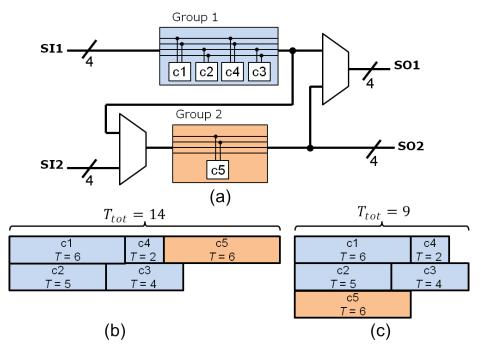

| 4.4  | Test Architecture 1: (a) TAM assignment and partitioning, (b) schedule for 4-bit configuration, (c) schedule for 8-bit configuration                                                             | 95   |

| 4.5  | Test Architecture 2: (a) TAM assignment and partitioning, (b) schedule for 4-bit configuration, (c) schedule for 8-bit configuration                                                             | 96   |

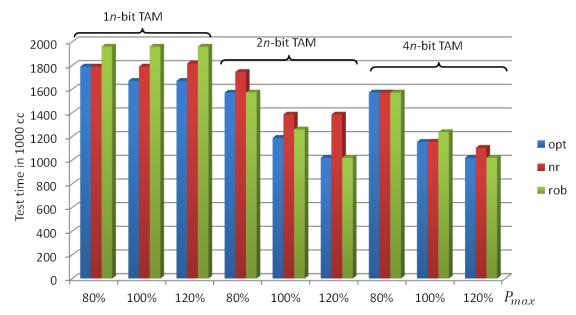

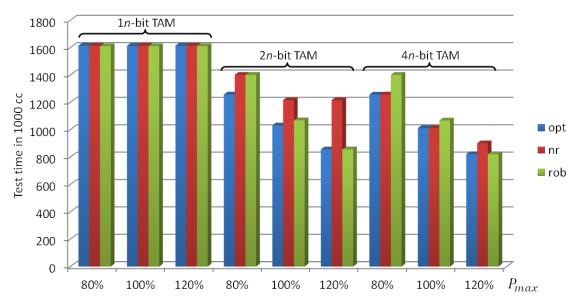

| 4.6  | Evaluation of the robust and non-robust solutions for p22810 in $1n$ -bit, $2n$ -bit, and $4n$ -bit configuration for different $P_{max}$ for nominal core test-time values $T_i$                | 100  |

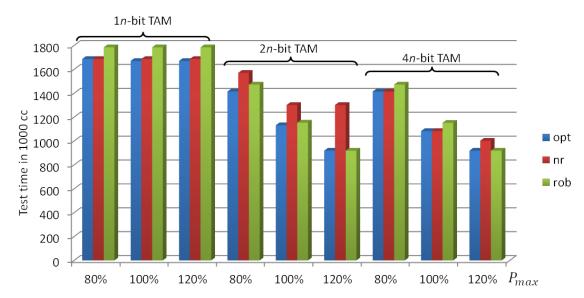

| 4.7  | Evaluation of the robust and non-robust solutions for p22810 in $1n$ -bit, $2n$ -bit, and $4n$ -bit configuration for different $P_{max}$ for some core test-time values $T_i$ reduced by $10\%$ | 101  |

| 4.8  | Evaluation of the robust and non-robust solutions for p22810 in $1n$ -bit, $2n$ -bit, and $4n$ -bit configuration for different $P_{max}$ for some core test-time values $T_i$ reduced by $20\%$ | 102  |

| 5.1  | Proposed debug flow                                                                                                                                                                              | 106  |

| 5.2  | Overview of the proposed design-for-debug architecture                                                                                                                                           | 107  |

| 5.3  | Architectural view of the trigger module                                                                                                                                                         | 110  |

| 5.4  | Setup example for a transition recognition                                                                                                                                                       | 112  |

| 5.5  | Operations of DfD modules during signal tracing                                                                                                                                                  | 113  |

| 5.6  | State diagram for the control block CTRL                                                                                                                                                         | 115  |

| 5.7  | Timing diagram for control signals                                                                                                                                                               | 115  |

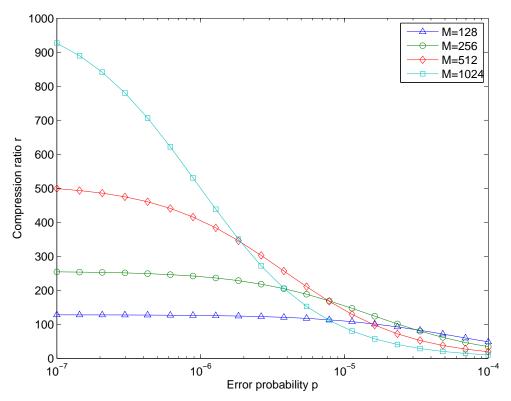

| 5.8  | Compression ratio $r$ as function of error probability $p$ for $L_{\rm t}=K_{\rm t}=32$ , $S_{\rm t}=32$ , and different values of $M_{\rm t}$ in the case of a uniform distribution             | .119 |

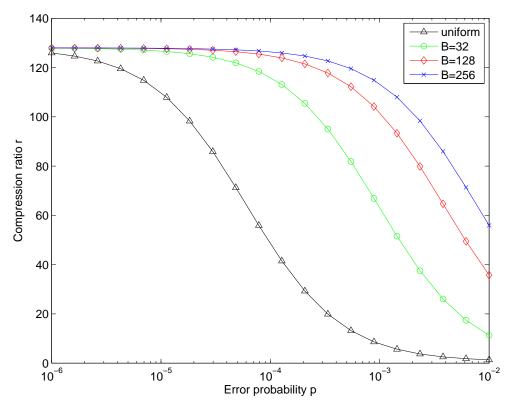

| 5.9  | Compression ratio $r$ as function of error probability $p$ for $L_{\rm t}=K_{\rm t}=32$ , $S_{\rm t}=32$ , and $M_{\rm t}=128$ in the case of error bursts of different lengths.                 | 120  |

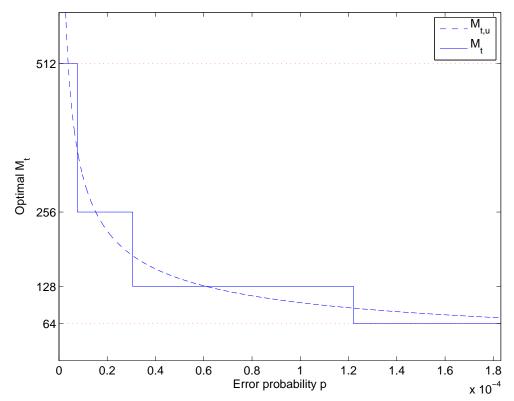

| 5.10 | Optimal trace depth $M_t$ as a function of error probability $p$ for the case                                                                   |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $L_{\rm t} = K_{\rm t} = 32. \dots \dots$ | 122 |

# Acknowledgements

I would like to acknowledge the financial support received from the National Science Foundation and the Semiconductor Research Corporation. I thank my PhD advisor, Krishnendu Chakrabarty, for his mentorship. I also thank Sun Kyu Lim and Shreepad Panth for the 3D design benchmarks that they contributed for use in research. I acknowledge Erik Jan Marinnisen for his collaboration. I also acknowledge the contributions of the past and present students at Duke University, including Mukesh Agrawal, Qing Duan, Hongxia Fang, Zipeng Li, Yan Luo, Brandon Noia, Ran Wang, and Fangming Ye. Finally, I would like to thank the members of my committee for for their time and effort in reading this dissertation and attending my defense.

1

# Introduction

Three-dimensional IC stacking using through-silicon vias (TSVs) is a relatively new technology that has a number of advantages over conventional stacking methodologies [1]. TSVs are vertical copper or tungsten conducting nails passing through a thinned die. Typical TSV dimensions are 5  $\mu$ m diameter and 50  $\mu$ m height. The actual connection to the next die can be a direct copper-to-copper bond of the TSV onto a small landing pad, but today is often implemented by means of a CuSn microbump, of which typical dimensions are 25  $\mu$ m diameter at 40  $\mu$ m pitch [2]. As they form direct vertical interconnects between stacked dies, TSVs allow for a much larger number and higher density of interconnects than conventional wire-bonds. Due to their geometry, TSVs have relatively low capacitance and inductance, and thus enable high bandwidth and low power consumption [3].

Despite the numerous benefits offered by 3D integration, test challenges for 3D-stacked integrated circuits (ICs) must be addressed before volume manufacturing and defect screening can be feasible [4, 5, 6]. These challenges include the following.

#### • Test content

As any semiconductor product, a 3D IC should be tested for defects that lead to errors in the functional operation of the IC. These defects can be divided into two categories: (a) defects that are specific to 3D ICs, and (b) defects that occur both in traditional (2D) ICs and 3D ICs. The category (a) includes defects in TSVs and micro-bumps, as well as defects caused by mechanical stress during TSV and micro-bump manufacturing. New test techniques need to be developed to screen for these defects. The category (b) includes defects in the internal die logic. Traditional test methods, such as scan test, have been successfully used to test for these defects. However, test costs tend to multiply with the increasing complexity of 2D and 3D ICs; therefore, more efficient test solutions are required to keep test costs low.

#### Test access

Test access is difficult both in pre-bond and post-bond test of 3D ICs. In pre-bond test, probing on micro-bumps and TSVs is constrained due to their small dimensions. Therefore, special techniques are required to test TSV-based connections prior to die bonding. In post-bond test, only one die in a 3D stack has external connections - other dies require test access through this die, necessitating a 3D design-for-test (DfT) architecture that allows for test access to all components in the stack. In addition, 3D DfT architectures must be optimized for on-chip area requirements and test time, which both have a major impact on test costs.

#### • Diagnosis and Debug

Silicon debug requires a relatively large engineering effort, accounting for a significant portion of the total time-to-market of the silicon product and this portion has been projected to grow [7, 8]. In order to keep pace with advances in system-level integration, including 3D stacking, traditional methodologies for

bug localization need to be improved.

This introduction provides a motivation for this dissertation, which addresses the challenges of 3D test presented above.

In Chapter 2, we address the issue of thermo-mechanical stress due to TSV fabrication. TSV stress changes the timing profile of the digital logic surrounding TSVs, which has an impact on delay-fault testing. We analyse this effect and show quantitatively that test quality is significantly reduced if the test patterns are generated with TSV stress-oblivious circuit models. The detrimental impact of TSV stress on pattern effectiveness and test quality can be overcome by using stress-aware circuit models for test generation.

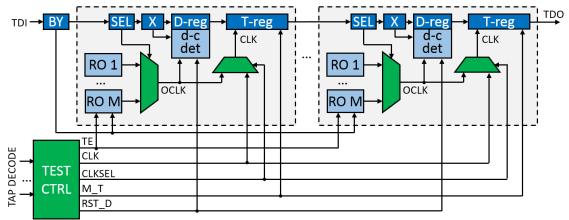

Chapter 3 presents a technique for contactless pre-bond TSV test and diagnosis using ring oscillators and duty-cycle detectors. TSVs are used as capacitive loads of their driving gates that are configured in a ring oscillator. By measuring the oscillation period and the duty cycle of the signal generated by the ring oscillators, we can detect resistive open and leakage faults. A regression model based on artificial neural networks can predict the fault type and the fault size using the oscillation period and the duty cycle measured at multiple voltage levels as input parameters. The accuracy of the regression model is evaluated through simulation using realistic models for a 45nm CMOS technology.

Chapter 4 addresses the challenge of robust optimization of 3D test-access architectures. Traditional optimization frameworks suffer from the drawback that they ignore potential uncertainties in input parameters. In realistic scenarios, however, the input parameter values used in the design phase may differ from the actual values that are known only after the design phase. Examples of such parameters include test power and configuration of the die test-access mechanism. We propose a robust-optimization framework that takes uncertainties in input parameters into account

and provides robust solutions. We evaluate the proposed framework and show that robust solutions are superior to single-point solutions in terms of average test time when there are uncertainties in the values of input parameters.

Finally, Chapter 5 presents a method for massive signal tracing using on-chip DRAM for in-system silicon debug. Traditional debug techniques using signal tracing suffer from the limited capacity of on-chip trace buffers. We propose a low-cost debug architecture for signal tracing that exploits large amounts of fast on-chip memories available in wide-I/O 3D ICs. The key idea of the proposed architecture is to store the trace data into functional memory, thereby significantly increasing the signal-observation window compared to traditional methods that use dedicated trace buffers. We evaluate the proposed method and show that the observation window can be increased by orders of magnitude compared to prior work at comparable hardware cost.

This introduction will continue with a general overview of 3D integration using TSVs and prior work in 3D test.

## 1.1 Introduction to 3D Integration Using TSVs

3D stacking by means of through-silicon vias (TSVs) is a relatively new technology that has a number of advantages over conventional stacking methodologies. TSVs are usually copper or tungsten nails going through the silicon substrate, electrically connecting the circuitry of the stacked dies [9]. Dies are bonded together by using copper or copper-tin micro-bumps, which are part of the inter-die interconnects. TSV-based interconnects allow a much higher density than traditional wire-bonds, which can only be placed along the perimeter of the die. This technology has the following benefits:

• The option of combining dies from different process technologies, i.e., optimized

for digital logic, analog logic, or DRAM.

- High-bandwidth, low-power, high-density inter-die connections

- Increased compound yield, as systems can be partitioned into smaller dies, increasing the yield of individual dies.

#### • Smaller footprint

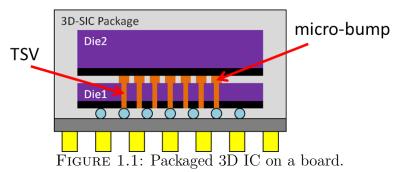

Figure 1.1 shows a packaged 3D stack consisting of two dies. In *Die1*, TSVs (in orange) have been processed and the silicon wafer has been thinned down in order to expose the TSVs on the back side. *Die2* has been manufactured using conventional (2D) technology without TSVs. Together with micro-bumps, TSVs form electrical connections between the active circuitry (in black) of both dies.

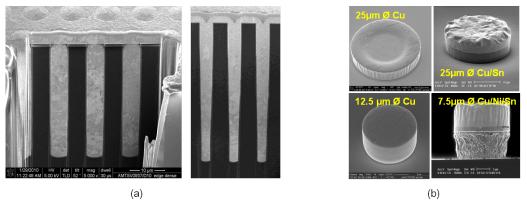

Cross-sections of two silicon wafers containing TSVs with different aspect ratios are depicted in Figure 1.2(a). Figure 1.2(b) shows micro-bumps of different forms and sizes. Table 1.3 shows the TSV and micro-bump dimensions that are used in the current technology at IMEC [10].

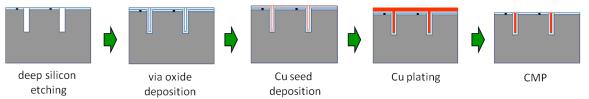

Figure 1.4 shows a typical TSV manufacturing flow. In the first step, holes are etched into the silicon substrate. Then an insulator is deposited and the holes are filled with copper. Chemical Mechanical Polishing removes the excess layer of copper. In order to expose the TSVs on the back-side of the silicon substrate, it needs to be thinned down, which is the next step.

FIGURE 1.2: SEM photographs of (a) TSVs and (b) micro-bumps (source IMEC).

| Dimension     | TSV                 | micro-bump              |

|---------------|---------------------|-------------------------|

| Diameter      | $5.2~\mu\mathrm{m}$ | $7.5 - 25 \ \mu { m m}$ |

| Height        | $40~\mu\mathrm{m}$  | $5-10~\mu\mathrm{m}$    |

| Minimum pitch | $10~\mu\mathrm{m}$  | $40~\mu\mathrm{m}$      |

FIGURE 1.3: Typical TSV and micro-bump dimensions.

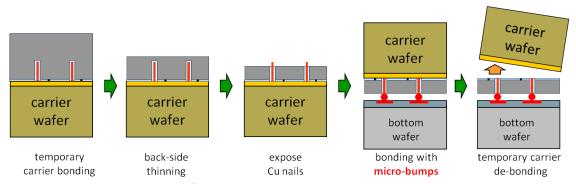

Wafer thinning and bonding processes are shown in Figure 1.5. The silicon substrate is temporarily bonded with the front-side to a carrier wafer and the back-side is thinned down. The exposed TSVs on the back-side are bonded to the front-side of the bottom wafer by means of micro-bumps. Finally, the carrier wafer is removed.

TSV can be processed at different stages of the CMOS manufacturing flow. There are three common approaches [11]:

- Via-first. In this case, TSVs are processed before the transistors (front end of line, FOEL).

- *Via-middle*. In this case, TSVs are fabricated after FOEL but prior to metal layers (back end of line, BOEL).

- Via-last. In this case, TSVs are processed after BOEL.

Typically, via-first and via-middle TSVs are smaller and denser than via-last TSVs. A major drawback of the via-first approach is that the TSVs are exposed to high

FIGURE 1.4: TSV fabrication steps in IMEC's process.

FIGURE 1.5: Wafer thinning and stacking steps in imec process.

temperatures during annealing, which is done at FOEL. Therefore, copper cannot be used as TSV filling material in the via-first approach due to material diffusion as well as thermo-mechanical stress, which results from different thermal expansion coefficients of copper and the silicon substrate.

Dies can be stacked in three different ways: Wafer-to-Wafer (W2W), Die-to-Wafer (D2W), and Die-to-Die (D2D). W2W approach has the advantage that it does not require pick-and-place operations for single dies and hance can be done faster than D2W and D2D. However, in the W2W approach, it is difficult to match Known Good Die of the wafers being stacked; therefore, the compound yield of W2W scheme is typically lower than those of D2W and D2D.

A number of 3D IC architectures have been considered for volume manufacturing.

• Interposer-based 3D ICs, called "2.5D ICs", in which multiple active dies are placed next to each other on top of a passive silicon interposer base and interconnected through it. The active dies are bonded to the interposer by means

of micro-bumps. An example of a 2.5D ICs is depicted in Figure 1.6(a)), in which the interposer contains TSVs that provide connections to the external package pins. 2.5D ICs are attractive for high-performance compute and communication applications, as they offer high-bandwidth interconnect between the various active dies and good cooling opportunities [12, 13].

- "True" 3D ICs, with multiple dies stacked in a single tower, as shown in Figure 1.6(b). This type of 3D ICs is attractive for applications, where cooling is not an issue but the form factor needs to be optimized, for instance, for hand-held mobile devices.

- Combination of 2.5D ICs and 3D ICs, where multiple towers of active dies are mounted next to each other on a silicon interposer, as illustrated in Figure 1.6(c).

FIGURE 1.6: Various vertical die stack architectures: (a) 2.5D IC, (b) 3D IC, and (c) 5.5D IC [14].

The main advantages of 3D stacking is the possibility of integration heterogeneous dies and high-bandwidth interconnects. It is therefore no surprise that memory-on-logic stacks are among the first 3D IC applications appearing on the market [15, 16]. Recently, JEDEC, a microelectronics industry association, has released a new standard for Wide-I/O DRAMs for stacking with TSVs (JESD-229) [17]. This standard defines the mechanical and electrical logic-memory interface, allowing for 512-bit data signals. The standard also specifies boundary-scan-like test structures for DRAM

FIGURE 1.7: 2D (a) and 3D (b) test flows [18].

dies, enabling interconnect test for TSV-based connections between the logic and the memory dies [14].

### 1.2 3D Test Flow

Test flows for 3D ICs are distinctly different from a conventional test flow. Figure 1.7 shows a comparison between the two flows. A conventional (2D) IC is typically tested twice: (a) after wafer fabrication (wafer-level test) and after packaging (final test). A wafer-level test ensures that most of the defective dies are screened out before packaging in order to save cost, and a final test ensures the outgoing product quality.

A 3D-IC test flow has several potential test insertions [18].

#### • Pre-bond test

All dies should be tested prior to bonding to ensure that only known good dies (KGD) are stacked. This test targets the internal logic as well as TSVs, which are processed before die bonding.

### • Post-bond test

Partial and full stacks can be tested for defects that may have been induced

during the stacking process, which include defects in the TSV-based inter-die connections, as defects in the internal die areas surrounding TSVs.

#### • Final test

As in traditional ICs, the entire 3D IC is thoroughly re-tested after packaging in order to ensure the outgoing product quality.

## 1.3 3D DfT Architectures and Optimization

In a typical 3D stack, only one die holds all external connections and the other dies communicate with the outside world through that die. Therefore, in order to provide test data to all dies in the stack, a 3D DfT architecture is required that can transport test data from external test pins through the stack to the die under test and back.

Marinissen et al. have proposed a 3D test architecture based on die-level wrappers for logic-on-logic 3D stacks [19], which has been extended to support memory-on-logic stacks [14]. Figure 1.8 shows a schematic view of the architecture. The die-level wrappers are based on embedded-core wrappers in IEEE Std 1500 [20] and allow for modular test of die-internal structures (INTEST mode), as well as inter-die connections (EXTEST mode). The architecture provides a serial test-access mechanism (TAM) and a parallel TAM for each die. The serial TAM is connected to an IEEE 1149.1 interface in Die 1 [21], and the parallel TAM is multiplexed onto functional I/Os in Die 1. Each die wrapper contains a wrapper instruction register (WIR) that configures the wrapper in one of three test modes: (a) INTEST, in order to test the die logic using internal scan chains, (b) EXTEST, in order to test the TSV-based connections using the wrapper boundary register, and (c) BYPASS, in order to bypass the die.

Dies in a 3D stack may contain embedded cores that need to be tested as separate entities. Typically, the width of the parallel TAM is not sufficient to provide test access to all cores of the stack simultaneously; therefore, only certain cores can be

FIGURE 1.8: Schematic view of the logic-on-logic 3D DfT architecture [14].

tested in parallel, depending on the design of the TAMs. In order to optimize the total test time of a 3D IC, optimization of the test architecture and test scheduling is necessary.

Optimization of 2D system-on-chip (SoC) test architectures has been explored well in the past [22, 23, 24, 25, 26]. A general problem of TAM optimization can be formulated as follows. Given the total TAM width, as well as the parameters for each core in the SoC, including scan-chain information and the test-pattern information, determine an optimal assignment of cores to the global TAM such that the test time is minimum.

Iyengar et al. [27] have proposed a framework for co-optimization of TAM design and wrappers. This work assumes a *test-bus* model for the TAMs, where cores can be tested independently from each other; however, cores sharing a TAM are tested sequentially. The paper presents an efficient algorithm to construct wrappers that

reduce the core-testing time, as well as mathematical models for TAM optimization that use the calculated core-testing times as input parameters. The TAM optimization for small SoCs is solved using integer linear programming (ILP). For large SoCs, the authors have proposed an efficient heuristic based on rectangle stacking [28]. Each core can be represented as a rectangle, where the width is the TAM width of the core, and the length is the test time, as shown in Figure 1.9(a). The objective is to pack the rectangles without overlapping in a bin, the width of which equals the maximum TAM width, such that the length of the bin, i.e., the SoC testing time, is minimized. Once an optimal packing is obtained, it can be mapped back to the corresponding core-TAM assignment, as shown in Figure 1.9(b).

FIGURE 1.9: An illustration of (a) rectangle packing and (b) the corresponding TAM design [28].

The authors of [29] have addressed the issue of robustness of test architectures against variations in input parameters and proposed to solve the problem of robust optimization by using a daisy-chain architecture, matching the width of the corelevel TAM to that of the system-level TAM, and testing one core at a time. The requirement of reconfigurable core wrappers is, however, difficult to meet in practice because of complex scan-chain routing. In addition, some cores do not benefit from extra TAM width, wasting the bandwidth that could be used for testing other cores

in parallel.

Recent publications have been focusing on optimization of test architectures for 3D ICs [30, 31, 32]. Noia et al. [32] have proposed a framework for test-architecture optimization for 3D stacked ICs with hard, soft, and firm dies. In a hard die, the test architecture is fixed and known in advance. Firm dies allow for serial/parallel conversion in order to adjust the TAM width. In the case of soft dies, the test architecture is to be designed, which offers extra degrees of freedom. In addition, two different 3D test architectures are considered: (a) serial and (b) parallel test architectures, as shown in Figure 1.10. In a serial architecture, all dies share TAM wires and hence only one die can be tested at a time. In a parallel test architecture, certain dies have a dedicated TAM and can be tested independently of other dies, for instance, Die 1 in Figure 1.10(b). This can reduce the total test time but typically requires a wider stack-level TAM. The authors formulate a mathematical model of the problem, using the number of available test pins and the number of dedicated test TSVs as constraints, and solve the problem using ILP.

FIGURE 1.10: An example of a 3D test architecture with (a) serial TAM and (b) parallel test architecture [32].

## 1.4 Defects due to TSV Manufacturing

As in any microelectronics, the manufacturing process of 3D ICs is defect-prone and hence 3D ICs need to be tested to ensure the outgoing product quality. Since this manufacturing process includes steps that are also used for conventional (2D) chips, the same defects may occur in both 2D and 3D products. A defect is a physical imperfection in the processed wafer, for instance an open in interconnects, a short between interconnects, missing transistor, incorrect doping level.

Due to TSV manufacturing and bonding steps, 3D ICs can potentially have a number of new defect types [6]. TSV-related defects include:

- Voids in TSVs

- Pinch-off of the TSV

- Oxide defects, e.g. pinholes

- Thermo-mechanical stress induced defects

- Voids and cracks in micro-bumps

Voids in TSVs, as shown in Figure 1.11(a), can result from Cu electroplating or insufficient wetting of the vias in the plating solution [33]. Another defect due to plating is *pinch-off* of the TSV, as depicted in Figure 1.11(b). These defects can increase the TSV resistance or even create an open circuit.

FIGURE 1.11: TSV plating defects: (a) voids, (b) pinch-off [33].

Oxide defects, such as pinholes, may occur along the TSV wall and create shorts between the TSV and the substrate [34].

Breakdown voltage reduction of the thermal oxide is caused by strong buried oxide (BOX) undercuts, an example of which is depicted in Figure 1.12(a) [35]. BOX undercuts result from TSV etching, post-etch cleaning, and insulator layer deposition. Figure 1.12(b) highlights the effect of a strong undercut: the electric field at the corner of the silicon-on-insulator is greatly increased. This degrades the breakdown voltage, which must be sufficiently high for high voltage applications (in the 200 V range) [35].

FIGURE 1.12: (a) BOX undercut, (b) Simulated electric field [35].

TSV reliability can be degraded by stress resulting from thermal expansion mismatch between Cu, Si, and SiO<sub>2</sub>. Resulting failures can be categorized in terms of the stress origin: (a) Cu-area, (b) Si-area, and (c) overall area, as shown in Figure 1.13 [36].

- (a) Although the strains in Cu are not high enough to cause failures in perfect TSV structures, the combination of these strains and manufacturing imperfections in TSVs might lead to failures, for instance *interfacial delamination*, *micro-bump* cracks, and cracks in TSVs [36, 37, 38, 39].

- (b) Local stress in Si can alter the carrier mobility of a MOS device, depending on its location relative to the TSVs [40]. This effect causes *timing variations* of

up to  $\pm 10\%$  for individual cells in the TSV proximity, which may increase the critical path delay. This affect the test quality for small-delay defect (SDD) test [41], as the SDD test relies on an accurate timing model of the circuit. Recently, a study has shown that the SDD-test quality can be significantly decreased if stress due to TSVs is not taken into account during test generation

(c) Global stress results in die warpage which, in turn, might lead to cracks in the micro-bumps, as shown in Figure 1.14 [36].

FIGURE 1.13: TSV stress types and their induced failures [36].

FIGURE 1.14: Crack in a micro-bump due to mechanical stress [36].

An important issue in 3D ICs is electromigration in micro-bumps, which are part of the TSV-based interconnects. Studies of micro-bump reliability report that *voids* and *cracks* can occur in the joints due to electromigration [42]. For example, Figure 1.15 shows such defects in a chip sample with an IMC–Sn–IMC (Intermetallic Compound) joint structure after 0.13A current stressing [42]. The resulting voids and cracks increased the resistance of this micro-bump by more than 20%.

FIGURE 1.15: Micro-bump failure after current stress test [42].

Many of the listed defects affect the reliability of 3D ICs, for instance, by creating shorts or increasing the interconnect resistance. The phenomena causing these defects have been studied and the underlying physics has been explained in the literature [43, 44]. The studies also propose new design and manufacturing techniques to avoid these defects, for instance

- Layout optimization for reduced mechanical stress [45],

- Layout optimization with respect to carrier mobility variations near TSVs [40],

- Void-free filling techniques [46].

The efficiency of these techniques has been experimentally verified but volume production data is still awaited. It is unlikely that the industry is going to reveal any significant data about their manufacturing processes or yield, hence testing remains relevant.

## 1.5 Pre-Bond TSV Test

Pre-bond TSV testing remains one of the major challenges in a 3D test flow due to the limited access to TSVs [47]. In the following paragraphs, we review several methods for pre-bond TSV test that have been proposed in the literature.

Noia and Chakrabarty proposed a method for TSV testing in which multiple TSVs are mechanically contacted by the same probe needle to measure TSV capacitance and resistance [48, 49]. This approach allows for the testing of multiple TSVs simultaneously at the expense of measurement resolution, significantly reducing the test time. Simulation results have demonstrated high measurement accuracy, even in the presence of process variations and probe contact variations. Despite its benefits, this method has several drawbacks. First, it places extra burden on the test equipment, such as custom and active probe cards. Second, the method requires multiple contacts on the back side of the thinned wafer, which can be difficult in practice. Finally, mechanical force on TSV tips and micro-bumps can result in damage to TSVs, leading to their degraded performance or even failure.

Chen et al. have proposed a methodology for detecting capacitive TSV faults [50]. In this method, a TSV is charged to a certain voltage level and then its charge is shared among a number of TSVs. After charge sharing, a sense amplifier measures the voltage of TSV, from which the TSV capacitance can be deduced. This method also allows for the detection of leakage faults. A major drawback of this approach is its susceptibility to process variations. In addition, this method requires analog structures on the die that are not part of typical standard cell libraries and need to be manually designed and optimized.

Pak et al. have developed a technique for TSV connectivity test using ring oscillators [51]. The key idea of this approach is to create on-chip oscillators from inverters and to use TSVs as capacitive loads, which are connected through MOSFET switches to the oscillators. The number of toggles of the oscillating signals is counted twice in a fixed time frame: once, when the switch of the corresponding TSV under test is "on", and once, when the switch is "off". If the difference in the count is zero, the TSV is considered as disconnected from the metal layers. However, the work in [51]

does not show whether this approach can be used to detect weak resistive-open faults and weak leakage faults in TSVs.

Huang et al. have developed a solution for detecting resistive open faults and leakage faults in TSVs using ring oscillators [52]. Their method is similar to the so-called "input sensitivity analysis", which was originally designed for post-bond TSV diagnosis using ring oscillators [53]. The disadvantage of the method in [52] is that it requires modification of functional TSV I/O cells that are carefully designed for performance and robustness.

Another method proposed by Huang et al. uses phase-locked loops (PLLs) for TSV leakage binning [54]. The key idea of this method is to measure the discharge time of a "floating" TSV. According to the simulation results, the method provides a high resolution even for very weak leakage below 1  $\mu$ A. However, it needs to be shown that the method is robust against random-process variations. In addition, this method cannot detect resistive-open faults and requires modification of the functional I/O circuitry driving the TSV.

Hao and McCluskey proposed very-low-voltage testing to detect resistive shorts and hot-carrier-induced degradation [55]. They have shown that the effects of these defects are increased at voltage levels lower than  $V_{\rm DD}$ ; this finding has been supported by analytical models and SPICE simulations [56, 57]. This prior work motivated us to consider using multiple voltage levels for pre-bond TSV test. Since multiple-voltage testing neither imposes limits on the test equipment nor requires extra on-chip DfT structures, it can be applied in practice without introducing additional hardware costs [58, 59]. Since pre-bond TSV test does not require long test sequences (scan data), test time does not grow significantly if multiple voltages are used.

## 1.6 Post-Silicon Debug Using Signal Tracing

Despite steady progress in pre-silicon verification methods and tools [60, 61, 62], first silicon is rarely bug-free. Silicon debug requires a relatively large engineering effort, accounting for a significant portion of the total time-to-market of the silicon product and this portion has been projected to grow [7, 8]. Several design-for-debug solutions have been proposed in the past to provide observability of a circuit's internal signals [63, 64, 7, 65]. Most of these methods are based either on scan dumps or signal tracing.

A scan dump is a snapshot of the circuit's state at a particular point of time [66, 67, 68]. It is obtained by freezing the clocks during execution of a functional test and scanning out the content of the scan flip-flops. Analysis of the obtained values can help to localize errors in the design. A major difficulty of this method is the implementation of a cycle-accurate, deterministic clock freeze in the module under test. In addition, scan dump is destructive, which requires a reset of the circuit and rerunning the test program in order to obtain another snapshot.

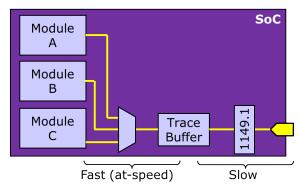

Signal tracing is a commonly-used technique for post-silicon debug. The main idea of this method is to localize bugs in digital logic by observing internal nodes of the circuit during test-program execution. The tapped signals can be captured either on-chip or off-chip [64]. Figure 1.16 shows a traditional architecture for signal tracing. Busses of internal signals from different modules feed through a multiplexer tree into an on-chip trace buffer. The multiplexer select a module, the signals of which will be captured into the trace buffer at-speed during a functional test. After the capturing of data is complete, the content of the trace buffer is transferred to an external debug equipment through a debug interface, for instance, an IEEE 1149.1 [21] interface. The major limitations of this approach are (a) the requirement of extra chip pins, and (b) low bandwidth of the external equipment, which limit the amount of signals that

FIGURE 1.16: Traditional signal-tracing architecture.

can be sampled at-speed. Alternatively, the traced data can be temporarily stored in on-chip trace buffers that are read after program execution. Due to the limited size of the trace buffers, only a few signals can be observed over a relatively short period of time, which is typically a fraction of the total run time of a test program.

In order to overcome these limitations, a number of innovative methods have been proposed in the past. In [69], the authors reconstruct the values of more signals than actually traced, virtually increasing the number of signals observed. The authors of [70] propose a method for selection of signals for tracing that are most susceptible to possible errors. In [71], several signal-selection methods have been proposed as well as a metric described to quantify the observability of each technique. Another type of enhancement of signal tracing incorporates compression before the storage of trace data into a trace buffer [72, 73]. These methods can be effectively combined with other methods that increase the observation window.

The authors of [74] propose an iterative debug scheme. In the first iteration, time intervals in which erroneous data is captured are identified using lossy compression. In the following iterations, the method zooms into these intervals for a better resolution. The disadvantage of this method is the requirement to run multiple iterative debug sessions with intermediate post-processing steps.

In [75], the authors use a three-pass debug methodology in order to expand the

observation window. In the first pass, the error rate is calculated using parity bits. In the second pass, suspect clock cycles are determined. In the third pass, the erroneous data is captured during suspect clock cycles. The price for an expanded observation window is extra debug passes and the need for post-processing of captured data in between these passes.

In [76], a generic debug infrastructure is proposed to gather trace information from different modules through a "Trace Memory Controller" and redirect it to different targets, for instance, a dedicated debug port, SRAM, or system memory. The solution described in [76] does not cover trace-data compression or selective trace-data storage and leaves these implementation details up to the user.

## TSV Stress-Aware ATPG

Despite the numerous benefits offered by 3D integration, test challenges for 3D ICs must be addressed before volume manufacturing and defect screening can be feasible [4, 5]. One of the serious problems confronting 3D integration is that of thermomechanical stress due to TSV processing. The thermal expansion coefficient of copper, a common TSV fill material, is significantly higher than that of silicon:  $17 \times 10^{-6}/K$  versus  $3 \times 10^{-6}/K$  [77]. Due to this mismatch, TSVs are likely to cause residual stress in the silicon during fabrication and thermal cycling. One of the effects of thermal stress is mobility variation in MOS devices in the proximity of TSVs. These variations lead to a change in the timing profile of the circuit [40, 45], which affects delay-fault testing.

Recent work on 3D IC testing has targeted solutions to overcome problems related to test access in 3D ICs and TSV testing. We focus here on post-bond delay-fault testing of internal die logic in 3D ICs, a problem that has received much less attention in the literature. In this chapter, we study the impact of timing variations due to TSV stress on the quality of test patterns generated to screen small-delay defects (SDDs). In particular, we focus on the following problems: (i) How severe is the impact of

TSV-induced stress on the effectiveness of patterns for SDDs and test escapes? (ii) To what extent can test escapes be reduced by including analytical TSV stress models as a preprocessing step in the ATPG flow? (iii) What is the impact of TSV stress-aware ATPG on pattern count and how does the process yield affect test escapes due to TSV-induced stress?

We assume that SDD testing is done after stacking, such that the clock tree for functional operation is available for at-speed capture cycles. We show that the use of TSV stress-oblivious circuit models results in a significantly increased escape rate of faulty chips. The level of this increase depends on the yield of the fabrication process; we conclude that accurate modeling of TSV stress is more important for processes with lower yields.

The impact of TSV stress on pattern effectiveness is quantified using the statistical delay quality level (SDQL) metric [78]. This is a key metric in our approach, since the SDQL of a chip correlates with the expected test escape rate due to small-delay defects. We also show that the test escape can be reduced considerably by incorporating TSV stress in cell timing libraries and using these libraries with a commercial timing-aware ATPG tool. Therefore, any detrimental impact of TSV stress on pattern effectiveness and test quality can be overcome by using stress-aware models for test generation. We also show that TSV stress-aware testing leads to negligible increase, if any, in pattern count.

The remainder of this chapter is organized as follows. In Section 2.1, we give an overview of small-delay testing, and mobility variations due to TSV stress. Section 2.2 describes our methodology to create TSV stress-aware test patterns using conventional ATPG tools. In Section 2.3, we present simulation results obtained with 3D logic-on-logic benchmarks. Finally, Section 2.4 concludes this chapter.

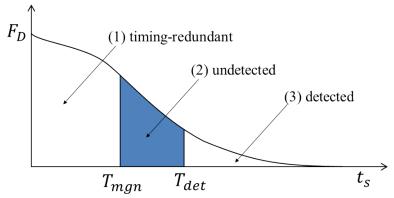

FIGURE 2.1: Delay distribution  $F_D(t_s)$ .

### 2.1 Related Prior Work

### 2.1.1 SDD Testing and SDQL

Due to continuous miniaturization, integrated circuits have become more susceptible to process variations and resistive defects. As a result, SDDs have become more prevalent [41]. Despite the fact that their size might be small compared to the clock period, SDDs can cause errors if the length of a path affected by them exceeds the clock period. Therefore, effective and low-cost screening for SDDs is important to ensure product quality. Several methods have been proposed in the literature to test for SDDs [79, 41, 80].

To quantify the effect of TSV stress on the quality of a delay-fault test, we use the statistical delay quality level (SDQL) proposed in [78]. With this metric, we can quantitatively estimate the test escape rate due to delay defects and evaluate the increase in test quality if TSV stress-aware circuit models are used for ATPG.

SDQL computation is based on the assumption that delay defects follow a probability distribution  $F_D(t_s)$ , where  $t_s$  is the size of the defect, and that the defects are equally distributed over all sites. This distribution is dependent on the manufacturing process and can be obtained by analyzing manufacturing data [81].

Figure 2.1 shows an example of a delay-defect distribution function. For each

delay fault, this function is divided intro three regions by  $T_{mgn}$  and  $T_{det}$ , which are defined as follows. The time margin  $T_{mgn}$  for a fault is the slack on the longest of the paths that can propagate this fault:

$$T_{mgn} = T_{ck,f} - \max_{i}(T_i), \tag{2.1}$$

where  $T_{ck,f}$  is the functional clock period and  $T_i$  are lengths of the sensitizable paths. A fault can only be detected if its size  $T_{det}$  exceeds the slack of the path sensitized by a particular test:

$$T_{det} = T_{ck.t} - T_{sens}, (2.2)$$

where  $T_{ck,t}$  is the test clock period and  $T_{sens}$  is the length of the sensitized path. As Figure 2.1 shows, delay faults can be put into three categories dependent on their size  $t_s$ : (1) timing-redundant, (2) undetected, and (3) detected. The area below the curve in the undetected region represents the probability of the fault being undetected and escaping the test. The summation of these probabilities for all faults is called SDQL [78]:

$$SDQL = \sum_{k}^{2N} \int_{T_{mgn}}^{T_{det}} F_D(t_s) dt_s, \qquad (2.3)$$

We use the SDQL metric to show that the use of TSV stress-oblivious circuit models may lead to a significantly increased escape rate for 3D ICs.

### 2.1.2 Mobility Variation due to TSV Stress

Due to a mismatch in thermal expansion coefficients of copper and silicon, TSVs cause thermo-mechanical stress in the surrounding silicon. This stress affects not only the mechanical device reliability but also material properties such as carrier mobility [38], which results in timing variations of the devices. Recent studies have reported up to  $\pm 10\%$  variations for individual cells [40].

Since a correct timing model of the circuit is crucial for delay testing, we need an efficient methodology to take TSV stress into consideration in the ATPG flow.

In the literature, we can find a simple closed form formula for the thermo-mechanical stress caused by a TSV, known as the Lamé stress solution [40]. However, this model is 2D in its nature, capturing only the information in the x and y directions on the wafer surface, and it fails to capture the true 3D nature of the TSV stress field near the wafer surface. Since there is no simple formula for the 3D stress field available in the literature, we can apply the methodology outlined in [45] for full chip analysis. The main idea of this methodology is to perform a finite-element analysis (FEA) for a single TSV and use linear superposition to estimate the total stress  $\sigma_{rr}$  due to multiple TSVs.

The resulting  $\sigma_{rr}$  serves as an input to compute the carrier mobility variation, which can be expressed as a function of  $\sigma_{rr}$  and the device channel orientation  $\theta$  with respect to the TSV [40]:

$$\frac{\Delta\mu}{\mu}(\theta) = -\Pi \times \sigma_{rr} \times \alpha(\theta), \tag{2.4}$$

where  $\alpha(\theta)$  is the orientation factor as a function of the angle  $\theta$  between the channel orientation and the center of the TSV, and  $\Pi$  is the piezo-resistive coefficient at  $\theta = 0$ .  $\Pi$  can be extracted using the methodology described in [82].

The estimated carrier mobility change can be used to update the timing information of the devices around TSVs for a more accurate circuit model.

### 2.2 Methodology

Our approach consists of two major parts:

- 1. Generation of a TSV stress-aware circuit model;

- 2. Test pattern generation and simulation.

FIGURE 2.2: The TSV structure and three different KOZ sizes used in our studies.

The rest of this section describes the two steps in detail.

#### 2.2.1 TSV Stress-Aware Model Generation

The TSV structure considered in our simulations is shown in Figure 2.2. The TSV diameter, height, landing pad size, and liner thickness are assumed to be 5  $\mu$ m, 30  $\mu$ m, 7  $\mu$ m, and 125 nm, respectively. The TSV is assumed to be made of copper, and the liner of SiO<sub>2</sub>. The material properties used in our simulations are: CTE (ppm/K) for Cu = 17, Si = 2.3, SiO<sub>2</sub> = 0.5; Youngs modulus (GPa) for Cu = 110, Si = 130, SiO<sub>2</sub> = 71. We also consider three different keep-out-zone (KOZ) sizes of 1.7  $\mu$ m, 2.4  $\mu$ m and 3.1  $\mu$ m as shown. This corresponds to 6, 7 and 8 standard cell rows in the Nangate 45 nm technology library. A larger KOZ will mean less impact of TSV stress on the gates. However, increasing the KOZ will affect other design metrics such as area and wirelength.

FIGURE 2.3: The design flow used to obtain TSV-stress-aware timing

The overall design flow used to obtain stress aware timing is shown in Figure 2.3. We first start with creating a timing library with different mobility values. We start with the nominal PMOS and NMOS mobility, and characterize all the cells in increments of 4%. The next step is stress calculation, and this is performed as outlined in [45]. We first perform FEA simulation of the stress generated by a single TSV using the FEA software ABAQUS [83]. At any given point in the chip, the stress can be represented by its nine-component stress-tensor as follows:

$$\sigma = \sigma_{ij} = \begin{bmatrix} \sigma_{11} & \sigma_{12} & \sigma_{13} \\ \sigma_{21} & \sigma_{22} & \sigma_{23} \\ \sigma_{31} & \sigma_{32} & \sigma_{33} \end{bmatrix}$$

The first index i indicates that the stress acts on a plane normal to the i axis, and the second index j denotes the direction in which the stress acts. In cylindrical coordinates, the three indices 1, 2, and 3 represent r,  $\theta$ , and z respectively. Since the stress of a single TSV is radially symmetric, we only need to store the stress tensors

along one arbitrary radial line. The steps outlined so far only need to be performed once and the results can be used for any design.

For any given design, we need to perform full-chip stress analysis. For computation of stress due to multiple TSVs, we use linear superposition. The stress at each point in the chip is simply the vector sum of the stress caused by all TSVs at that point. A vector sum of the stress components is performed by transforming the cylindrical stress tensor into its Cartesian form, adding the components individually along the x, y and z axis, and then transforming it back to cylindrical coordinates.

With the stress tensor at each point in the design, the corresponding change in mobility of electrons (NMOS) and holes (PMOS) can be computed using the measured piezoresistive coefficients given in [82], assuming (100) silicon. With this approach, we obtain the change in mobility due to TSV stress for each cell in the design.

The appropriate timing library can then be picked from the pre-characterized set of timing libraries. All the libraries, netlists, and parasitics are fed into Synopsys Primetime to get TSV-stress-aware timing results.

#### 2.2.2 TSV-Stress-Aware ATPG

Delay-fault ATPG relies on correct circuit timing information, which is used to generate the path profile in order to target the longest sensitizable paths for each fault. In 3D ICs, timing variations in devices due to TSV stress might occur, resulting in a change of the timing profile of the circuit. The slacks for paths that include the the affected devices can increase or decrease dependent on the device type (PMOS or NMOS) and on the location relative to the TSVs, changing the longest sensitizable path for certain delay faults. If these changes are not taken into account, the ATPG tool might propagate faults through paths that are shorter than the actual longest path. This will invariably result in a lower test quality, since delays of a particular size will not be detected.

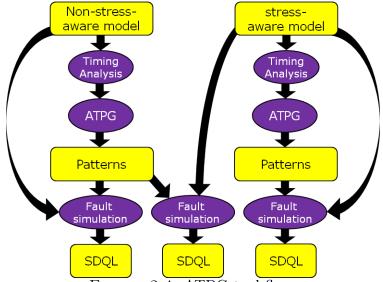

To evaluate the impact of the TSV-induced stress on the test quality, we have developed a tool flow using conventional timing analysis and ATPG tools: Synopsys PrimeTime and TetraMax, respectively. Figure 2.4 gives an overview of the flow. As input, we use the original (non-stress-aware, NSA) models and the modified (stress-aware, SA) models. First, we perform timing analysis with PrimeTime to extract the slack data. Next, we generate two delay test pattern sets with TetraMax: one using the NSA and the other using SA models. Finally, we perform fault simulation and compute SDQL with TetraMax using the following combinations.

- 1. The NSA pattern set on the NSA model. The results of this simulation show the test quality that is expected if TSV stress is not present.

- 2. The NSA pattern set on the SA model. The simulated SDQL numbers indicate the actual test quality of the NSA pattern set.

- 3. The SA pattern set on the SA model. The simulated SDQL numbers indicate the actual test quality of the SA pattern set, i.e., under realistic conditions of TSV stress.

### 2.3 Case Study

### 2.3.1 Test Vehicles

We use three benchmarks taken from the open cores benchmark suite [84]. They are synthesized and scan-inserted using the Nangate open cell library, at the 45 nm node. Table 2.1 gives an overview of the design data, including gate, scan flip-flop and TSV count. We partition the netlist and create three different stacks for each core: two-die, three-die, and four-die stacks. For each die, we use a 3D force-directed placer to place the gates [85]. This placer places TSVs in a regular fashion, and assigns nets to TSVs using a 3D Minimum Spanning Tree approach.

FIGURE 2.4: ATPG tool flow.

Table 2.1: Design statistics for the benchmarks.

| Benchmark    | # Gates | # Scan FFs | 3D Impl. | # TSVs |

|--------------|---------|------------|----------|--------|

|              | 26,251  |            | 2-die    | 419    |

| des_perf     |         | 1,984      | 3-die    | 884    |

|              |         |            | 4-die    | 1322   |

|              | 156,624 | 20,480     | 2-die    | 589    |

| cf_rca_16    |         |            | 3-die    | 676    |

|              |         |            | 4-die    | 953    |

|              | 299,273 | 75,723     | 2-die    | 2193   |

| cf_fft_256_8 |         |            | 3-die    | 4717   |

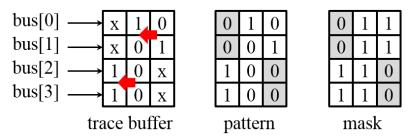

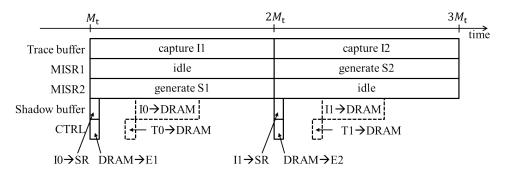

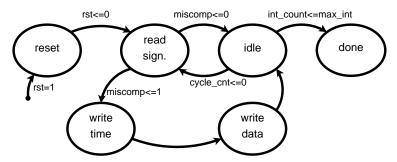

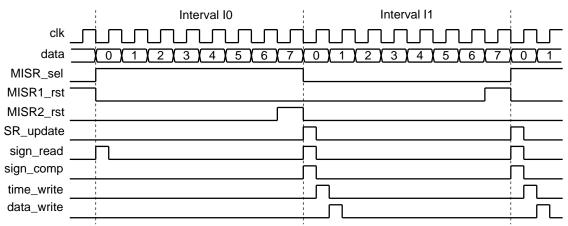

|              |         |            | 4-die    | 5843   |