# A Two-Level Modeling Approach to Analog Circuit Performance Macromodeling

Mengmeng Ding, Ranga Vemuri

## ▶ To cite this version:

Mengmeng Ding, Ranga Vemuri. A Two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A Two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A two-Level Modeling Approach to Analog Circuit Performance Macromodeling. EDAA - European design and Automation Association. DATE'05, Mar 2005, Munich, Germany. 2, pp.1088-1089, 2005. <a href="https://www.enaloy.org">https://www.enaloy.org</a> (A two-Level Modeling Approach to Analog Circuit Performance Approach to A

## HAL Id: hal-00181275 https://hal.archives-ouvertes.fr/hal-00181275

Submitted on 23 Oct 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### A Two-Level Modeling Approach to Analog Circuit Performance Macromodeling

Mengmeng Ding and Ranga Vemuri Digital Design Environments Lab University of Cincinnati, Cincinnati, OH, 45220-0030, USA {dingm, ranga}@ececs.uc.edu

#### Abstract

In this paper, we present a two-level modeling approach to performance macromodeling based on radial basis function Support Vector Machine (SVM). The two-level model consists of a feasibility model and a set of performance models. The feasibility model identifies the feasible designs that satisfy the design constraints. The performance macromodel is valid for feasible designs. We formulate the feasibility macromodeling problem as a classification problem and the performance macromodeling as a regression problem and apply SVM algorithm to build the classifier and regressors correspondingly. Our experiment shows that performance macromodels for feasible designs are much more accurate, faster to train and evaluate than those without functional or performance constraints considered.

#### 1. Introduction

Performance macromodels are mathematical models that relate the controllable design parameters and performance parameters of an analog circuit. Frequently as an alternative to a circuit level simulator for performance parameter acquisition, performance macromodels take much less time to evaluate than that needed by its counterpart. Often a certain analog circuit topology is configured with different design parameters in various applications. This property of an analog circuit topology makes its corresponding performance macromodels reusable for various applications.

A popular approach to performance macromodeling is using regression based techniques, which often use samples of performance parameters obtained from simulation to fit a regressor. This type of technique is challenged by the high nonlinearity relationship between design variables and performance parameters. S. Zazalaand, J. Eckmuller and H. Grab [4] have shown that by constraining the circuit in the *feasible design space*, one can build performance macromodels of higher accuracy. Feasible design space is a multidimensional space determined by certain design constraints. In this paper, we present a similar two-level modeling approach. The two-level model is composed of a feasibility model and a set of performance models.

In contrast to [4], we will construct a feasibility model of much higher accuracy than [4] by formulating the feasibility modeling problem as a two class *classification* problem and apply state of the art classification technique, radial basis function Support Vector Machine(SVM) to build the classifier. Performance models in the feasible design space are then constructed by fitting SVM regressor.

#### 2. Problem formulation

As mentioned in Section 1, feasible design space is a multidimensional space determined by certain design constraints. Given a circuit topology, we can pose three types of constraints: Geometry constraints on the design parameters, primarily device sizes and bias voltages and currents; Functional constraints that insure the functional correctness of the given circuit topology and Performance constraints on the performance measurements depending on the applications. Geometry constraints define the initial design space, usually a hypercube. Feasible design space I is the subspace of the initial design space, in which every design configuration satisfies all the design constraints. While performance constraints have never been used in performance macromodeling, we are enabled to do so by formulating the feasibility modeling problem as a classification problem and thus to handle arbitrary constraints.

Since functional and performance constraints are not directly posed on the design variables, *I* is not in an analytic form. We thus define a feasibility function y(x) whose output only takes two values  $\{+1, -1\}$  depending on whether  $x \in I$ .

$$y(x) = \begin{cases} +1 & \text{if } x \in I \\ -1 & \text{if } x \notin I \end{cases}$$

(1)

To build performance macromodels, we use Vapnik [3] proposed radial basis function SVM as our regressor. The original SVM regressor uses a  $\epsilon$ -insensitive loss function

<sup>0</sup> This work was supported in part by the Defense Advanced Research Projects Agency and the Sensors Directorate of the Air Force Research Laboratory, U.S. Air Force, Wright-Patterson AFB, OH, under Contract F33615-01-C-1977, the Dayton Area Graduate Studies Institution (DAGSI) under the DAGSI/AFRL Research Program Project SN-UC-01-08, and the National Science Foundation under award number CCF-0429717.

which is equivalent to minimizing the maximum error. Minimizing the maximum error is favored here because we want to make sure the models will perform well even in the worst case.

#### **3.** Experimental results

We apply the two-level modeling methodology to build feasbility model as well as performance macromodels for an OTA opamp, schematic shown in [2]. Our experiments are conducted on a Sun Blade 1000 machine and computational time is CPU time. The technology is AMI  $0.5\mu m$ CMOS process and supply voltage is 5V. The functional constraints insure all the transistors are on and in saturation region with some margin. We use a software called libsvm [1] to train and validate the SVM classifier and regressors.

|                       | $W_1 = W_2$                | [6µm, 200µm]         |

|-----------------------|----------------------------|----------------------|

|                       | $W_1 = W_2$<br>$W_3 = W_4$ | $[6\mu m, 200\mu m]$ |

|                       |                            |                      |

| Design variables      | $W_5 = W_6$                | [6µm, 200µm]         |

|                       | $W_7 = W_8$                | [6µm, 200µm]         |

|                       | $W_9 = W_{10}$             | [6µm, 200µm]         |

|                       | Ibias                      | [6µA, 100µA]         |

| Fix design parameters | $L_1, \cdots, L_{10}$      | 1.2µm                |

|                       | $C_c$                      | 1pF                  |

Table 1. Design variables of OTA op-amp

| I eriormanee constraints | That the set of the se |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Performance constraints  | Phase Margin $> 45^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | $V_{\rm os} \le 0.01 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                          | $V_{\rm ds} \ge V_{\rm gs} - V_{\rm th} + 0.1V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Functional constraints   | $V_{\rm gs} - V_{\rm th} \ge 0.1 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 2. Design constraints of OTA opamp

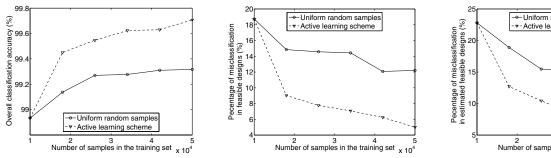

The feasible design space is only about 2.4% of the entire design space in this particular example. Using a set of uniform random samples to train the SVM, we can get a feasibility model of very high overall accuracy but approximate the feasible design space very poorly. We apply the active learning scheme proposed by [2] to solve the problem. The overall accuracy is always above 98.9% due to the powerful classification ability of the SVM. The active learning scheme can approximate the feasible design space much better with the same number of samples.

We construct and validate various performance macromodels using performance parameters of feasible designs. The training set has 7,000 samples and the validation set has 7,101 samples. In Table 3, RMS stands for root mean

squared error and MAX stands for the maximal absolute value of training or validation errors.

|          | Training set |       | Validation set |       | Teval  | Ttrain |

|----------|--------------|-------|----------------|-------|--------|--------|

|          | RMS          | MAX   | RMS            | MAX   | (s)    | (s)    |

| Gain(db) | 0.048        | 0.215 | 0.049          | 0.227 | 1.0e-4 | 27.9   |

| UGF(%)   | 0.55         | 1.27  | 0.57           | 2.41  | 1.2e-4 | 48.2   |

| PM(°)    | 0.062        | 0.357 | 0.080          | 0.917 | 6.6e-4 | 2929   |

#### Table 3. Statistics of performance macromodels of OTA opamp in feasible design space

We also generate performance models *without* the constraints in Table 2. As shown in Table 4, these models are less accurate, take much longer time to train and evaluate.

|                | Training set |       | Validation set |       | $T_{\rm eval}$ | T <sub>train</sub> |

|----------------|--------------|-------|----------------|-------|----------------|--------------------|

|                | RMS          | MAX   | RMS            | MAX   | (s)            |                    |

| Gain(db)       | 0.053        | 0.777 | 0.058          | 0.618 | 2.6e-4         | 101sec             |

| UGF(%)         | 0.87         | 5.09  | 0.94           | 6.81  | 9.8e-4         | 1.58hr             |

| $PM(^{\circ})$ | 0.166        | 1.79  | 0.35           | 4.17  | 3.0e-3         | 5.20hr             |

Table 4. Statistics of performance macromodels of OTA opamp without feasibility constraints

#### 4. Conclusion

This paper presents a two-level modeling approach which consists a classifier as a feasibility model and a set of regressors as performance models. Experimental results show that it is an efficient approach to performance macromodeling.

#### References

- [1] C.-C. Chang and C.-J. Lin. LIBSVM: a library for support vector machines, 2001. Software available at http://www.csie.ntu.edu.tw/~cjlin/libsvm.

- [2] M. Ding and R. Vemuri. An active learning scheme using support vector machines for analog circuit feasibility classification. In Proceedings of the 18th international conference on VLSI design, 2005, to be published.

- [3] V. Vapnik. The nature of statistical learning theory. Springer, New York, 1995.

- [4] S. Zizala, J. Eckmueller, and H. Grab. Fast calculation of analog circuits' feasibility regions by low level functional measures. In IEEE International Conference on Electronics, Circuits and Systems, pages 85-88, 1998.