# SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

# INFRA-2011-2.3.5 – Second Implementation Phase of the European High Performance Computing (HPC) service PRACE

## PRACE-2IP

# **PRACE Second Implementation Phase Project**

**Grant Agreement Number: RI-283493**

# D5.2 Best Practices for HPC Procurement and Infrastructure

#### **Final**

Version: 1.0

Author(s): Norbert Meyer, Marcin Lawenda, PSNC

Date: 23.08.2013

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-283493                                                               |                               |  |  |

|---------------|-----------------------------------------------------------------------------------------|-------------------------------|--|--|

|               | Project Title: PRACE Second Implementation Phase Project                                |                               |  |  |

|               | Project Web Site: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a> |                               |  |  |

|               | Deliverable ID: < D5.2>                                                                 |                               |  |  |

|               | Deliverable Nature: Report                                                              |                               |  |  |

|               | <b>Deliverable Level:</b>                                                               | Contractual Date of Delivery: |  |  |

|               | PU                                                                                      | 31/08/2013                    |  |  |

|               |                                                                                         | Actual Date of Delivery:      |  |  |

|               |                                                                                         | 31/08/2013                    |  |  |

|               | EC Project Officer: Leonardo Flores Añover                                              |                               |  |  |

# **Document Control Sheet**

|            | Title: Best Practices for                 | HPC Procurement and Infrastructure  |  |  |

|------------|-------------------------------------------|-------------------------------------|--|--|

| Document   | ID: D5.2                                  |                                     |  |  |

|            | <b>Version:</b> <1.0 >                    | Status: Final                       |  |  |

|            | Available at: http://www.prace-project.eu |                                     |  |  |

|            | <b>Software Tool:</b> Microso             | oft Word 2010                       |  |  |

|            | File(s): D5.2.docx                        |                                     |  |  |

|            |                                           | Norbert Meyer, Marcin Lawenda, PSNC |  |  |

| Authorship | <b>Contributors:</b>                      | Guillermo Aguirre de Carcer, BSC    |  |  |

|            |                                           | Jean-Philippe Nominé, CEA           |  |  |

|            |                                           | François Robin, CEA                 |  |  |

|            |                                           | Mickael Amiet, CEA                  |  |  |

|            |                                           | Marco Sbrighi, CINECA               |  |  |

|            |                                           | Ioannis Liabotis, GRNET             |  |  |

|            |                                           | George Karagiannopoulos, GRNET      |  |  |

|            |                                           | Vangelis Floros, GRNET              |  |  |

|            |                                           | Antonis Zissimos, GRNET             |  |  |

|            |                                           | Vladimir Slavnic, IPB               |  |  |

|            |                                           | Georgi Prangov, NCSA                |  |  |

|            |                                           | Radek Januszewski, PSNC             |  |  |

|            |                                           | Lukas Dutka, Cyfronet,              |  |  |

|            |                                           | Mscislaw Nakonieczny, TASK          |  |  |

|            |                                           | Walter Lioen, SURFsara              |  |  |

|            |                                           | Gert Svensson, SNIC/KTH             |  |  |

|            |                                           | Andreas Johansson, SNIC/LiU         |  |  |

|            |                                           | Todor Gurov, NCSA                   |  |  |

|            |                                           | Emanuil Atanassov, NCSA             |  |  |

|            | Reviewed by:                              | Thomas Eickermann, PRACE PMO&FZJ    |  |  |

|            |                                           | Thomas Bönisch, HLRS                |  |  |

|            | Approved by:                              | MB/TB                               |  |  |

# **Document Status Sheet**

| Version | Date        | Status        | Comments                                                                                                                 |

|---------|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| 0.1     | 12/06/2013  | Draft         | First outline                                                                                                            |

| 0.2     | 28/06/2013  | Draft         | Added contributions:<br>recommendations from<br>the White Paper, updated<br>contributions from HPC<br>workshop in Lugano |

| 0.3     | 12/07/2013  | Draft         | Added contributions: security, introduction, summary                                                                     |

| 0.4     | 25/07/2013  | Draft         | Added contributions: cooling, monitoring, energy efficiency, updated contributions: security                             |

| 0.5     | 31/07/2013  | Draft         | Added: best practices in air cooling, exascalability sections, extended many subsections, text corrections               |

| 0.62    | 4-5/08/2013 | Draft         | Updated exascalability chapter, cooling, summary, general updates and compilation                                        |

| 0.7     |             | Draft         | Proofread                                                                                                                |

| 0.8     |             | Draft         | For internal review                                                                                                      |

| 1.0     | 26/08/2013  | Final version | Updates and corrections done after PRACE internal review process                                                         |

# **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure, Petascale, Exascale, security,     |  |

|------------------|-------------------------------------------------------------------------|--|

|                  | data centre, cooling, electricity, monitoring, big data, interconnects, |  |

|                  | Top500, Green500                                                        |  |

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° RI-283493. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2013 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-283493 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| rkt  | JIEC | I AND DE | ELIVERABLE INFORMATION SHEET                                 |            |

|------|------|----------|--------------------------------------------------------------|------------|

| DO   | сим  | ENT CON  | ITROL SHEET                                                  |            |

| DO   | сим  | ENT STA  | TUS SHEET                                                    |            |

| DO   | CUM  | ENT KEY  | WORDS                                                        |            |

|      |      |          | NTS                                                          |            |

|      |      |          |                                                              |            |

|      |      |          |                                                              |            |

|      |      |          |                                                              |            |

| REF  | ERE  | NCES ANI | D APPLICABLE DOCUMENTS                                       | VII        |

| LIST | T OF | ACRONY   | MS AND ABBREVIATIONS                                         | X          |

| EXE  | CUT  | IVE SUMI | MARY                                                         | 1          |

| 1    | IN   | TRODUC   | TION                                                         | 3          |

| 2    |      |          | FER FACILITIES ECOSYSTEM                                     |            |

|      |      |          |                                                              |            |

| 2    | 2.1  |          | v of HPC facitilities in Europe – Tier-0 sites               |            |

|      |      | 2.1.1    | CEA (France)                                                 |            |

|      |      | 2.1.2    | FZJ (Germany)                                                |            |

|      |      | 2.1.3    | LRZ (Germany)                                                | 6          |

|      |      | 2.1.4    | CINECA (Italy)                                               | 6          |

| 2    | 2.2  | OVERVIEV | V OF HPC FACILITIES PROJECTS IN EUROPE – TIER-1 SITES        | 7          |

|      |      | 2.2.1    | VSB-TUO (Czech Republic)                                     | 7          |

|      |      | 2.2.2    | CINES (France)                                               |            |

|      |      | 2.2.3    | SURFsara (Netherlands)                                       | 8          |

|      |      | 2.2.4    | PSNC (Poland)                                                | 8          |

|      |      | 2.2.5    | CSCS (Switzerland)                                           |            |

|      |      | 2.2.6    | IPB (Serbia)                                                 |            |

|      |      | 2.2.7    | LiU (Sweden)                                                 |            |

|      |      | 2.2.8    | EPCC (UK)                                                    |            |

| :    | 2.3  | OVERVIEV | v of HPC facilities projects in Europe – Other sites         |            |

|      |      | 2.3.1    | TU-DRESDEN (Germany)                                         |            |

|      | 2.4  | -        | v of HPC facilities projects in US                           |            |

| •    | ۷.٦  | 2.4.1    | National Center for Atmospheric Research (NCAR)              |            |

|      |      | 2.4.2    | National Energy Research Scientific Computing Center (NERSC) |            |

|      |      | 2.4.2    | National Renewable Energy Laboratory (NREL)                  |            |

|      |      | 2.4.3    | ORNL                                                         |            |

|      | 2.5  |          | SUMMARY                                                      |            |

|      |      |          |                                                              |            |

| 3    | ΕIV  |          | FICIENCY IN HPC                                              |            |

| 3    | 3.1  | STATE OF | THE ART IN MONITORING AND ADMINISTRATION SYSTEMS             |            |

|      |      | 3.1.1    | IBM                                                          |            |

|      |      | 3.1.2    | SGI                                                          |            |

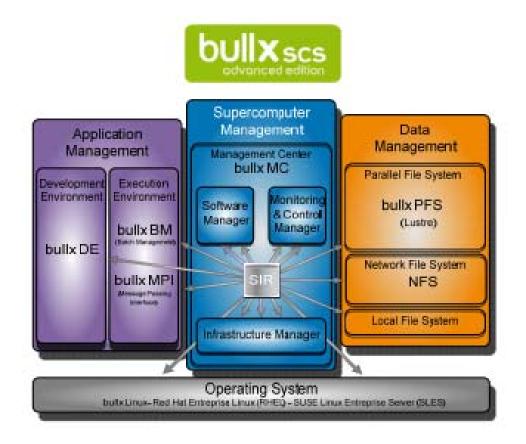

|      |      | 3.1.3    | BULL                                                         | 20         |

|      |      | 3.1.4    | BRIGHT                                                       | 22         |

|      |      | 3.1.5    | HP                                                           | <b>2</b> 3 |

|      |      | 3.1.6    | CRAY                                                         | 24         |

|      |      | 3.1.7    | Energy Efficient HPC Working Group Natalie Bates             | 24         |

|      |      | 3.1.8    | Ganglia                                                      | 25         |

|      |      | 3.1.9    | Pinguin computing - Scyld ClusterWare                        | 25         |

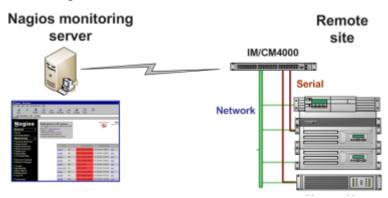

|      |      | 3.1.10   | Nagios                                                       |            |

| 3    | 3.2  | COOLING  | SYSTEMS AND THEIR EFFICIENCY                                 |            |

|      |      | 3.2.1    | Trends in HPC Cooling                                        |            |

|      |      | 3.2.2    | Direct Liquid Cooling                                        |            |

|      |      | 3.2.2.1  | Different Types of Direct Liquid Cooling                     |            |

|      |      |          | - · · · / F · - · - · - · - · - · - · · · · ·                |            |

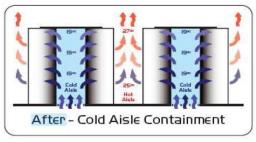

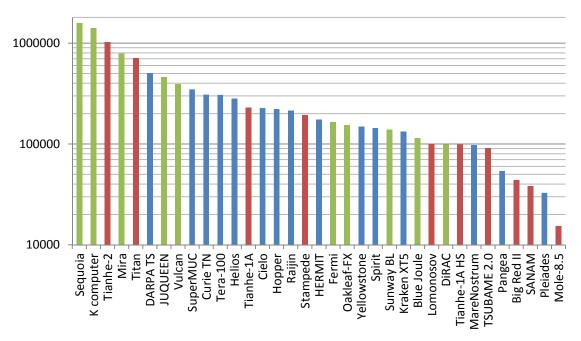

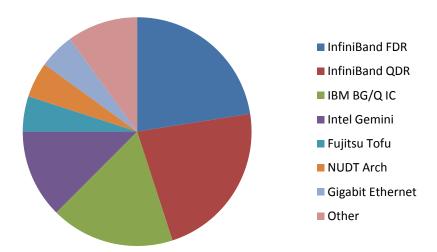

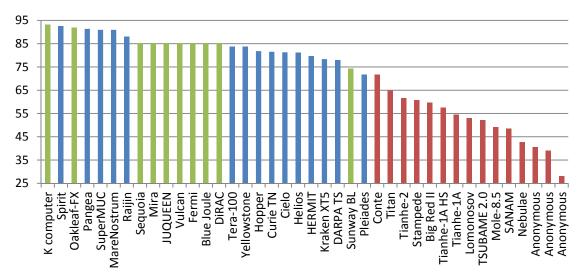

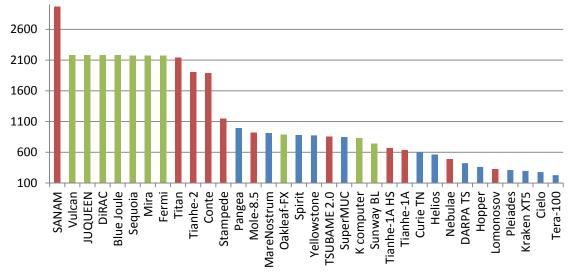

| 3.3.3 IEMI and eBoost. 3.4.1 Intel keynote speech at ISC 2013. 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY.  4.1 ASSESSMENT OF PETASCALE SYSTEMS.  4.1.1 HPC related electronic publications and web sites. 4.1.1.1 HPC related electronic publications and web sites. 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.1 Funding agencies web sites. 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the result searches we created an HPC Market Watch Google Custom Search engine (CSE), CSE allows the crustomised search engines using the Google search, by limiting the search space to only a predeficient search space to only a predeficient search engine (CSE), CSE allows the crustomised deadly within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Very of construction. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.2 Power efficiency. 4.1.3.3 Power efficiency. 4.1.3.4 Interconnect. 4.1.4 Dynamic Analysis. 4.1.4 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.2 Power efficiency. 4.1.4.3 Interconnect. 4.1.4 Dynamic Analysis. 4.1.4 Power efficiency. 4.1.4 Dynamic Analysis. 4.1.4 Power efficiency. 4.1.5 Beyond Top500. 4.2 BUSINSS NAILYSIS. 4.2.5 Current buzzwords 4.2.5 Large Systems Vendors. 4.2.5 Current buzzwords 4.2.5 Current buzzwords 4.2.5 Current buzzwords 4.2.5 Current buzzwords                                                              |   |     | 3.2.3    | Best practices in air cooling            | 29   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------|------------------------------------------|------|

| 3.3.1 Infrastructure Technologies. 3.3.2 Ultracapacitors 3.3.2 IPractical use of Ultra-capacitors at CEA. 3.3.3 IEMI and eBoost. 3.4.1 Intel keynote speech at ISC 2013. 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS). 3.5 CHAPTER SUMMARY. 4 ASSESSMENT OF PETASCALE SYSTEMS. 4.1 Sources. 4.1.1 Fur Crelated electronic publications and web sites. 4.1.1 Computing centre websites. 4.1.1 Funding agencies web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Google Custom Search Engine - To facilitate a more efficient search among the result search search engine (CSE). CSE allows the crecustomised search engines using the Google search, by limiting the search space to only a predeficient search among the result search engine expression is needed. Within WPS, we have created as Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Is Vendor. 4.1.3 Peak performance. 4.1.3 Peak performance. 4.1.3 Peak performance. 4.1.3 Processor. 4.1.3 Processor. 4.1.3 Processor. 4.1.3 Department of the Computer |   | 3.3 | ELECTRIC | ,                                        |      |

| 3.3.2 Ultracapacitors 3.3.3 I Practical use of Ultra-capacitors at CEA 3.3.3 IEMi and eBoost 3.4.1 Intel keynote speech at ISC 2013 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-waver Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY 4 ASSESSMENT OF PETASCALE SYSTEMS 4.1 MARKET WATCH AND ANALYSIS 4.1.1 Sources 4.1.1 PC related electronic publications and web sites 4.1.1.1 Vendor web sites 4.1.1.3 Vendor web sites 4.1.1.4 Funding agencies web sites 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the result searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the created and HPC Market Watch Google Custom Search engine (CSE). CSE allows the created and HPC Market Watch Google Custom Search bengine to searches we created an HPC Market Watch Google Custom Search bengine (Topical) is in seeded. Within WPS, we have created a Market Watch CSE that contains all sites that are relevativity, which can be accessed directly from a Google. 4.1.2 Snapshot 4.1.3 Year of construction 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.7 Accelerator 4.1.3.8 CPU cores 4.1.3.9 Nemory 4.1.4 Dynamic Analysis 4.1.4 Dynamic Analysis 4.1.4 Performance 4.1.4.5 Vendor 4.1.4 Performance 4.1.4 Dynamic Analysis 4.1.4 Dynamic Analysis 4.1.5 Large Systems Vendors 4.1.4 Dynamic Analysis 4.1.5 Large Systems Vendors 4.1.6 Processor 4.1.7 Accelerators 4.1.8 Linterconnects 4.1.9 Linyack Efficiency 4.1.4 Dynamic Analysis 4.1.5 Large Systems Vendors 4.2.5 Large Systems Vendors 4.2.5 Large Systems Vendors 4.2.5 CRAY 4.2.5 New CPU architectures                                                                                                                                                                                                                                                                              |   | 0.0 |          |                                          |      |

| 3.3.21 Practical use of Ultra-capacitors at CEA 3.3.3 IEMi and eBoost 3.4.1 Intel keynote speech at ISC 2013 3.4.2 Impressions and trends about processors at ISC 2013 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY 4.1 MARKET WATCH AND ANALYSIS 4.1 MARKET WATCH AND ANALYSIS 4.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites 4.1.1.3 HPC related electronic publications and web sites 4.1.1.4 Funding agencies web sites 4.1.1.5 Funding agencies web sites 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Susche, by limiting the search space to only a predeficient search space to only a predeficient search space to only a predeficient search way CSE provides only relevant search results, thus speeding the process of searching it is needed. Within WPS, we have created as Market Watch CSE that contains all sites that are relevant view which can be accessed directly from a Google. 4.1.2 Snapshot 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.9 Memory 4.1.3.10 Interconnects 4.1.3.1 Computing efficiency 4.1.3.1 Processor 4.1.4 Pymanic Analysis 4.1.4 Pymanic Analysis 4.1.4 Number of petascale systems 4.1.4 Pymanic Analysis 4.1.4 Performance 4.1.4.5 Processor 4.1.4 Pymanic Analysis 4.1.4 Performance 4.1.4 Processor 4.1.4 Processor 4.1.4 Performance 4.1.4 Processor 4.1.4 Performance 4.1.4 Performance 4.1.4 Performance 4.1.4 Performance 4.1.4 Performance 4.1.5 Processor 4.1.6 Processor 4.1.7 Reproduced to the Processor 4.1.8 Processor 4.1.9 Processor 4.1.1 Processor.                                                                                                                                  |   |     |          |                                          |      |

| 3.3.3 IEMI and eBoost. 3.4.1 Intel keynote speech at ISC 2013. 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY.  4.1 ASSESSMENT OF PETASCALE SYSTEMS.  4.1.1 HPC related electronic publications and web sites. 4.1.1.1 HPC related electronic publications and web sites. 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.1 Funding agencies web sites. 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the result searches we created an HPC Market Watch Google Custom Search engine (CSE), CSE allows the crustomised search engines using the Google search, by limiting the search space to only a predeficient search space to only a predeficient search engine (CSE), CSE allows the crustomised deadly within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Very of construction. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.2 Power efficiency. 4.1.3.3 Power efficiency. 4.1.3.4 Interconnect. 4.1.4 Dynamic Analysis. 4.1.4 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.2 Power efficiency. 4.1.4.3 Interconnect. 4.1.4 Dynamic Analysis. 4.1.4 Power efficiency. 4.1.4 Dynamic Analysis. 4.1.4 Power efficiency. 4.1.5 Beyond Top500. 4.2 BUSINSS NAILYSIS. 4.2.5 Current buzzwords 4.2.5 Large Systems Vendors. 4.2.5 Current buzzwords 4.2.5 Current buzzwords 4.2.5 Current buzzwords 4.2.5 Current buzzwords                                                              |   |     |          | Practical use of Ultra-capacitors at CEA |      |

| 3.4.1 Intel keynote speech at ISC 2013 3.4.2 Impressions and trends about processors at ISC 2013 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY.  4 ASSESSMENT OF PETASCALE SYSTEMS  4.1 MARKET WATCH AND ANALYSIS 4.1.1 HPC related electronic publications and web sites 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites 4.1.1.4 Funding agencies web sites 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the result searchs we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the created sites. That way CSE provides only relevant search search search search space to only a predeficient search with WPPs, we have created a Market Watch CSE that contains all sites that are releva activity, which can be accessed directly from a Google 4.1.2 Snapshot 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.9 Memory 4.1.3.10 Interconnects 4.1.3.1 Computing efficiency 4.1.3.2 Power efficiency 4.1.3.3 Power efficiency 4.1.3.4 Number of petascale systems 4.1.4 Dynamic Analysis 4.1.4 Number of petascale systems 4.1.4 Processor 4.1.4 Number of petascale systems 4.1.4 Processor 4.1.4 Processor 4.1.4 Dynamic Analysis 4.1.5 Vendor 4.1.4 Dynamic Analysis 4.1.4 Dynamic Analysis 4.1.5 Depond Type Construction 4.1.6 Processor 4.1.7 Country 4.1.8 Interconnect 4.1.9 Power efficiency 4.1.10 Power efficiency 4.1.11 Power efficiency 4.1.2 Current Duzzwords 4.2.5 Current Duzzwords 4.2.5 Current Duzzw                                                                                                                                                             |   |     |          | IEMi and eBoost                          |      |

| 3.4.1 Intel keynote speech at ISC 2013. 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY.  4 ASSESSMENT OF PETASCALE SYSTEMS.  4.1 MARKET WATCH AND ANALYSIS. 4.1.1 Sources. 4.1.1.1 PC related electronic publications and web sites. 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSIS). CSE allows the crucius of the control of the contro |   | 3 4 |          |                                          |      |

| 3.4.2 Impressions and trends about processors at ISC 2013. 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 5.4 | _        |                                          | _    |

| 3.4.3 Application-Aware Energy Efficiency HPC via Dynamic Voltage-Frequency Scaling (DVFS) 3.5 CHAPTER SUMMARY.  4.1 ASSESSMENT OF PETASCALE SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |     | -        |                                          |      |

| 4.1 MARKET WATCH AND ANALYSIS 4.1.1 MARKET WATCH AND ANALYSIS 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the crustomised search engines using the Google search, by limiting the search space to only a predefi sites. That way CSE provides only relevant search results, thus speeding the process of searching is in needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.11 Power efficiency. 4.1.4.14 Pyramic Analysis. 4.1.4.1 Number of petascale systems. 4.1.4.1 Pyramic Analysis. 4.1.4.2 Pyramic Construction. 4.1.4.3 Country. 4.1.4.3 Country. 4.1.4.4 Pyramic Construction. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.2 LINPACK Efficiency. 4.1.4.3 Current buzwords. 4.2.5 Large Systems Vendors.                                                                                                                                                                                                              |   |     | -        |                                          |      |

| 4.1 MARKET WATCH AND ANALYSIS  4.1.1 Sources. 4.1.1.1 HPC related electronic publications and web sites. 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google custom Search engine (CSE). CSE allows the creates were created an HPC Market Watch Google custom Search engine (CSE). CSE allows the creates were created an HPC Market Watch Google custom Search engine (CSE). CSE allows the created sites. That way CSE provides only relevant search results, thus speeding the process of searching is is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevant structures. Statis and structures activity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.14 Number of petascale systems. 4.1.4.14 Power of construction. 4.1.4.14 Power of construction. 4.1.4.15 Power efficiency. 4.1.4.16 Processor. 4.1.4.16 Processor. 4.1.4.17 Accelerators. 4.1.4.19 LINPACK Efficiency. 4.1.4.19 LINPACK Efficiency. 4.1.4.19 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.11 Department. 4.1.4.2 LINPACK Efficiency. 4.1.4.3 LINPACK Efficiency. 4.1.4.4 LINPACK Efficiency. 4.1.4.5 LINPACK Efficiency. 4.1.4.6 LINPACK Efficiency. 4.1.4.7 Accelerators. 4.1.4.8 LINPACK Efficiency. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.2 LINPACK Efficiency. 4.1.4.3 LINPACK Efficiency. 4.1.4.4 LINPACK Efficiency. 4.2.5 Large Systems Vendors. 4.2.5 Large Systems Vendors. 4.2.5 Large Systems Vendors. 4.2.5 Large Systems Vendors.                         |   | 3 5 |          |                                          |      |

| 4.1.1 Sources 4.1.1.1 HPC related electronic publications and web sites 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the created search search engines using the Google search, by limiting the search space to only a predefi sites. That way CSE provides only relevant search results, thus speeding the process of searching is in needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevativity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Sapshot. 4.1.3 Year of construction. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator 4.1.3.8 CPU cores 4.1.3.9 Memory 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency 4.1.3.12 Power efficiency 4.1.3.12 Power efficiency 4.1.3.14 Number of petascale systems 4.1.4.14 Number of petascale systems 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction. 4.1.4.3 Power efficiency 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Acceleratore. 4.1.4.8 INPACK Efficiency 4.1.4.9 LINPACK Efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.2 United the processor of the pr |   |     |          |                                          |      |

| 4.1.1 Sources 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creates we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creates searches we created an HPC Market Watch Coole sites. That way CSE provides only relevant search results, thus speeding the process of searching in is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.12 Power efficiency. 4.1.3.14 Pymaric Analysis. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.11 Number of petascale systems. 4.1.4.2 Vendor. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.11 Number of petascale systems. 4.1.4.2 Vendor. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.5 Beyond TopSoo. 4.2 BUSINESS ANALYSIS. 4.2.1 Current buzzwords 4.2.2 Memory. 4.2.3 Storage. 4.2.4 Intel or HPC accelerator. 4.2.5.1 Eurotech. 4.2.5.1 Eurotech. 4.2.5.1 Eurotech.                    | 4 | AS  | SSESSME  | NT OF PETASCALE SYSTEMS                  | 35   |

| 4.1.1 Sources 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites. 4.1.1.3 Vendor web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creates we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creates searches we created an HPC Market Watch Coole sites. That way CSE provides only relevant search results, thus speeding the process of searching in is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.12 Power efficiency. 4.1.3.14 Pymaric Analysis. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.10 Power efficiency. 4.1.4.11 Number of petascale systems. 4.1.4.2 Vendor. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.11 Number of petascale systems. 4.1.4.2 Vendor. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.5 Beyond TopSoo. 4.2 BUSINESS ANALYSIS. 4.2.1 Current buzzwords 4.2.2 Memory. 4.2.3 Storage. 4.2.4 Intel or HPC accelerator. 4.2.5.1 Eurotech. 4.2.5.1 Eurotech. 4.2.5.1 Eurotech.                    |   | 1 1 | MARKET   | ANALYSIS AND ANALYSIS                    | 2.5  |

| 4.1.1.1 HPC related electronic publications and web sites 4.1.1.2 Computing centre websites 4.1.1.3 Vendor web sites 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the cr customised search engines using the Google search, by limiting the search space to only a predeficients. That way CSE provides only relevant search results, thus speeding the process of searching in is needed. Within WP5, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.7 Accelerator 4.1.3.8 CPU cores 4.1.3.9 Memory 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency 4.1.3.12 Power efficiency 4.1.3.11 Number of petascale systems 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction 4.1.4.3 Country 4.1.4.3 Reproduction 4.1.4.4 Performance 4.1.4.5 Vendor 4.1.4.6 Processor 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction 4.1.4.3 Country 4.1.4.4 Performance 4.1.4.5 Vendor 4.1.4.6 Processor 4.1.4.7 Accelerators 4.1.4.8 Interconnect 4.1.4.9 UNPACK Efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.5 Beyond Top500 4.2 Unrel of HPC accelerator 4.2.5 Large Systems Vendors                                                                                                                                                                                |   | 4.1 |          |                                          |      |

| 4.1.1.2 Computing centre websites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the result searches we created an HPC Market Watch Google Search, by limiting the search space to only a predeficient search engine (CSE). CSE allows the created search engines using the Google search, by limiting the search space to only a predeficient search search in the search space to only a predeficient search was created a Market Watch CSE that contains all sites that are relevated activity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.11 Computing efficiency. 4.1.3.11 Power efficiency. 4.1.3.11 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor 4.1.4.6 Processor. 4.1.4.1 Seyond TopSoo. 4.1.5 Beyond TopSoo. 4.2 BUSINESS ANALYSIS. 4.2.1 Current buzzwords. 4.2.2 Memory. 4.2.3 Storage. 4.2.5 Large Systems Vendors. 4.2.5 Large Systems Vendors. 4.2.5 Large Systems Vendors. 4.2.5 New CPU architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |          |                                          |      |

| 4.1.1.3 Vendor web sites. 4.1.1.4 Funding agencies web sites. 4.1.1.5 Market Watch Tools. 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creutotomised search engines using the Google search, by limiting the search space to only a predeficient is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are releval activity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.4.13.12 Power efficiency. 4.1.4.4 Dynamic Analysis. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.2 Vera of construction. 4.1.4.3 Stowards. 4.2.2 Memory. 4.2.3 Storage. 4.2.4 Intel of HPC accelerator. 4.2.5.1 Eurotech. 4.2.5.2 CRAY. 4.2.5.3 NEC. 4.2.5.4 Eurotech. 4.2.5.6 New CPU architectures.                                                                                                                                                                                                                                                                                                                                                                   |   |     |          |                                          |      |

| 4.1.1.4 Funding agencies web sites 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Sustom Search engine (CSE). CSE allows the created search engines using the Google search, by limiting the search space to only a predeficient search results, thus speeding the process of searching it is needed. Within WP5, we have created a Market Watch CSE that contains all sites that are relevated activity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.7 Accelerator 4.1.3.8 CPU cores 4.1.3.9 Memory. 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency 4.1.3.11 Power efficiency 4.1.3.12 Power efficiency 4.1.3.1 Number of petascale systems 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction 4.1.4.3 Country. 4.1.4.1 Number of petascale systems 4.1.4.2 Vendor 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor 4.1.4.5 Vendor 4.1.4.6 Processor 4.1.4.7 Accelerators 4.1.4.9 LINPACK Efficiency 4.1.4.1 UNPACK Efficiency 4.1.4.1 INPACK Efficiency 4.1.4.1 Dynamic Analysis 4.1.4.1 Current buzzwords 4.2.2 Memory 4.2.3 Storage. 4.2.4 Intel or HPC accelerator. 4.2.5 Large Systems Vendors. 4.2.5.1 Eurotech. 4.2.5.4 Eurotech. 4.2.5.6 New CPU architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     |          | · · ·                                    |      |

| 4.1.1.5 Market Watch Tools 4.1.1.6 Google Custom Search Engine - To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the cn customised search engines using the Google search, by limiting the search space to only a predefix sites. That way CSE provides only relevant search results, thus speeding the process of searching is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot. 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country. 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator 4.1.3.8 CPU cores 4.1.3.9 Memory. 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.1 Power efficiency. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction 4.1.4.3 Country. 4.1.4.4 Performance 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators 4.1.4.8 Interconnect 4.1.4.9 LINPACK Efficiency. 4.1.4.1 Number of petascale systems 4.1.4.2 LINPACK Efficiency. 4.1.4.3 Beyond Top500. 4.2 Business Analysis 4.2.1 Current buzwords 4.2.2 Memory. 4.2.3 Storage. 4.2.4 Intel or HPC accelerator 4.2.5.1 Carge Systems Vendors 4.2.5.2 CRAY. 4.2.5.3 NEC 4.2.5.3 NEC 4.2.5.5 Nec CPU architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     | _        |                                          |      |

| 4.1.1.6 Google Custom Search Engine — To facilitate a more efficient search among the resul searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the customised search engines using the Google search, by limiting the search space to only a predeficient, which can be accessed only relevant search results, thus speeding the process of searching is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are releval activity, which can be accessed directly from a Google.  4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.1 Power efficiency. 4.1.4.3 Country. 4.1.4.4 Pyramic Analysis. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency. 4.1.4.9 LINPACK Efficiency. 4.1.4.1 Power efficiency. 4.1.4.1 Power efficiency. 4.1.4.1 Power efficiency. 4.1.4.2 LINPACK Efficiency. 4.1.4.3 Country. 4.1.4.4 LINPACK Efficiency. 4.1.4.5 Large Systems Vendors. 4.2.5 New CPU architectures.                                                                                                                                                                                                                       |   |     |          |                                          |      |

| searches we created an HPC Market Watch Google Custom Search engine (CSE). CSE allows the creators customised search engines using the Google search, by limiting the search space to only a predefisites. That way CSE provides only relevant search results, thus speeding the process of searching is needed. Within WP5, we have created a Market Watch CSE that contains all sites that are relevated activity, which can be accessed directly from a Google.  4.1.2 Snapshot. 4.1.3 Static Analysis. 4.1.3.1 Year of construction. 4.1.3.2 Country. 4.1.3.3 Peak performance. 4.1.3.4 LINPACK performance. 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores. 4.1.3.9 Memory. 4.1.3.10 Interconnects. 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency. 4.1.3.13 Power efficiency. 4.1.3.14 Dynamic Analysis. 4.1.4.1 Number of petascale systems. 4.1.4.1 Number of petascale systems. 4.1.4.2 Year of construction. 4.1.4.3 Country. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect 4.1.4.9 LINPACK Efficiency. 4.1.4.10 Power efficiency. 4.1.4.1 Number of petascale systems. 4.1.4.2 Vear of construction. 4.1.4.3 Cuurtry. 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.9 LINPACK Efficiency. 4.1.4.1 Dynamic Analysis. 4.2.1 Current buzzwords 4.2.2 Memory. 4.2.3 Storage. 4.2.4 Intel or HPC accelerator. 4.2.5 Large Systems Vendors. 4.2.5 Reyurched. 4.2.5 Reyurched. 4.2.5 Reyurched. 4.2.5 Reyurched. 4.2.5 Reyurched. 4.2.5 New CPU architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |     |          |                                          |      |

| customised search engines using the Google search, by limiting the search space to only a predeficites. The way CSE provides only relevant search results, thus speeding the process of searching in seeded. Within WPS, we have created a Market Watch CSE that contains all sites that are relevance in the content of the cont |   |     | _        |                                          |      |

| sites. That way CSE provides only relevant search results, thus speeding the process of searching is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevant in the process of searching is needed. Within WPS, we have created a Market Watch CSE that contains all sites that are relevant in the process of searching is needed. Within WPS.  4.1.2 Snapshot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     |          |                                          | . 1. |

| is needed. Within WP5, we have created a Market Watch CSE that contains all sites that are relevantivity, which can be accessed directly from a Google. 4.1.2 Snapshot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     |          |                                          |      |

| activity, which can be accessed directly from a Google. 4.1.2 Snapshot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     |          |                                          | nat  |

| 4.1.2 Snapshot 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor. 4.1.3.6 Processor. 4.1.3.7 Accelerator. 4.1.3.8 CPU cores 4.1.3.9 Memory. 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency. 4.1.3.12 Power efficiency 4.1.4 Dynamic Analysis 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction 4.1.4.3 Country 4.1.4.4 Performance. 4.1.4.5 Vendor. 4.1.4.6 Processor. 4.1.4.7 Accelerators. 4.1.4.8 Interconnect. 4.1.4.9 LINPACK Efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.1 Current buzzwords 4.1.4.2 Line Department buzzwords 4.1.4.3 Storage. 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.10 LINPACK Efficiency 4.1.4.10 LINP |   |     |          |                                          | 40   |

| 4.1.3 Static Analysis 4.1.3.1 Year of construction 4.1.3.2 Country 4.1.3.3 Peak performance 4.1.3.4 LINPACK performance 4.1.3.5 Vendor 4.1.3.6 Processor 4.1.3.7 Accelerator 4.1.3.9 Memory 4.1.3.10 Interconnects 4.1.3.11 Computing efficiency 4.1.3.12 Power efficiency 4.1.4.1 Number of petascale systems 4.1.4.2 Year of construction 4.1.4.3 Country 4.1.4.4 Performance 4.1.4.5 Vendor 4.1.4.6 Processor 4.1.4.7 Accelerators 4.1.4.8 Interconnect 4.1.4.9 LINPACK Efficiency 4.1.4.9 LINPACK Efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.2 Line connect 4.1.4.3 Line connect 4.1.4.4 Line connect 4.1.4.5 Line connect 4.1.4.7 Accelerators 4.1.4.8 Interconnect 4.1.4.9 LINPACK Efficiency 4.1.4.10 Power efficiency 4.1.4.10 Power efficiency 4.1.4.10 Line or PPC accelerator 4.2.1 Current buzzwords 4.2.2 Memory 4.2.3 Storage 4.2.4 Intel or HPC accelerator 4.2.5 Large Systems Vendors 4.2.5.1 Bull 4.2.5.2 CRAY 4.2.5.3 NEC 4.2.5.4 Eurotech 4.2.6 New CPU architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | • • •    | · · ·                                    |      |

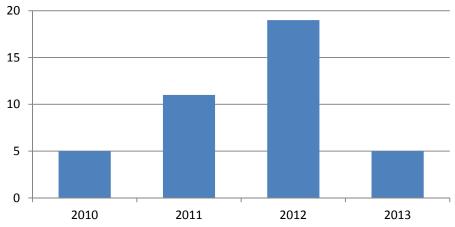

| 4.1.3.1       Year of construction         4.1.3.2       Country         4.1.3.3       Peak performance         4.1.3.4       LINPACK performance         4.1.3.5       Vendor.         4.1.3.6       Processor         4.1.3.7       Accelerator         4.1.3.8       CPU cores         4.1.3.9       Memory         4.1.3.10       Interconnects         4.1.3.11       Computing efficiency         4.1.3.12       Power efficiency         4.1.4       Dynamic Analysis         4.1.4.1       Number of petascale systems         4.1.4.2       Year of construction         4.1.4.3       Country         4.1.4.4       Performance         4.1.4.5       Vendor         4.1.4.6       Processor         4.1.4.7       Accelerators         4.1.4.8       Interconnect         4.1.4.9       LINPACK Efficiency         4.1.4.10       Power efficiency         4.1.4.1       Power efficiency         4.1.4.1       Power efficiency         4.1.4.2       Ling Morrow         4.2.1       Current buzzwords         4.2.2       Memory         4.2.3 <td< th=""><th></th><th></th><th></th><th>· ·</th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     |          | · ·                                      |      |

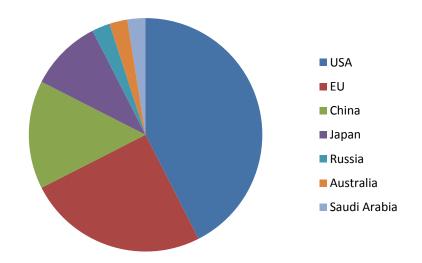

| 4.1.3.2       Country                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     | _        | ·                                        |      |

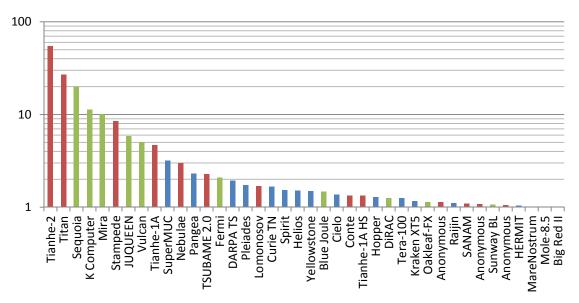

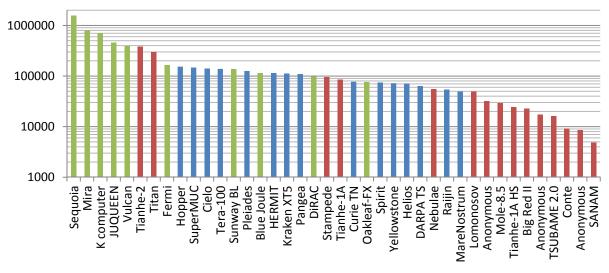

| 4.1.3.3       Peak performance         4.1.3.5       LINPACK performance         4.1.3.6       Processor         4.1.3.7       Accelerator         4.1.3.8       CPU cores         4.1.3.10       Interconnects         4.1.3.11       Computing efficiency         4.1.3.12       Power efficiency         4.1.4.1       Number of petascale systems         4.1.4.1       Number of petascale systems         4.1.4.2       Year of construction         4.1.4.3       Country         4.1.4.4       Performance         4.1.4.5       Vendor         4.1.4.6       Processor         4.1.4.7       Accelerators         4.1.4.8       Interconnect         4.1.4.9       LINPACK Efficiency         4.1.4.10       Power efficiency         4.1.4.1       Power efficiency         4.1.4.2       Vendor         4.1.4.3       Interconnect         4.1.4.4       Interconnect         4.1.4.5       Beyond Top500.         4.2       Business Analysis         4.2.1       Current buzzwords         4.2.2       Memory         4.2.3       Storage.         4.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     |          |                                          |      |

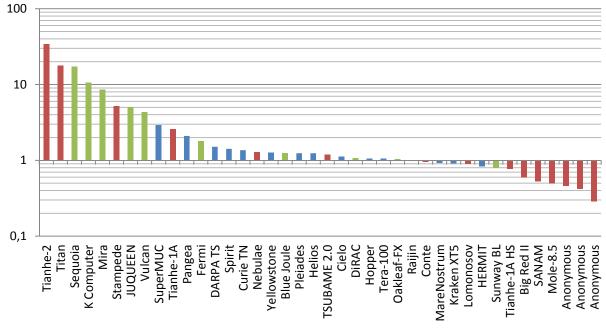

| 4.1.3.4       LINPACK performance         4.1.3.5       Vendor         4.1.3.6       Processor         4.1.3.7       Accelerator         4.1.3.8       CPU cores         4.1.3.9       Memory         4.1.3.10       Interconnects         4.1.3.11       Computing efficiency         4.1.3.12       Power efficiency         4.1.4       Dynamic Analysis         4.1.4.1       Number of petascale systems         4.1.4.2       Year of construction         4.1.4.3       Country         4.1.4.4       Performance         4.1.4.5       Vendor         4.1.4.6       Processor         4.1.4.7       Accelerators         4.1.4.8       Interconnect         4.1.4.9       LINPACK Efficiency         4.1.4.10       Power efficiency         4.1.4.5       Beyond Top500         4.2       Business Analysis         4.2.1       Current buzzwords         4.2.2       Memory         4.2.3       Storage         4.2.4       Intel or HPC accelerator         4.2.5.1       Bull         4.2.5.2       CRAY         4.2.5.3       NEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     | _        | •                                        |      |

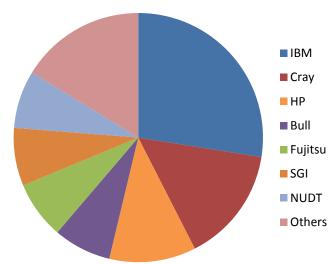

| 4.1.3.5       Vendor.         4.1.3.6       Processor         4.1.3.7       Accelerator         4.1.3.8       CPU cores         4.1.3.9       Memory         4.1.3.10       Interconnects         4.1.3.11       Computing efficiency         4.1.3.12       Power efficiency         4.1.4       Dynamic Analysis         4.1.4.1       Number of petascale systems         4.1.4.2       Year of construction         4.1.4.3       Country         4.1.4.4       Performance         4.1.4.5       Vendor         4.1.4.6       Processor         4.1.4.7       Accelerators         4.1.4.8       Interconnect         4.1.4.9       LINPACK Efficiency         4.1.4.10       Power efficiency         4.1.4.10       Power efficiency         4.1.4.10       Power efficiency         4.1.4.10       Power efficiency         4.1.4.2       Limpack Efficiency         4.1.4.3       Storage         4.2.1       Current buzzwords         4.2.2       Memory         4.2.3       Storage         4.2.4       Intel or HPC accelerator         4.2.5.1 <td< th=""><th></th><th></th><th></th><th>•</th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |     |          | •                                        |      |

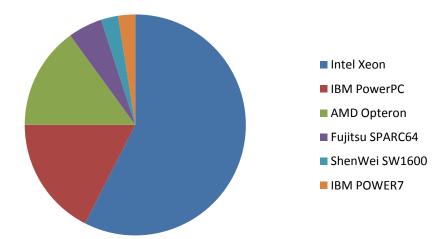

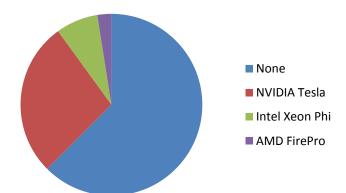

| 4.1.3.6       Processor         4.1.3.7       Accelerator         4.1.3.8       CPU cores         4.1.3.9       Memory         4.1.3.10       Interconnects         4.1.3.11       Computing efficiency         4.1.3.12       Power efficiency         4.1.4       Dynamic Analysis         4.1.4.1       Number of petascale systems         4.1.4.2       Year of construction         4.1.4.3       Country         4.1.4.4       Performance         4.1.4.5       Vendor         4.1.4.6       Processor         4.1.4.7       Accelerators         4.1.4.8       Interconnect         4.1.4.9       LINPACK Efficiency         4.1.4.10       Power efficiency         4.1.4.10       Power efficiency         4.1.5       Beyond Top500         4.2       Business Analysis         4.2.1       Current buzzwords         4.2.2       Memory         4.2.3       Storage         4.2.4       Intel or HPC accelerator         4.2.5.1       Bull         4.2.5.2       CRAY         4.2.5.3       NEC         4.2.5.4       Eurotech <t< th=""><th></th><th></th><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |     |          |                                          |      |