# Reduction of Power in General Purpose Processor Through Clock-Gating Technique

R. Prakash Rao, P. Bala Murali Krishna, S. Sree Chandra, Shaik Fairooz, P. Prasanna Murali

Abstract: Now a days DC power supply plays very important role in the Electronic industry because for every electronic gadget DC power is required to operate it. Even though durable DC batteries are available in the market to operate the various electronic gadgets for more time, electronic designers are continuously concentrating more and more to reduce the power through the various new Technologies like increasing parallel operations, pipe line concepts [1] etc. To work such durable batteries more duration than the actual duration what they can give, in this work we are concentrating on the 'clock-gating' technique to reduce the power in the general purpose microprocessor. For every microprocessor clock is required. All operations of any processor are performed by the clock cycle. There are various blocks in the processor but all the blocks are not operated at a time while using it, some blocks in the off mode while other blocks are in the working mode. Hence in order to power off such blocks for a little while clock gating is used in this work. Wherever particular block is not operated, for that block clock is disabled by the clock gating technique. The main principle of clock getting is nothing but ANDing the processor clock with a gate-control signal.

Keywords: DC Power, Electronic Gadgets, Clock Gating, General Purpose Microprocessor, Clock Cycle.

## INTRODUCTION

Without the power, no system is operated in the nature. Power is two types, AC power and DC power. AC power is used for all the electrical applications whereas DC power is used for all electronic applications. DC power is generated by converting AC to DC adaptors but we cannot carry easily such setup from one place to other place. Hence, portable batteries like Lithium, Cadmium DC batteries came into the picture. Such portable DC batteries may give more durability.

Manuscript received on May 19, 2021. Revised Manuscript received on May 29, 2021. Manuscript published on May 30, 2021.

\* Correspondence Author

Dr. R. Prakash Rao\*, Professor, Department of ECE, PACE ITS(Autonomous), (Andhra Pradesh), Ongole dr\_prakashrao@pace.ac.in

Dr. P. Bala Murali Krishna, Professor, Department of ECE, Chalapathi Institute of Technology, Guntur (Andhra Pradesh), India. Email: pbmk05@gmail.com

S. Sree Chandra, Assoc. Professor, Department of ECE, Chalapathi Institute of Technology, Guntur (Andhra Pradesh), India. Email: sreechandra23@gmail.com

Dr. Shaik Fairooz, Assoc. Professor, Department of ECE, MREC(Autonomous), Maisammaguda, Secunderabad, T.S, India. Email: fairoozsk@gmail.com

Dr. P. Prasanna Murali, Professor, Department of ECE, KCIT, Markapur (Andhra Pradesh), India. Email: pprasannamurali@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

But to extend the DC battery run time further, researchers are concentrating on the more design optimization techniques. If we optimize the design of electronic devices then the power consumption will be reduced hence battery run time will be increased more than normal [2].

For the past few years power sensitive devices have got the more importance because all the portable electronic appliances are being used portable power supplies like lithium, cadmium batteries. Examples of such electronic appliances are cell phones, personal digital assistants, notebook, laptop, palmtop and portable communication

For every 'technology generation' power consumption is increased due to the increased frequencies and increased density of transistors in the die. But upto certain limits scaling of supply voltage is maintained the power consumption. For high performance applications scaling of voltages have certain limits [3]. Hence to maintain the power density within limits only voltage scaling is not sufficient it leads to power sensitive applications.

Dissipation of power by the circuits of VLSI:

There are two types of power dissipations or consumptions by the VLSI circuits i.e., static power dissipation and dynamic power dissipation.

Static power consumption:

Any VLSI circuit is the combination of combinational logic circuits and sequential logic circuits. Such combinational and sequential logic circuits are designed by

Logic gates will consume the power in two ways that is first one is static power consumption and second one is dynamic power consumption. When the static current flows from V<sub>DD</sub> to V<sub>SS</sub> or supply rails then that current multiplied by resistance is called static resistance. Consumption of static power is occurred in NMOS technology because in NMOS technology pull up transistor is depletion mode transistor which should act as always ON resistance. Hence, static current will flow from  $V_{DD}$  to  $V_{SS}$  when pull down transistor is on. When such static current multiplied by ON resistance of pull up and pull down transistors then it gives rise to static power of that particular logic circuit. Apart from this type of static power dissipation, at the transistor level in the nano meter range there are some other leakage powers which cannot be avoided. In NMOS FET or PMOS FET these are -

#### Reduction of Power in General Purpose Processor through Clock-Gating Technique

1. Leakage power due to reverse biased PN junction at drain and substrate terminals. 2. Gate terminal leakage current due to direct tunneling between potential barrier and  $SiO_2$  layer. 3. Leakage current due to sub-threshold.

Dynamic power consumption:

Dynamic power consumption occurs when ON and OFF switching actions take place for the pull up and pull down transistors for a given VLSI circuits. When the load capacitance is being charged or discharged, depending on operation of the logic circuit this dynamic power is produced.

We can observe dynamic power consumption in all CMOS circuits because in CMOS circuits pull up is PMOS transistors and pull-down is NMOS transistors. When input voltage logic '0' is applied pull up transistor comes to ON position and hence the load capacitance  $C_{\rm L}$  is charged, at that time pull down transistor is in OFF condition. Similarly, when input voltage logic 1 is applied pull down transistor comes to ON position and pull up transistor goes OFF position hence capacitor  $C_{\rm L}$  is discharged through pull down transistor. Like this, due to charging and discharging of load capacitor  $C_{\rm L}$  with pull up and pull down transistors respectively dynamic power occur.

Various techniques are there to reduce static and dynamic powers. They are-Static power can be reduced by run time technique, cache memories and duel threshold techniques. Similarly, dynamic power is reduced by scaling technique, by reduced interconnections and clock-gating methods.

#### II. PROPOSED METHOD

#### A. Clock-Gating:

In a microprocessor for all the peripheral devices like flip-flops, latches and logic gates and address decoders the clock will come from the clock network. At high level the necessary charging and discharging of capacitances when the circuit is idle is avoided by gating the clock to a latch are a logic gate by ANDing the clock with a control signal. Hence the circuit clock power is saved.

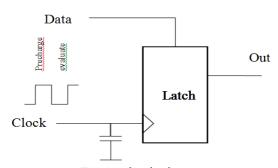

Below figure.1 shows the latch element schematic diagram. In this, gate capacitance Cg is the cumulative gate capacitance of a latch. The gate capacitance Cg gets charged or discharged as the clock switches from ON to OFF and OFF to ON, so that the significant amount of power is consumed. Even though the inputs are not changed from present clock position to the next clock position still the power is consumed by the latch.

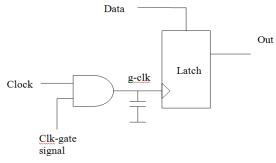

Figure.2 shows the clock gating, in which the clock is gated by ANDing it with a control signal. In this the clock gate signal is turned off when the latch is not required to switch state and hence the clock does not allow to charge or discharge capacitor, therefore clock power is saved. Using this technique, we can get a net power saving. As the latches of an operand i.e., 32 bit or 64 bit is driven by an AND gate and as we know the capacitance of AND gate itself is soo smaller than the sum of multiple gate capacitance Cg of these latches, net power will be saved.

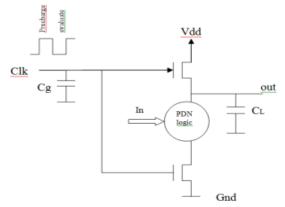

Figure.3 shows the schematic diagram of dynamic logic gate. The load capacitance CL is connected at the output of circuit. Similarly, at the input Cg capacitance is connected which charges and discharges for any clock cycle and consumes power. Capacitances Cg, CL charged or discharged through PMOS and NMOS transistors. During

the pre-charge stage Cg will charge. When it fully charges PMOS goes OFF and NMOS comes to ON, hence load capacitance is charged. During evaluate stage vice-versa, that is Cg is discharged. When it fully discharged PMOS will ON and NMOS goes OFF hence load capacitance is discharged or retains value depending on input to the pull-down network. Capacitance CL consumes power or not depends on the both previous output and current input of the circuit.

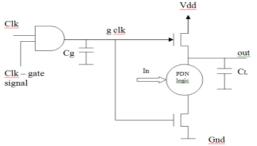

Figure 4 shows dynamic logic gate which is being clock gating by clock gate signal. When dynamic logic cell is not used in a cycle, clock gate signal prevents both Cg and CL from switching in the cycle.

Fig.1 A latch element

Fig.2 clock gating a latch element

Fig.3 A dynamic logic gate

Published By:

Blue Eyes Intelligence Engineering and Sciences Publication

© Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.A59270510121 DOI: 10.35940/ijrte.A5927.0510121 Journal Website: www.ijrte.org

Fig.4 clock gating a dynamic logic gate

This logic reduces unwanted clock power due to Cg and also the dynamic logic power due to C<sub>L</sub>.

In this compared with Cg plus C<sub>L</sub>, the capacitance due to AND gate is small, hence net power will be saved.

#### III. DESIGN OF GENERAL PURPOSE PROCESSOR WITH CLOCK-GATING

For every processor while designing its central processing unit we have to design its instruction set first. We have to come to one conclusion with some points like how many instructions we require? what type of instructions they are? and assignment of op-code to each and every instruction is important. After come to conclusion regarding instruction set we have to design data path. Data path will execute various instructions of instruction set. As per processor requirement a tailored cut data path is designed. Hence, while designing data path we have to keep in the mind like number of functions, number of registers, register and connection for different units After designing above two, at the end we have to design control unit. The control unit passes various control signals

to data path. Based on that the logic operations are performed.

The control unit performs operations like fetching, decoding and executing the instructions. The instructions are categorized into different sections i.e., 1.data transfer instructions which are used to move data from accumulator to memory or registers and vice-versa. 2. Arithmetic instructions which perform addition and subtraction operations. 3. Logical instructions which perform basic logic gate operations like NOT, AND, OR, Ex-OR, NAND, NOR etc., 4. Input instructions, these will send data from input devices to CPU. 5. Output instructions, these will collect data from CPU to output devices. 6. Jump instructions, these will change the sequence of operation from one address location to other address location. Unless otherwise memory address as one of its operand, all instructions are encoded by one byte. If memory address is one of its operand then second byte is required for addresses. In the encoding scheme, first four bits are used for opcode. Based on this, identified four bits which are opcode has two operand instructions, one operand instructions, instructions using of memory address and jump instructions.

#### A. Data Path:

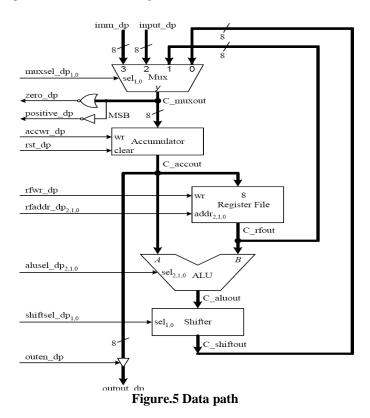

The data path is designed after completing the instruction set definitions. All instructions in the instruction set are executed by the data path shown in figure 5. The thick lines indicate the width of data path. The width of data path is 8, that is, for data movement 8 bits wide data path is used. As shown in figure 5, thin lines show control lines and all are 1 bit wide except the name is like fddr\_dp2,1,0 and it indicates many lines.

Retrieval Number: 100.1/ijrte.A59270510121 DOI: 10.35940/iirte.A5927.0510121 Journal Website: www.ijrte.org

## Reduction of Power in General Purpose Processor through Clock-Gating Technique

Flags:

There are two types of conditional flags like zero\_dp and position\_dp which are being set by two components like NOR gate and NOT gate as shown in figure . For the above two conditions of zero\_dp and position\_dp, the output of multiplexer will be written into accumulator. To check the zero value 8 input NOR gate is used at the output of multiplexer. To test the number 1, check only MSB of 8 bit values which is by NOT gate.

### Accumulator:

The input of accumulator comes from output of multiplexer and it has 8 bit length. Accumulator content will reset by rst\_dp and the content of memory or register will write up into accumulator if accur\_dp goes high. The output of accumulator goes to output buffer, ALU and register file.

#### Register file:

Eight locations are there for register file. Each location size is 8 bit length. For reading and writing there are three address lines like rfaddr\_dp2, rfaddr\_dp1, rfaddr\_dp0. Read and write ports are there. Read port is always high which indicates that value from present selected address location. To write selected location rfwr dp must be used. This is important to note that separate read and write control signals are not needed because we require at a time either read or write.

### Arithmetic Logic Unit:

With respect to above data path shown in figure 3, it has 8 operations. The eight operations are selected by 3 select lines as shown like alusel\_dp<sub>2.1.0</sub>. i.e., alusel\_dp<sub>2</sub> alusel\_dp<sub>1</sub>. and alusel\_dp<sub>0</sub>. Depending on instruction the logic will be performed and the output is send to

# Shifter:

The input of shifter is 8 bit length which comes from output of ALU. Based on control lines shown as shift dp1 and 0, number of positions will be shifted either to left are right depending on operations and then the output will be sent to input of multiplexer.

## Output buffer:

Output buffer is a register to which input comes from accumulator. The data will be controlled by outen\_dp. The final result of particular operation will be stored in this output buffer. At the end it will be sent to output devices.

#### Control word:

For the data path shown in figure 5, control word bit length is 14. This control word maps the different data paths come by the control signals.

#### **B.** Control Unit:

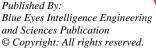

Below figure.6 shows the control unit of the finite state machine. It consist of various states like reset state, fetch state, decode state and execute state. The operation under particular state is given below-

### Reset:

When the reset signal is high, finite state mission starts its execution. On reset signal is high, all its control signals and working variables are initialized. For example, variable are-

IR state and program counter etc. Apart from this, the program for execution is also loaded in memory.

#### Fetch:

When the fetch state is activated, the content of memory location which is being indicated by program counter will be loaded into instructions register. To fetch the next instruction the program counter will be incremented immediately by 1. Sometimes the fetched instruction may be jump instruction, at that time the program counter will change accordingly.

#### Decode:

The content of the instruction register is decoded as per encoding specified by processor. This process will be accomplished in VHDL by the switch condition as opcode. From various cases the state that is exiting respective instruction, is allotted to the next state variable hence the new instructions will be executed starting from the beginning of clock cycle.

#### Execute:

This state will set up the control word. The control word assigns certain control signals for data path to act accordingly. Every instruction contains its own execution state. Data path will not take it's action for all jump instructions.

Figure.6 State diagram for the control unit.

# **C. Complete Processor:**

Retrieval Number: 100.1/ijrte.A59270510121 DOI: 10.35940/ijrte.A5927.0510121 Journal Website: www.ijrte.org

Figure.7 Complete general purpose processor

Figure.7 shows the architecture of complete general purpose processor. It consists of control unit and data path blocks as the main units. Control unit block consists of next state logic, storage memory register and output logic. Present state of the logic circuit will be stored by state memory resistor based on the present state logic, output logic will be framed and then control signals will be passed to the data path black. While sending the present state logic to output logic the same is fed back to the next state logic. Depending on the control signal which have come from control unit, the data will be manipulated by multiplexer,

ALU, register and buffer the final data output is available at the output of buffer. In order to generate the next state, logic state signals will come to next state logic black from the data path block.

#### IV. SIMULATION RESULTS

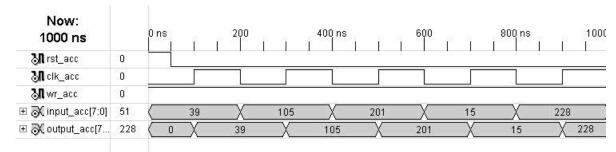

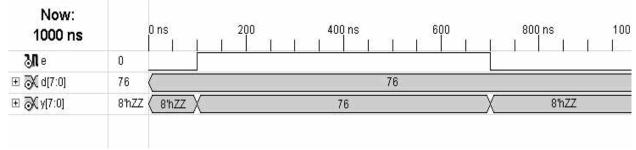

Below figure.8 to 13 show simulation results of general purpose processor when with and without clock gate is used. Simulation has been done by Xilinx 13.5 software tool and synthesis by XST with SPARTAN FPGA board.

Figure.8. Accumulator output when without clock gate

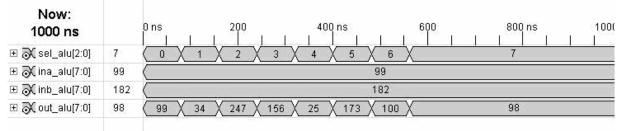

Figure 9. ALU output for without clock gate when the inputs are A = "01100011" and B = "10110110".

| Now:<br>1000 ns |     | 0 ns  | 200<br>I I I I | 400 ns  | 600<br> | 800 ns | 100<br>I I |

|-----------------|-----|-------|----------------|---------|---------|--------|------------|

| <b>∭</b> clk_rf | 0   |       |                |         |         |        |            |

| <b>∭</b> wr_rf  | 0   |       | , i            |         |         |        |            |

|                 | 0   |       | X              | 1       | 0       | 1      | χ o        |

|                 | 118 | 0 \   | 118 X          | 173     | (118)   | 173    | 118        |

|                 | 118 | 8"hUU | X 118 X        | 8'hUU ) | 118     | 8'hUU  | 118        |

|                 |     |       |                |         |         |        |            |

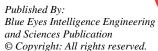

Figure.10. Multiplexer output when without clock gate.

Retrieval Number: 100.1/ijrte.A59270510121 DOI: 10.35940/ijrte.A5927.0510121 Journal Website: www.ijrte.org

Figure.11. Register file output when with clock gate

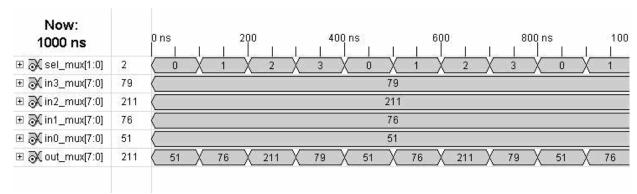

Figure.12. Shifter output for with clock gate when the input is "00111011".

Figure.13. Tri-state buffer output when with clock gate

POWER CALCULATIONS (WITH CLOCK GATE & WITHOUT CLOCK GATE):

| WER CHECCENTIONS (WITH CECCR CHIE & WITHOUT CECCR CHIE). |                 |          |                 |             |                    |             |                 |             |                    |             |  |

|----------------------------------------------------------|-----------------|----------|-----------------|-------------|--------------------|-------------|-----------------|-------------|--------------------|-------------|--|

|                                                          | ALU             |          | ACC             |             | MUX                |             | SHIFTER         |             | BUFFER             |             |  |

|                                                          | With Out<br>C.G | With C.G | With out<br>C.G | With<br>C.G | With<br>out<br>C.G | With<br>C.G | With out<br>C.G | With<br>C.G | With<br>out<br>C.G | With<br>C.G |  |

| No.of<br>slices                                          | 26              | 18       | 14              | 9           | 12                 | 8           | 10              | 8           | 3                  | 1           |  |

| No. of 4 i/p LUT's                                       | 32              | 25       | 14              | 9           | 20                 | 16          | 11              | 9           | 3                  | 1           |  |

| No. of<br>IO's                                           | 35              | 27       | 24              | 19          | 56                 | 42          | 24              | 18          | 22                 | 17          |  |

| No. of IO<br>Buffers                                     | 35              | 27       | 24              | 19          | 56                 | 42          | 24              | 18          | 22                 | 17          |  |

**Table.1 Cell Usage for the General Purpose Processor**

# V. CONCLUSION

Even though portable batteries like Lithium, Cadmium can give the more durability, design engineers had found the various techniques like parallel processing, pipe lining, scaling etc., to consume the less power by the VLSI circuits so that power sensitive packs could work for more and more run time. All those techniques have its own limitations. To avoid those limitations and to give more

durability to power packing devices, similarly to consume less power by the general purpose processors clock-gating technique which is a novel technique applied and proven that power consumption is less with clock gating compared to without clock gating.

go lemod lenoteman

w.ijrte.org

**Exploring Innovatio**

Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.

#### REFERENCES

- RP Rao, ND Rao, K Naveen, P Ramya, "Implementation of the standard floating point MAC using IEEE 754 floating point adder"-2018 Second International Conference on Computing Methodologies and Communication (ICCMC), IEEE digital library, DOI:10.1109/ICCMC.2018.8487626

- M. Pedram, "Power minimization in IC design: Principles and applications", ACM Trans. Design Automation, vol. 1, no. 1, pp. 3-56, Jan. 1996.

- G. Friedman, "Clock distribution design in VLSI circuits: An overview", Proc. IEEE ISCAS, pp. 1475-1478, 1994-May.

- E. Tellez, A. Farrah and M. Sarrafzadeh, "Activity-driven clock design for low power circuits", *Proc. IEEE ICCAD*, pp. 62-65, 1995-Nov.

#### **AUTHORS' PROFILE**

**Dr. R. Prakash Rao,** received Ph.D from JNTUH, Hyderabad; M.Tech from College of Engineering Andhra University, Vizag and B.Tech from Nagarjuna University, Guntur, India. He has 17 years of teaching experience. He worked as Professor & HOD in the department of ECE, St.Peter"s Engineering College, Hyderabad for 8 years. Presently he is working as Professor & BOS Chair in the department of ECE, PACE ITS, Ongole. He

published 19 papers in various National and International reputed Journals and Conferences. He got best faculty award for the A.Y 2017-2018 by the Rotaract club, Secundrabad. He has guided 14 M.Tech projects and about 32 B.Tech projects in various fields. His research interest includes VLSI, VLSI with signal processing, Microwave Engineering and Embedded Systems.

**Dr. Balamuralikrishna**, received B.E in Electronics and Communication from Andhra University, Andhra Pradesh, M. Tech in Electronics and Communication and Ph.D. in Wireless Mesh Networks from JNTU Kakinada. He has 20 years of administrative and teaching experience. He published 40+ research papers in reputed National & International Journals and conferences. He is a reviewer for leading journals like Springer, Elsevier and some others.

He is a life member in IETE and ISTE. His research interests include Wireless Networks, Image Processing and Communications. He has been inspiring and motivating the students over the years through academic excellence.

Communications.

Sree Chandra Swarna, received B. Tech. in Electronics and Communication Engineering from JNTU, Hyderabad and M. Tech. in Electronics and Communication Engineering from JNTUK Kakinada. She is persuing her Ph.D. in Wireless Communication at KLEF, Vijayawada. She has 17 years of teaching experience and 4 years of research experience. Her research interests include Wireless Networks, Image Processing and

**Dr. SK.Fairooz,** is an Associate Professor in Electronics and Communication Department in MREC ( Autonomous) , Hyderabad . He is having total Experience of 21 Yrs. He completed his PhD from JNTU Hyderabad in the research field VLSI in the year Oct 2018. He was post graduated from Osmania University , Hyderabad in the year 2006 with the specialization Digital Systems and Secured Top rank from OU. He was graduated from VJREC, Vijayawada in the

year 2000. His expertise in subjects like Network Analysis, Control Systems. He use active and collaborative learning techniques, engage students in experiences, emphasize higher-order cognitive activities in the classroom, interact with students, challenge students academically, and value enriching educational experiences. He is one of the editorial member for annual department magazine ELECTRONICA FORUM 2014, 2015 and also an coordinator of International Conference ICrtSIV 2015. He

Retrieval Number: 100.1/ijrte.A59270510121 DOI: 10.35940/ijrte.A5927.0510121

Journal Website: www.ijrte.org

presented and published several papers in SCI/Scopus Indexed / International Journals/ Conference Papers.

**Dr. P Prasanna Murali Krishna,** presently working as Professor & HOD of ECE Department in Krishna Chaitanya Institute of Technology & Sciences, Markapur. He has 18 years of experience. He completed his B.E from Dr. Baba Saheb Ambedkar Marathawada University, Auragabad in 2000, M.Tech from JNTU, Kakinada in 2003. He obtained his Ph.D in wireless communications from JNTU, Kakinada in 2017. His areas of interest include Wireless Communications, VLSI Design, Digital

ICs. He published various national & international journals in reputed journals.