Zen 3アーキテクチャは効果てきめん? AMDがモバイル向け「Ryzen 5000」シリーズを解説(1/2 ページ)

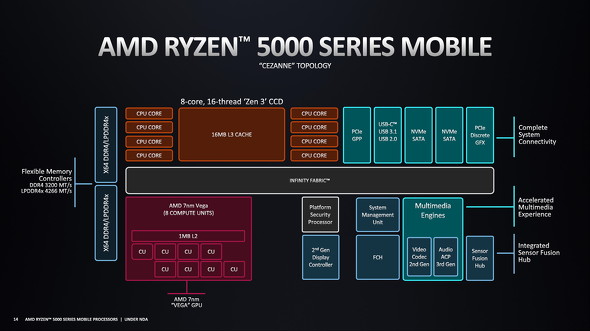

既報の通り、AMDは1月12日(米国太平洋時間)に新型APU(GPU統合CPU)「Ryzen 5000 Series Mobile Processors」(開発コード名:Cezanne)を発表した。

この記事では、1月14日に行われた報道関係者向け説明会の内容を基に、Ryzen 5000 Series Mobile Processors(以下「モバイル向けRyzen 5000」)の特徴を説明する。

一部を除きCPUアーキテクチャは「Zen 3」に

モバイル向けRyzen 5000の特徴の1つが、一部のモデルを除いてCPUアーキテクチャを「Zen 3」に移行したことだ。Zen 3アーキテクチャは、先代の「Ryzen 4000 Series Mobile Processors(Ryzen 4000)」で用いられた「Zen 2」と同じく7nmプロセスで作られているが、構造を改善することでパフォーマンスの向上を図っている。

CCXの構造変更

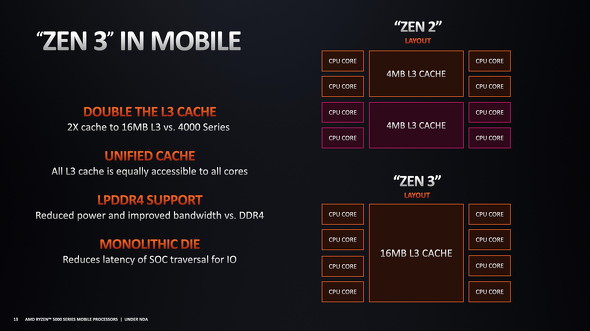

モバイル向けのZen 2アーキテクチャでは、1基のCCX(※)に最大4基のCPUコアと4MBのL3キャッシュを統合している。8コアCPUの場合、2基のCCXに合計で8MBのL3キャッシュを搭載することになるが、あるCCXに属するCPUコアは、他方のCCXにあるL3キャッシュに直接アクセスできないため、L3キャッシュがボトルネックになってパフォーマンスが低下する恐れがあった。

(※)CCX(Core Complex):CPUコアとCPUキャッシュを統合したモジュール

それに対し、モバイル向けのZen 3アーキテクチャでは、CCXの構造を最大8基のCPUで16MBのL3キャッシュを共有するように改めた。キャッシュ容量の倍増に加え、8基のCPUコアが同じL3キャッシュにアクセスできるようになったことで、パフォーマンスの改善につながっている。

メモリコントローラーの改善

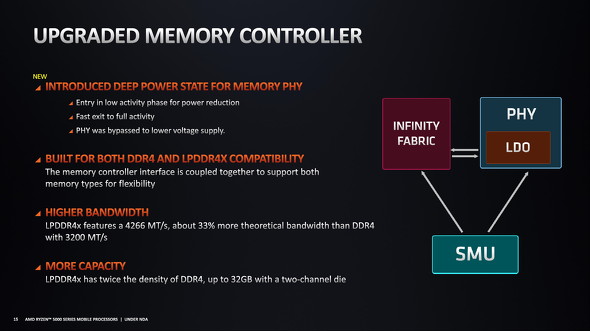

モバイル向けRyzen 5000のメモリコントローラーは、メモリチップに対する省電力機能も強化している。メインメモリへのアクセスが少ない場合、メモリチップを省電力モードに移行させることでバッテリーの消費を抑制できる。

なお、メインメモリはDDR4規格(DDR4-3200/PC4-25600)とLPDDR4X規格(LPDDR4X-4266)の両方をサポートすることは変わりない。

CPUクロックの切り替えの高速化

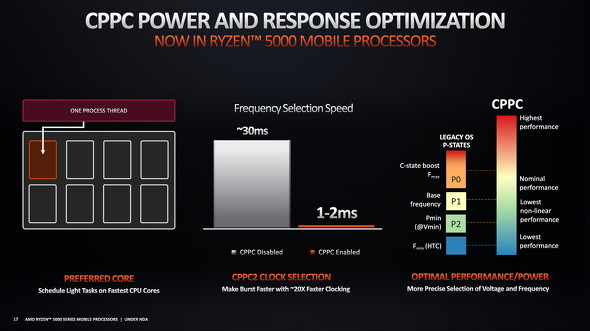

従来のモバイル向けRyzenは「バッテリー駆動時のパフォーマンスが悪い」とされてきた。この点は、AMDの競合であるIntelが機会のある度に指摘してきたことでもある。

その改善策として、モバイル向けRyzen 5000では「CPPC(Collaborative Processor Performance Controls)」と呼ばれるCPUクロック(周波数)の調整機能をサポートした。これにより、UEFI(ファームウェア)とOSが対応していれば、CPUクロックの切り替えが最大で20倍高速に行えるようになる。

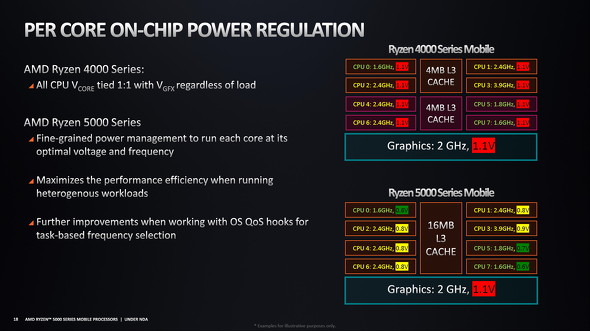

コア単位での省電力管理に対応

モバイル向けRyzen 5000では、コア単位で電圧とクロックを調整できるようになった。これにより電力効率が改善し、消費電力を削減できている。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- “本気マウス”に傑作キーボードの改良、ラピトリ対応まで ロジクールの最新デバイスに触れてみた (2024年12月27日)

- 2024年のベストバイガジェット5選 リング付きMagSafeモバイルバッテリーに大満足 (2024年12月28日)

- 武者良太が選ぶ、2024年のベストバイガジェット4選 取材用カメラとして“アレ”が最強すぎた (2024年12月28日)

- 2024年を月ごとに振り返る! 9万4800円から買える新型「Mac mini」の魅力(10月編) (2024年12月28日)

- 6万円超え&約2.5kgのフルキーボードがデビュー (2024年12月28日)

- “仕事しやすい”を追求する変態(?)ガジェットライターの2024ベストバイはこれ! (2024年12月26日)

- Intelの苦境と変わりゆくデバイス――“AIシフト”の影響を受け続けた2024年のテック業界 (2024年12月27日)

- 「Windows 11 24H2」のインストールメディアに問題 対応策を検討中/Xが有料プラン「X Premium+」を値上げ 月額630円・年額6740円アップ (2024年12月29日)

- 木に裏配線、ダミーモジュールなど“自作PCの幅”が広がった2024年 (2024年12月27日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)