DISS. ETH NO. 19163

# DATA STREAM PROCESSING ON EMBEDDED DEVICES

A dissertation submitted to

# ETH ZURICH

for the degree of

Doctor of Sciences

presented by

RENÉ MÜLLER

Master of Science ETH in Computer Science, ETH Zurich

September 24, 1978

citizen of Walterswil, Solothurn

accepted on the recommendation of

Prof. Dr. Gustavo Alonso, examiner Prof. Dr. Donald Kossmann, co-examiner Prof. Dr. Samuel R. Madden, co-examiner Dr. Satnam Singh, co-examiner

2010

Typeset with LATEX Printer: ETH Zurich Printed in Switzerland © 2010 by René Müller

# Abstract

Over the years, online processing of data has become more important. In inventory management, monitoring and financial applications data is generated in streams that are processed on the fly instead of being stored in a repository and processed offline later. As data volumes increase, processing has to be offloaded from the central stream processing engine. Processing either has to be moved to the data sources or to specialized accelerators placed between data source and engine. Stream processing platforms thus become heterogeneous. The problem is how to optimize query execution when it spans different streaming systems.

This thesis discusses stream processing on two different platforms: wireless sensor networks and field-programmable gate arrays (FPGAs). Both are typically connected to traditional server-class streaming processors. Driven by the different optimization goals (e.g., throughput, latency, resource consumption) operators have to be carefully placed. In some cases it is more efficient to place operators, for example, into the sensor network. Other operators that require a substantial amount of state are better placed on the server. The problems addressed in this work is the design of the underlying execution platforms that facilitate the operator placement, strategies, and cost-models used for optimization.

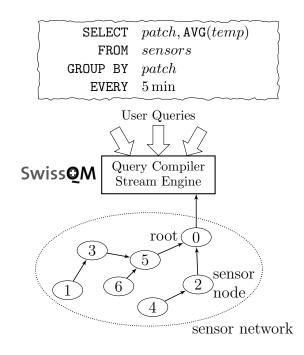

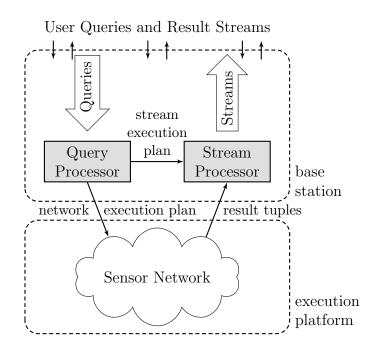

In the first part of the thesis SwissQM is presented. SwissQM is a stream processing platform for wireless sensor networks and is based on a small virtual machine that is deployed on resource-constrained sensor nodes. Declarative queries submitted by the user are translated into short bytecode sequences and are disseminated in the network. The bytecode programs implement streaming operators that are executed at the data source in the network. The remaining operators of the queries are placed onto the base station that connects the wireless sensor network to, e.g., the Internet. The base station also performs multi-query optimization of multiple user queries that are executed concurrently. The thesis proposes an energy-based cost model and presents optimization strategies that rely on the cost model. Multi-query optimization maximizes utilization of the network infrastructure such that expensive deployments can be accessed by several users and applications concurrently.

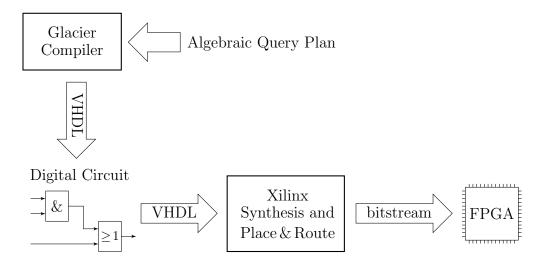

The second part of the thesis applies the same techniques to FPGAs, i.e., the automated compilation of queries into digital circuits that can be placed onto FPGAs. First, a stream processing algebra is defined, which is later used to express stream execution plans. *Glacier*, a library of hardware components and a set of translation rules is presented as compositional approach to translate queries into FPGAs circuits. A key property of the generated hardware circuits is the well-defined performance behavior. The dissertation also presents optimization techniques to trade-off various parameters on the FPGAs such as throughput, latency, and chip space.

The thesis proposes a common solution for both the sensor network and the FPGA domain, which allows users to specify queries in the same declarative language. As such, it increases the level of abstraction on both platforms from embedded systems programming and hardware description languages to a high-level language. As a domain-specific language it makes this technology available to broader range of users.

# Kurzfassung

Die Online-Datenverarbeitung hat in den letzten Jahren an Bedeutung gewonnen. Lagerverwaltungs- und Überwachungssysteme sowie Anwendungen aus dem Finanzsektor verarbeiten Daten, sogenannte Datenströme, zunehmend ohne vorgängiges Speichern. Mit steigendem Datenvolumen muss ein Teil der Verarbeitung vom Streamprozessor ausgelagert werden. Die Verarbeitung wird entweder in die Datenquelle selbst oder auf einen Hardware-Beschleuniger im Datenpfad zwischen Quelle und Streamprozessor ausgelagert. Die Streamverarbeitung erfolgt somit auf einer heterogenen Plattform. Das Problem besteht nun darin, die Verarbeitung zu Optimieren, auch wenn diese unterschiedliche Systeme umschliesst.

Im Rahmen dieser Dissertation werden zwei Streamverarbeitungplattformen vorgestellt: drahtlose Sensornetzwerke und FPGAs (Field-Programmable Gate Arrays). Beide sind üblicherweise mit einem bestehenden, Server-basierten Streamverarbeitungssystem verbunden. Unterschiedliche Optimierungsziele (z.B. Durchsatz, Latenz, Resourcenverbrauch) bestimmten das Platzieren der Operatoren. In bestimmten Fällen ist es effizienter, einen Operator in das Sensornetzwerk zu verschieben. In anderen Fällen werden Operatoren, die üblicherweise sehr speicherintensiv sind, sinnvollerweise auf dem leistungsfähigeren Server ausgeführt. Das Design der Ausführungsplattform, welche das Verschieben von Operatoren ermöglicht, sowie die entsprechenden Platzierungsstrategien und Kostenmodelle für die Optimierung werden in dieser Dissertation behandelt.

Im ersten Teil der Arbeit wird SwissQM vorgestellt. SwissQM ist eine Streamverarbeitungsplattform für drahtlose Sensornetzwerke, die auf einer virtuellen Maschine (VM) basiert. Diese VM wird auf den Sensorknoten installiert. Deklarative Anfragen, die Anwender an das System stellen, werden in kurze Bytecodesequenzen übersetzt und im Netzwerk verteilt. Die Bytecodeprogramme implementieren diejenigen Streamoperatoren, welche ins Sensornetzwerk verschoben wurden. Die übrigen Verarbeitungsschritte werden auf der Basisstation ausgeführt, welche das Sensornetzwerk mit beispielsweise dem Internet verbindet. Die Basisstation führt ebenfalls Multiquery-Optimierung durch, d.h., parallele Anfragen von mehreren Anwendern werden optimiert und gleichzeitig ausgeführt. Dadurch kann die üblicherweise äussert teure Installation von mehreren Benutzern oder Endanwendungen gleichzeitig verwendet und die Kosten entsprechend aufgeteilt werden. Im zweiten Teil werden diese Techniken auf FPGAs angewendet, d.h., die automatische Übersetzung von Anfragen in digitale Schaltung für FPGAs. Zuerst wird eine Streamalgebra eingeführt, anhand deren Anfragepläne dargestellt werden können. Anschliessend wird *Glacier* vorgestellt. Es handelt sich dabei um eine Bibliothek aus Hardwarekomponenten und einen Satz von Regeln, anhand derer die Anfragepläne durch Einsatz von Komposition in FPGA-Schaltungen übersetzt werden können. Eine wichtige Eigenschaft der erzeugten Hardwareschaltungen ist das wohldefinierte Verhalten bezüglich Latenz und Durchsatz. Die Arbeit stellt weiter Optimierungstechniken vor, die es erlauben, verschiedene Parameter wie beispielsweise, Durchsatz, Latenz und die erforderliche Chip-Fläche gegeneinander abzuwägen.

In dieser Dissertation wird eine allgemeine Lösung vorstellt, die sowohl für Sensornetzwerke als auch für FPGAs eingesetzt werden kann. Benutzer können Anfragen in deklarativer Form stellen. Als solche, entspricht diese einer domänenspezifischen Sprache, welche den Abstraktionsgrad vom Programmieren eingebetteter Systeme und dem Design von Schaltungen auf die Ebene einer Hochsprache erhöht. Das macht die Plattformen für einen weiteren Benutzerkreis verwendbar.

# Contents

| A | bstra                            | $\operatorname{ct}$                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                                                                                                                                                |

|---|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K | urzfa                            | ssung                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{v}$                                                                                                                                                                       |

| 1 | <b>Intr</b><br>1.1<br>1.2<br>1.3 | oduction         Motivation                                                                                                                                                                                                                                                                                                                                                                                                          | <b>1</b><br>1<br>5<br>7                                                                                                                                                            |

| Ι | Da                               | ta Stream Processing in Wireless Sensor Networks                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                                                                                                                                                  |

| 2 | Dat<br>2.1<br>2.2<br>2.3<br>2.4  | a Processing in Wireless Sensor NetworksWireless Sensor Nodes2.1.1 Hardware2.1.2 Programming2.1.2 ProgrammingArchitectures of Wireless Sensor Networks2.2.1 Wireless Communication Links2.2.2 Link Quality Measurements2.2.3 Network Architectures2.2.4 Collection Tree RoutingData Processing in Sensor Networks2.3.1 Programming Models2.3.2 System Space2.3.3 Virtual Machine-based Approaches2.3.4 Declarative InterfacesSummary | <ol> <li>11</li> <li>12</li> <li>12</li> <li>15</li> <li>17</li> <li>17</li> <li>18</li> <li>22</li> <li>23</li> <li>27</li> <li>29</li> <li>30</li> <li>31</li> <li>33</li> </ol> |

| 3 | <b>The</b><br>3.1                | SwissQM ApproachQuery Platform for Sensor Networks3.1.1Design Considerations3.1.2System Architecture                                                                                                                                                                                                                                                                                                                                 | <b>35</b><br>35<br>36<br>36                                                                                                                                                        |

|   |     | 3.1.3          | SwissQM Gateway                    | 37 |

|---|-----|----------------|------------------------------------|----|

|   |     | 3.1.4          | •                                  | 38 |

|   |     | 3.1.5          |                                    | 41 |

|   | 3.2 | SwissQ         |                                    | 42 |

|   |     | 3.2.1          |                                    | 42 |

|   |     | 3.2.2          |                                    | 43 |

|   |     | 3.2.3          | 5 5                                | 45 |

|   |     | 3.2.4          |                                    | 48 |

|   |     | 3.2.5          | • 0                                | 49 |

|   |     | 3.2.6          |                                    | 53 |

|   |     | 3.2.7          |                                    | 58 |

|   |     | 3.2.8          | 1 0 0                              | 59 |

|   |     | 3.2.9          | 1 00 0                             | 59 |

|   | 3.3 |                | 8                                  | 61 |

|   |     | 3.3.1          |                                    | 61 |

|   |     | 3.3.2          | Query Interfaces                   | 62 |

|   |     | 3.3.3          |                                    | 64 |

|   |     | 3.3.4          |                                    | 65 |

|   | 3.4 | Exam           |                                    | 66 |

|   |     | 3.4.1          |                                    | 67 |

|   |     | 3.4.2          |                                    | 68 |

|   |     | 3.4.3          |                                    | 71 |

|   | 3.5 | Evalua         | ation                              | 74 |

|   |     | 3.5.1          | Execution Time                     | 74 |

|   |     | 3.5.2          | Concurrent programs                | 75 |

|   |     | 3.5.3          |                                    | 77 |

|   |     | 3.5.4          |                                    | 80 |

|   | 3.6 | Summ           | hary                               | 81 |

| 4 | Que | erv Op         | timization for Sensor Networks 8   | 33 |

|   | 4.1 |                |                                    | 83 |

|   | 4.2 | Data I         |                                    | 84 |

|   |     | 4.2.1          | 1                                  | 84 |

|   |     | 4.2.2          |                                    | 87 |

|   | 4.3 | Querv          |                                    | 89 |

|   |     | 4.3.1          | 0 0                                | 94 |

|   |     | 4.3.2          |                                    | 95 |

|   |     | 4.3.3          | - · ·                              | 97 |

|   |     | 4.3.4          |                                    | 99 |

|   |     | 4.0.4          |                                    | 23 |

|   |     | 4.3.4<br>4.3.5 | Evaluation Merging Techniques   10 |    |

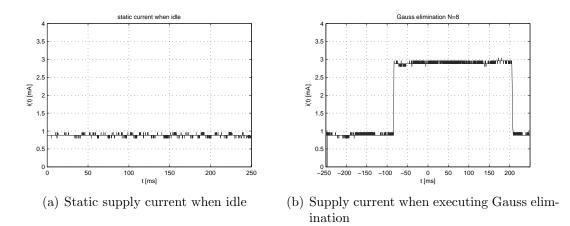

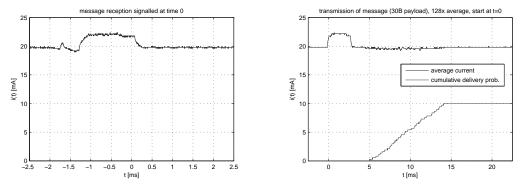

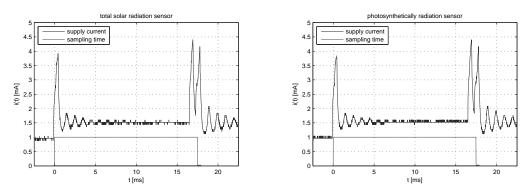

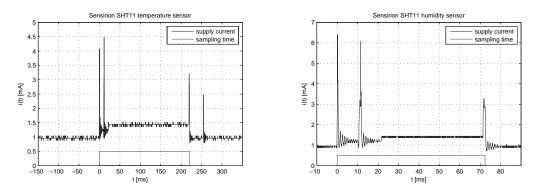

|         |                                                                            | 4.4.1 Power Consumption of a Tmote Sky Sensor Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 106                                                                                                        |

|---------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|         |                                                                            | 4.4.2 Per-Tuple Costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 112                                                                                                        |

|         |                                                                            | 4.4.3 Overall Cost Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

|         | 4.5                                                                        | Query Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|         |                                                                            | 4.5.1 Plan Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|         |                                                                            | 4.5.2 Plan Optimizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|         |                                                                            | 4.5.3 Cost of Submitting Queries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 121                                                                                                        |

|         |                                                                            | 4.5.4 Optimizer Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

|         |                                                                            | 4.5.5 Queries with Predicates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 123                                                                                                        |

|         | 4.6                                                                        | Optimizer Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|         |                                                                            | 4.6.1 Min-Execution Cost Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 126                                                                                                        |

|         |                                                                            | 4.6.2 Delta-Plan Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 134                                                                                                        |

|         |                                                                            | 4.6.3 Single-Plan Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 134                                                                                                        |

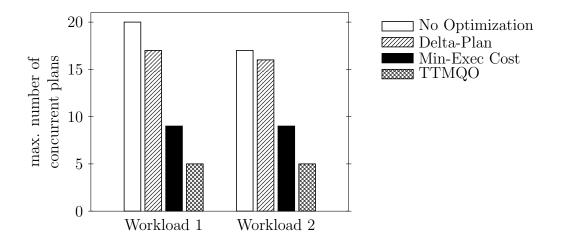

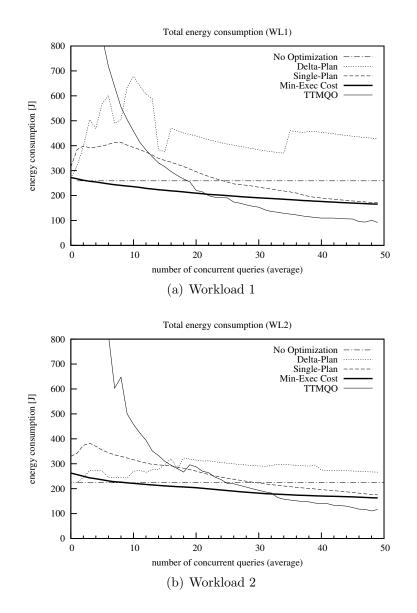

|         | 4.7                                                                        | Evaluation of Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 135                                                                                                        |

|         |                                                                            | 4.7.1 Query Workload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 135                                                                                                        |

|         |                                                                            | 4.7.2 Few Concurrent Queries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 136                                                                                                        |

|         |                                                                            | 4.7.3 Many Concurrent Queries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 139                                                                                                        |

|         | 4.8                                                                        | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 142                                                                                                        |

|         | 4.9                                                                        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 143                                                                                                        |

|         |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|         |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

| II      | D                                                                          | ata Stream Processing on FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 147                                                                                                          |

| II<br>5 |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 147<br>149                                                                                                   |

|         |                                                                            | d Programmable Gate Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 149                                                                                                          |

|         | Fiel                                                                       | d Programmable Gate Arrays<br>Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>149</b><br>. 151                                                                                          |

|         | <b>Fiel</b><br>5.1                                                         | d Programmable Gate Arrays<br>Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>149</b><br>. 151<br>. 152                                                                                 |

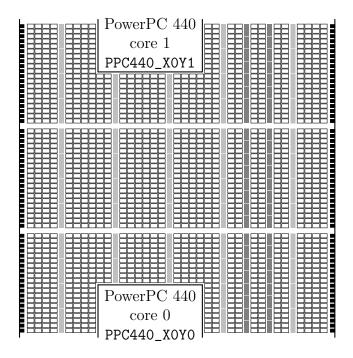

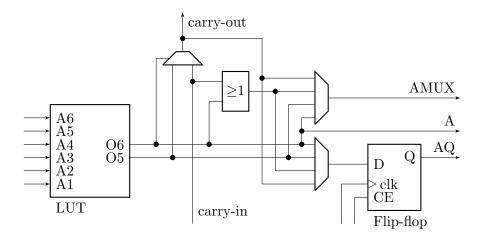

|         | <b>Fiel</b><br>5.1                                                         | d Programmable Gate Arrays         Related Work         Overview of FPGAs         5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>149</b><br>. 151<br>. 152<br>. 153                                                                        |

|         | <b>Fiel</b><br>5.1                                                         | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154                                                               |

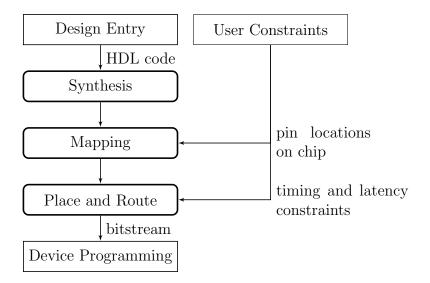

|         | <b>Fiel</b><br>5.1                                                         | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154<br>. 156                                                      |

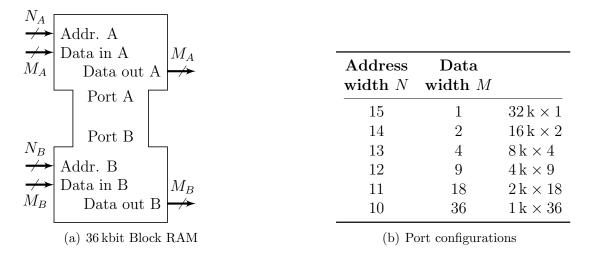

|         | <b>Fiel</b><br>5.1                                                         | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154<br>. 156<br>. 157                                             |

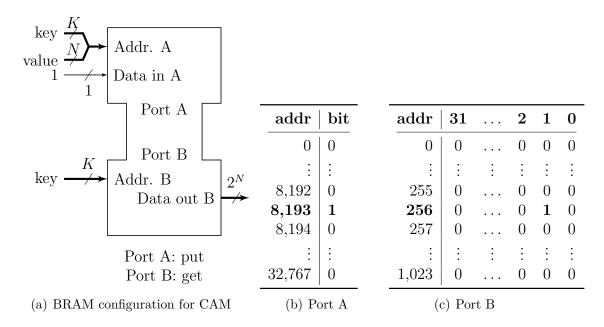

|         | <b>Fiel</b><br>5.1<br>5.2                                                  | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154<br>. 156<br>. 157<br>. 158                                    |

|         | <b>Fiel</b> 5.1 5.2 5.3                                                    | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154<br>. 156<br>. 157<br>. 158<br>. 159                           |

|         | <b>Fiel</b> 5.1 5.2 5.3 5.4                                                | d Programmable Gate Arrays         Related Work         Overview of FPGAs         5.2.1       FPGA Architecture         5.2.2       FPGA Design Flow         5.2.3       Hardware Setup         5.2.4       Dual-Ported Block RAM         Content-Addressable Memory         Network Interface                                                                                                                                                                                                                                               | <b>149</b><br>. 151<br>. 152<br>. 153<br>. 154<br>. 156<br>. 157<br>. 158<br>. 159<br>. 160                  |

|         | <b>Fiel</b> 5.1 5.2 5.3 5.4                                                | d Programmable Gate Arrays         Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 149<br>. 151<br>. 152<br>. 153<br>. 154<br>. 156<br>. 157<br>. 158<br>. 159<br>. 160<br>. 160                |

|         | <b>Fiel</b> 5.1 5.2 5.3 5.4                                                | d Programmable Gate Arrays         Related Work         Overview of FPGAs         5.2.1 FPGA Architecture         5.2.2 FPGA Design Flow         5.2.3 Hardware Setup         5.2.4 Dual-Ported Block RAM         Content-Addressable Memory         Network Interface         FPGA Co-Processor         5.5.1 Bus Attachment                                                                                                                                                                                                                | 149<br>151<br>152<br>153<br>154<br>156<br>157<br>158<br>159<br>160<br>160<br>161                             |

| 5       | <b>Fiel</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                      | d Programmable Gate Arrays         Related Work         Overview of FPGAs         5.2.1 FPGA Architecture         5.2.2 FPGA Design Flow         5.2.3 Hardware Setup         5.2.4 Dual-Ported Block RAM         Content-Addressable Memory         Network Interface         FPGA Co-Processor         5.5.1 Bus Attachment         5.5.2 Attachment to CPU Execution Pipeline         Summary                                                                                                                                             | 149<br>151<br>152<br>153<br>154<br>156<br>157<br>158<br>159<br>160<br>160<br>161<br>163                      |

|         | <b>Fiel</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Sor</b>        | d Programmable Gate Arrays         Related Work       Overview of FPGAs         5.2.1       FPGA Architecture         5.2.2       FPGA Design Flow         5.2.3       Hardware Setup         5.2.4       Dual-Ported Block RAM         Content-Addressable Memory       Network Interface         FPGA Co-Processor       FPGA Co-Processor         5.5.1       Bus Attachment         5.5.2       Attachment to CPU Execution Pipeline         Summary       Summary                                                                       | 149<br>151<br>152<br>153<br>154<br>156<br>157<br>158<br>159<br>160<br>160<br>161<br>163                      |

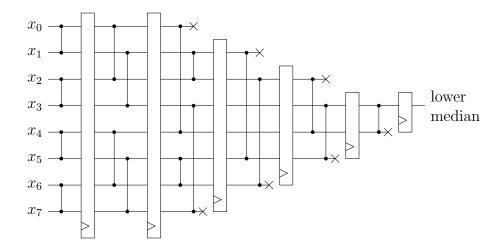

| 5       | <b>Fiel</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Sor</b><br>6.1 | d Programmable Gate Arrays         Related Work       Overview of FPGAs         Overview of FPGAs       52.1         5.2.1       FPGA Architecture         5.2.2       FPGA Design Flow         5.2.3       Hardware Setup         5.2.4       Dual-Ported Block RAM         5.2.4       Dual-Ported Block RAM         Content-Addressable Memory       Network Interface         FPGA Co-Processor       55.1         Summary       Summary         summary       Summary         ting Networks on FPGAs         Related Work       Summary | 149<br>151<br>152<br>153<br>154<br>156<br>157<br>158<br>159<br>160<br>160<br>161<br>163<br>165<br>166        |

| 5       | <b>Fiel</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Sor</b>        | d Programmable Gate Arrays         Related Work       Overview of FPGAs         5.2.1       FPGA Architecture         5.2.2       FPGA Design Flow         5.2.3       Hardware Setup         5.2.4       Dual-Ported Block RAM         Content-Addressable Memory       Network Interface         FPGA Co-Processor       FPGA Co-Processor         5.5.1       Bus Attachment         5.5.2       Attachment to CPU Execution Pipeline         Summary       Summary                                                                       | 149<br>151<br>152<br>153<br>154<br>156<br>157<br>158<br>159<br>160<br>160<br>161<br>163<br>165<br>166<br>167 |

# CONTENTS

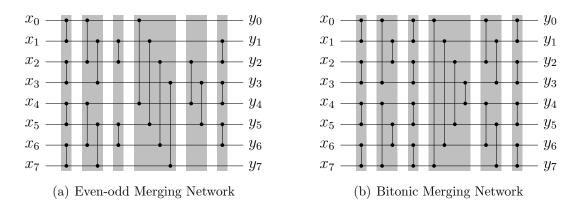

|   |     | 6.2.2  | Bitonic Merging Networks                                                                                                      |

|---|-----|--------|-------------------------------------------------------------------------------------------------------------------------------|

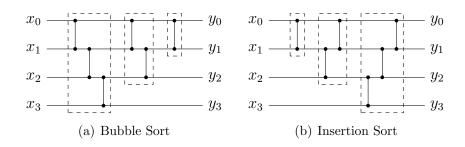

|   |     | 6.2.3  | Bubble and Insertion Sort Networks                                                                                            |

|   |     | 6.2.4  | Sorting Networks Comparison                                                                                                   |

|   | 6.3 | Implei | menting Sorting Networks                                                                                                      |

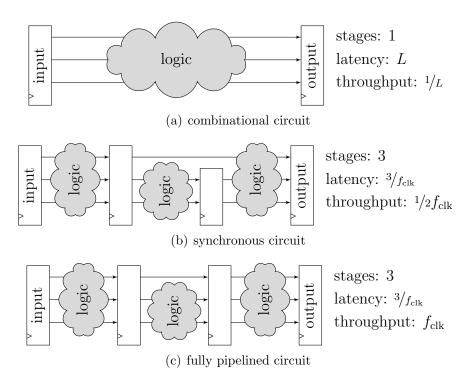

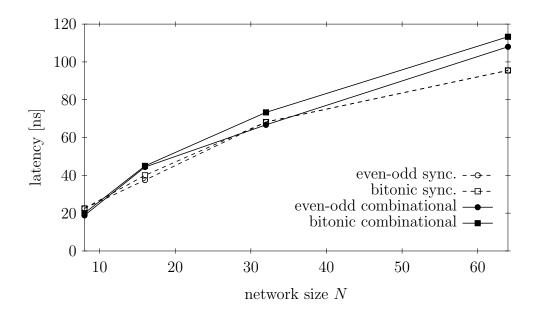

|   |     | 6.3.1  | Combinational vs. Synchronous Pipelined Circuits 173                                                                          |

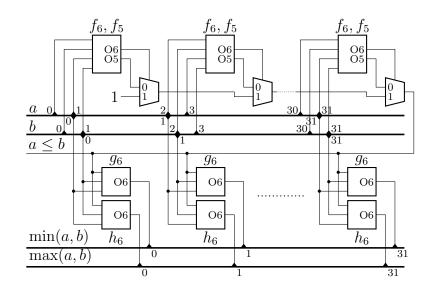

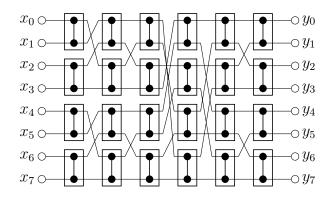

|   |     | 6.3.2  | Implementing Comparators on FPGAs                                                                                             |

|   |     | 6.3.3  | Combinational Sorting Networks                                                                                                |

|   |     | 6.3.4  | Synchronous Implementation on FPGA                                                                                            |

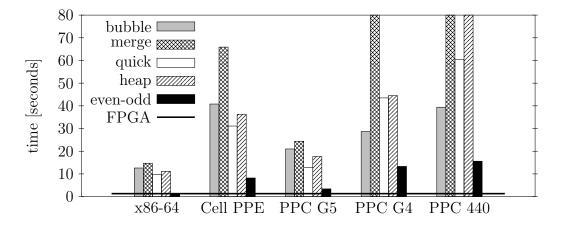

|   |     | 6.3.5  | Sorting Networks on CPUs                                                                                                      |

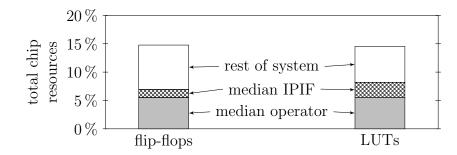

|   | 6.4 | Evalua | ation: Sorting Circuits on FPGAs                                                                                              |

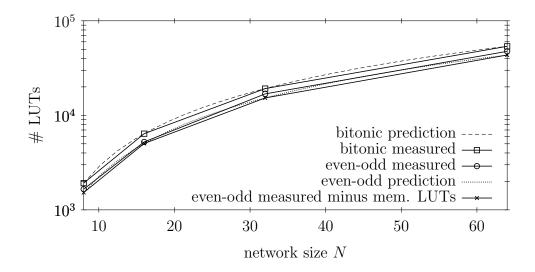

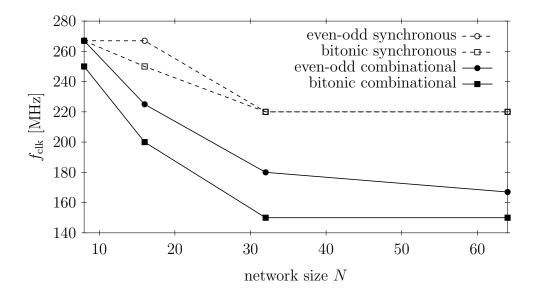

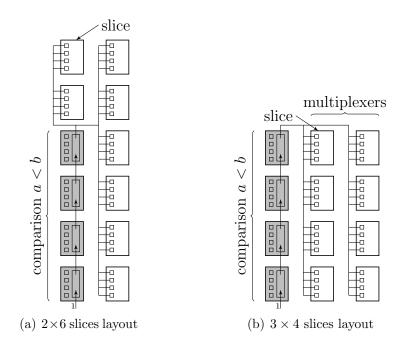

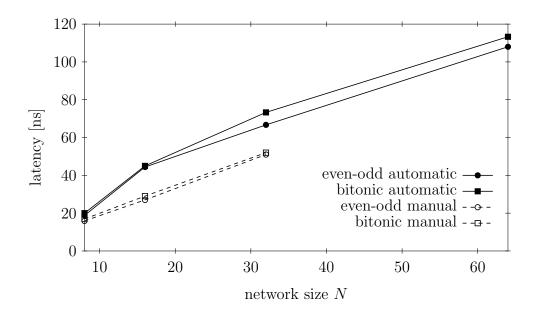

|   |     | 6.4.1  | Synchronous Implementations                                                                                                   |

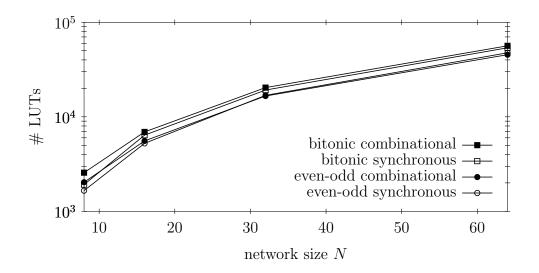

|   |     | 6.4.2  | Implementation based on Combinational Logic                                                                                   |

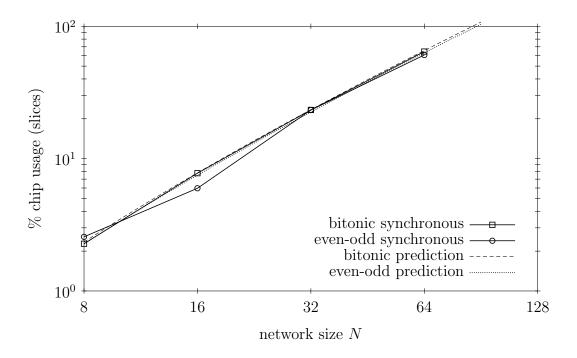

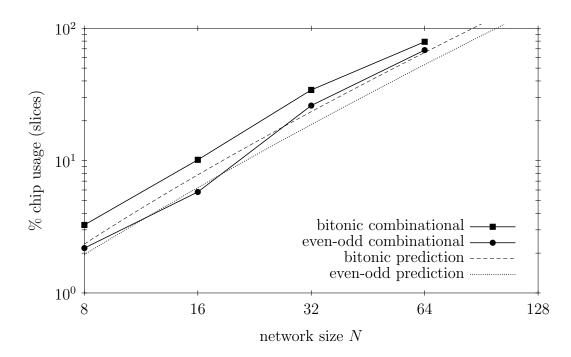

|   |     | 6.4.3  | Chip Usage                                                                                                                    |

|   |     | 6.4.4  | Circuit Performance                                                                                                           |

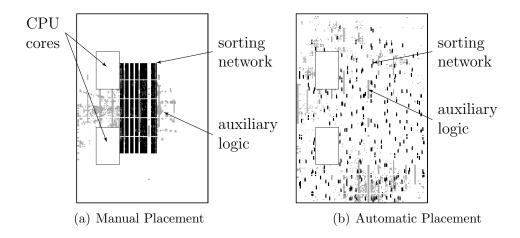

|   | 6.5 | Manua  | al Placement                                                                                                                  |

|   |     | 6.5.1  | Relative Location Constraints                                                                                                 |

|   |     | 6.5.2  | Placement of Sorting Network Elements                                                                                         |

|   |     | 6.5.3  | Performance of Manual Placement                                                                                               |

|   | 6.6 | Use C  | ase: A Streaming Median Operator                                                                                              |

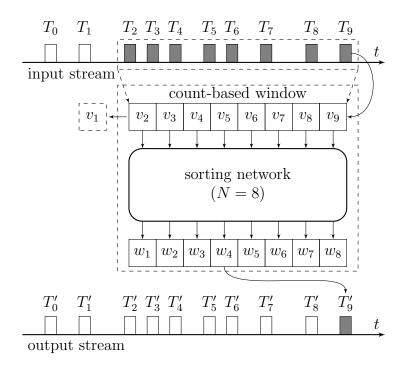

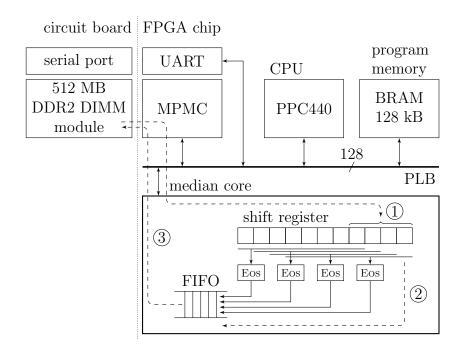

|   |     | 6.6.1  | An FPGA Median Operator                                                                                                       |

|   |     | 6.6.2  | System Design                                                                                                                 |

|   |     | 6.6.3  | System Overview                                                                                                               |

|   |     | 6.6.4  | Evaluation                                                                                                                    |

|   | 6.7 | Use C  | ase: A Sorting Co-Processor                                                                                                   |

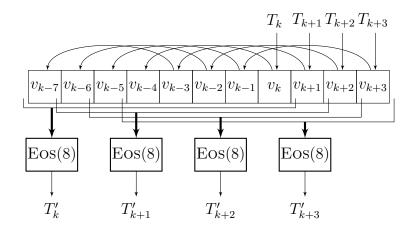

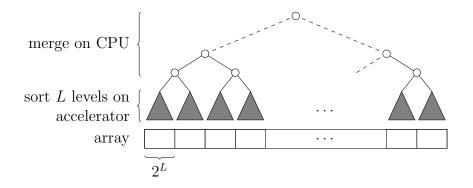

|   |     | 6.7.1  | Heterogeneous Merge Sort                                                                                                      |

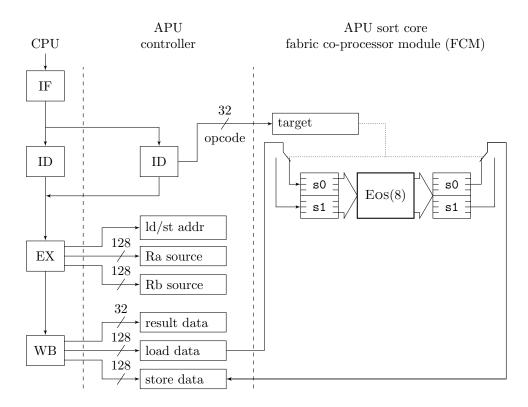

|   |     | 6.7.2  | Sorting Core connected to the CPU Execution Pipeline 208                                                                      |

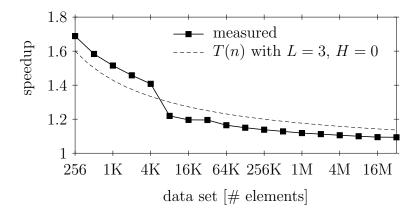

|   |     | 6.7.3  | Evaluation                                                                                                                    |

|   | 6.8 | Summ   | ary                                                                                                                           |

| 7 | Que | -      | Hardware Compiler213                                                                                                          |

|   | 7.1 |        | ns in Software $\ldots \ldots 214$ |

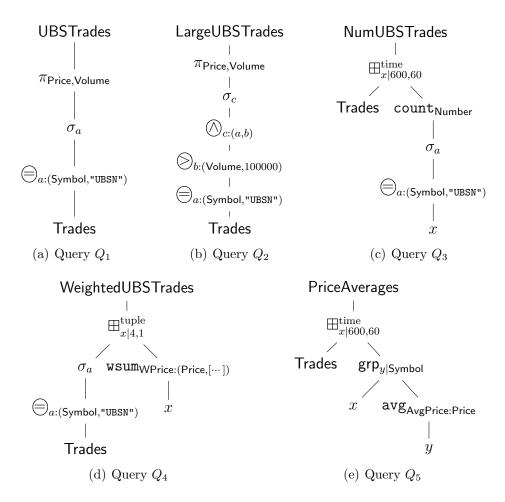

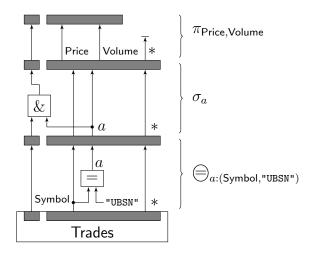

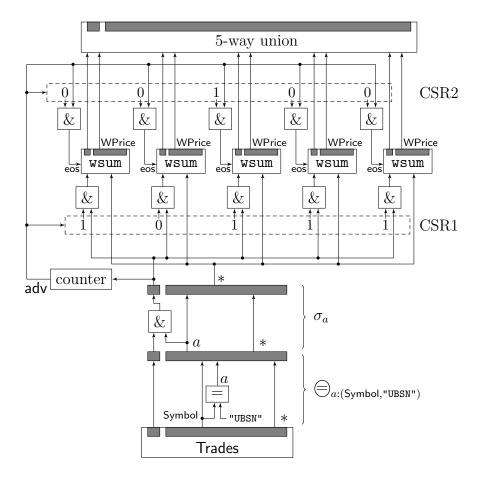

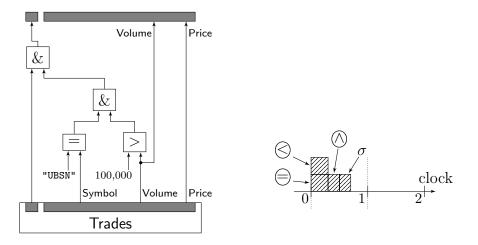

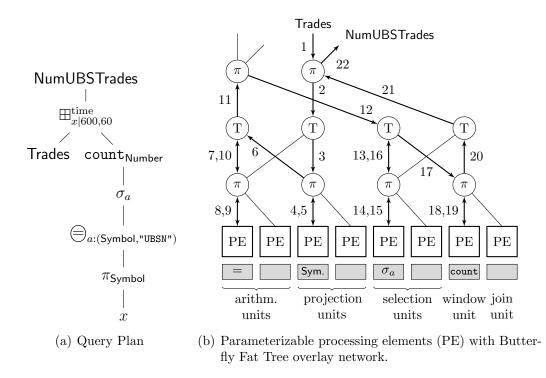

|   |     | 7.1.1  | Motivating Application                                                                                                        |

|   |     | 7.1.2  | Example Queries                                                                                                               |

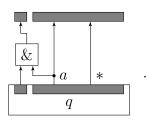

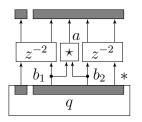

|   |     | 7.1.3  | Algebraic Plans                                                                                                               |

|   | 7.2 |        | as for Stream Processing                                                                                                      |

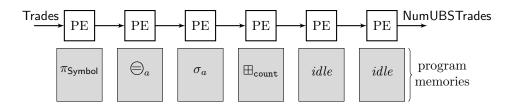

|   |     | 7.2.1  | System Setup                                                                                                                  |

|   |     | 7.2.2  | Query Compilation                                                                                                             |

|   | 7.3 |        | Queries to Circuits                                                                                                           |

|   |     | 7.3.1  | Wiring Interface                                                                                                              |

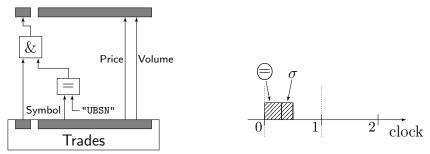

|   |     | 7.3.2  | Selection and Projection                                                                                                      |

|   |     | 7.3.3  | Arithmetics and Boolean Operations                                                                                            |

Х

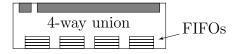

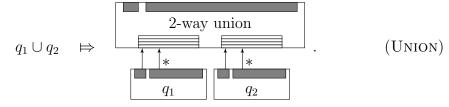

|   |      | 7.3.4   | Union                                  |

|---|------|---------|----------------------------------------|

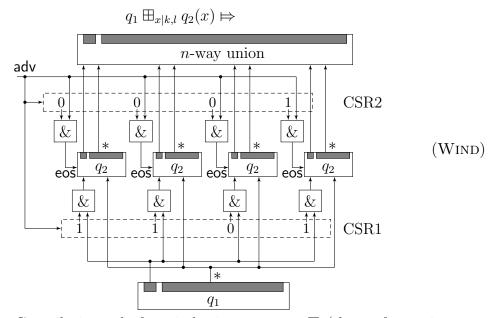

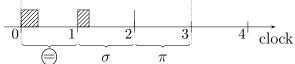

|   |      | 7.3.5   | Windowing                              |

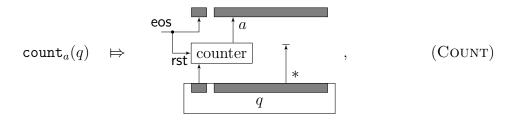

|   |      | 7.3.6   | Aggregation                            |

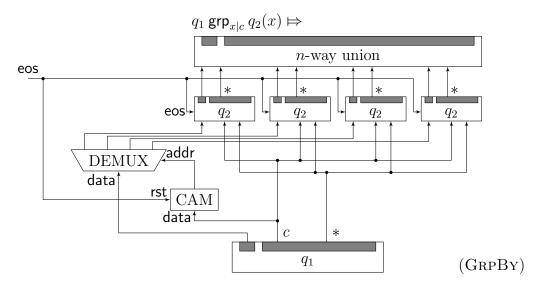

|   |      | 7.3.7   | Grouping                               |

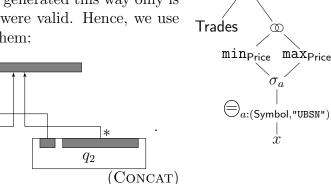

|   |      | 7.3.8   | Concatenation Operator                 |

|   | 7.4  | Auxilia | ary Components                         |

|   |      | 7.4.1   | Network Adapter                        |

|   |      | 7.4.2   | CPU Adapter                            |

|   |      | 7.4.3   | Stream De-Multiplexing                 |

|   | 7.5  | Optim   | ization Heuristics                     |

|   |      | 7.5.1   | Reducing Clock Synchronization         |

|   |      | 7.5.2   | Increasing Parallelism                 |

|   |      | 7.5.3   | Trading Unions For Multiplexers        |

|   |      | 7.5.4   | Group By/Windowing Unnesting           |

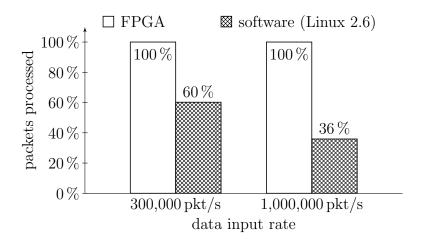

|   | 7.6  | Evalua  | tion                                   |

|   |      | 7.6.1   | Latency and Throughput                 |

|   |      | 7.6.2   | End-To-End Performance                 |

|   | 7.7  | Stream  | 1 Joins                                |

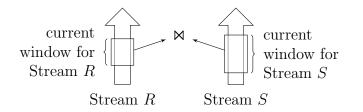

|   |      | 7.7.1   | Sliding-Window Joins                   |

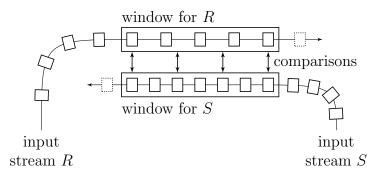

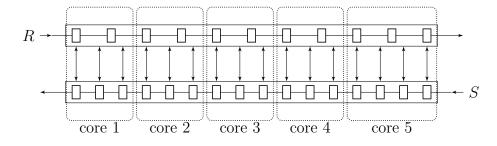

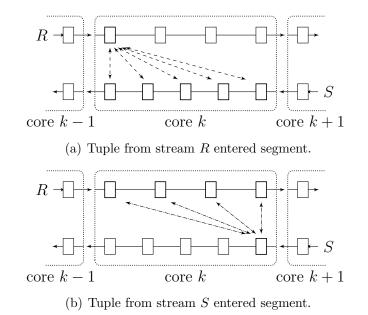

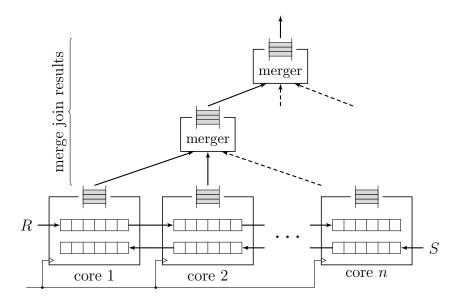

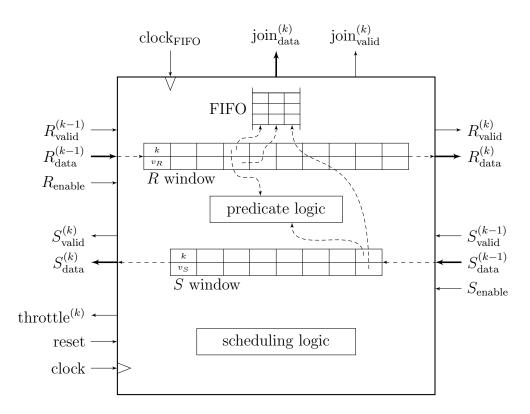

|   |      | 7.7.2   | Handshake Join                         |

|   |      | 7.7.3   | Handshake Join Implementation on FPGAs |

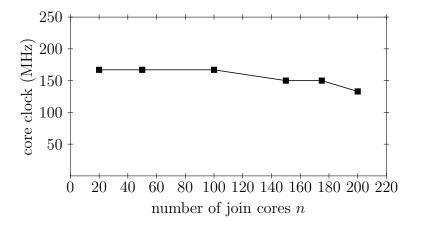

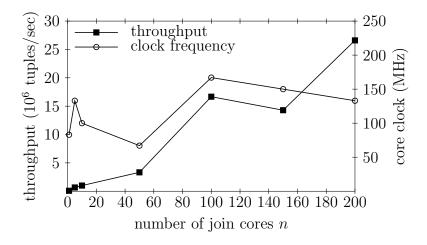

|   |      | 7.7.4   | Evaluation of Handshake Join Operator  |

|   |      | 7.7.5   | Optimal Number of Cores                |

|   | 7.8  | High-le | evel Architectures                     |

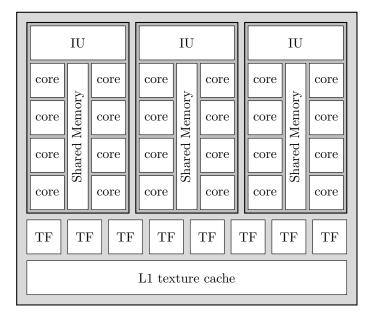

|   |      | 7.8.1   | Overlay Architectures                  |

|   |      | 7.8.2   | Graphic Processors                     |

|   | 7.9  | Relate  | d Work                                 |

|   | 7.10 | Summ    | ary                                    |

| 8 | Sun  | ımary   | and Conclusions 257                    |

|   | 8.1  | Query   | Processing in Sensor Networks          |

|   | 8.2  | Query   | Processing on FPGAs                    |

|   | 8.3  | Direct  | ions for Future Work                   |

# CONTENTS

xii

# Introduction

# 1.1 Motivation

**Data Stream Systems.** The proliferation of information systems as led to high data volumes that have to be transferred, processed, and stored. Databases increase in size and number, ranging from Google-scale systems to a large number of small federated databases in small and medium-sized enterprises. Next to traditional databases, data is increasingly available as (data) streams. Data streams are generated from many different sources, such as deeply embedded sensors, network monitoring systems, and financial systems.

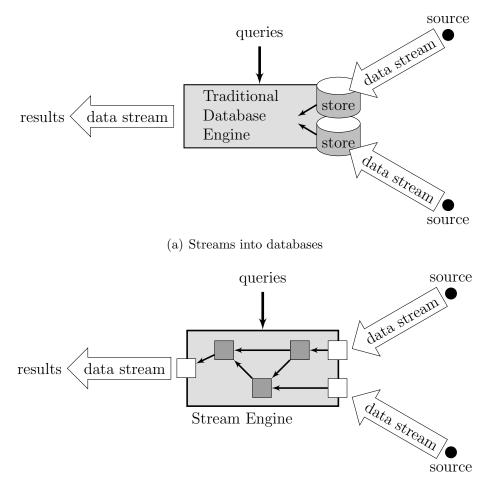

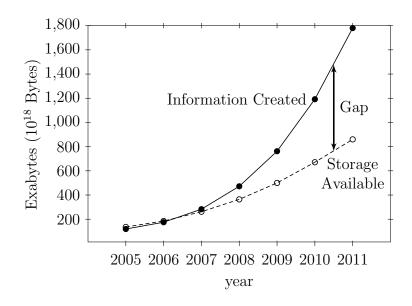

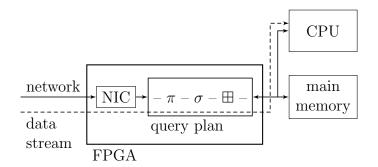

One approach to implement data stream processing is to use existing database technology as illustrated in Figure 1.1(a). The streams are stored in tables of a traditional database system such that conventional query processing can be performed through queries. There is, however, a steadily increasing amount of data produced. Figure 1.2 shows the development of the generated data volume and storage capacity as predicted by Gantz et al. [GCM<sup>+</sup>08]. There is a widening gap between the information generated and the available storage. This trend has led to *data stream processing systems*. Data streams are directly fed into the engine as shown in Figure 1.1(b) and processed on the fly through in a network of data operators. There are already many commercial stream processing systems available today [Str, Mic, Ora, Syb, Tru].

The approach used in these systems, as sketched in Figure 1.1(b), is based on two assumptions: (a) the streams can be brought into the engine, that is, there

(b) In-flight processing of data streams

Figure 1.1: Architectures for stream processing systems

is enough I/O bandwidth available, and (b) the engine has enough resources to process the data.

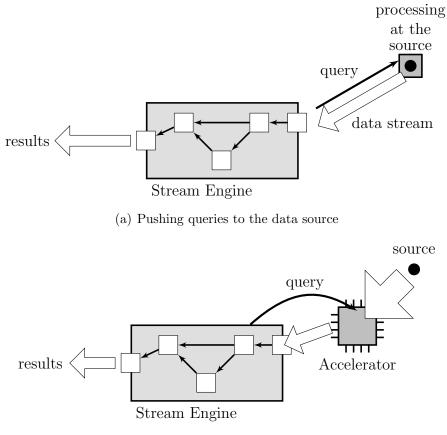

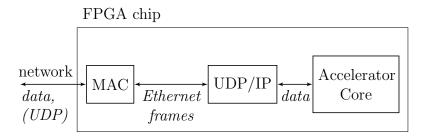

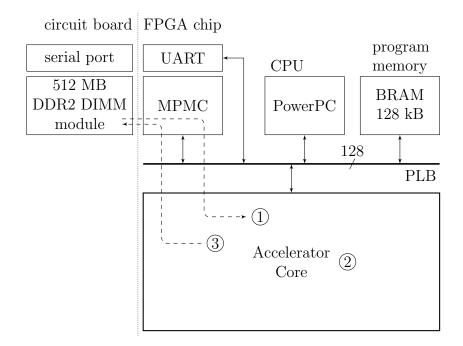

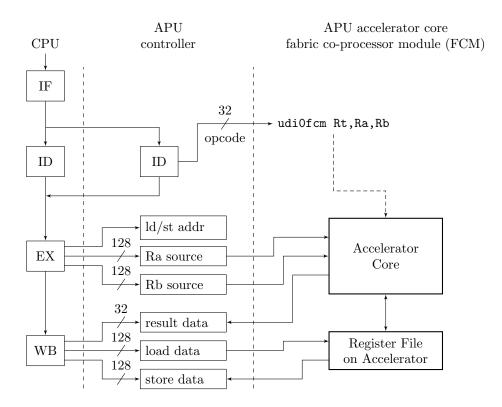

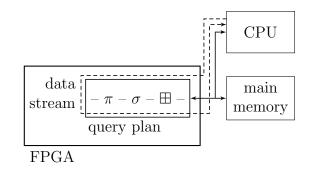

If this is not the case, part of the processing has to be offloaded. Stream processing typically contains filter operations, e.g., predicate queries, that select only a subset of the data and, hence, reduce data. This type of data reduction functionality can be ideally offloaded, as it not only removes part of the processing load from the central engine but also because it reduces the amount of data that needs to transferred. In practice, offloading means pushing part of the processing to the data sources as shown in Figure 1.3(a) or to an intermediary between the sources and the engine. Such an intermediary can be considered an accelerator that that sits on the data path between source and engine (Figure 1.3(b)). In the

Figure 1.2: Data Volume vs. Storage Capacity by Gantz et al. [GCM<sup>+</sup>08]

context of database processing these accelerators have been used on the I/O path to disks [Net09] or to the network [Net].

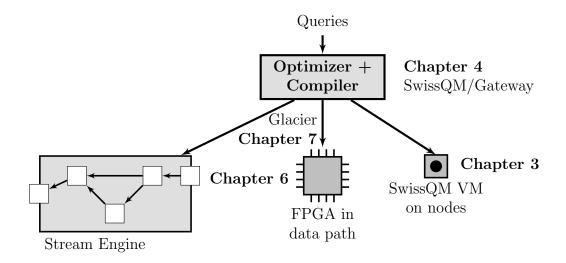

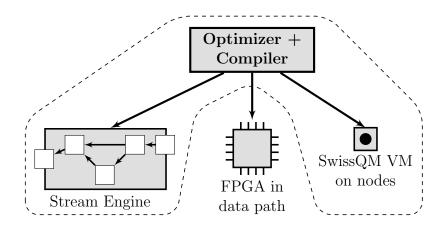

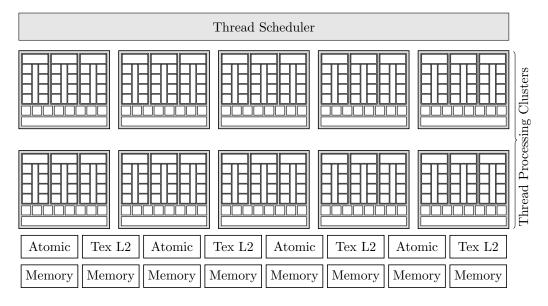

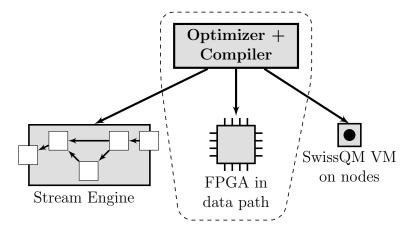

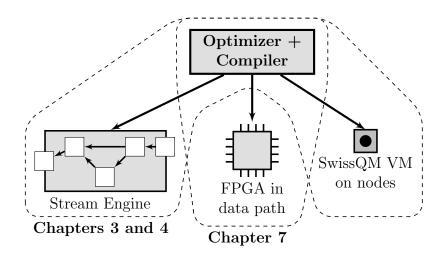

Streaming systems thus become heterogeneous as they not only include the core engine but also the accelerator and the actual data source. A query planner and optimizer needs to span multiple entities: the engine, an accelerator, and the data source. The ultimate goal is to have a common solution that autonomously distributes operations onto the elements of a such a heterogeneous system (Figure 1.4).

This thesis focuses on data stream processing on those heterogeneous platforms. It studies the problem of how the different characteristics of the individual subsystem can be be hidden from the user such that a general interface can be provided. It contributes to a unified stream processing solution that considers the costs and properties of the underlying platforms when generating query execution plans. Heterogeneous systems typically have very different cost models. An optimizer thus has to be able to decide *where* to place an operator in the query execution graph. This thesis contributes towards such a solution by extending stream processing onto two different execution platforms: *wireless sensor networks* (WSNs) and *field-programmable gate arrays* (FPGAs).

**Embedded Systems.** Moore's Law has not only resulted in faster CPUs and multi-core technology on commodity computers but had an impact on the embedded computing space. Small microcomputer systems equipped with sensor and ra-

(b) Processing streams on the data path

Figure 1.3: Heterogeneous architectures for stream processing systems

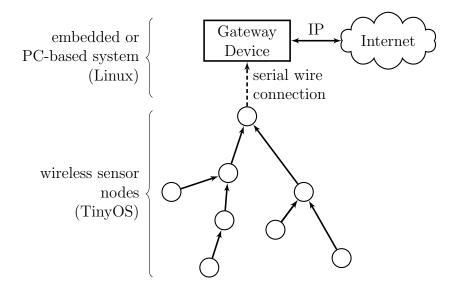

dio communication modules and powered by batteries have been deployed as wireless sensor networks [JOW<sup>+</sup>02,KDD04,LBV06,MCP<sup>+</sup>02,SJ04,THGT07,TPS<sup>+</sup>05]. They are not only capturing sensor data. Their microprocessors provide sufficient computation power such that they can also process data (e.g., filtering, smoothing, etc.) and selectively report data if the sensors detect an interesting pattern. As such they can contribute to stream processing. In the first part of this dissertation the wireless sensor networks are used for offloading query processing to the data source as illustrated in Figure 1.3(a).

The second part of the thesis discusses the accelerator approach shown in Figure 1.3(b). The accelerator is implemented on a field-programmable gate array (FPGA). FPGAs are "programmable" hardware that provide a number of logic gates that can be configured to implement any arbitrary digital circuit. They are widely used in the embedded system world. Programming, in this context means

Figure 1.4: Heterogeneous stream engine with offloading to data source and data path accelerator

essentially how to map data processing steps into digital circuits and onto FPGAs. FPGAs offer a high flexibility at a very low level and, unlike sensor networks, they cannot be programmed in the traditional way. Furthermore, they exhibit very different properties that have to be accounted for when designing FPGA circuits.

The thesis describes the different execution platforms and cost models used for query compilation for sensor networks and FPGAs. The goal for sensor network is maximizing the utilization of a deployment, i.e., providing concurrent access to multiple users, while minimizing the energy consumption or equivalently maximizing battery life. The optimization goal for FPGA-based accelerators is the minimization of latency or maximizing throughput. At the same time chip consumption has to be minimized.

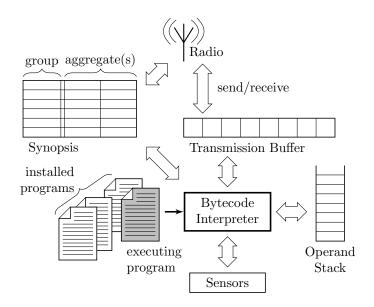

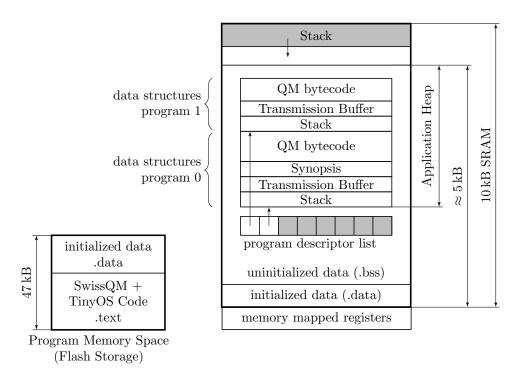

# **1.2** Contributions

In this dissertation the heterogeneous system shown in Figure 1.4 is envisioned. Users can submit queries, which are then partitioned on the underlying execution platforms, the main-memory stream engine, an FPGA, and the wireless sensor network. The type of execution plans depends on the platform. For FPGAs they are hardware circuits, for the sensor network they are bytecode programs. In summary, the thesis makes following contributions: Virtual Machine. As embedded systems, sensor networks are difficult to program. To large extend low-level programming is needed. In our approach we increase the abstraction level by providing a virtual machine that is deployed in the sensor network. We propose *SwissQM*, a stack-based virtual machine for resource-constrained sensor nodes. SwissQM was specifically designed and tailored to facilitate stream processing tasks. SwissQM can be used as application-specific virtual machine. Its instruction set can be extended with application-specific instructions. In general, SwissQM raises the abstraction level of network programming. Instead of using low-level programming languages, data processing tasks can be implemented using high-level bytecode macros.

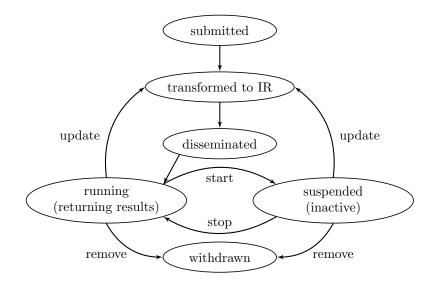

Query-to-Bytecode Compiler. The SwissQM virtual machine is used as an execution platform for streaming queries. Users can submit data collection tasks in the form of continuous queries to a gateway device that is connected to the sensor network. Queries are automatically compiled into bytecode sequences and are disseminated in the network. This first of all provides an even higher level of abstraction to the end-user. Since a declarative interface is used, no program has to be written at all. Second, the dissemination of execution plans as bytecode programs is very efficient and very flexible. For example, complex expressions and user-defined function can easily be compiled into bytecode.

**Cost Models.** Accurate cost models are built from a detailed analysis of the characteristics of the underlying hardware technology. For sensor networks we provide an energy-based cost model. Its parameters are identified by measurements of an real hardware.

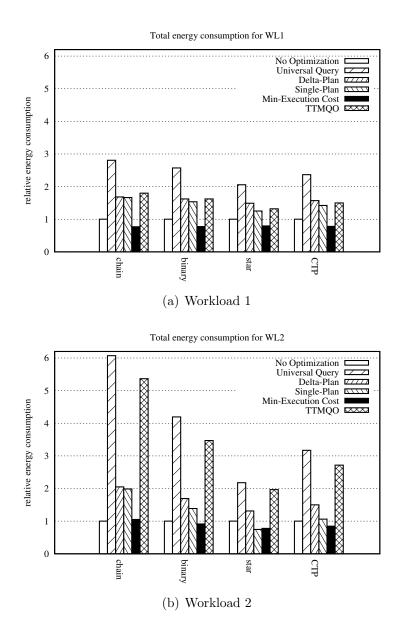

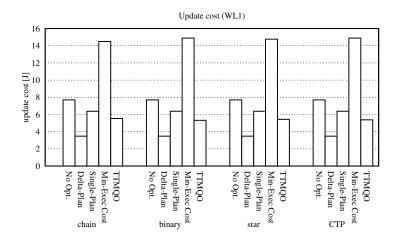

**Multi-query Optimization Strategies.** Using the cost model we provide different strategies to perform multi-query optimization to maximize utilization in sensor networks. We evaluate the strategies using different workloads and provide the resulting heuristics for an optimizer.

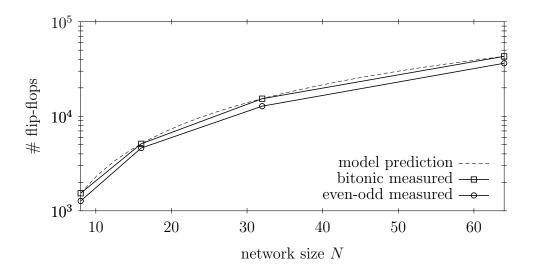

**Characterization of FPGA Computing.** We use *sorting networks* as a use case to characterize the properties of FPGAs as a processing platform. We present and validate a cost model of the chip usage in this context. We discuss the trade-offs of the different attachment methods of FPGAs to conventional computing systems. We also provide a set of design guidelines for the design of FPGA-based computing solutions.

**Query-to-Hardware Compiler.** We introduce a compositional algebra for data stream processing that can be used to express streaming queries. The algebra con-

### 1.3. STRUCTURE

sists of well-defined operators. The thesis describes *Glacier*, a hardware component library, that provides the necessary operators. The library provides operators for selection, projection, windowing, grouping, and window joins. Finally, a set of translation rules is presented that can be used to automatically translate plans expressed in this algebra into hardware circuits for FPGAs. This translation step for queries to FPGA-circuits is similar to the query-to-bytecode translation for sensor networks. In both cases, the abstraction level is raised from low-level, in case for FPGAs gate-level, programming to a high-level declarative interface.

# 1.3 Structure

The outline of the dissertation follows the architecture Figure 1.4. In detail, the dissertation is structured as follows:

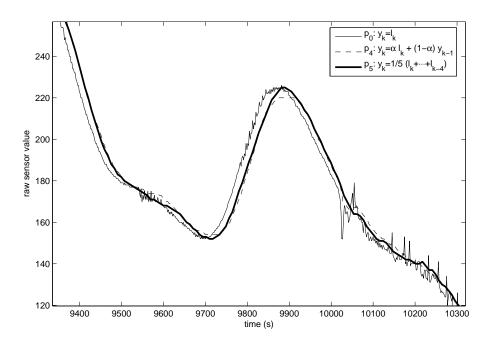

**Chapter 2** introduces wireless sensor networks. It describes the hardware platform, the constraints, and limitations. Through experiments we describe the behavior of the wireless communication channel and the implication on the design of the software stack.

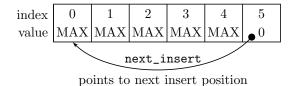

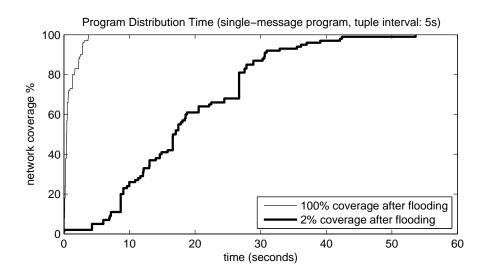

**Chapter 3** describes the design and implementation of the SwissQM virtual machine and the gateway system that performs the query-to-bytecode translation. The power and flexibility of SwissQM is illustrated through several examples of increasing complexity. The chapter also provides an evaluation of SwissQM in terms of execution performance, bytecode flexibility, and communication cost for program distribution.

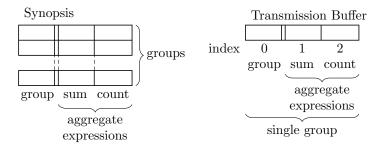

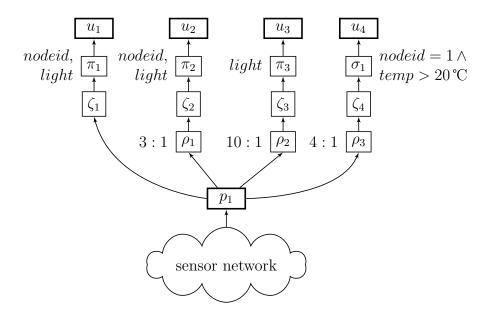

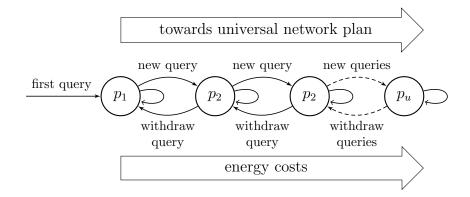

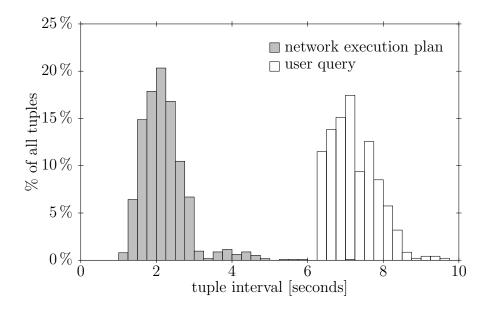

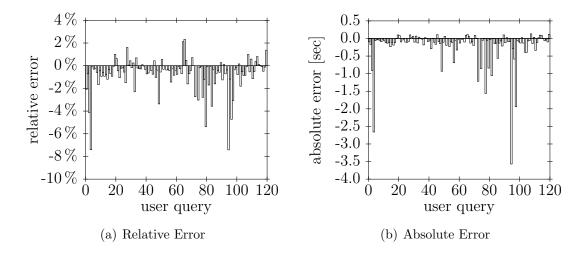

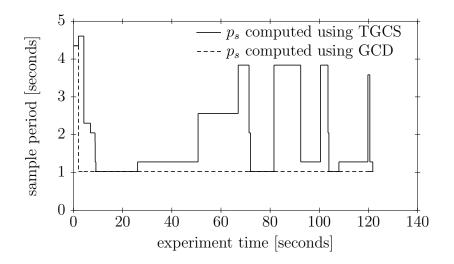

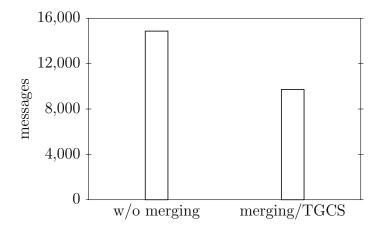

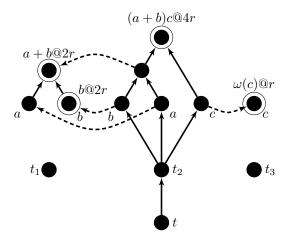

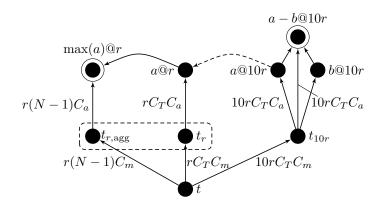

**Chapter 4** first introduces an energy-based cost model for sensor networks. Then it describes how several user queries can be combined into a single query. The problem of merging queries with different sampling rates is also addressed. In our approach, multi-query optimization is implemented in the query processor at the gateway. The query processor considers both execution costs as well costs for propagating workload updates into the network. Finally, different multi-query optimization strategies are presented and evaluated using sets of random queries. This completes the declarative query execution platform SwissQM for wireless sensor networks.

**Chapter 5** opens up the venue for the FPGA part. It provides an introduction into FPGAs and describes the building blocks that are used later in chapters 6 and 7.

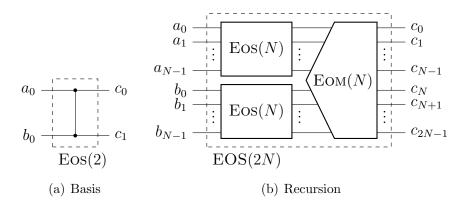

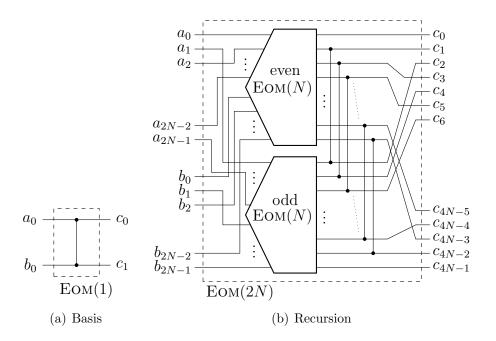

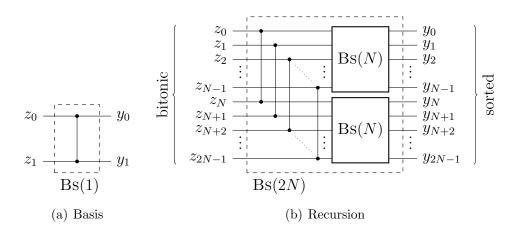

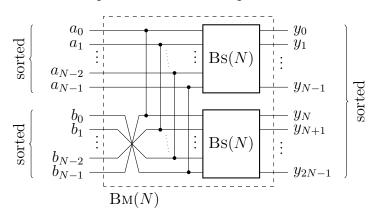

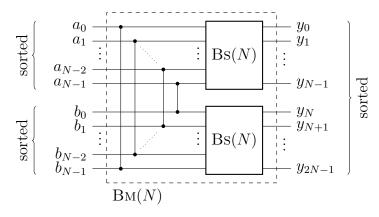

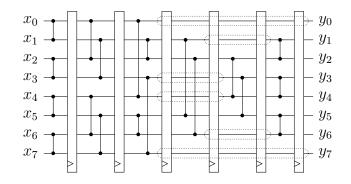

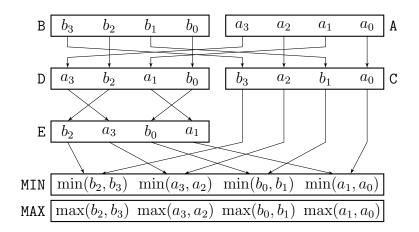

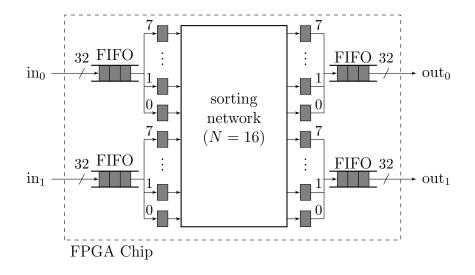

**Chapter 6** evaluates FPGAs as a computing platform using sorting networks as an example. It describes how sorting networks can be implemented on FPGA logic. The impact of different implementation strategies on the overall performance and space requirement is analyzed. Two different use cases are provided that show how the FPGA can be used in a complete system. For both systems we measure the end-to-end performance. The chapter provides insight in the design space of FPGA solutions. Techniques developed and evaluated in this chapter serve as a basis for the design of query-to-hardware compiler.

**Chapter 7** introduces the operator algebra for streaming queries. A set of translation rules is provided that can be used in a compositional way to translate queries, i.e., query plans expressed in this algebra, into hardware circuits. A number of operators is presented that are part of our *Glacier* component library. We provide optimization guidelines for the circuits that allow balancing latency against throughput. This chapter also presents *Handshake Join* our novel approach to window-based stream joins. An evaluation shows that this pipelining-based technique has excellent scalability characteristics. The chapter completes the FPGA aspect of the heterogeneous solution outlined in Figure 1.4.

**Chapter 8** takes up the original vision and contrasts it with the results obtained from SwissQM and Glacier. The chapter summarizes the thesis and discusses possible future work directions.

# Part I

# Data Stream Processing in Wireless Sensor Networks

# Data Processing in Wireless Sensor Networks

Thanks to Moore's law, the IT industry has seen computers getting smaller, cheaper, and more powerful during the last three decades. Now and in the coming years, computers are increasingly being enhanced with powerful sensing devices. Following Mark Weiser's *Pervasive Computing* paradigm [Wei99] computing devices are embedded into the physical world. They are extended with sensors and combined into *sensor networks* to tackle larger data acquisition tasks, e.g., monitoring the behavior of a large population of animals [MCP<sup>+</sup>02] or the climate of a large territory [THGT07]. Commercial applications of sensor networks include supply chain management [KDD04], support of elderly people [SJ04], and security facilities for manufacturing sites and homes.

Sensor networks typically employ wireless communication although there are several examples of wired sensor networks too. For example, wired sensors can be found in structural health monitoring applications and cars. In the context of the dissertation the nature of the wireless communication is explicitly considered. Properties related to sampling, and the quality of sensor readings, however, are equally important for wired sensor networks. In this dissertation only *wireless sensor networks* (WSN) are considered. For clarity the term "sensor networks" is often used interchangeably for WSNs.

Despite the numerous existing use cases, building and deploying sensor networks remain elusive and difficult tasks. Most existing deployments use applicationspecific, *hard-coded* software. Typically, there is little support for data independence, high level abstractions, multiple users, and, above all, integration with the higher layers of the data processing chain. Systems are also very rigid on how sensors can be programmed and what the sensor network can do.

In this chapter, we describe the characteristics of wireless sensor networks and introduce data processing for wireless sensor networks. The discussion begins with the different hardware platforms. Then we illustrate the properties of wireless communication and the resulting network architecture before we turn to data processing and declarative interfaces to WSNs, in particular, query processing. Section 2.3 covers the relevant related work.

# 2.1 Wireless Sensor Nodes

Wireless sensor networks consist of many—ranging from 10s to 100s, possibly 1000s—nodes. Each node has limited computing and communication capabilities. The nodes build a network using wireless communication that collectively perform a data acquisition or event detection task.

# 2.1.1 Hardware

The use of tiny wirelessly connected computing devices equipped with sensors was envisioned as *Smart Dust* by Hahn et al. in 1999 [KKP99]. They explored whether an autonomous sensing, computing, and communication system can packed into a device of a cubic-millimeter volume. Considering the small size they referred to the nodes as *motes* (small particles or specks). Their prototype was a microelectromechanical system (MEMS) with an optical communication component. Communication was implemented through small movable mirrors that deflect and modulate a laser beam. While "Smart Dust" was an interesting case study the design was highly experimental. Sensor nodes used later on were significantly larger in size, had more powerful microcontrollers, and used radio communication instead. Although roughly the size of a matchbox those later nodes were still called *motes*.

Many different note platforms are deployed today. In this dissertation the three different hardware types shown in Table 2.1 were used. The platforms have different properties. They contain different microcontrollers, communication chips and sensors. The microcontrollers used in Mica2 and Tmote Sky nodes provide comparable processing power. The amount of volatile memory used for program data is in the order of a few kilobytes. Tens of kilobytes of flash memory are available for program storage. The amount of RAM and flash memory directly limits the complexity of the software stack that can run on a node. Specific embedded operating systems and applications have the be carefully designed in order to fit onto these resource constrained devices. The newer Intel Imote2 node

|                 | Mica2                            | Tmote Sky                      | Imote2                         |

|-----------------|----------------------------------|--------------------------------|--------------------------------|

| microcontroller | Atmel ATmega128L                 | TI MSP430                      | Intel PXA271                   |

| RAM             | $4\mathrm{kB}$                   | $10\mathrm{kB}$                | $32\mathrm{MB}$                |

| Flash storage   | $128\mathrm{kB}$                 | $48\mathrm{kB}$                | 32 MB                          |

| radio chip      | CC1000                           | CC2420                         | CC2420                         |

| communication   | $916 \mathrm{MHz}, \mathrm{FSK}$ | IEEE 802.15.4                  | IEEE 802.15.4                  |

| radio bandwidth | 19.2  kbit/sec                   | 250  kbit/sec                  | 250  kbit/sec                  |

| max. power      | $5 \mathrm{dBm} (3 \mathrm{mW})$ | $0\mathrm{dBm}~(1\mathrm{mW})$ | $0\mathrm{dBm}~(1\mathrm{mW})$ |

| sensors         | light                            | light                          | light                          |

|                 | temperature                      | photo light                    | photo light                    |

|                 | microphone                       | temperature                    | 3D acceleration                |

|                 | (separate board)                 | humidity                       | 4 channel ADC                  |

|                 |                                  | (onboard)                      | (separate board)               |

| manufacturer    | Crossbow                         | moteiv                         | Intel/Crossbow                 |

| price           | CHF 290                          | $\mathrm{CHF}140$              | $\mathrm{CHF}640$              |

| introduction    | 2002                             | 2005                           | 2006                           |

Table 2.1: Characteristics of sensor node types used in this dissertation

shown in Table 2.1 contains a full-featured ARM CPU (PXA271) and significantly more memory. It is even able to run Linux and applications that use the Microsoft .NET Micro Framework.

Wireless sensor network typically operate in unlicensed ISM frequency bands. The motes shown in Table 2.1 use two different communication technologies. The older Mica2 platform uses a proprietary radio that operates in the 900 MHz ISM band. It uses *Frequency-shift Keying* (FSK) and Manchester coding. Operating at a symbol rate of 38.4 kbaud the resulting gross bit rate is 19.2 kbit/sec. The newer Tmote Sky and Imote2 nodes use a more energy-efficient radio technology and a physical layer that follows the IEEE 802.15.4 standard for personal area networks. Relying on a common standard permits interoperability between device families. The CC2420 transceivers operands on the 2.4 GHz ISM band that is shared with traditional 802.11bgn wireless LAN and Bluetooth. The transceiver complexity of the CC2420 is significantly larger than of the CC1000. It uses Direct-Sequence Spread Spectrum (DSSS) communication. Four bits are encoded into a pseudo-random sequence consisting of 32 chips. The chip sequences are modulated using Offset Quadrature Phase-shift Keying (OQPSK) at a rate of 2 MChips/sec resulting in a gross bandwidth of 250 kbit/sec. The use of spreadspectrum communication in the CC2420 instead narrow-band radio in the CC1000

provides additional robustness against noise and interference. This reduces the bit error rate and increases the overall reliability of the communication channels in the wireless network. Additional robustness is necessary as the same frequency band is occupied by different radio technologies (802.11 and Bluetooth, microwave ovens, etc.). However, the wireless communication channel is nevertheless much less reliable than communication over a wire. In the wireless case not only noise has to be considered but also fading effects, i.e., temporary fluctuations in the channel attenuation [TV05]. The packet loss probability can be reduced at the cost of increased overhead by reducing the packet sizes. For example, the lowpower personal area network standard IEEE 802.15.4 specifies a maximum payload length of 115 bytes of a single packet [IEE03]. The actual usage of the channel is 133 bytes ( $\approx 16\%$  overhead) including additional header and footer information. In contrast, traditional wireless LAN (unencrypted 802.11) supports payloads of up to 2304 bytes [IEE97]. The overhead per frame in 802.11 is 58 bytes including header and preamble bits ( $\approx 2.5\%$  overhead).

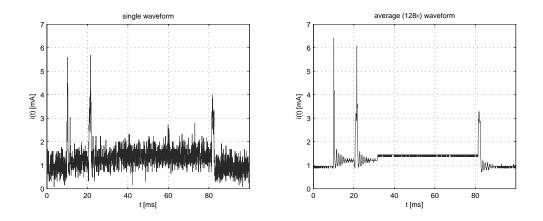

Sensor nodes are typically battery powered. In some cases they also use energy scavenging techniques. Most common is photovoltaic energy conversion through solar cells. Mechanical energy has also been used (vibrations and piezoelectric converters [RWR03]). In order to mitigate the difficulties of intermittent power generation the electrical energy is stored in secondary batteries or high capacity capacitors on the nodes. Wireless nodes have to be designed and—equally important—used very energy efficiently. This is particularly relevant for systems whose energy supply is based on primary batteries since replacing drained batteries is often difficult, e.g., in Alpine deployments [THGT07], or at all impossible.<sup>1</sup> In general, the lifetime of a deployment is given by the battery lifetime of its nodes. Therefore, all components of the notes have to be duty-cycled, i.e., turned off when they are not used in order to save energy. We provide a detailed analysis of the power breakdown for one hardware platform in Chapter 4.

The motes shown in Table 2.1 contain different sensors capturing various physical phenomena. Together with the built-in sensors the nodes can be considered as prototype systems that can be used in research. The quality of the sensors is in general not sufficient for scientific measurements. For example, the temperature sensors do not provide the necessary resolution and since they are mounted on the circuit boards the thermal coupling to the measurement environment is difficult. Nevertheless, the nodes can be used to acquire real measurements for prototype applications is system research focusing on routing and data processing. Specific

<sup>&</sup>lt;sup>1</sup>The Swiss Avalanche Research Institute operates a deployment of acoustic sensors (geophones) at the Wannengrat near Davos Switzerland. The sensors are covered by several meters of snow during the winter season. Digging out the sensors for a battery replacement would irreversibly damage the snow pack and destroy the measurement setup.

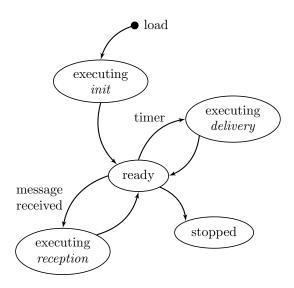

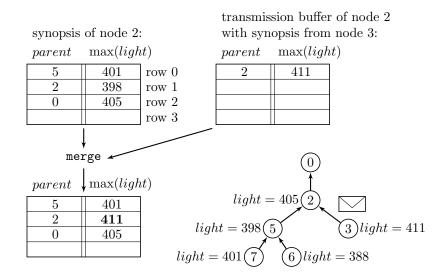

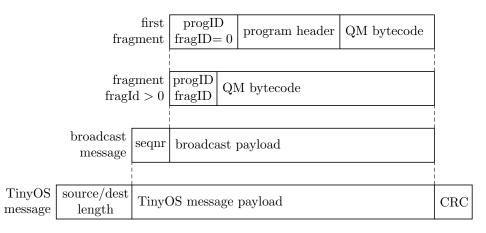

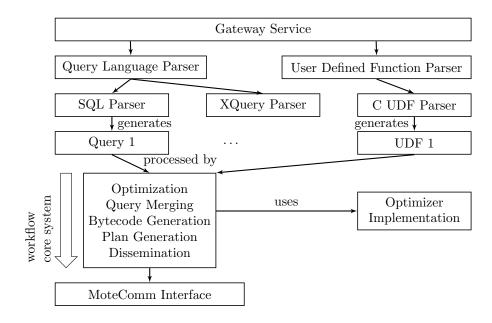

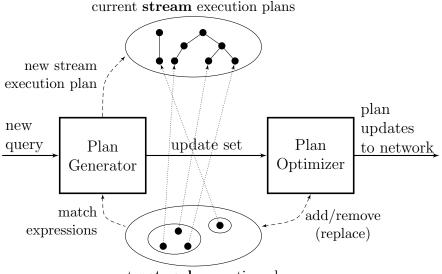

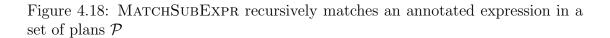

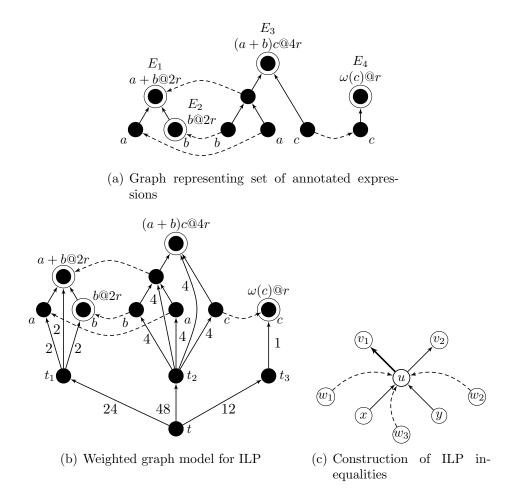

deployments such as the permafrost measurements in the Swiss Alps [THGT07] require custom designs and can only make limited use of off-the-shelf components. Experiments performed during this dissertation are done in a controlled lab setup using commodity nodes.