Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Uploaded by

Sai KrishnaCopyright:

Available Formats

Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Uploaded by

Sai KrishnaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro Systems

Uploaded by

Sai KrishnaCopyright:

Available Formats

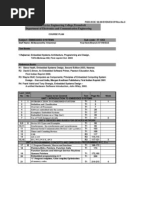

Proceedings of the 1999 Particle Accelerator Conference, New York, 1999

GPLS VME MODULE: A DIAGNOSTIC AND DISPLAY TOOL FOR NSLS MICRO SYSTEMS*

S.Ramamoorthy, J.D.Smith, BNL, Upton, NY

Abstract

The General Purpose Light Source VME module is an integral part of every front-end micro in the NSLS control system. The board incorporates features such as a video character generator, clock signals, time-of-day clock, a VME bus interrupter and general-purpose digital inputs and outputs. This module serves as a valuable diagnostic and real-time display tool for the micro development as well as for the final operational systems. This paper describes the functions provided by the board for the NSLS micro control monitor software.

2.1 Interrupt Generator

The interrupt generator on the board is capable of generating four interrupts on the VME bus. The input pins for the TIL level signals are on the P2 connector. Each interrupt can be independently enabled or disabled by software. The trigger edge (rising or falling edge of the input signal) and the interrupt level are independently programmable for each interrupt. All the four interrupts can share the same level.

2.2 Video Generator

The video section of the board can generate ASCII video that can be displayed on a TV monitor. The board can accept an NTSC signal from an external source and overlay the text data onto the original signal. It uses Dual Ported RAM that permits simultaneous VME-bus access with video character generation. The RAM provides 4 video pages and three memory pages (4 Kbytes each) for general- purpose use. Page selection can be done using the slider switch at the front panel. The video memory can be read and written at any time but only the selected page will be displayed. The video hardware provides four screen formats (12 lined16 char, 12 lined20 char, 16 lined32 char and 16 lined44 char). It has four programmable color palettes. Each color palette can be set up to one of 64 color shades (e.g. A value 0 will set the color palette to black, 63 to white, 3 to red, 12 to green, 48 to blue and so on). Foreground or background color can be programmed on a character by character basis. The character generator PROM on the board can be programmed for user-definable fonts.

1 INTRODUCTION

The front-end computers that interface with the hardware in the NSLS control system [ l ] are VME-based microprocessor systems. The minimum requirements to configure a system are a CPU board with Ethernet controller (68k series: Motorola mvme162 or power PC series: Motorola mv1603, mv1604, mv230x are used at present), one megabyte battery-backed-up memory board and a General Purpose Light Source board (referred to as GPLS board). Additional boards are dictated by the specific hardware or equipment to be controlled andor monitored. These systems are driven by real-time software known as the NSLS Control Monitor [2],[3]. This paper describes the hardware features of the GPLS board and how the software uses the various components.

2 HARDWARE DESCRIPTION

The GPLS board in use since 1987, was originally developed by the NSLS controls and diagnostic groups to provide bus interrupter and ASCII video display functions. As some of the components used by the board have become obsolete, a new GPLS board has been redesigned by Apogee Lab Inc.[4], following the specifications from the NSLS controls group. The new board (Apogee Lab: Model number VME-TVI) provides new features such its a time code reader and generator and enhanced video functions. The board can be accessed through an extended (A32:D16/DOS) or a standard (A24:D16/D08) address space of a VME-bus slave interface. The main components of the board are an interrupt generator, a video generator, a timer module and general-purpose inputs and outputs.

*Work performed under the auspices of U.S.Dept. of Energy under the contact no: DE-AC02-98CH10886.

2.3 Timer Module

The time module provides three clock signals (lkHz, 4 kHz and 250Hz) on the P2 connector and a time code reader and generator. The time generator can be operated in two modes. In the standalone mode, one can load Time into the registers of the generator and start it by software. In the synchronized mode, an external signal (amplitude modulated 1 kHz IRIG-B carrier) is input through the P2 connector. If the IRIG-B input is lost or corrupted, the board will free wheel and continues to provide the Time. The Time-of-Day information can be read in three words with one microsecond resolution.

0-7 803-5573-3/99/$10.00@ 1999 IEEE.

690

Authorized licensed use limited to: NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL. Downloaded on November 5, 2009 at 05:28 from IEEE Xplore. Restrictions apply.

Proceedings of the 1999 Particle Accelerator Conference, New York, 1999

2.4 Digital I/O

The other general purpose components are 16-bit LEDs on the front panel, two banks of DIP switches, each consisting of 8 switches and 32 I/O lines for parallel TIZ digital I/O (16 inputs and 16 outputs) on the P2 connector. More information on the board can be obtained from the user's manual supplied by Apogee Labs Inc.[S]. A transition module that will provide easy access to the various signals is also available from the same company.

3.2 Video Displays

The video feature of the GPLS board plays a very important role in the monitor software for micro development as well as for the final target systems. The simple MEMORY WRITE operation to generate an ASCII video display is very fast and can be used as a great debugging tool even in interrupt routines. The standard technique of using routines to send messages to a console (e.g. logtask in VxWorks) for diagnostic output is not sometimes suitable in interrupt or bus exception handlers. The system may crash even before the console output is initiated. Also programmers may have encountered cases where a software bug appears to have been removed by introducing the standard printf function for debugging. Since the console output is not synchronous with the code being executed, one can get a false indication of the bug location in the code when it crashes. The simple memory write on the video page exactly locates the problem area in the code. The software multiplexes the first hardware page to 8 software pages. When hardware page 0 is selected, the software will display one of the eight pages. The software page for the display can be changed easily either by a push-button on a panel connected to the micro or by a remote command from any workstation in the control system network. Both system and application tasks generate displays for diagnostics and for continuous monitoring of device parameters (analog read backs and digital status). Error conditions can be highlighted in yellow and red colors. Figures 1 to 3 show some typical displays from the micros. Since the board generates composite video (NTSC signal), one can monitor the displays on the local cable TV channels from anywhere in the lab. Some micros whose displays are crucial for operations have dedicated TV channels. Displays from other micros are routed through multiplexers to two general-purpose TV channels. The required display can be selected from any workstation. Since these displays are generated locally, the parameter updates are as fast as they are acquired and there is zero loading on the network. The hardware page 1 is used by the system task to dump the stack registers and other pertinent information captured when a micro encounters bus errors. Before resetting the micro, one can get some information on the crash from the display. Pages 2 and 3 are used by applications to display the hardware initialization and other diagnostics.

3 SOFTWARE INTERFACE

The control monitor software uses VxWorks which is a commercial real-time operating system. The software consists of a set of system tasks, interrupt handlers, application specific modules and hardware drivers. The system software is standard for all micros and manages the system hardware (GPLS board, etc.), communications, command decoding, etc. It provides system timing, and uses real-time OS primitives to synchronize and coordinate the activities of other tasks. This module isolates all the kernel specifics and system hardware interfacing from application modules and provides services to them for real-time control.

3. I'Tasks and interrupt handlers

The system timing has a resolution of 2 milliseconds and it is derived from the 1 kHz clock on the GPLS board. The clock signal is connected to the first interrupt pin to generate the timer interrupt. The monitor provides a wait routine (equivalent to sleep call in Unix) to the application tasks. The tasks can set a wait time as low as 2 milliseconds. The task delay (wait) does not have to rely on the granularity of the time ticks provided by the realtime OS. A second interrupt is generated every 8 milliseconds by connecting the 250 Hz clock to the second interrupt pin. This interrupt is used both by system and application software to start data acquisition (e.g. reading of ADC boards) and to signal events to other tasks. The system provides interrupt handlers for 2 external signals (usually from external hardware or from another micro). The external signals are fed to the third and fourth interrupt pins via the transition card. The handlers call the appropriate module to service the interrupt. The levels of these interrupts can be changed by software based on the request from the application tasks. The use of the GPLS board for generating timing, periodic interrupts and servicing external interrupts has made the software easily portable. Since the software does not use the CPU timers, there is no conflict with the realtime kernel timing. The software has been ported to different 68k series of CPU boards and Power PC boards and also from the RTUX real-time OS to VxWOrks OS with minimum changes in the system module and absolutely no change in the application code.

3.3 Time stamping

The board extracts the time-of-day information from the amplitude-modulated 1 kHz IRIG-B carrier available from one of the outputs of a Spectracom NetCLOCW2. This derives time from the atomic time standard at the National Institute of Standards and Technology via their WWVB

69 1

Authorized licensed use limited to: NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL. Downloaded on November 5, 2009 at 05:28 from IEEE Xplore. Restrictions apply.

Proceedings of the 1999 Particle Accelerator Conference, New York, 1999 radio broadcast at 60 kHz. The system module reads the three timer-registers every 250 milliseconds, decodes the Time-of-Day information and makes it available to other tasks. In addition, the time registers can be used to time a code segment (with an accuracy of + or - 4 microseconds) and display the value on a video page. The time data is also used to time stamp data or an event such as an occurrence of an alarm.

3.4 Digital I/O integace

The 16 LEDs are used for diagnostic purposes. Each task sets up different LEDs . This provides a quick indication if a task gets into a loop. One LED is used to generate heartbeat signal by application tasks. The DIP switches are used for setting up different configurations or modes of operation. One bank of switches is located on the board and is used to define configurations that cannot be accidentally altered. The front panel switches can be changed easily for the required mode of operation. As an example, one switch is assigned for controlling the parameter initialization during start-up. The micros save the parameters last set by the operators from a workstation, in the battery-backed-up memory. When the micro reboots following a reset, power-on or power-dip, it retrieves the battery-backed-up data for or the default values based on the switch setting. Another switch is used to inhibit the reporting of alarm messages. The digital inputs and outputs are used by the applications for various purposes. One of the outputs is connected to the system RESET pin. Using a software command one can initiate a system RESET. The outputs have also been used to generate interrupts by software to other micros or external hardware.

Figure 1. Display of radiation levels.

Figure 2. Display of XRFl signals.

4 CONCLUSIONS

The use of the GPLS board timers for system timing and interrupts by the software makes the porting of software to different VME-based CPU boards and to different realtime operating systems very easy. The video display serves as a great debugging tool during program development. The fast display of signal values and hardware status on TV without any load on the network are widely used for diagnostics and general monitoring by engineers, operators and physicists.

Figure 3. Display of VUV ring Parameters.

6. REFERENCES

[I] J.D.Smith, S.Ramamoorthy,Y.Tang.Nucl.Inst. and M e t h h Phys. Res, A32 (1994) 114. [2] SRamamoorthy, J.D.Smith, Proc.IEEE PAC 1993, 1849. [3] http://www.nsls.bnl.gov/Systems/Controls. [4] Apogee Lab Inc.,Dickerson Rd, Unit3/4, North Wales, PA19454. [5] Users Manual for TimeNideolIntermpt Module Model VME-TVI.

5 ACKNOWLEDGEMENT

The authors wish to thank Gary Frisbie for his technical support during the testing of the boards and to Dave Grebe of Apogee Lab for his constructive suggestions.

692

Authorized licensed use limited to: NATIONAL INSTITUTE OF TECHNOLOGY WARANGAL. Downloaded on November 5, 2009 at 05:28 from IEEE Xplore. Restrictions apply.

You might also like

- Mini Project DocumentationDocument43 pagesMini Project Documentationmgitecetech100% (6)

- Taking Care of Krishna DevoteesDocument185 pagesTaking Care of Krishna DevoteesSai Krishna100% (1)

- Onion and Garlic FactsDocument23 pagesOnion and Garlic FactsSai Krishna100% (1)

- Eng-Design of Open Architecture Ship-M.S. ZaghloulDocument18 pagesEng-Design of Open Architecture Ship-M.S. ZaghloulImpact JournalsNo ratings yet

- Pir Sensor Based Energy SaverDocument76 pagesPir Sensor Based Energy Saverk.aparna100% (1)

- ATM Terminal Design Based On Figure Print Recognition DocuDocument115 pagesATM Terminal Design Based On Figure Print Recognition DocuPraveen NaiduNo ratings yet

- Manual For Cycle 1Document193 pagesManual For Cycle 1Seth GreeneNo ratings yet

- Gui Based Liquid Indicator Using Cortex M3 For Industry Monitoring SystemDocument9 pagesGui Based Liquid Indicator Using Cortex M3 For Industry Monitoring SystemeditorijaiemNo ratings yet

- Mplab 1Document75 pagesMplab 1lingalashanthipriya_No ratings yet

- Data SheetDocument44 pagesData SheetDani SosaNo ratings yet

- Unit 1Document20 pagesUnit 1prabhavathysund8763No ratings yet

- Embedded SystemsDocument24 pagesEmbedded SystemsDileep KumarNo ratings yet

- Design of Programmable Logic Controller and I/O ExpansionsDocument5 pagesDesign of Programmable Logic Controller and I/O ExpansionsRanjan JlNo ratings yet

- 8051 LAB Manual NewDocument189 pages8051 LAB Manual New9491104570100% (2)

- Acknowledgement: DEVICE MANEGMENT SYSTEM" Has Given Us Immense PleasureDocument20 pagesAcknowledgement: DEVICE MANEGMENT SYSTEM" Has Given Us Immense PleasuresonalsrsNo ratings yet

- G7M Dr30aDocument12 pagesG7M Dr30aszjenterNo ratings yet

- Research Paper GPS Based Voice Alert System For The BlindDocument5 pagesResearch Paper GPS Based Voice Alert System For The BlindVenkata RatnamNo ratings yet

- An0043 Efm32 Debug Trace CapabilitiesDocument28 pagesAn0043 Efm32 Debug Trace CapabilitiesahimpliNo ratings yet

- CGC LAB MPDocument39 pagesCGC LAB MPJames ManningNo ratings yet

- Objective and AimDocument6 pagesObjective and AimSaadat ZaidiNo ratings yet

- Embedded System MaterialDocument143 pagesEmbedded System MaterialAnwesa Priyadarsini PradhanNo ratings yet

- IvrsDocument11 pagesIvrsMuskan JainNo ratings yet

- 0305 0310 PDFDocument6 pages0305 0310 PDFFahim AkterNo ratings yet

- Implementing Security in Industrial AutomationDocument63 pagesImplementing Security in Industrial AutomationKeerthi KeethuNo ratings yet

- Chapter-1: 1.1 Non Real Time Operating SystemsDocument58 pagesChapter-1: 1.1 Non Real Time Operating SystemsAnonymous XybLZfNo ratings yet

- Report 12 FinalDocument37 pagesReport 12 Finalkumar2005manojNo ratings yet

- Eng-Design of Open Architecture Ship-M.S. ZaghloulDocument20 pagesEng-Design of Open Architecture Ship-M.S. ZaghloulImpact JournalsNo ratings yet

- Electronics Project Automatic Bike Controller Using Infrared RaysDocument16 pagesElectronics Project Automatic Bike Controller Using Infrared RaysragajeevaNo ratings yet

- USER MANUAL Mab - 51Document93 pagesUSER MANUAL Mab - 51Pushpinder Singh KhalsaNo ratings yet

- Ai GETCPDocument9 pagesAi GETCPzrondjulNo ratings yet

- Tkbase + 2148 D-Board: Lpc2148 Training ManualDocument47 pagesTkbase + 2148 D-Board: Lpc2148 Training ManualMahesh BhatkalNo ratings yet

- Fault Tolerant Processor Using Hybrid Hardware RedundancyDocument24 pagesFault Tolerant Processor Using Hybrid Hardware RedundancyProject Symphony Collection100% (2)

- Embedded SystemsDocument144 pagesEmbedded SystemsUmesh KamathNo ratings yet

- Batch 8Document9 pagesBatch 8kota naikNo ratings yet

- GSM Based Car Engine Control System To Detect Car TheftDocument24 pagesGSM Based Car Engine Control System To Detect Car TheftPriya Ammu100% (1)

- RFID Based Museum Guide For TouristsDocument47 pagesRFID Based Museum Guide For Touristspraveen_kodgirwarNo ratings yet

- Microcontroller Lab ManualDocument127 pagesMicrocontroller Lab Manualsiri.pogula100% (2)

- Chap 03 Part1Document64 pagesChap 03 Part1oncerz93No ratings yet

- PIC LAB ManualDocument13 pagesPIC LAB ManualxyzzyzNo ratings yet

- Modicon Quantum - SOE SystemDocument4 pagesModicon Quantum - SOE SystemAgis Rijal AtmawijayaNo ratings yet

- Microcontroller (AT89S52) Based Remote Notice Board Using GSMDocument72 pagesMicrocontroller (AT89S52) Based Remote Notice Board Using GSMAkshayNo ratings yet

- (1 Introduction To Laboratory Hardware and ToolsDocument12 pages(1 Introduction To Laboratory Hardware and ToolsMalix ismNo ratings yet

- Ibs Vme6H Sc/I-T: Interbus Data SheetDocument8 pagesIbs Vme6H Sc/I-T: Interbus Data SheetprimaryrateNo ratings yet

- Voice Controlled Wheel ChairDocument48 pagesVoice Controlled Wheel ChairAjith manjuNo ratings yet

- CEIBO EB-251-Emulation Board: MCS 251 Suppor TDocument1 pageCEIBO EB-251-Emulation Board: MCS 251 Suppor TProf. Eng. Fabricio CouraNo ratings yet

- 1.2 Parts of A DAQ SystemDocument37 pages1.2 Parts of A DAQ SystemMaddipati SumanthNo ratings yet

- Unit I Embedded Computing: 2 Marks QuestionsDocument28 pagesUnit I Embedded Computing: 2 Marks Questionslogu87No ratings yet

- Ihm Exor PDFDocument4 pagesIhm Exor PDFMário Sérgio OliveiraNo ratings yet

- MCP Lab Manual C-16Document62 pagesMCP Lab Manual C-16siri.pogula67% (6)

- Cukurova University Faculty of Engineering and Architecture Department of Mechanical Engineering Experiment ReportDocument8 pagesCukurova University Faculty of Engineering and Architecture Department of Mechanical Engineering Experiment ReportSülbiye İşçi TemizciNo ratings yet

- Multi Level Security Based Access Control SystemDocument3 pagesMulti Level Security Based Access Control Systemprashant goreNo ratings yet

- Ucos + ArmDocument33 pagesUcos + Armசெல்வம் முத்துராமன்No ratings yet

- S.Y.B.Sc. IT (Sem - IV) - Embedded Systems PDFDocument112 pagesS.Y.B.Sc. IT (Sem - IV) - Embedded Systems PDFGowri Shankar100% (1)

- A PROJECT REPORT ON Electronic Voting MachineDocument97 pagesA PROJECT REPORT ON Electronic Voting Machinereddu143No ratings yet

- Traffic LightDocument18 pagesTraffic LightHarish KhanNo ratings yet

- ManholeDocument19 pagesManholeAbdul Razzak100% (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Success Stories 123Document90 pagesSuccess Stories 123Sai KrishnaNo ratings yet

- EkadashiDocument28 pagesEkadashiSai KrishnaNo ratings yet

- Art of Dealing With WomenDocument13 pagesArt of Dealing With WomenSai KrishnaNo ratings yet

- Eligibility Criteria EngDocument4 pagesEligibility Criteria EngumashankarsinghNo ratings yet

- Book 2Document12 pagesBook 2Sai KrishnaNo ratings yet

- TulasiDocument1 pageTulasiSai KrishnaNo ratings yet

- The Lotus FeetDocument9 pagesThe Lotus FeetSai KrishnaNo ratings yet

- ISKCON Desire Tree - Romapada SwamiDocument522 pagesISKCON Desire Tree - Romapada SwamiISKCON desire tree100% (3)

- Krishna Consciousness For YouthDocument27 pagesKrishna Consciousness For YouthSai Krishna100% (1)

- Chaitanya Mahaprabhu's Advent Predictions From Various VedicDocument101 pagesChaitanya Mahaprabhu's Advent Predictions From Various VedicSai Krishna100% (1)

- Words of Wisdom From Srila Bhaktisiddhanta Sarasvati ThakuraDocument1 pageWords of Wisdom From Srila Bhaktisiddhanta Sarasvati ThakuraSai KrishnaNo ratings yet

- Vaishnava SongsDocument124 pagesVaishnava SongsSai KrishnaNo ratings yet

- Are Men and Women EqualDocument10 pagesAre Men and Women EqualSai KrishnaNo ratings yet

- IBPS PO Booster PDFDocument1 pageIBPS PO Booster PDFvinee9999No ratings yet

- A Seminar On Personality DevelopmentDocument6 pagesA Seminar On Personality DevelopmentSai KrishnaNo ratings yet

- Mind ControlDocument11 pagesMind ControlSai KrishnaNo ratings yet

- Getting The Eyes To See GodDocument5 pagesGetting The Eyes To See GodSai KrishnaNo ratings yet

- Module 5Document35 pagesModule 5Azeem TopNo ratings yet

- uCOS-III-NXP-LPC1768 - The Real-Time KernelDocument838 pagesuCOS-III-NXP-LPC1768 - The Real-Time Kernelb3091035No ratings yet

- Sia 9Document3 pagesSia 9Arini KamaliaNo ratings yet

- 5.3 Task States and SchedulingDocument3 pages5.3 Task States and SchedulingkathirdcnNo ratings yet

- Chapter 4Document44 pagesChapter 4Girma MogesNo ratings yet

- 2nd Session Unit III 1Document26 pages2nd Session Unit III 1balakrishnaNo ratings yet

- RTOS ComparisonDocument4 pagesRTOS ComparisonPrabhakar CharyNo ratings yet

- Remote Terminal Unit With 8203 - Dual RS-485 Communications ModulesDocument220 pagesRemote Terminal Unit With 8203 - Dual RS-485 Communications ModulesАлександрNo ratings yet

- Industrial Training Report For AyobamiDocument22 pagesIndustrial Training Report For AyobamiemmaxadebanksNo ratings yet

- Unit-I-Operating System Overview and StructureDocument57 pagesUnit-I-Operating System Overview and StructureDiya KubalNo ratings yet

- Lesson Plan RTS Odd 2019Document3 pagesLesson Plan RTS Odd 2019Aravind RNo ratings yet

- Operating System FinalDocument14 pagesOperating System FinaljayaNo ratings yet

- Lecture 04: Realtime Operating Systems (Rtos)Document57 pagesLecture 04: Realtime Operating Systems (Rtos)MulugetaNo ratings yet

- FreeRTOS Task and Scheduler APIsDocument11 pagesFreeRTOS Task and Scheduler APIsbalacebNo ratings yet

- RtosDocument37 pagesRtosMalu MohanNo ratings yet

- OsDocument279 pagesOsshiddharthakumar2No ratings yet

- Types of Operating System: Submitted by Submitted ToDocument7 pagesTypes of Operating System: Submitted by Submitted ToAli RazaNo ratings yet

- POSIX and Linux Application Compatibility Final - V1.0Document19 pagesPOSIX and Linux Application Compatibility Final - V1.0Mahendra Pratap SinghNo ratings yet

- Important Questions of Information Technology BBA & B.Com With AnswersDocument60 pagesImportant Questions of Information Technology BBA & B.Com With AnswersRishit GoelNo ratings yet

- Porting The C-OS-II Real Time Operating System To The M16C MicrocontrollersDocument142 pagesPorting The C-OS-II Real Time Operating System To The M16C MicrocontrollersskalydNo ratings yet

- A Methodology For Customization of A Real-Time Operating System For Embedded SystemsDocument4 pagesA Methodology For Customization of A Real-Time Operating System For Embedded SystemsGustavo Nunes FerreiraNo ratings yet

- Francis Xavier Engineering College, Tirunelveli Department of Electronics and Communication EngineeringDocument8 pagesFrancis Xavier Engineering College, Tirunelveli Department of Electronics and Communication EngineeringImmanuel VinothNo ratings yet

- ComputerScience EngineeringDocument52 pagesComputerScience EngineeringdeepujobNo ratings yet

- Real Time Multitasking Con ArduinoDocument45 pagesReal Time Multitasking Con ArduinoRatrankNo ratings yet

- RTL Book1Document254 pagesRTL Book1api-3860349No ratings yet

- Chapter FourDocument73 pagesChapter FourAnonymous XNqKjnNo ratings yet

- Rtos QP MRDocument2 pagesRtos QP MRSandeepSharmaNo ratings yet

- Chapter 6: CPU Scheduling: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionDocument37 pagesChapter 6: CPU Scheduling: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionGul SherNo ratings yet

- Dokumen - Pub Embedded Realtime Systems Programming 9780070482845 0070482845Document320 pagesDokumen - Pub Embedded Realtime Systems Programming 9780070482845 0070482845Murat Yasar ERTASNo ratings yet

- Operating System 1 Com 311 Cte 223 ND 11 Ce HND 1 CSDocument1 pageOperating System 1 Com 311 Cte 223 ND 11 Ce HND 1 CSibraheemu60No ratings yet