Epo242 PDF

Epo242 PDF

Uploaded by

ikmalzaidan640Copyright:

Available Formats

Epo242 PDF

Epo242 PDF

Uploaded by

ikmalzaidan640Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Epo242 PDF

Epo242 PDF

Uploaded by

ikmalzaidan640Copyright:

Available Formats

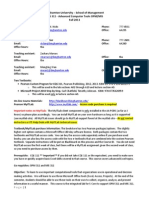

CONFIDENTIAL

EE/MAR 2012/EPO242

UNIVERSITI TEKNOLOGI MARA

FINAL EXAMINATION

COURSE

DIGITAL ELECTRONICS FUNDAMENTAL

COURSE CODE

EP0242

EXAMINATION

MARCH 2012

TIME

3 HOURS

INSTRUCTIONS TO CANDIDATES

1.

This question paper consists of five (5) questions.

2.

Answer ALL questions in the Answer Booklet. Start each answer on a new page.

3.

Do not bring any material into the examination room unless permission is given by the

invigilator.

4.

Please check to make sure that this examination pack consists of:

i)

ii)

the Question Paper

an Answer Booklet - provided by the Faculty

DO NOT TURN THIS PAGE UNTIL YOU ARE TOLD TO DO SO

This examination paper consists of 6 printed pages

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL

EE/MAR 2012/EPO242

QUESTION 1

a)

Convert the following numbers and codes into binary number.

i)

ii)

iii)

iv)

7E.B16

100000011001 BCD

11001011gray

0.210

(6 marks)

b)

Perform EA16 + 21 1 0 using binary addition. State the answer in octal.

(3 marks)

c)

Compute - 438 - 3616 using an eight bit 2's complement signed binary number

System. Provide the answer in decimal.

(5 marks)

d)

Assign proper even parity bit to the following code groups. A parity bit must be

appended to the right of each code.

101100,001000, 111001, 111111

(2 marks)

e)

Given a logic function F(A, B,C, D) = Z/w(4,5,7,12,13). Determine the followings:

i)

ii)

Maxterm function.

Simplified product of sum (POS) form using Karnaugh Map.

(4 marks)

QUESTION 2

a)

State two (2) Standard forms of Boolean Expression.

(2 marks)

b)

Simplify the following expression using Boolean Algebra and DeMorgan's Theorem.

Hence, implement the simplified function by using basic logic gates.

F (w, x, y) - (xy + xy)(w + x + y)

(5 marks)

c)

Provide the logic symbol, truth table and Boolean expression of 4 to 1 multiplexer.

(4 marks)

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL

d)

EE/MAR2012/EPO242

Figure Q2d shows the application of multiplier and logic gates. Multiplier is a device

to multiply 2 numbers (AiAo and B^o) and produce 4 product Outputs (P3P2PiPo)Complete the truth table in Table Q2d by referring to the application.

Figure Q2d

Table Q2d

X

0

0

0

0

1

1

1

1

Y

0

0

1

1

0

0

1

1

Po

Pl

p2

p3

0

1

0

1

0

1

0

1

(9 marks)

QUESTION 3

a)

Sequential logic circuit can be connected either in synchronous or asynchronous way.

Define synchronous and asynchronous connection and support your answer with

appropriate diagram.

(3 marks)

b)

Design a synchronous counter using positive edge triggering that counts through the

following counting sequence using JK flip flop and logic gates if required. The unused

state(s) is/are forced to don't care on the next dock pulse.

0"

->3

>2

>5

*4

*1

(11 marks)

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL

c)

EE/MAR2012/EPO242

Determine the counting sequence of the synchronous counter circuit in Figure Q3c by

completing the timing diagram up to 5 dock pulses. Assume the initial condition

Q2QiQo = 011.

iCt

L>2

u2

1

L>1

>

Qo

>

>

Q

CLK

Do

Qi

Q

1

'

Figure Q3c

(6 marks)

QUESTION 4

a)

Implement the following function using NAND gates only.

Z(A, B, C) = AB + BC + ABC

(4 marks)

b)

State two (2) advantages of R/2R Ladder DAC over Binary Weighted Resistor DAC.

(4 marks)

c)

The step size value for 4-bit Successive Approximation (SAC) ADC is 100 mV.

i)

ii)

Determine the digital Output for analog voltage, VA = 1.12 V.

Calculate the fll scale output.

(5 marks)

d)

Figure Q4d shows a 4 bit R/2R ladder DAC with R = 5 kO and Vref = 5V.

i)

ii)

iii)

Prove that V0 = Vref if the digital input is 1000.

Determine the step size.

Determine the resolution in percentage.

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL

EE/MAR2012/EPO242

Vo

Figure Q4d

(7 marks)

QUESTION 5

a)

The following object names are invalid identifier. Explain why.

i)

)

iii)

iv)

architecture

5question

x

y

element

(4 marks)

b)

Design a PROM structure for the function, F(A, B, C, D) = ABD + BC

(5 marks)

c)

Figure Q5c shows a 2 to 4 decoder with active high enable and active high Output.

The truth table for the decoder is given in Table Q5c(i).

i)

ii)

Write the entity declaration in VHDL for the device.

Complete the VHDL description for architecture declaration that uses sequential

Statements in Table Q5c(ii).

a0

2to4

decoder

ai

Z0

Zi

z2

en

z3

Figure Q5c

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL

EE/MAR2012/EPO242

Table Q5c(i)

en

0

1

1

1

1

ai

X

a0

0

0

1

1

0

1

0

1

Z0

0

1

0

0

0

Zi

z2

z3

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

Table Q5c(ii)

Architecture behaviour of

begin

process

if

,

case

end

is

begin

then

is

when

when

when

when others

_=>

_=>

<=

_=>

<=

=>

<=

z <= _

end case;

eise

z <= (others =>

end if;

end process;

;

) ;

(11 marks)

END OF QUESTION PAPER

Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

You might also like

- Httpseclass - Yorku.capluginfile - Php3581012mod - resourcecontent10FINAL-2022.pdf 2 PDFNo ratings yetHttpseclass - Yorku.capluginfile - Php3581012mod - resourcecontent10FINAL-2022.pdf 2 PDF9 pages

- IID2173 Digital Logic Design 41634 Final - Exam - QNo ratings yetIID2173 Digital Logic Design 41634 Final - Exam - Q8 pages

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignNo ratings yetII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design8 pages

- DIT Level 1 Computer Systems Architecture I - June Final Examination 2016No ratings yetDIT Level 1 Computer Systems Architecture I - June Final Examination 20163 pages

- Sample Question Paper Digital Techniques PDFNo ratings yetSample Question Paper Digital Techniques PDF5 pages

- WWW - Manaresults.co - In: (Common To CSE, IT)No ratings yetWWW - Manaresults.co - In: (Common To CSE, IT)2 pages

- ASSESSMENT BRIEF 2021-2022: Date of Submission: 15No ratings yetASSESSMENT BRIEF 2021-2022: Date of Submission: 1510 pages

- M.S. Software Engineering at Wipro Technologies (WASE) : 4Q X 5M 20marksNo ratings yetM.S. Software Engineering at Wipro Technologies (WASE) : 4Q X 5M 20marks2 pages

- Part - A Q1) A) Define Term Multimedia? Explain How Multimedia Data Is Represented?No ratings yetPart - A Q1) A) Define Term Multimedia? Explain How Multimedia Data Is Represented?1 page

- Ec2203-Digital Electronics Question BankNo ratings yetEc2203-Digital Electronics Question Bank22 pages

- Ama 2115 Mathematics for Science Computational MathsNo ratings yetAma 2115 Mathematics for Science Computational Maths3 pages

- Department of Geology College of Science Mosul University North Oil Company KirkukNo ratings yetDepartment of Geology College of Science Mosul University North Oil Company Kirkuk13 pages

- Department of Education: Walkthrough in Self-Learning Module (SLM) in Mathematics Grade/Level: 7 Quarter: - 1No ratings yetDepartment of Education: Walkthrough in Self-Learning Module (SLM) in Mathematics Grade/Level: 7 Quarter: - 14 pages

- Unesco - Eolss Sample Chapters: Thermochemical CyclesNo ratings yetUnesco - Eolss Sample Chapters: Thermochemical Cycles5 pages

- How Children, Adolescents and Adults Learn100% (1)How Children, Adolescents and Adults Learn23 pages

- Letter To Superintendent Mendez From Pan Am International HS Teachers, 2013No ratings yetLetter To Superintendent Mendez From Pan Am International HS Teachers, 20131 page

- Binghamton University - School of Management CQS 311 - Advanced Computer Tools OPM/MIS Fall 2013No ratings yetBinghamton University - School of Management CQS 311 - Advanced Computer Tools OPM/MIS Fall 20133 pages

- Harman Kardon AVR 635/AVR 435 Firmware/Software Upgrade InstructionsNo ratings yetHarman Kardon AVR 635/AVR 435 Firmware/Software Upgrade Instructions2 pages

- European Research Institute On Cooperative and Social EnterprisesNo ratings yetEuropean Research Institute On Cooperative and Social Enterprises38 pages

- Cisco UCS C240 Server Installation and Service GuideNo ratings yetCisco UCS C240 Server Installation and Service Guide160 pages

- School Form 2 (SF2) Daily Attendance Report of LearnersNo ratings yetSchool Form 2 (SF2) Daily Attendance Report of Learners3 pages

- Homosexual, He Is Promiscuous Cancer NavamsaNo ratings yetHomosexual, He Is Promiscuous Cancer Navamsa12 pages

- Httpseclass - Yorku.capluginfile - Php3581012mod - resourcecontent10FINAL-2022.pdf 2 PDFHttpseclass - Yorku.capluginfile - Php3581012mod - resourcecontent10FINAL-2022.pdf 2 PDF

- IID2173 Digital Logic Design 41634 Final - Exam - QIID2173 Digital Logic Design 41634 Final - Exam - Q

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design

- DIT Level 1 Computer Systems Architecture I - June Final Examination 2016DIT Level 1 Computer Systems Architecture I - June Final Examination 2016

- ASSESSMENT BRIEF 2021-2022: Date of Submission: 15ASSESSMENT BRIEF 2021-2022: Date of Submission: 15

- M.S. Software Engineering at Wipro Technologies (WASE) : 4Q X 5M 20marksM.S. Software Engineering at Wipro Technologies (WASE) : 4Q X 5M 20marks

- Part - A Q1) A) Define Term Multimedia? Explain How Multimedia Data Is Represented?Part - A Q1) A) Define Term Multimedia? Explain How Multimedia Data Is Represented?

- Ama 2115 Mathematics for Science Computational MathsAma 2115 Mathematics for Science Computational Maths

- Department of Geology College of Science Mosul University North Oil Company KirkukDepartment of Geology College of Science Mosul University North Oil Company Kirkuk

- Department of Education: Walkthrough in Self-Learning Module (SLM) in Mathematics Grade/Level: 7 Quarter: - 1Department of Education: Walkthrough in Self-Learning Module (SLM) in Mathematics Grade/Level: 7 Quarter: - 1

- Unesco - Eolss Sample Chapters: Thermochemical CyclesUnesco - Eolss Sample Chapters: Thermochemical Cycles

- Letter To Superintendent Mendez From Pan Am International HS Teachers, 2013Letter To Superintendent Mendez From Pan Am International HS Teachers, 2013

- Binghamton University - School of Management CQS 311 - Advanced Computer Tools OPM/MIS Fall 2013Binghamton University - School of Management CQS 311 - Advanced Computer Tools OPM/MIS Fall 2013

- Harman Kardon AVR 635/AVR 435 Firmware/Software Upgrade InstructionsHarman Kardon AVR 635/AVR 435 Firmware/Software Upgrade Instructions

- European Research Institute On Cooperative and Social EnterprisesEuropean Research Institute On Cooperative and Social Enterprises

- Cisco UCS C240 Server Installation and Service GuideCisco UCS C240 Server Installation and Service Guide

- School Form 2 (SF2) Daily Attendance Report of LearnersSchool Form 2 (SF2) Daily Attendance Report of Learners