Structural Diagram of 4 To 16 Decoder Components

Structural Diagram of 4 To 16 Decoder Components

Uploaded by

Anonymous xjG9nufVYBCopyright:

Available Formats

Structural Diagram of 4 To 16 Decoder Components

Structural Diagram of 4 To 16 Decoder Components

Uploaded by

Anonymous xjG9nufVYBOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Structural Diagram of 4 To 16 Decoder Components

Structural Diagram of 4 To 16 Decoder Components

Uploaded by

Anonymous xjG9nufVYBCopyright:

Available Formats

CECS 201 Computer Logic Design © 2013 R. W.

Allison

Xilinx Verilog Lab #3 – Spring 2013 Name ______________________________

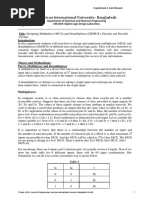

General Statement: You are to create a structural verilog module of a 4-to-16 decoder (named dec_4to16) using five

instances of a verilog module for a 2-to-4 decoder (named dec_2to4). Your verilog module for the 4-to-16 decoder will

have a 4-bit data input, (d[3:0]) and a 1-bit enable input (en). There will be one 16-bit output (y[15:0]). The 4-to-16

decoder is to be created using ONLY 2-to-4 decoders, having two 1-bit data inputs, a 1-bit enable input and four 1-bit

outputs. The purpose of this lab is to use “structural modeling” techniques with verilog. The “unconnected” structure of

the 4-to-16 decoder components, along with global/local inputs and outputs is illustrated in the diagram below:

Structural Diagram of

4‐to‐16 Decoder

dec_2to4

Components

d1 y3

d0 y2

y1

en y0

dec_2to4

d1 y3

d0 y2

y1

dec_2to4 en y0

4 16 global

d1 y3

d0 y2 outputs

d[3:0]

y1 dec_2to4 y[15:0]

en y0

d1 y3

global d0 y2

inputs y1

en y0

dec_2to4

en d1 y3

local local

d0 y2

inputs y1 outputs

en y0

Note: the “local” data inputs of the individual

2-to-4 decoder's (d1, d0) must be connected to

the appropriate “global” data inputs of the

4-to-16 decoder (d3, d2, d1, d0).

Deliverables: You are to turn in (1) this cover sheet, followed by (2) a printout of three verilog modules: the “top level”

(given on page 3), dec_4to16 and dec_2to4 modules, followed by (3) a printout of the simulation waveform (see p. 2).

Due Date: Thursday, April 11, 2013 {Thur. of week 11}

Verilog Lab # 3 – Page 1

CECS 201 Computer Logic Design © 2013 R. W. Allison

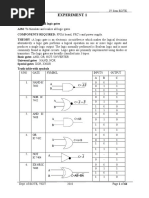

As mentioned previously, since the 4-to-16 decoder will be constructed with instances of a 2-to-4 decoder module which

you are to produce. The 2-to-4 decoder module may be designed either behaviorally or structurally. My suggestion is to

design it behaviorally, using a “case statement,” similar to what was done in the last lab assignment, (i.e. Verilog Lab 2).

Since the proper operation of the 4-to-16 decoder is dependent upon the proper operation of the 2-to-4 decoder, it will

save time to write a “throw-away” testbench to verify to operation of the 2-to-4 decoder before depending on it.

Once you are assured the 2-to-4 decoder module works correctly, write the verilog module for the 4-to-16 decoder

module, again, using five instances of module dec_2to4. Once you save the verilog file for the 4-to-16 decoder, the Xilinx

Project Navigator window should look something like below (depending on the name of your instances):

To verify the operation of the 4-to-16 decoder, create a testbench that assigns the four data inputs d[3:0] with all possible

combinations (0000 to 1111) while to enable input (en) is asserted (i.e. en=1). Following those 16 values, deasserted the

enable and set the data inputs to “xxxx.” Conclude the test vectors with the enable deasserted (i.e. en=0) and the data

inputs set to 0000. The correct output from the ISE Simulator is shown below.

Note that the 16-bit output, y[15:0], is being display in hexadecimal format for the sake of readability. In the graphic

above, the cursor (706.6 ns) is placed when to input to the decoder is binary “0111,” which should assert output y[7]. By

converting the output 0x0080 to binary 0000_0000_1000_0000, we verify that, in fact, only the y[7] output is asserted

while all other 15 outputs are deasserted.

Also note in the last two test vectors, when the enable input is deasserted (i.e. 0) none of the 16 outputs is asserted.

Verilog Lab # 3 – Page 2

CECS 201 Computer Logic Design © 2013 R. W. Allison

Top‐Level Verilog Module for FPGA Board Test

Unfortunately, the Nexys2 FPGA board does not have 16 LED’s to connect to the 4-to-16 decoder outputs. Thus, your

project is to include the following “top-level” module that will instantiate the dec_4to16 module and select either the

upper 8 outputs (i.e. y[15:8]) or lower 8 outputs (i.e. y[7:0]) to go to the 8 LED’s that are on the Nexys2 board:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////

// Company: CSULB_CECS_Dept

// Engineer: R. W. Allison

//

// Create Date: 19:56:32 01/15/2013

// Design Name: Verilog_Lab3_Spring2013

// Module Name: Verilog_Lab3_Top_Level

//

// Description: This purpose of this top-level module is to

// instantiate the 4-to-16 decoder and then select either

// the lower 8 outputs y[7:0] or upper 8 outputs of the

// (since we don't have 16 LED's) 4-to-16 decoder.

//

//////////////////////////////////////////////////////////////////////////

module Verilog_Lab3_Top_Level( d, enable, up8_lo8, leds );

input [3:0] d;

input enable, up8_lo8;

output wire [7:0] leds;

// used when instantiating the 4-to 16

wire [15:0] y;

//instantiate the 4-to-16 decoder module

dec_4to16 uut ( d, enable, y );

//the conditional assignment acts like a 2-to-1 MUX

// if (up8_lo8==1) leds = y[15:8] else leds = y[7:0]

assign leds = (up8_lo8 == 1) ? y[15:8] : y[7:0];

endmodule

Obviously, you must change the “Engineer,” “Create Date,” and “Design Name” fields in the comment header

appropriately, but the rest of the module must be typed in exactly as shown above, including the formatting.

Use the following specifications for the creation of your “constraints” file for the Nexys2 boards:

The inputs to the “top-level” module (d[3:0]) are to be connected to switches SW3 to SW0, respectively.

The enable input “enable” is to be connected to switch SW4.

The up8_lo8 select input is to be connected to switch SW7.

The outputs from the “top-level” module (leds[7:0]) are to be connected to LD7 to LD0, respectively.

Verilog Lab # 3 – Page 3

You might also like

- Rhetorical Analysis EssayDocument5 pagesRhetorical Analysis Essayapi-253584128No ratings yet

- Exadata Training Full SatyaDocument191 pagesExadata Training Full SatyaGanesh Ganeshan80% (5)

- MEAL Policies and Procedures-Updated PDFDocument4 pagesMEAL Policies and Procedures-Updated PDFGull Ahmad Mohammadi100% (1)

- Lab1 VHDLDocument9 pagesLab1 VHDLMishelzhitha CalderónNo ratings yet

- American International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderDocument4 pagesAmerican International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderAbid ChowdhuryNo ratings yet

- DLCmanual 4Document7 pagesDLCmanual 4Md Shamin YasarNo ratings yet

- ProgrammableLogicDesign NguyenTienThong 20200353Document4 pagesProgrammableLogicDesign NguyenTienThong 20200353Triệu HảiNo ratings yet

- Multiplexer and DemultiplexerDocument4 pagesMultiplexer and Demultiplexeranurag9122004No ratings yet

- Experiment # 10: DecoderDocument4 pagesExperiment # 10: DecoderPao JJNo ratings yet

- 03 DigitalComponentsDocument65 pages03 DigitalComponentskb24baller8No ratings yet

- Digital Logic Design Lab: Experiment No.Document8 pagesDigital Logic Design Lab: Experiment No.mdrubel miahNo ratings yet

- Lecture 3Document13 pagesLecture 3beshoymaherr1No ratings yet

- 05 - Combinational Logic Function BlocksDocument76 pages05 - Combinational Logic Function BlockskamhadidoNo ratings yet

- American International University-BangladeshDocument7 pagesAmerican International University-Bangladeshanon_776365175No ratings yet

- EncoderDocument10 pagesEncoderSiva Shankar0% (1)

- Lec 13 Encoders _ DecodersDocument36 pagesLec 13 Encoders _ Decodersi232578No ratings yet

- Chapter-4c - Encoders DecodersDocument31 pagesChapter-4c - Encoders DecodersMarkhor GamingNo ratings yet

- Avionics Lab - AjayDocument3 pagesAvionics Lab - AjayAIDEN WRISTNo ratings yet

- Experiment-5: Aim: To Write VHDL Code For 2:4 Decoder, Observe The Waveform and Synthesize The Code WithDocument2 pagesExperiment-5: Aim: To Write VHDL Code For 2:4 Decoder, Observe The Waveform and Synthesize The Code WithYidnekachwe MekuriaNo ratings yet

- D 6 F 7 G 8 BunimDocument71 pagesD 6 F 7 G 8 BunimAyman Ihab Saad AwadNo ratings yet

- Title:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10Document5 pagesTitle:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10MUNEEB SHAHNo ratings yet

- Exp 6Document13 pagesExp 6lkira8207No ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFDocument92 pagesFALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFChiranjeev Vishnoi 21BCT0043No ratings yet

- Combinatinal CircuitDocument22 pagesCombinatinal Circuitnaseemshaik.1133No ratings yet

- Sec a Encoder&DecoderDocument13 pagesSec a Encoder&DecoderVaishnavi PandeyNo ratings yet

- 271 6 PDFDocument5 pages271 6 PDFpriyanshiNo ratings yet

- Digital Experiment File With LogisimDocument4 pagesDigital Experiment File With LogisimNandini SeerviNo ratings yet

- 4-To-1 MUXDocument2 pages4-To-1 MUXMahijaNo ratings yet

- 4-To-1 MUXDocument2 pages4-To-1 MUXMahijaNo ratings yet

- Vivek MittalDocument27 pagesVivek Mittalvivek122No ratings yet

- Digital Logic Design Chapter 4: Combinational Function and Circuits 2 Semester BS ElectronicsDocument48 pagesDigital Logic Design Chapter 4: Combinational Function and Circuits 2 Semester BS Electronicsafzal khanNo ratings yet

- HDL Manual09-10Document64 pagesHDL Manual09-10tejasvivNo ratings yet

- Title: Multiplexer Instruction AimsDocument5 pagesTitle: Multiplexer Instruction Aimssuv_fame100% (1)

- Combinational Circuits - 3Document76 pagesCombinational Circuits - 3harshulyagnik.cseNo ratings yet

- Logic Design Module - 2Document45 pagesLogic Design Module - 2bodamaddyNo ratings yet

- Chapter 6 - Part B: Encoder: A Digital Circuit That Priority Encoder: An Encoder ThatDocument5 pagesChapter 6 - Part B: Encoder: A Digital Circuit That Priority Encoder: An Encoder Thatpp003No ratings yet

- DLC LAB_04_student_manual_Spring 2023-24Document7 pagesDLC LAB_04_student_manual_Spring 2023-24nono nanaNo ratings yet

- HDL Manual 2020 5th Sem E&CE 18ECL58Document74 pagesHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaNo ratings yet

- 4-Fold Selection Element 42 500 Safety-RelatedDocument4 pages4-Fold Selection Element 42 500 Safety-RelatedRogerio SouzaNo ratings yet

- DLD Lab 7Document5 pagesDLD Lab 7Tausif AhmedNo ratings yet

- Lab Worksheet # 9Document6 pagesLab Worksheet # 9MUNEEB SHAHNo ratings yet

- 4-Fold Output Module 22 100 Safety-Related: 1 F 1 F 1 F 1 F 1 F 1 F 1 F 1 FDocument4 pages4-Fold Output Module 22 100 Safety-Related: 1 F 1 F 1 F 1 F 1 F 1 F 1 F 1 FGilberto Alejandro Tun BritoNo ratings yet

- DLD Manual EEDocument9 pagesDLD Manual EEMuhammad Umer ShakirNo ratings yet

- Lecture8 1 (CL Examples)Document5 pagesLecture8 1 (CL Examples)litoduterNo ratings yet

- Data-Processing Circuits 3.2Document83 pagesData-Processing Circuits 3.2DEEPAK UPADHYAYNo ratings yet

- Examples on Triple Integrals with Cylindrical Coordinates-Fall2024Document2 pagesExamples on Triple Integrals with Cylindrical Coordinates-Fall2024M.SNo ratings yet

- Session - 06 - Encoder DecoderDocument16 pagesSession - 06 - Encoder DecoderArnoldNo ratings yet

- ALPS 2337 Maths Assignment PaperDocument10 pagesALPS 2337 Maths Assignment PaperSujal KapoorNo ratings yet

- ELEC2141 Combinational Circuit Building BlocksDocument36 pagesELEC2141 Combinational Circuit Building Blocks刘浩灵No ratings yet

- Experiment:9 ,:, AIM:-Software Used: - TheoryDocument10 pagesExperiment:9 ,:, AIM:-Software Used: - TheoryAshwani kumar kushwahaNo ratings yet

- Digital Logic Design Exp. No. 10-1Document21 pagesDigital Logic Design Exp. No. 10-1Abbas RaxaNo ratings yet

- (C) 2017 Second Wind Productions, LLC: (S) Values in Fractional FormDocument21 pages(C) 2017 Second Wind Productions, LLC: (S) Values in Fractional FormAhsan AliNo ratings yet

- Decoder TocciDocument25 pagesDecoder ToccimohitNo ratings yet

- Simple RTL PipelineDocument7 pagesSimple RTL PipelinepawanzNo ratings yet

- EncoderDocument3 pagesEncoderMahijaNo ratings yet

- DLD 03 Comb Logic Design Part1Document22 pagesDLD 03 Comb Logic Design Part1Ishmam BhuiyanNo ratings yet

- Module 3 STDDocument93 pagesModule 3 STDmatlabdec12No ratings yet

- Encoders and Decoders in Digital LogicDocument6 pagesEncoders and Decoders in Digital LogickroyombatiNo ratings yet

- VHDL Lab1 PDFDocument9 pagesVHDL Lab1 PDFOluwole Abraham FajuyiNo ratings yet

- IT212 - Lecture 8 - Decoders & EncodersDocument75 pagesIT212 - Lecture 8 - Decoders & EncodersAhmed AlaaNo ratings yet

- TOLEXO - 2019 Passing Out Batch (Only For Eligible & Unplaced Students)Document2 pagesTOLEXO - 2019 Passing Out Batch (Only For Eligible & Unplaced Students)Anonymous xjG9nufVYBNo ratings yet

- Blue DrawingDocument358 pagesBlue DrawingAnonymous xjG9nufVYBNo ratings yet

- Railway Signalling and Telecommunication: Industrial Traning ReportDocument44 pagesRailway Signalling and Telecommunication: Industrial Traning ReportAnonymous xjG9nufVYBNo ratings yet

- Anant Seminar Report On WiTricityDocument4 pagesAnant Seminar Report On WiTricityAnonymous xjG9nufVYBNo ratings yet

- UserCustom DeviceProfile PDFDocument1 pageUserCustom DeviceProfile PDFAnonymous xjG9nufVYBNo ratings yet

- UserCustom DeviceProfile PDFDocument1 pageUserCustom DeviceProfile PDFAnonymous xjG9nufVYBNo ratings yet

- Digital Signal Processing by KrishnaDocument303 pagesDigital Signal Processing by Krishnakrishna chaithanyaNo ratings yet

- 2 Transferred Electron DevicesDocument34 pages2 Transferred Electron DevicesAnonymous xjG9nufVYBNo ratings yet

- Grade 10 Math Performance Task Practice Test Scoring Guide Lights Candles ActionDocument20 pagesGrade 10 Math Performance Task Practice Test Scoring Guide Lights Candles ActionMaychelle TañezaNo ratings yet

- MadhwanaamaDocument99 pagesMadhwanaamaSathya Shree100% (1)

- Topic 2 - Nursing ProcessDocument36 pagesTopic 2 - Nursing ProcessJoshua MendozaNo ratings yet

- Passive Voice SheetsDocument6 pagesPassive Voice Sheetsgermine ahmedNo ratings yet

- Cyberpsychology, Behavior and Social NetworkingDocument12 pagesCyberpsychology, Behavior and Social NetworkingLIAN BENJAMN OGANDO PAULINONo ratings yet

- Exam-Style Question:: Mathematical ModellingDocument4 pagesExam-Style Question:: Mathematical ModellingFadi AyyoubNo ratings yet

- Acids and Bases WorksheetDocument2 pagesAcids and Bases WorksheetNickole PeraltaNo ratings yet

- Polygon Poster RubricDocument2 pagesPolygon Poster Rubricapi-265434395100% (1)

- Why Nothing Appear When You Take A Photo of An YogiDocument3 pagesWhy Nothing Appear When You Take A Photo of An YogiBradley MitchellNo ratings yet

- Soal Integrated EnglishDocument3 pagesSoal Integrated Englishjudith febiola0% (1)

- Trolo LolDocument7 pagesTrolo LolAnonymous P1iMibNo ratings yet

- The Freedom Model 5Document6 pagesThe Freedom Model 5wifihad458No ratings yet

- Sarab's ProjectDocument83 pagesSarab's ProjectSarbmeet KhillanNo ratings yet

- House (Individual House/Apartment) Rental Management SystemDocument6 pagesHouse (Individual House/Apartment) Rental Management SystemjanscarletTM uzamakiNo ratings yet

- Secd 03Document495 pagesSecd 03nawabrpNo ratings yet

- Unit 4Document2 pagesUnit 4My T.No ratings yet

- Development of Communication TechnologyDocument4 pagesDevelopment of Communication TechnologyGedhe PratamaNo ratings yet

- Albert SangDocument132 pagesAlbert SangadderpanNo ratings yet

- Where The Mind Is Without FearDocument2 pagesWhere The Mind Is Without FearabdulmusaverbhNo ratings yet

- Eng - Common Punctuation MarksDocument21 pagesEng - Common Punctuation MarksBeatrice Musiimenta Wa MpireNo ratings yet

- Operational Modal Analysis Tutorial - Svib Seminar May 2007Document12 pagesOperational Modal Analysis Tutorial - Svib Seminar May 2007HOD MECHNo ratings yet

- Freedom of Religion Under The Malaysian Federal ConstitutionDocument19 pagesFreedom of Religion Under The Malaysian Federal ConstitutionSarah Nadia100% (1)

- Laws and Practices - Why Do The Shiah Combine PrayersDocument4 pagesLaws and Practices - Why Do The Shiah Combine PrayersShahid.Khan1982100% (1)

- Robin DiAngelo's 'White Fragility' Ignores The Differences Within WhitenessDocument4 pagesRobin DiAngelo's 'White Fragility' Ignores The Differences Within WhitenessgaryrobertNo ratings yet

- ReferencesDocument4 pagesReferencesapi-691509991No ratings yet

- 2017 FVDocument17 pages2017 FVdanny leeNo ratings yet

- Conor MedsystemsDocument6 pagesConor MedsystemsAndrii DutchakNo ratings yet