CAO IAT 2 QP 2019 Set 2

CAO IAT 2 QP 2019 Set 2

Uploaded by

formyphdCopyright:

Available Formats

CAO IAT 2 QP 2019 Set 2

CAO IAT 2 QP 2019 Set 2

Uploaded by

formyphdOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

CAO IAT 2 QP 2019 Set 2

CAO IAT 2 QP 2019 Set 2

Uploaded by

formyphdCopyright:

Available Formats

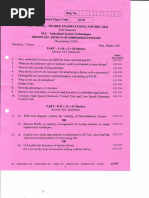

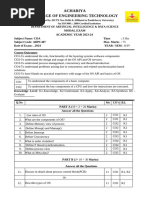

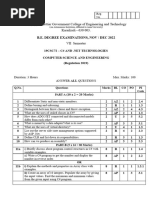

Reg. No.

:

Mohamed Sathak A J College of Engineering

Siruseri IT Park, OMR, Chennai - 603103.

Assessment – II Exam(Set B)

Date /Time Max. Marks 50 Marks

Subject with Code EC 8552 - Computer Architecture And Time 90 minutes

Organization

Branch ECE Year/Semester III/V

Course Objectives

The Student should be able

S. No. Course Objective

1 To make students understand the basic structure and operation of digital computer

2 To familiarize with implementation of fixed point and floating-point arithmetic operations

3 To study the design of data path unit and control unit for processor

4 To understand the concept of various memories and interfacing

5 To introduce the parallel processing technique

Course Outcomes:

On Completion of the course the students will be able to

CO No. Course Outcome

1 Describe data representation, instruction formats and the operation of a digital computer

2 Illustrate the fixed point and floating-point arithmetic for ALU operation

3 Discuss about implementation schemes of control unit and pipeline performance

4 Explain the concept of various memories, interfacing and organization of multiple processors

5 Discuss parallel processing technique and unconventional architectures

BLOOMS TAXONOMY(BT Level)

K1-Remembering , K2-Understanding, K3-Applying, K4-Analyzing, K5-Evaluating ,K6-Creating

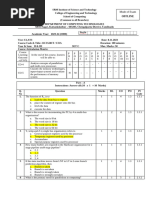

Part A (7x2=14 marks) CO BT level Univ. QP

(Answer all the questions) Mapping Reference

1 Subtract (11011)2-(10011)2 using 2‘s complement. 2 K2 May 2017

2 What do mean by Subword Parallelism? 2 K2 15,16,18

3 What is guard bit? What are the ways to truncate the guard bits? 2 K2 Nov16

4 State the rule for floating point addition. 2 K2 Apr 2017

5 What are the major characteristics of a pipeline? 3 K1 Nov2014

6 What is meant by pipeline bubble? 3 K2 Nov 2016

7 What is the ideal CPI of a pipelined processor? 3 K1 Apr2018

Part B (2x13=26marks) CO BT Univ.QP Marks

(Answer all the questions) level Reference Alloted

8 (a) Explain the Booth’s multiplication algorithm with suitable 2 K4 Apr2018 13

example.

(OR)

(b) Explain how floating point addition is carried out in a 2 K3 Apr 2017 13

computer system. Give an example for a binary floating

point addition.

9 (a) What is data hazard? Explain the ways and means of 3 K3 Apr2018 13

handing it in pipelined datapath.

OR

(b) Draw a simple MIPS data path with the control unit and 3 K3 Dec 2018 13

explain the execution of ALU instructions.

Part C (1x10=10marks) CO BT Univ.QP Marks

level Reference Alloted

10. (a) How IEEE 752 single,Double precision floating point 2 K4 Nov18 10

number -0.75 is represented?

OR

(b) A processor has five individual stages, namely IF 3 K5 Dec 2018 10

,ID, EX, MEM, and WB and their latencies are

250ps,350 ps,150ps,300ps and 200ps respectively.

The frequency of the instructions executed by the

processor are as follows: ALU 40%, Branch 25%,

Load 20% and Store 15%.What is the clock

cycle time in a pipelined and non-pipelined

processor? If you can split one stage of the

pipelined data path into two stages, each with

half the latency of the original stage, which

stage would you split and what is the new clock

cycle time of the processor? Assuming there are

no stalls or hazards, what is the utilization of the

data memory? Assuming there are no stalls or

hazards, what is the utilization of the write-

register port of the ‘Registers” unit?

*****ALL THE BEST****

Prepared By Verified By Approved By

You might also like

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Cao Iat 2 QP 2019 Set1Document2 pagesCao Iat 2 QP 2019 Set1formyphdNo ratings yet

- Cao Iat 1 QP 2019 Set1Document2 pagesCao Iat 1 QP 2019 Set1formyphdNo ratings yet

- Mohamed Sathak A J College of Engineering: Model Exam (Set 1)Document3 pagesMohamed Sathak A J College of Engineering: Model Exam (Set 1)formyphdNo ratings yet

- CS3351 Dpco Iat2Document1 pageCS3351 Dpco Iat26001 Aarthi VNo ratings yet

- CO Previous Year O.UDocument7 pagesCO Previous Year O.UVistasNo ratings yet

- Rmkcet-22cs302-Coa Unit 2 FinalDocument87 pagesRmkcet-22cs302-Coa Unit 2 Finalkoteeswaran259No ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- 21341 20pespc103 Design of Embedded SystemsDocument2 pages21341 20pespc103 Design of Embedded SystemsulaganathanNo ratings yet

- Mohamed Sathak A J College of Engineering: Aeronautical Engg Course Objectives S. No. Course ObjectivesDocument2 pagesMohamed Sathak A J College of Engineering: Aeronautical Engg Course Objectives S. No. Course ObjectivesformyphdNo ratings yet

- Doc. Ref. Internal Examination QP Format: Coimbatore - 35, TN, India Kite/Ems/Int - Ex/02/IaqpDocument14 pagesDoc. Ref. Internal Examination QP Format: Coimbatore - 35, TN, India Kite/Ems/Int - Ex/02/Iaqpvignesh2906viNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- Embedded System Design - Term-1Document2 pagesEmbedded System Design - Term-1Gokul SNo ratings yet

- Copy of 20pespc103 Design of Embedded SystemsDocument2 pagesCopy of 20pespc103 Design of Embedded SystemsulaganathanNo ratings yet

- 6CS4-04 CaoDocument1 page6CS4-04 CaoUdit SharmaNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- Coa Ct3 Set A Answer KeyDocument5 pagesCoa Ct3 Set A Answer KeyAaniya JainNo ratings yet

- model OSDocument8 pagesmodel OSchithraNo ratings yet

- Computer Networks 2023Document2 pagesComputer Networks 2023jit189111No ratings yet

- B.Tech II Year II Semester (R15) Regular Examinations May/June 2017Document2 pagesB.Tech II Year II Semester (R15) Regular Examinations May/June 2017Abson MulengaNo ratings yet

- Computer NetworksDocument3 pagesComputer NetworksAravind SNo ratings yet

- coa-cat2Document2 pagescoa-cat2moneeshbrNo ratings yet

- CLAT3_Set BDocument3 pagesCLAT3_Set Bpw5908No ratings yet

- Mahendra Engineering College) : Continuous Assessment Test - II - Aug - 2019Document2 pagesMahendra Engineering College) : Continuous Assessment Test - II - Aug - 2019Gowri ShankarNo ratings yet

- 3/2/1: High/Medium/LowDocument8 pages3/2/1: High/Medium/Lowaman singhNo ratings yet

- Vlsi Model Question Paper 2 (June 2021)Document3 pagesVlsi Model Question Paper 2 (June 2021)PushpalathaNo ratings yet

- Deco QB 23-24 MainDocument9 pagesDeco QB 23-24 Mainsyedizaan9876No ratings yet

- CLAT3_Set C _answerkeyDocument5 pagesCLAT3_Set C _answerkeypw5908No ratings yet

- CLAT3_Set B_answerkeyDocument7 pagesCLAT3_Set B_answerkeypw5908No ratings yet

- QuestionsDocument5 pagesQuestionsgirishdsk2002No ratings yet

- OS Previous YearDocument6 pagesOS Previous YearDarling SkandaNo ratings yet

- AET305 Dec 2023Document2 pagesAET305 Dec 2023tve22ae062No ratings yet

- Set 2 External - COADocument2 pagesSet 2 External - COASonu KumarNo ratings yet

- Dpco QBDocument5 pagesDpco QBMaheswariNo ratings yet

- Ec8552-Cao Unit 5Document72 pagesEc8552-Cao Unit 5Anonymous c75J3yX33No ratings yet

- Sri Ramanujar Engineering College Department of Information Technology Model Exam Ii Year/Iv SemDocument2 pagesSri Ramanujar Engineering College Department of Information Technology Model Exam Ii Year/Iv SemGovarathanNo ratings yet

- 21CS404 Operating SystemsDocument2 pages21CS404 Operating Systemsjothishwar007No ratings yet

- 15ecsc704 576 Kle54-Ecsc704Document5 pages15ecsc704 576 Kle54-Ecsc704Aniket AmbekarNo ratings yet

- Ect342 Ktu Qbank LicDocument10 pagesEct342 Ktu Qbank Licaginkk922No ratings yet

- Compre FinalDocument2 pagesCompre Finalf20201654No ratings yet

- Computer Organization and ArchitectureDocument3 pagesComputer Organization and ArchitecturecoolshubupaunikarNo ratings yet

- 19CSC72Document3 pages19CSC72padmanabanm47No ratings yet

- CAO Guess PaperDocument7 pagesCAO Guess Paperbaburishabh368No ratings yet

- DLDM Assignment - Tutorial - QB - MCQ - (DIV B)Document21 pagesDLDM Assignment - Tutorial - QB - MCQ - (DIV B)so0071129No ratings yet

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDocument4 pagesJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANo ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- Information TechnologyDocument7 pagesInformation TechnologyDEVANAND ANo ratings yet

- Computer Network KCS-603 ST-2 QP Even 20-21Document2 pagesComputer Network KCS-603 ST-2 QP Even 20-21Hàmmád KhânNo ratings yet

- Previous Year Question PaperDocument11 pagesPrevious Year Question PaperMinuNo ratings yet

- CIAT - 1 - QP - IV ECE - DSP - ArchitectureDocument2 pagesCIAT - 1 - QP - IV ECE - DSP - ArchitectureKalaNo ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- CT2 QP SetBDocument5 pagesCT2 QP SetBsansheela2014No ratings yet

- Big Data QpapersDocument4 pagesBig Data QpapersSushma SNo ratings yet

- 24ec102 Unit - IIDocument170 pages24ec102 Unit - II23102208No ratings yet

- 2nd Ia Assignment Questions Updated (2)Document3 pages2nd Ia Assignment Questions Updated (2)shaikshandhani91No ratings yet

- Em - Unit 1-A (1) NewDocument2 pagesEm - Unit 1-A (1) NewdeepakNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- 75649a04605 Vlsi DesignDocument1 page75649a04605 Vlsi DesignbandarugnanatejaNo ratings yet

- SplitPDFFile 153 To 159Document7 pagesSplitPDFFile 153 To 159Sanjay DevNo ratings yet

- DSP Iat1 FinalDocument2 pagesDSP Iat1 FinalformyphdNo ratings yet

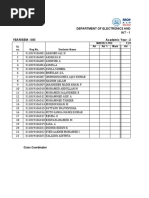

- Department Ofelectronics and Communication Engineering Question Wise Marksheet - Iat IDocument2 pagesDepartment Ofelectronics and Communication Engineering Question Wise Marksheet - Iat IformyphdNo ratings yet

- Ec8552 - Cao MCQDocument27 pagesEc8552 - Cao MCQformyphdNo ratings yet

- St. Joseph'S College of Engineering Department of Ece Multiple Choice Questions (MCQ) Subject: Ec 8553-Discrete Time Signal Processing (Unit I)Document65 pagesSt. Joseph'S College of Engineering Department of Ece Multiple Choice Questions (MCQ) Subject: Ec 8553-Discrete Time Signal Processing (Unit I)formyphdNo ratings yet

- Higher Sem Univ Exam Slot Feb 2021Document26 pagesHigher Sem Univ Exam Slot Feb 2021formyphdNo ratings yet

- Control Systems Engineering MCQDocument74 pagesControl Systems Engineering MCQformyphdNo ratings yet

- GEDC India Altair WebinarDocument1 pageGEDC India Altair WebinarformyphdNo ratings yet

- QB SJDocument56 pagesQB SJformyphdNo ratings yet

- Format For Att and Marks IAT1Document3 pagesFormat For Att and Marks IAT1formyphdNo ratings yet

- CS MCQ QBDocument21 pagesCS MCQ QBformyphdNo ratings yet

- Control System QB MsajceDocument54 pagesControl System QB MsajceformyphdNo ratings yet

- SyllabusDocument2 pagesSyllabusformyphdNo ratings yet

- Mohamed Sathak A J College of Engineering: Assessment - II Exam EC6701Document3 pagesMohamed Sathak A J College of Engineering: Assessment - II Exam EC6701formyphdNo ratings yet

- Coupling-Matrix Design of Dual and Triple Passband FiltersDocument7 pagesCoupling-Matrix Design of Dual and Triple Passband FiltersrallabhandiSKNo ratings yet

- Installation and Operating Instructions: Automatic Control Units, OMD200 and 300Document48 pagesInstallation and Operating Instructions: Automatic Control Units, OMD200 and 300moma52No ratings yet

- DX DiagDocument27 pagesDX DiagNizar SuryamanNo ratings yet

- Advanced Diploma in Computer Applications With Arabic. (ADCAA)Document15 pagesAdvanced Diploma in Computer Applications With Arabic. (ADCAA)Imran ShaNo ratings yet

- Batch AllotmentDocument12 pagesBatch Allotmentpan.bharatbhushanNo ratings yet

- Cara Setting Koneksi Modem Wireless ADSLDocument6 pagesCara Setting Koneksi Modem Wireless ADSLFaidul RochmanNo ratings yet

- Bài tập tự động hóa sản xuấtDocument7 pagesBài tập tự động hóa sản xuấtTiến Đạt LêNo ratings yet

- EXAM IN CIRCUIT by Amado, Leter D.Document6 pagesEXAM IN CIRCUIT by Amado, Leter D.Lester AmadoNo ratings yet

- Arduino Uno Rev3-SchematicDocument1 pageArduino Uno Rev3-Schematicc_mestre100% (1)

- Chapter 1 Lecture 2 & 3 - Computer PerformanceDocument37 pagesChapter 1 Lecture 2 & 3 - Computer PerformanceIsiyak SolomonNo ratings yet

- Synchronous Buck Converter Based Low-Cost and High-Efficiency Sub-Module DMPPT PV System Under Partial Shading ConditionsDocument15 pagesSynchronous Buck Converter Based Low-Cost and High-Efficiency Sub-Module DMPPT PV System Under Partial Shading ConditionsSri SriNo ratings yet

- DX DiagDocument33 pagesDX DiagCarlos Lux MontañoNo ratings yet

- Datadomain Management CenterDocument132 pagesDatadomain Management CenterUmit ArslanNo ratings yet

- Data Distribution Unit (Ddu) Block IiiDocument2 pagesData Distribution Unit (Ddu) Block IiiLa PedroNo ratings yet

- Port Monitor For KYOCERA Net Manager User GuideDocument22 pagesPort Monitor For KYOCERA Net Manager User GuideTestni AkauntNo ratings yet

- MC9251 Middleware TechnologiesDocument7 pagesMC9251 Middleware Technologiesvel.sakthi3152No ratings yet

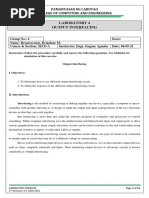

- Laboratory 4 Output Interfacing: Pamantasan NG Cabuyao College of Computing and EngineeringDocument16 pagesLaboratory 4 Output Interfacing: Pamantasan NG Cabuyao College of Computing and EngineeringKrizalene ResurreccionNo ratings yet

- CN Roadmap FrazDocument2 pagesCN Roadmap FrazAman SinghNo ratings yet

- Vyshak Resume QA AnalystDocument2 pagesVyshak Resume QA Analystramanuj padhyNo ratings yet

- Idea Explanation - Anti Sleep AlarmDocument11 pagesIdea Explanation - Anti Sleep AlarmcrazyopsgamerNo ratings yet

- Setting Up CodeblockDocument14 pagesSetting Up CodeblockAdam LassakNo ratings yet

- MP SI Old Paper 2014Document47 pagesMP SI Old Paper 2014gaurav yadavNo ratings yet

- BSC C++ Unit IDocument31 pagesBSC C++ Unit Ikudikala kalabharathiNo ratings yet

- Master Boot Record: Usman Mansoor Junaid Ali Husnain Manzoor Fahad AliDocument10 pagesMaster Boot Record: Usman Mansoor Junaid Ali Husnain Manzoor Fahad AliJunaidAliNo ratings yet

- dv4 LA-4117PDocument56 pagesdv4 LA-4117PWade Dyer100% (1)

- Capacitive Touch Module V0.2Document11 pagesCapacitive Touch Module V0.2ptmahvalNo ratings yet

- Ddei 5.0 IdgDocument139 pagesDdei 5.0 IdgNguyen AnhNo ratings yet

- Cobra ODE DMC InstallationDocument15 pagesCobra ODE DMC InstallationTahir BashirNo ratings yet

- Dataflow TestingDocument14 pagesDataflow Testinggopi chandNo ratings yet