Superscalar and Super Pipelined Processors

Superscalar and Super Pipelined Processors

Uploaded by

SharathMenonCopyright:

Available Formats

Superscalar and Super Pipelined Processors

Superscalar and Super Pipelined Processors

Uploaded by

SharathMenonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Superscalar and Super Pipelined Processors

Superscalar and Super Pipelined Processors

Uploaded by

SharathMenonCopyright:

Available Formats

Superscalar and Super pipelined Processors

A scalar processor executes scalar instructions, that is instructions operating on

single quantity operands such as integers. As we have seen, the design of such a

processor may be pipelined where the staggered use of the pipeline can improve

instruction throughput. A superscalar processor is one which executes more than one

scalar instruction concurrently. This is achieved by having a number of independent

pipelines. A limited form of superscalar operation is present in processors that have,

for example, separate integer and floating point units. After the decode stage the

instructions are sent to the appropriate unit and can execute in parallel. True superscalar

operation can only be achieved by fetching a number of instructions simultaneously

and executing them simultaneously.

The objective of superscalar design is to improve performance by exploiting

instruction level parallelism in user programs. We might expect that doubling the

number of pipelines would double performance, but we have seen the problems caused

by pipeline hazards in a single pipeline and can see that this problem is much more

critical for superscalar processors and that some of the pipelines will be stalling. One

of the characteristics of RISC designs is that the processor has a simplified instruction

set architecture resulting in fewer data interdependencies. For this reason, virtually all

superscalar designs have been based on a RISC architecture. The superscalar degree is

low due to limited instruction parallelism that can be exploited in ordinary programs.

Instruction issue and completion policies are critical to superscalar processor

performance.

When instructions are issued (i.e. initiation of their execution in functional units) in

program order it is called in-order issue. When program order is violated, out-of-order

issue is being practiced.

When instructions must be completed (i.e. have altered register and/or memory) in

program order, it is called in-order completion, otherwise out-of-order completion

may result. In-order issue is easier to implement but may not yield the optimal

performance. Proper scheduling can avoid stalling the pipelines. A number of possible

scheduling policies are possible. In the examples below, the pipeline cycle is the

minimum time between consecutive exchanges between each stage of the pipeline.

In-Order Issue with In-Order Completion

Assume we have a superscalar pipeline capable of fetching and decoding two

instructions at a time. Let's say there are three separate functional units and that there

are two instances of the writeback pipeline stage. Let's say we have six instructions

with the following constraints:

I1 requires two cycles to execute. I3 and I4 conflict for the same functional unit. I5

depends on the value produced by I4. I5 and I6 conflict for a functional unit.

Instructions are only decoded up to the point of a dependency or resource conflict. No

additional instructions are decoded until the conflict is resolved. This means a

maximum of two instructions can be in the execute stage as later instructions have a

time dependency on earlier ones executing first.

You might also like

- Datastage - Parameters - Schema FilesDocument23 pagesDatastage - Parameters - Schema FilesRMNo ratings yet

- Superscalar Vs Superpipeline ProcessorDocument17 pagesSuperscalar Vs Superpipeline ProcessorNormalia SamianNo ratings yet

- Week-11 - 12-Hivepdf - 2023 - 11 - 10 - 12 - 47 - 43Document8 pagesWeek-11 - 12-Hivepdf - 2023 - 11 - 10 - 12 - 47 - 43Sheshikanth DonNo ratings yet

- Stack and SUBROUTINES Bindu AgarwallaDocument15 pagesStack and SUBROUTINES Bindu AgarwallaNobodyNo ratings yet

- Lecture 12 Stack and SubroutinesDocument24 pagesLecture 12 Stack and SubroutinesfalconblockNo ratings yet

- 14-Lesson Cloudera HiveDocument9 pages14-Lesson Cloudera Hiveadchy7No ratings yet

- Pig HiveDocument72 pagesPig HivesuhasspotifypvtNo ratings yet

- Chapter 01 Introduction To Computer Organization and ArchitectureDocument47 pagesChapter 01 Introduction To Computer Organization and ArchitectureDann LaurteNo ratings yet

- MahoutDocument6 pagesMahoutPappu KhanNo ratings yet

- Unit 3: Bus Structure, Memory and I/O InterfacingDocument1 pageUnit 3: Bus Structure, Memory and I/O Interfacingyogesh deoNo ratings yet

- BD - Unit - IV - Hive and PigDocument41 pagesBD - Unit - IV - Hive and PigPrem KumarNo ratings yet

- Working With A Dynamic Lookup CacheDocument15 pagesWorking With A Dynamic Lookup CacheVarun Pratap JaiswalNo ratings yet

- Unit 3Document14 pagesUnit 3Ankit Kumar JhaNo ratings yet

- Disk Management in Operating SystemDocument8 pagesDisk Management in Operating SystemRabia kainat100% (1)

- New DOC DocumentDocument6 pagesNew DOC Documentgaura nitai100% (1)

- TransformationsDocument25 pagesTransformationsBharathNo ratings yet

- CS8492 /database Management Systems 2017 RegulationsDocument20 pagesCS8492 /database Management Systems 2017 RegulationsgraciaNo ratings yet

- Apache Hadoop Yarn Architecture PDFDocument3 pagesApache Hadoop Yarn Architecture PDFNabeela SayedNo ratings yet

- Classical Problems of SynchronizationDocument10 pagesClassical Problems of SynchronizationveeramatNo ratings yet

- Notes - Unit 3 - Map Reduce ApplicationsDocument11 pagesNotes - Unit 3 - Map Reduce ApplicationssoundharyaNo ratings yet

- Map-Reduce For Parallel Computing: Amit JainDocument72 pagesMap-Reduce For Parallel Computing: Amit JainNate AustinNo ratings yet

- Hadoop I/O: Jaeyong ChoiDocument36 pagesHadoop I/O: Jaeyong ChoiPrakash SharmaNo ratings yet

- CD Unit - 4Document39 pagesCD Unit - 4Ganesh Pavan Kumar BattulaNo ratings yet

- Datatypes in HiveDocument31 pagesDatatypes in HiveMytheesh WaranNo ratings yet

- APT ConfigDocument9 pagesAPT Confignithinmamidala999No ratings yet

- Hashing Concepts in DBMS PDFDocument7 pagesHashing Concepts in DBMS PDFkaramthota bhaskar naikNo ratings yet

- SrikanthDocument7 pagesSrikanth2srikanthNo ratings yet

- COA Unit 1Document33 pagesCOA Unit 1Keshav NaganathanNo ratings yet

- Machine Learning With SparkDocument26 pagesMachine Learning With SparkyagoencuestasNo ratings yet

- SUG613 GIS - Project 2 ReportDocument10 pagesSUG613 GIS - Project 2 ReportSafwan IzzatyNo ratings yet

- B.tech Viii Bda Chapter 3Document21 pagesB.tech Viii Bda Chapter 3duggyNo ratings yet

- Hadoop Unit-4Document44 pagesHadoop Unit-4Kishore ParimiNo ratings yet

- 1 Introduction Module 1Document64 pages1 Introduction Module 1Ranjitha JayaramaiahNo ratings yet

- Lab Manual 07 DSA PDFDocument19 pagesLab Manual 07 DSA PDFhiraNo ratings yet

- Arp and RarpDocument36 pagesArp and RarpShiva NageswararaoNo ratings yet

- The Osi Model and TCP Ip Protocol SuiteDocument24 pagesThe Osi Model and TCP Ip Protocol SuiteRahul DhandeNo ratings yet

- Processes: Process Concept Process Scheduling Operation On Processes Cooperating Processes Interprocess CommunicationDocument27 pagesProcesses: Process Concept Process Scheduling Operation On Processes Cooperating Processes Interprocess CommunicationMaha IbrahimNo ratings yet

- Mining Data StreamsDocument67 pagesMining Data StreamsushaNo ratings yet

- DATA ANALYTICS LabDocument3 pagesDATA ANALYTICS LabBoopathi kumarNo ratings yet

- AsdfghjkDocument23 pagesAsdfghjkSatyam SharmaNo ratings yet

- Threads: Multicore Programming Multithreading Models Thread Libraries Threading Issues Operating System ExamplesDocument22 pagesThreads: Multicore Programming Multithreading Models Thread Libraries Threading Issues Operating System Examplesmriaz14No ratings yet

- COA - Module-5Document35 pagesCOA - Module-5shruthingowda48No ratings yet

- MCQ Type QuestionsDocument24 pagesMCQ Type QuestionsGuruprasad VijayakumarNo ratings yet

- 3 Array Pointer and StructureDocument17 pages3 Array Pointer and StructureAKASH PALNo ratings yet

- Devops RecordDocument109 pagesDevops RecordPriya NeelamNo ratings yet

- TF On SparkDocument35 pagesTF On SparkarkNo ratings yet

- Advanced Computer Networks - CS716 Power Point Slides Lecture 25Document264 pagesAdvanced Computer Networks - CS716 Power Point Slides Lecture 25Taran AulakhNo ratings yet

- pdc1: MODULE 1: PARALLELISM FUNDAMENTALSDocument42 pagespdc1: MODULE 1: PARALLELISM FUNDAMENTALSVandana M 19BCE1763No ratings yet

- DSA RTU 2022 PaperDocument15 pagesDSA RTU 2022 PaperAmaan KhokarNo ratings yet

- Software Testing MethodologcompletenotesDocument147 pagesSoftware Testing Methodologcompletenotesmotasunil46No ratings yet

- HBase Interview QuestionsDocument12 pagesHBase Interview Questionspooh06No ratings yet

- Bit Slice ProcessorDocument1 pageBit Slice ProcessorAkash RuhilNo ratings yet

- Stqa VivaDocument10 pagesStqa Vivaharshit gargNo ratings yet

- Hadoop Command Line InterfaceDocument10 pagesHadoop Command Line Interfacepallavibhardwaj1124No ratings yet

- Unit 4 - 4.4Document23 pagesUnit 4 - 4.4King BavisiNo ratings yet

- CP Tutorial1Document6 pagesCP Tutorial1naruatNo ratings yet

- Manual For DBMS LABDocument82 pagesManual For DBMS LABKavitha SubramaniamNo ratings yet

- BA5302-Strategic Management PDFDocument18 pagesBA5302-Strategic Management PDFAkshaya nandhini AkshayaNo ratings yet

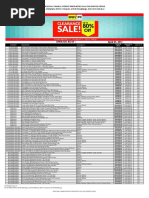

- Easy PC Clearance SaleDocument2 pagesEasy PC Clearance SaleVIRT BIZNo ratings yet

- Private Employers Kanchi - KancheepuramDocument18 pagesPrivate Employers Kanchi - Kancheepuramhem1980No ratings yet

- Grape Eng Rev4Document2 pagesGrape Eng Rev4hzf0915No ratings yet

- The Fractional Fourier Transform and Its ApplicationsDocument47 pagesThe Fractional Fourier Transform and Its Applicationsscribd99190No ratings yet

- JMET 2006 Original PaperDocument68 pagesJMET 2006 Original PaperBrian WilliamsNo ratings yet

- 3D TransformationDocument5 pages3D TransformationEky SutomoNo ratings yet

- 8.1. Wireless and Mobile Computing LabDocument2 pages8.1. Wireless and Mobile Computing Labdrives267No ratings yet

- CSOE Certification Steps 1 PDFDocument3 pagesCSOE Certification Steps 1 PDFApoorva BadolaNo ratings yet

- PBL-II Presentation Template For StudentsDocument13 pagesPBL-II Presentation Template For StudentsKongNo ratings yet

- Wago App FTPDocument189 pagesWago App FTPMarcioWatanabeNo ratings yet

- AndroidAPS Guide en 3Document29 pagesAndroidAPS Guide en 3Patricia TrejoNo ratings yet

- Arch Linux - ArchWikiDocument4 pagesArch Linux - ArchWikiVakkasNo ratings yet

- K8vblWMS DSCON3000-M Datasheet 20181030Document2 pagesK8vblWMS DSCON3000-M Datasheet 20181030thomvalensiNo ratings yet

- TERM - PAPER - INTERNET - OF - THINGS - Uzoh Obinna - 065810Document30 pagesTERM - PAPER - INTERNET - OF - THINGS - Uzoh Obinna - 065810obinnauzohNo ratings yet

- KeyDocument2 pagesKeyRiniNo ratings yet

- Your Journey To Success Starts Here With A Little Help From Your Guide BookDocument40 pagesYour Journey To Success Starts Here With A Little Help From Your Guide BookJenice WhiteNo ratings yet

- Switchs de Acceso IndustrialDocument25 pagesSwitchs de Acceso IndustrialJorge Luis Yaya CruzadoNo ratings yet

- Seda Book Beginner Rewind (2020!10!05 15-50-54 UTC)Document50 pagesSeda Book Beginner Rewind (2020!10!05 15-50-54 UTC)Jeferson Souza PazzeNo ratings yet

- KZ SA ELST 0001 Electrical Detail EngineeringDocument12 pagesKZ SA ELST 0001 Electrical Detail EngineeringTTRRTTGFNo ratings yet

- HMDongle40 enDocument29 pagesHMDongle40 entazzo2No ratings yet

- A A 51880Document5 pagesA A 51880MUHAMMAD SISWANTORONo ratings yet

- Timers and InterruptDocument38 pagesTimers and Interrupt21146387No ratings yet

- Qualification and Exam Details: 10Th or EquivalentDocument1 pageQualification and Exam Details: 10Th or Equivalentbya48829No ratings yet

- VxworksmmDocument21 pagesVxworksmmGIRISH PECHETTINo ratings yet

- 7SR11 and 7SR12 Argus Catalogue Sheet - IEC61850Document24 pages7SR11 and 7SR12 Argus Catalogue Sheet - IEC61850hanishalim89No ratings yet

- An Integrated PV Based DVR For Power Quality Improvement in Distribution SystemDocument7 pagesAn Integrated PV Based DVR For Power Quality Improvement in Distribution SystemdevchandarNo ratings yet

- R24 System Diagram: AMD OntarioDocument36 pagesR24 System Diagram: AMD OntarioRicardo SilvaNo ratings yet

- Mrs. Jyoti Haweliya Payal Mavi - 18C7034 Soniya Kori - 18C7055 Kanchan Ahirwar - 18C7022Document10 pagesMrs. Jyoti Haweliya Payal Mavi - 18C7034 Soniya Kori - 18C7055 Kanchan Ahirwar - 18C7022Kanchan AhirwarNo ratings yet

- P142 UP P147 UP - Users - ManualDocument8 pagesP142 UP P147 UP - Users - ManualForward MyanmarNo ratings yet