BQ24190 2 SchematicChecklist V1p0

BQ24190 2 SchematicChecklist V1p0

Uploaded by

Mladen GavricCopyright:

Available Formats

BQ24190 2 SchematicChecklist V1p0

BQ24190 2 SchematicChecklist V1p0

Uploaded by

Mladen GavricCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

BQ24190 2 SchematicChecklist V1p0

BQ24190 2 SchematicChecklist V1p0

Uploaded by

Mladen GavricCopyright:

Available Formats

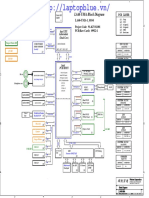

BQ24190/2

TYPICAL SCHEMATIC

BQ24190/2 SCHMATIC CHECKLIST

PIN NAME REQUIREMENT COMPONENT MIN TYP MAX DESCRIPTION COMMENTS AND RELEVANT EQUATIONS

USB data line pair

D+/D‐ 1. D+/D‐ based USB host/charging port detection. The detection includes data contact detection(DCD),

2,3 Optional Positive line of the USB data line pair.

BQ24190 ONLY primary and secondary detection in BC1.2.

Optional Negative line of the USB data line pair. 2. If D+/D‐ based input current limit detection is not used, short D+/D‐ pins together.

PSEL Power source selection input.

2

BQ24192 ONLY Required High indicates a USB host source and Low indicates an adapter source. Do not float.

Open drain active low power good indicator.

/PG

3 LOW indicates a good input source if the input voltage is between UVLO and ACOV, above SLEEP mode

BQ24192 ONLY Optional PG resistor 2.2 kΩ 10 kΩ Connect to the pull up rail via 10‐kΩ resistor.

threshold, and current limit is above 30 mA.

Open drain charge status output

STAT 4 1. If not used, leave it float. 2. HIGH indicates charge complete or charge disabled. When any fault Digital

Optional STAT resistor 2.2 kΩ 10 kΩ Connect to the pull up rail via 2.2‐kΩ resistor.

condition occurs, STAT pin in blinks at 1 Hz.

I2C Interface clock and data

SCL/SDA 5‐6 Optional SCL resistor 10 kΩ Connect SCL to the logic rail through a 10‐kΩ resistor. If I2C communication is not used, leave it float.

Optional SDA resistor 10 kΩ Connect SDA to the logic rail through a 10‐kΩ resistor. If I2C communication is not used, leave it float.

Open‐drain Interrupt Output

INT 7 1. If not used, leave it float. 2. The INT pin sends active low, 256‐μs pulse to host to report charger device

Optional INT resistor 10 kΩ Connect the INT to a logic rail via 10‐kΩ resistor.

status and fault.

Active high enable pin during boost mode.

1. If OTG boost mode is not used, short it to ground. 2. In buck mode with USB host (PSEL=High), when OTG =

OTG 8 USB current limit selection pin during buck mode, and

Optional High, IIN limit = 500 mA and when OTG = Low, IIN Digital limit = 100 mA. 3. The boost mode is activated when

active high enable pin during boost mode.

the REG01[5:4] = 10 and OTG pin is High.

Active low Charge Enable pin.

/CE 9

Required

1. /CE pin must be pulled High or Low. 2. Battery charging is enabled when REG01[5:4] = 01 and CE pin = Low.

Input current limit Input.

1. The actual input current limit is the lower one set by ILIM and by I2C REG00[2:0]. 2.The minimum input

ILIM 10 A resistor is connected from ILIM pin to ground to set the

Required ILIM resistor * Ω current programmed on ILIM pin is 500 mA. 3. If ILIM pin is short, the input current limit is set by the register.

maximum limit as IINMAX = (1V/RILIM) × 530

4. If ILIM pin is open, the input current is limited to zero

Temperature qualification voltage inputs.

TS1, TS2 11,12 TS resistors and Connect a negative temperature coefficient thermistors.

Required

thermistor Recommend 103AT‐2 thermistors.

1. If thermistor is not used, set TS pin voltage within normal range. 2. If thermistor is used, program

temperature window with a resistor divider from REGN to TSx to GND. Charge suspends when either TS pin is

out of range.

Input source to the charger

VBUS 1,24 1. Place a 1‐μF ceramic capacitor from VBUS to PGND and place it as close as possible to IC. 2. It is

Required VBUS caps 1uF

recommended to have a total of ~10uF capacitance at VBUS & PMID for USB input compliance.

Actual input source to the charger

PMID 23

Required PMID caps 6.8uF

Given the total input capacitance, put 1 μF on VBUS to PGND, and the rest capacitance on PMID to PGND.

Positive battery connection point

VBAT 13‐14

Required VBAT caps 10uF 10uF

1. Connect a 10 μF closely to the BAT pin. 2. Charger may operate normally when battery is not connected.

System connection point.

VSYS 15‐16

Required VSYS caps 20uF 20uF 40uF

Connect a 20 μF closely to the SYS pin. The preferred ceramic capacitor is 6V or higher rating, X7R or X5R.

Switching node connecting to output inductor.

The charger device has internal loop compensator. To get good loop stability, the resonant frequency of the

SW 19‐20

Required Output inductor 1uH 2.2uH output inductor and output capacitor should be designed between 15 kHz and 25 kHz. With 2.2‐μH inductor,

the typical output capacitor value is 20 μF.

Optional SW Resistor * Ω Snubber circuit values empirically determined if required. Recommend unpopulated footprint on new

Switching converter snubber circuit

Optional SW Cap * F designs.

PWM high side driver positive supply.

BTST 21

Required BTST‐SW cap 0.047uF 0.047uF 0.047uF Connect the 0.047μF bootstrap capacitor from SW to BTST.

Optional BTST resistor * Ω Bootstrap capacitor snubbing resistor Help with EMI performance. Recommend unpopulated footprint on new designs.

PWM low side driver positive supply output.

REGN 22 Connect a 4.7 μF (10 Vrating) ceramic capacitor from REGN to analog GND. The capacitor should be placed

Required REGN cap 4.7uF 4.7uF 4.7uF

close to the IC. REGN also serves as bias rail of TS1 and TS2 pins.

Power ground connection for high‐current power

converter node.

PGND 17‐18

Required On PCB layout, connect directly to ground connection of input and output capacitors of the charger. A single

point connection is recommended between power PGND and the analog GND near the IC PGND pin.

Always solder PowerPAD Pad to the board, and have vias on the PowerPAD plane star‐connecting to PGND

PowerPAD Required

and ground plane for high‐current power converter.

You might also like

- Current Resonant Control IC FA6B20N: DatasheetDocument56 pagesCurrent Resonant Control IC FA6B20N: DatasheetCube7 Geronimo100% (8)

- Project Proposal of Printing ServiceDocument7 pagesProject Proposal of Printing ServiceLorene bby100% (10)

- Docuprint cm305 DF SERVICE MDocument879 pagesDocuprint cm305 DF SERVICE MJoshuaNo ratings yet

- EPOCH 600 Training Presentation 3-2014Document193 pagesEPOCH 600 Training Presentation 3-2014Raul MedinaNo ratings yet

- Philips 715g5821 m01 000 004i Meridian 5 Chassis SCHDocument8 pagesPhilips 715g5821 m01 000 004i Meridian 5 Chassis SCHRamkiNo ratings yet

- LA-C551P (AAPB0) 2015-08-18, Rev 1.0 (A00)Document74 pagesLA-C551P (AAPB0) 2015-08-18, Rev 1.0 (A00)123100% (1)

- Asus ROG Phone ZS600KL - Schematic DiagarmDocument90 pagesAsus ROG Phone ZS600KL - Schematic DiagarmWagner DiasNo ratings yet

- MediaTek LinkIt Smart 7688 Duo Pin Out v1 3Document1 pageMediaTek LinkIt Smart 7688 Duo Pin Out v1 3teguhscribdNo ratings yet

- Mediatek MT6235Document9 pagesMediatek MT6235rockstar5kNo ratings yet

- MT6592 Mediatek PDFDocument53 pagesMT6592 Mediatek PDFpop678100% (1)

- Dev Kit 8000Document5 pagesDev Kit 8000Shiva prasadNo ratings yet

- Dell Vostro 2420 SchematicDocument104 pagesDell Vostro 2420 SchematicNguyễn TeatraNo ratings yet

- Vl812 Via LabsDocument18 pagesVl812 Via LabsfabiopiraNo ratings yet

- How To Build A Bluetooth Controlled Home Automation Setup Using ArduinoDocument15 pagesHow To Build A Bluetooth Controlled Home Automation Setup Using ArduinoCairineLopesNo ratings yet

- HP EliteBook 6440b 6540b COMPAL LA-4891P KELL00 DIOR Discrete REV 0.1 SchematicsDocument50 pagesHP EliteBook 6440b 6540b COMPAL LA-4891P KELL00 DIOR Discrete REV 0.1 SchematicsSaid FakirNo ratings yet

- MT 6582 Data Sheet Technical BriefDocument51 pagesMT 6582 Data Sheet Technical BriefPeteLimNo ratings yet

- AAN-100 Hardware Manual: Revision Date: 11/27/2006Document81 pagesAAN-100 Hardware Manual: Revision Date: 11/27/2006ali_1976sweet7448No ratings yet

- La D641PDocument45 pagesLa D641PRicardo Nicolau Werlang0% (1)

- Laptop Schematics Abbreviations MeaningDocument3 pagesLaptop Schematics Abbreviations MeaningdongpalNo ratings yet

- Open Compute Project Intel Motherboard v2.0 YGMDocument32 pagesOpen Compute Project Intel Motherboard v2.0 YGMgawinNo ratings yet

- Asus Test ReportDocument4 pagesAsus Test ReportFerry RiantoNo ratings yet

- HP ENVY M6 Compal - La-8711p - r0.1 - Schematics PDFDocument58 pagesHP ENVY M6 Compal - La-8711p - r0.1 - Schematics PDFrahul sarkarNo ratings yet

- How To Check No Display Problem On CircuitDocument2 pagesHow To Check No Display Problem On CircuitLeth ComputerRepairNo ratings yet

- (20-58) Charging Case Firmware Update Guide For R180 - Rev1.1Document6 pages(20-58) Charging Case Firmware Update Guide For R180 - Rev1.1Brandon CifuentesNo ratings yet

- Compal LA-6591P r10 WWW - MYCOMP.SU PDFDocument66 pagesCompal LA-6591P r10 WWW - MYCOMP.SU PDFvideosonNo ratings yet

- Sim7230 Hardware Design v1.02 PDFDocument46 pagesSim7230 Hardware Design v1.02 PDFCristian BandilaNo ratings yet

- Asus Test ReportDocument3 pagesAsus Test ReporttingkimNo ratings yet

- 5th Gen Core Family Datasheet Vol 1 PDFDocument134 pages5th Gen Core Family Datasheet Vol 1 PDFLio SnNo ratings yet

- Scheme Lenovo Y570Document63 pagesScheme Lenovo Y570MariahaNo ratings yet

- Lenovo A6600 Plus - Schematic DiagarmDocument18 pagesLenovo A6600 Plus - Schematic DiagarmNdrik ElektraNo ratings yet

- Lenovo TB-8506X BlockDocument1 pageLenovo TB-8506X BlockSameer varshneyNo ratings yet

- MT762876037636 ATE User ManualDocument29 pagesMT762876037636 ATE User ManualNotupusNo ratings yet

- RT809F Programmer All Adapters LCD ReadeDocument5 pagesRT809F Programmer All Adapters LCD ReadeAlif Rizky ibadillahNo ratings yet

- Asus T12C (X51C) Motherboard Schematic DiagramDocument94 pagesAsus T12C (X51C) Motherboard Schematic DiagramYblis100% (1)

- Laptop Repair Topics Part1Document66 pagesLaptop Repair Topics Part1Bong BarcelitaNo ratings yet

- Dell Inspiron n5010 Wistron Berry Dg15 Intel Discrete Uma Rev A00 SCHDocument92 pagesDell Inspiron n5010 Wistron Berry Dg15 Intel Discrete Uma Rev A00 SCHAhmad BahaaNo ratings yet

- Lenovo b460 v460 Wistron La46uma Laptop ScheaticsDocument48 pagesLenovo b460 v460 Wistron La46uma Laptop ScheaticsVịnh DemoNo ratings yet

- RW b400c SpecDocument2 pagesRW b400c SpecindianmonkNo ratings yet

- Desktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Document7 pagesDesktop Motherboard Service Training-Chip Level: (30 Days 24 Hrs Time) 720 Hrs / (30 Days 1.30 Hrs 45 HRS)Rozitarmizi MohammadNo ratings yet

- Upgrading With The MtkTool - Rolsen Rl-32b04u Hisense Lcd32w58r Lcd32p69r CH Mtk8222 SMDocument4 pagesUpgrading With The MtkTool - Rolsen Rl-32b04u Hisense Lcd32w58r Lcd32p69r CH Mtk8222 SMdreamyson1983No ratings yet

- Unbrick MTKDocument3 pagesUnbrick MTKgiokspyNo ratings yet

- NPS711B9Document504 pagesNPS711B9funkyznNo ratings yet

- d9b19 Compal JBL00 LA-3801P - DeLL E6400 Laptop SchematicsDocument66 pagesd9b19 Compal JBL00 LA-3801P - DeLL E6400 Laptop SchematicsAdi Thama Thama100% (1)

- 5738Z JV50-MV Schematic DiagramDocument60 pages5738Z JV50-MV Schematic DiagramSelmn Şnlı100% (1)

- AdaptorDocument3 pagesAdaptorFelixius Rian Dwi WijayantoNo ratings yet

- Mt3151a05 2 PDFDocument28 pagesMt3151a05 2 PDFpeterNo ratings yet

- Asus Prime h310m-k r2.0Document113 pagesAsus Prime h310m-k r2.0skyloveasdfNo ratings yet

- Wistron Raichu - GL 18754 R-1MDocument106 pagesWistron Raichu - GL 18754 R-1MMadrif AlieNo ratings yet

- Service Manual: 17" LCD Monitor VS17EDocument58 pagesService Manual: 17" LCD Monitor VS17ECruz CastroNo ratings yet

- D/M Note Block Diagram - Intel Huron River ULVDocument43 pagesD/M Note Block Diagram - Intel Huron River ULVKhoirul ArifNo ratings yet

- Us 1Document4 pagesUs 1serviciobsasNo ratings yet

- Sample Demo Board (Linear)Document4 pagesSample Demo Board (Linear)Chandan Kumar Reddy EsanakulaNo ratings yet

- TMA2124F03V5 1D (A) DatasheetDocument4 pagesTMA2124F03V5 1D (A) DatasheetDebabrata SahaNo ratings yet

- MMIC Antenna Amplifier With Bypass Switch: G. KleineDocument1 pageMMIC Antenna Amplifier With Bypass Switch: G. KleineRadunNo ratings yet

- Modem Kantronics Packet Communicator KPC 3Document2 pagesModem Kantronics Packet Communicator KPC 3Miguel Muñoz BeverinottiNo ratings yet

- F6705 - AO (Safety Related) 2 Channels ModuleDocument4 pagesF6705 - AO (Safety Related) 2 Channels ModuleKourosh52No ratings yet

- Eurotherm Signal Limit Switch 1080-2000-1, ActionPak-AP1080-AP1090-721-0479-00-PDocument4 pagesEurotherm Signal Limit Switch 1080-2000-1, ActionPak-AP1080-AP1090-721-0479-00-Pfred.zhangNo ratings yet

- Cmy210 894306Document10 pagesCmy210 894306Agung KurniandraNo ratings yet

- High-Side Power Distribution Switch With Enable and Flag AP2820Document19 pagesHigh-Side Power Distribution Switch With Enable and Flag AP2820SangaNo ratings yet

- AP1509Document12 pagesAP1509Андрей ОлененкоNo ratings yet

- Tle 7259G PTM VWDocument28 pagesTle 7259G PTM VWSCANNER LABORAUTONo ratings yet

- BTS5210GDocument14 pagesBTS5210GsbgrimssonNo ratings yet

- I-Twin Limitless Pendrive TechnologyDocument3 pagesI-Twin Limitless Pendrive TechnologySarafa AbdulazeezNo ratings yet

- CP 111 1 EngDocument61 pagesCP 111 1 Engmisungwijohn01No ratings yet

- VEIKK A30 Instruction ManualDocument22 pagesVEIKK A30 Instruction ManualLQ530No ratings yet

- Quality Inspection Specification MID - LaptopDocument33 pagesQuality Inspection Specification MID - LaptopTV R&DNo ratings yet

- Basics Android VersionDocument31 pagesBasics Android VersionJacekNo ratings yet

- Accessories / Operating Modes Rk-006 As Usb Midi Interface: Manual v1.0, Feb 2020Document4 pagesAccessories / Operating Modes Rk-006 As Usb Midi Interface: Manual v1.0, Feb 2020Arthur ErpenNo ratings yet

- Ict Network and Comp Maintenance SopDocument6 pagesIct Network and Comp Maintenance Sopdesterious ImoliNo ratings yet

- Katana Librarian - Frequently Asked QuestionsDocument12 pagesKatana Librarian - Frequently Asked QuestionsLuki KurniawanNo ratings yet

- AirstepDocument39 pagesAirstepTechtureGNo ratings yet

- STM32 on-The-Go Host and Device LibraryDocument107 pagesSTM32 on-The-Go Host and Device LibraryNam Nguyễn HữuNo ratings yet

- kARL FISCHER 870 TITRIN PDFDocument100 pageskARL FISCHER 870 TITRIN PDFUrsula HilleNo ratings yet

- T100 Series Portable SSD: Huge CapacityDocument2 pagesT100 Series Portable SSD: Huge CapacitySoledad MezaNo ratings yet

- FETA40i-C/ FETT3-C OKA40i-C/ OKT3-C: Android ManualDocument50 pagesFETA40i-C/ FETT3-C OKA40i-C/ OKT3-C: Android ManualRaja MustaqeemNo ratings yet

- HUAWEI MatePad T 10 User Guide - (AGR-L09&W09, EMUI10.1 - 02, EN - UK)Document75 pagesHUAWEI MatePad T 10 User Guide - (AGR-L09&W09, EMUI10.1 - 02, EN - UK)fitriNo ratings yet

- TITAN Installation GuideDocument35 pagesTITAN Installation GuideMarco Antonio RubinaNo ratings yet

- SIM7600 USB-OTG Application Note V1.00Document8 pagesSIM7600 USB-OTG Application Note V1.00timNo ratings yet

- Samsung Galaxy Note8 User Manual SM-N950U1 enDocument221 pagesSamsung Galaxy Note8 User Manual SM-N950U1 enBarbara RadoševićNo ratings yet

- BLACKBOXDocument31 pagesBLACKBOXMarcosNo ratings yet

- HUAWEI Mate Xs User Guide - (TAH-N29m, EMUI11.0 - 01, EN)Document166 pagesHUAWEI Mate Xs User Guide - (TAH-N29m, EMUI11.0 - 01, EN)Otto YeungNo ratings yet

- Huawei Y9a User Guide - (Frl-l22&l23, Emui10.1.1 - 02, En)Document108 pagesHuawei Y9a User Guide - (Frl-l22&l23, Emui10.1.1 - 02, En)pmugova004No ratings yet

- User Manual LPC3250Document721 pagesUser Manual LPC3250elaa82No ratings yet

- PCX Hotline: 725-8888: Dealer's Price List Wed, Aug 18, 2021Document2 pagesPCX Hotline: 725-8888: Dealer's Price List Wed, Aug 18, 2021TatsNo ratings yet

- Mando Maz Catz Quick Start Guide 5Document93 pagesMando Maz Catz Quick Start Guide 5Luis Torres ParejaNo ratings yet

- HAPIPOLA Catalogue CompDocument66 pagesHAPIPOLA Catalogue CompTROUBLESOME 18No ratings yet

- Circuito Integrado USB AU6860cDocument14 pagesCircuito Integrado USB AU6860cRonan NolascoNo ratings yet

- Uma01214588 3Document355 pagesUma01214588 3yikyongNo ratings yet

- Onyx Boox Max LumiDocument155 pagesOnyx Boox Max LumisaccermoredaNo ratings yet