Digital Electronics Circuits: Experiment: 9

Digital Electronics Circuits: Experiment: 9

Uploaded by

movabCopyright:

Available Formats

Digital Electronics Circuits: Experiment: 9

Digital Electronics Circuits: Experiment: 9

Uploaded by

movabOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Digital Electronics Circuits: Experiment: 9

Digital Electronics Circuits: Experiment: 9

Uploaded by

movabCopyright:

Available Formats

Digital Electronics Circuits 2017

EXPERIMENT: 9

STUDY OF COUNTERS

I. STUDY OF ASYNCHRONOUS COUNTER

AIM: To design and test 3-bit binary asynchronous counter using flip-flop IC

7476 for the given sequence.

LEARNING OBJECTIVE:

To learn about Asynchronous Counter and its application

To learn the design of asynchronous up counter and down counter

COMPONENTS REQUIRED:

IC 7476, Patch Cords & IC Trainer Kit

THEORY:

A counter in which each flip-flop is triggered by the output goes to previous

flip-flop. As all the flip-flops do not change state simultaneously spike occur at the

output. To avoid this, strobe pulse is required. Because of the propagation delay

the operating speed of asynchronous counter is low. Asynchronous counter are

easy and simple to construct.

Design:

MOD-8 UP COUNTER

Lab Manual EC37L Page 36

Digital Electronics Circuits 2017

MOD_5 UP COUNTER

CIRCUIT DIAGRAM:

MOD-8 DOWN COUNTER

CIRCUIT DIAGRAM:

Lab Manual EC37L Page 37

Digital Electronics Circuits 2017

TRUTH TABLE

CLK QC QB QA

0 1 1 1

1 1 1 0

2 1 0 1

3 1 0 0

4 0 1 1

5 0 1 0

6 0 0 1

7 0 0 0

8 1 1 1

PROCEDURE:

1. Check the components for their working.

2. Insert the appropriate IC into the IC base.

3. Rig up the circuit as shown in the logic circuit diagram.

4. Apply various input data to the logic circuit via the input logic switches.

5. Note down the corresponding output and verify the truth table.

Note: Write the pin numbers of each gate and also write the intermediate expressions.

RESULT:

Lab Manual EC37L Page 38

Digital Electronics Circuits 2017

II. SYNCHRONOUS COUNTERS

AIM:

To design and test 3-bit binary synchronous counter using flip-flop IC 7476 for the

given sequence.

LEARNING OBJECTIVE:

To learn about synchronous Counter and its application

To learn the design of synchronous counter

COMPONENTS REQUIRED:

IC 7476, Patch Cords & IC Trainer Kit

THEORY:

A counter in which each flip-flop is triggered by the output goes to previous flip-

flop. As all the flip-flops do not change states simultaneously in asynchronous counter,

spike occur at the output. To avoid this, strobe pulse is required. Because of the propagation

delay the operating speed of asynchronous counter is low. This problem can be solved by

triggering all the flip-flops in synchronous with the clock signal and such counters are called

synchronous counters.

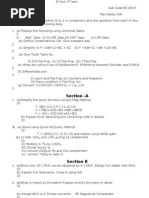

Design:

MOD 5 COUNTERS:

Present

TRUTH TABLE: count next count

QC QB QA QC QB QA QC QB QA

0 0 0 0 0 0 0 0 1

0 0 1 0 0 1 0 1 0

0 1 0 0 1 0 0 1 1

0 1 1 0 1 1 1 0 0

1 0 0 1 0 0 0 0 0

0 0 0

JK FF excitation table:

Q Q+ J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Lab Manual EC37L Page 39

You might also like

- Sample SPADocument3 pagesSample SPAiamyni93% (27)

- A Study On Future Trends in Recruitment India and OverseasDocument62 pagesA Study On Future Trends in Recruitment India and Overseasshiv infotech100% (1)

- Digital Logic Design: "4-Way Traffic Signal"Document11 pagesDigital Logic Design: "4-Way Traffic Signal"Sohaib Arif100% (1)

- Experiment 7 - Flip-FlopsDocument4 pagesExperiment 7 - Flip-FlopsPrr Prr100% (2)

- Digital and Logic Design: Lab-5 Karnaugh-Map, POS & SOPDocument9 pagesDigital and Logic Design: Lab-5 Karnaugh-Map, POS & SOPsaadNo ratings yet

- Assignment 3 Complex Engineering Problem Digital Logic Design/ Logic Design Switching TheoryDocument2 pagesAssignment 3 Complex Engineering Problem Digital Logic Design/ Logic Design Switching TheoryFaraz AbbasNo ratings yet

- Lab Report 1Document6 pagesLab Report 1Bappy HossenNo ratings yet

- Differential Amplifier Using BJTDocument11 pagesDifferential Amplifier Using BJTAssini Hussain100% (3)

- Experiment No-7 Design and Implementation of 4-Bit Ripple Counter and Mod-10 Counters Using Flip Flop and Gates ObjectDocument3 pagesExperiment No-7 Design and Implementation of 4-Bit Ripple Counter and Mod-10 Counters Using Flip Flop and Gates ObjectMohini Mohan BeheraNo ratings yet

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- Asynchronous Sequential Circuit NotesDocument15 pagesAsynchronous Sequential Circuit Notessujaganesan200950% (2)

- Digital Electronics Lab ManualDocument93 pagesDigital Electronics Lab ManualAnoop MathewNo ratings yet

- 2s Complement ManualDocument2 pages2s Complement ManualSRUJANA VNo ratings yet

- Chapter 2 Discrete Data Control SystemsDocument70 pagesChapter 2 Discrete Data Control SystemsAmruth Thelkar67% (3)

- Combinational and Sequential CircuitsDocument12 pagesCombinational and Sequential Circuitsdomainname9100% (1)

- Counter: Experiment No. 9 ObjectivesDocument5 pagesCounter: Experiment No. 9 ObjectivesAditya Patil100% (1)

- Lab Report Encoders and DecodersDocument10 pagesLab Report Encoders and DecodersOwais FarooqNo ratings yet

- 10a 3 Bit Up Down Counter DoneDocument6 pages10a 3 Bit Up Down Counter DoneVenkatGollaNo ratings yet

- Flip Flop ExperimentDocument5 pagesFlip Flop ExperimentDeepak KumbharNo ratings yet

- American International University-Bangladesh: Title: Design of A Half, Full and Parallel Adder and Subtractor CircuitsDocument4 pagesAmerican International University-Bangladesh: Title: Design of A Half, Full and Parallel Adder and Subtractor CircuitsAbid ChowdhuryNo ratings yet

- Lab Report Electronics 5thDocument18 pagesLab Report Electronics 5thMuhammad kawish iqbal100% (1)

- Experiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectDocument4 pagesExperiment-7 Design A Binary Subtractor Circuit Half and Full Subtractor 7-1 ObjectMohammed Dyhia AliNo ratings yet

- Ex 6 - Binary To Gray Code ConverterDocument6 pagesEx 6 - Binary To Gray Code Converterneha yarrapothuNo ratings yet

- Introduction To Logic Gates: 3.2 ObjectivesDocument4 pagesIntroduction To Logic Gates: 3.2 ObjectivesnarpatzaNo ratings yet

- Mod 5 Counter With VivaDocument3 pagesMod 5 Counter With Vivashrinidhi N100% (1)

- Implementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan KhalidDocument7 pagesImplementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan Khalidchachunasayan100% (1)

- Solution CH 05Document10 pagesSolution CH 05Sabeen ShujaNo ratings yet

- Half/Full Adder AndHalf/Full SubtractorDocument6 pagesHalf/Full Adder AndHalf/Full SubtractorJames Kevin Ignacio100% (10)

- Master Slave Flip FlopDocument3 pagesMaster Slave Flip FlophimanshuNo ratings yet

- STLD Lab ManualDocument43 pagesSTLD Lab Manualgsekharreddy100% (4)

- Monostable Multivibrator Using 555 Timer AimDocument4 pagesMonostable Multivibrator Using 555 Timer Aimneha yarrapothuNo ratings yet

- Practical No 7:-Demultiplexer (DEMUX)Document3 pagesPractical No 7:-Demultiplexer (DEMUX)vaishnaviNo ratings yet

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitNo ratings yet

- Digital Lab ManualDocument57 pagesDigital Lab ManualSUSISATYANo ratings yet

- Implementation of Basic Logic Gate (AND, OR, NOT) With Simulator.Document3 pagesImplementation of Basic Logic Gate (AND, OR, NOT) With Simulator.Mohayminul Al-HamimNo ratings yet

- Flip Flops, R-S, J-K, D, T, Master Slave - D&E NotesDocument7 pagesFlip Flops, R-S, J-K, D, T, Master Slave - D&E NotesNida AhmedNo ratings yet

- Shift RegisterDocument25 pagesShift RegisterFarhan NurNo ratings yet

- Digital Logic Design Lab 2Document11 pagesDigital Logic Design Lab 2M. Ahmad Raza100% (1)

- Electric Circuits &electronics Device Question PaperDocument5 pagesElectric Circuits &electronics Device Question PaperSalai Kishwar JahanNo ratings yet

- Notes On Counters (Digital Electronics)Document44 pagesNotes On Counters (Digital Electronics)wooDefyNo ratings yet

- Digital Electronics Exam PaperDocument2 pagesDigital Electronics Exam Paperswarnahans100% (1)

- Chapter 4 Counters PDFDocument37 pagesChapter 4 Counters PDFVeyronie Buggati SteveNo ratings yet

- Experiment - 1: Design and Analysis of Basic Logic Gates: AND, Or, Not, Nand, Xor, Xnor - Multisim 11.0Document4 pagesExperiment - 1: Design and Analysis of Basic Logic Gates: AND, Or, Not, Nand, Xor, Xnor - Multisim 11.0sakshamNo ratings yet

- 7 Segment Display Interfacing With 8051 MicrocontrollerDocument3 pages7 Segment Display Interfacing With 8051 MicrocontrollerPratheesh PrathiNo ratings yet

- DE LAB ManualC-18 FinalDocument85 pagesDE LAB ManualC-18 FinalBRAGPW,Karimnagar 087No ratings yet

- Digital Logic Design Lab ManualDocument55 pagesDigital Logic Design Lab ManualEngr Zaryab WarraichNo ratings yet

- 8 To 3 Bit Priority EncoderDocument12 pages8 To 3 Bit Priority EncoderDev SejvaniNo ratings yet

- Two Port NetworkDocument74 pagesTwo Port NetworkGil PrinNo ratings yet

- Example: Parity Checker: More Moore/Mealy MachinesDocument3 pagesExample: Parity Checker: More Moore/Mealy MachinesVIKRAMNo ratings yet

- Asynchronous Counter Lab ExperimentDocument2 pagesAsynchronous Counter Lab ExperimentShristi Sinha100% (1)

- Latches and Flip-FlopsDocument7 pagesLatches and Flip-FlopspresumidololoNo ratings yet

- Half Subtractor and Full Subtractor VHDL Simulation CodeDocument7 pagesHalf Subtractor and Full Subtractor VHDL Simulation Codearup duttaNo ratings yet

- Of 4-Bit Arithmetic Logic UnitsDocument15 pagesOf 4-Bit Arithmetic Logic UnitsYellasiri SureshNo ratings yet

- EXPT:-Study of J K Flip Flop Using IC 7476 Apparatus:-IC 7476, Breadboard, Single Stand WiresDocument4 pagesEXPT:-Study of J K Flip Flop Using IC 7476 Apparatus:-IC 7476, Breadboard, Single Stand WiresPoonam GholapNo ratings yet

- Experiment 6: Adders: Figure 5.1: Half AdderDocument3 pagesExperiment 6: Adders: Figure 5.1: Half AdderHassan Tariq100% (1)

- LAB 4 Summer and Subtractor OP-AMP Circuits: ObjectivesDocument4 pagesLAB 4 Summer and Subtractor OP-AMP Circuits: ObjectivesKidist kefelegnNo ratings yet

- ECA UNIT 1 Transistor Low Frequency and High Frequency AnalysisDocument22 pagesECA UNIT 1 Transistor Low Frequency and High Frequency Analysiscinthu chizhian22100% (1)

- 7 CountersDocument6 pages7 CountersSudhan HariNo ratings yet

- Experiment_7_excercise_experiment (1)Document6 pagesExperiment_7_excercise_experiment (1)01fe23bec345No ratings yet

- Ic 7432 (Quad 2-Input or Gates), Ic 7404 (Hex Inverters), Leds, Resister (220 ) - EtcDocument2 pagesIc 7432 (Quad 2-Input or Gates), Ic 7404 (Hex Inverters), Leds, Resister (220 ) - EtcIshtiaque Ahmed TanimNo ratings yet

- SY - Synchronous Counter Using Flip FlopsDocument2 pagesSY - Synchronous Counter Using Flip FlopsAbhishek Parmar100% (1)

- Expt 09Document7 pagesExpt 09sdmrnmistNo ratings yet

- Nikon (Louth 2007)Document5 pagesNikon (Louth 2007)guidoherzogNo ratings yet

- Immediate Download Kinetics in Materials Science and Engineering Dennis W. Readey Ebooks 2024Document62 pagesImmediate Download Kinetics in Materials Science and Engineering Dennis W. Readey Ebooks 2024yunnidarag100% (4)

- Arp PaperDocument30 pagesArp Paperapi-345689798No ratings yet

- Fabm Week 1 Asnd 2Document5 pagesFabm Week 1 Asnd 2John Calvin GerolaoNo ratings yet

- CH # 6 (Trees)Document31 pagesCH # 6 (Trees)Muhammad ImranNo ratings yet

- Cedr 341 Summary Questions and AnswersDocument72 pagesCedr 341 Summary Questions and Answersobinnabenedict123No ratings yet

- Thesis Topics in Medicine in Delhi UniversityDocument8 pagesThesis Topics in Medicine in Delhi UniversityBecky Goins100% (2)

- Ingles-Pasado SimpleDocument1 pageIngles-Pasado Simplemaritzaborquez.aNo ratings yet

- Vicenta Borja Breastfeeding LectureDocument23 pagesVicenta Borja Breastfeeding LectureSophie RoseNo ratings yet

- The Caravan Trade Is The Prominent Lead of CivilizationDocument3 pagesThe Caravan Trade Is The Prominent Lead of CivilizationkelvinroqueroNo ratings yet

- Soluciones Guillemin 2Document125 pagesSoluciones Guillemin 2Julian Uribe CastañedaNo ratings yet

- Jobs and Business Plan 2014-2017Document29 pagesJobs and Business Plan 2014-2017BarnsleyCouncilNo ratings yet

- glt1 Alternate AssignmentDocument7 pagesglt1 Alternate Assignmentapi-635141433No ratings yet

- Msra For Basement Parking Cable Pulling and ELV Room AccessDocument7 pagesMsra For Basement Parking Cable Pulling and ELV Room AccesshseNo ratings yet

- Outline: Outline:: BI/CH 422/622Document9 pagesOutline: Outline:: BI/CH 422/622Khadija JaraNo ratings yet

- Erp Research Paper - SynopsisDocument3 pagesErp Research Paper - SynopsisAshi GargNo ratings yet

- Dressmaking NC II - Coc 1 and Coc 2 - SagDocument3 pagesDressmaking NC II - Coc 1 and Coc 2 - SagRoderick FullerNo ratings yet

- 2229 - Unit 2 Bacterial NutritionDocument26 pages2229 - Unit 2 Bacterial Nutritionnirajkumar9439252No ratings yet

- ChatGPT MEGA CheatSheetDocument1 pageChatGPT MEGA CheatSheetDieguito RábaloNo ratings yet

- Philip Meadows by Jon DodsonDocument2 pagesPhilip Meadows by Jon Dodsonphuphighter0% (1)

- Olson Benjamin HedgeDocument134 pagesOlson Benjamin HedgeAdela WarsawNo ratings yet

- Ricardo V. Puno, Jr. and Conrado A. Boro For Plaintiff-AppellantDocument5 pagesRicardo V. Puno, Jr. and Conrado A. Boro For Plaintiff-AppellantParis LisonNo ratings yet

- FInal Exam KeyDocument27 pagesFInal Exam KeyQasim AtharNo ratings yet

- B.A. Hons Economics SEC 1 Financial EconomicsDocument3 pagesB.A. Hons Economics SEC 1 Financial EconomicsAkshara AwasthiNo ratings yet

- q4 Math Eqa ParentsDocument4 pagesq4 Math Eqa Parentsapi-296262817No ratings yet

- WEEK 8 Polynomial EquationsDocument4 pagesWEEK 8 Polynomial EquationsAzathoth AshkingNo ratings yet

- Childs 1993Document24 pagesChilds 1993deepdreamx6400No ratings yet

- Vision Collage of Management Kanpur Submitted To, Miss Keerti Tiwari Submitted By, M/S. Anam FatimaDocument24 pagesVision Collage of Management Kanpur Submitted To, Miss Keerti Tiwari Submitted By, M/S. Anam FatimaAnam FatimaNo ratings yet