Lab2 Block Level SSN Insertion On Processor Core

Uploaded by

zys WdLab2 Block Level SSN Insertion On Processor Core

Uploaded by

zys WdUnpublished work.

© 2021 Siemens

This material contains trade secrets or otherwise confidential information owned by Siemens Industry

Software Inc. or its affiliates (collectively, "SISW"), or its licensors. Access to and use of this information

is strictly limited as set forth in Customer's applicable agreement with SISW. This material may not be

copied, distributed, or otherwise disclosed outside of Customer's facilities without the express written

permission of SISW, and may not be used in any way not expressly authorized by SISW.

This document is for information and instruction purposes. SISW reserves the right to make changes in

specifications and other information contained in this publication without prior notice, and the reader

should, in all cases, consult SISW to determine whether any changes have been made. SISW disclaims

all warranties with respect to this document including, without limitation, the implied warranties of

merchantability, fitness for a particular purpose, and non-infringement of intellectual property.

The terms and conditions governing the sale and licensing of SISW products are set forth in written

agreements between SISW and its customers. SISW’s End User License Agreement may be viewed

at: www.plm.automation.siemens.com/global/en/legal/online-terms/index.html.

No representation or other affirmation of fact contained in this publication shall be deemed to be a

warranty or give rise to any liability of SISW whatsoever.

TRADEMARKS: The trademarks, logos, and service marks ("Marks") used herein are the property of

Siemens or other parties. No one is permitted to use these Marks without the prior written consent of

Siemens or the owner of the Marks, as applicable. The use herein of third party Marks is not an attempt

to indicate Siemens as a source of a product, but is intended to indicate a product from, or associated

with, a particular third party. A list of Siemens' trademarks may be viewed at:

www.plm.automation.siemens.com/global/en/legal/trademarks.html. The registered trademark Linux® is

used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on

a world-wide basis.

Support Center: support.sw.siemens.com

Send Feedback on Documentation: support.sw.siemens.com/doc_feedback_form

Table of Contents

Before you Begin .......................................................................................................................... 2

Lab 2: Block-level SSN Insertion on processor_core ................................................................... 3

Objectives .................................................................................................................................. 3

Introduction ................................................................................................................................ 3

Exercise 1: First DFT Insertion Pass: Performing Block-Level MemoryBIST .................................. 5

Exercise 2: Second DFT Insertion Pass: Inserting Block-Level EDT, OCC, and SSN ..................... 9

Exercise 3: Performing Synthesis for Block-Level ........................................................................13

Exercise 4: Performing Scan Chain Insertion using Tessent Scan................................................14

Exercise 5: Verifying the ICL-Based Patterns after Synthesis .......................................................18

Exercise 6: Generating Block-Level ATPG Patterns ....................................................................20

Exercise 7: Block-level SSN Insertion on gps_baseband (Optional) .............................................24

Introduction ...............................................................................................................................24

Lab Answers ................................................................................................................................29

Lab 2.........................................................................................................................................29

NOTES:.........................................................................................................................................31

Lab: Block-level SSN Insertion on processor_core 1

Before you Begin

You will need to:

1. Obtain lab data if you have not already done so.

2. Set environment variables.

Obtaining Lab Data

If the ssn_data directory, with lab subdirectories, is located in the home directory (e.g. cd ~), please

proceed to the lab exercises as you have already set up the lab database on this VM.

If this is the first time you are starting a session for this VM, the ssn_data directory will not be in the

home directory and you will need to download and extract it using the following instructions.

1. Double click on the Desktop icon Download_lab_data, . This launches a web browser.

2. On the resulting web page, select the file named tessent_ssn_data_v2021.2_20210907.tar.gz.

3. In the resultant window, select the Download button, enable the Save File button, then, select the OK

button to download the file.

4. Move the file in the Downloads directory to the home directory. If you are using the terminal

(Applications>Favorites>Terminal) you can use the following command:

mv ./Downloads/tessent_ssn_data_v2021.2_20210907.tar.gz .

5. In a terminal window, extract the files from the compressed tar file using the command:

tar xzvf ./tessent_ssn_data_v2021.2_20210907.tar.gz

You should now have a directory named ssn_data in your Home directory. That directory contains all the

files you need to perform the exercises, in this learning path.

Setting Environment Variables

The environment uses bash and is ready to use for the labs with all needed environment variables already

setup.

$SSN_LABS is an environment variable set up under the home directory that points to the training data

directory. If it is not already set up, you can execute SETENV SSN_LABS $HOME/ssn_data at your Linux

prompt to create it.

You are now ready to proceed with lab exercises.

Lab: Block-level SSN Insertion on processor_core 2

Lab 2: Block-level SSN Insertion on

processor_core

Objectives

Upon completing this lab, you should be able to:

• Insert block-level SSN circuitry on the processor_core (core contains memories)

• Generate and simulate core level patterns

• Set ssn_bus_clock_period and shift_clock_period to non-default values

• Report scan host core instance names

• Report bits per packet for patterns generated for the processor_core

Introduction

In the general SSN workflow, you perform a bottom-up DFT insertion for each physical block followed by

DFT insertion at the parent level. You continue this bottom-up flow until you have reached the top-level of

the design.

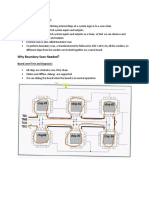

This lab is designed as demonstrated in the following figure, we have a simple chip which is an RTL

design, having three wrapped cores:

• Two gps_baseband cores

• One processor_core

Figure 2.1 Lab Design

TestKompress EDT logic will also be created for the top-level. You can see that we have some pipeline

stages in each one of the physical blocks, as well as at the input and the output of the SSN datapath.

For the SSN architecture, we have one single SSH in each physical block with an SSN bus width of 2 bits,

with SSN pipeline stage nodes at the chip interface to ensure timing. There’s also a receiver pipeline at the

first SSN node from the primary input pads and an output pipeline at the last SSN node before the primary

output pads.

Lab: Block-level SSN Insertion on processor_core 3

In addition to that, the multiplexer can bypass the gps_baseband cores if desired so that we can only focus

on the processor_core to operate the SSN with that option.

The following figure shows a block-level workflow used to process a child physical block when you are

using SSN. If you have any memories to test in that block, then you need to perform the first DFT insertion

pass, otherwise, you can ignore this step.

As highlighted in the figure, you insert SSN into the design during the second DFT insertion pass and in

this same step, you add a second smaller EDT implementation in the design for the wrapper chains during

the external test mode. The new Tessent logic created is described in RTL Verilog.

After that, you use a 3rd party application (non-Tessent) to produce the synthesized netlist and then use

Tessent for the scan insertion step. For this lab and the upcoming ones, the synthesized netlist is provided

for you since the lab environment does not include a synthesis tool to use. In your real work environment,

you might do scan chain stitching as part of the synthesis process. Hence the decision box in the diagram.

After scan chains are inserted, you will perform the ICL Based Patterns Verification step, which uses the

automation of create_patterns_specification / process_patterns_specfication for

specifying and creating the ICLNetwork and Continuity patterns, and as a final step, you will generate the

ATPG patterns.

Figure 2.2 SSN Block-Level Workflow

In this lab, we will be implementing this workflow on the processor_core, and we provide the

gps_baseband core steps if you want to run them optionally.

Lab: Block-level SSN Insertion on processor_core 4

Exercise 1: First DFT Insertion Pass: Performing

Block-Level MemoryBIST

In this exercise, you will perform the first DFT insertion pass that inserts the non-scan DFT elements, such

as memory BIST and IJTAG.

This lab exercise guides you through the Tessent MemoryBIST flow where you setup your design, then

use default settings to implement and validate memory BIST.

All of the required libraries (Tessent cell, Verilog, Memory) are located in a common directory

$SSN_LABS/libs/library.

Instructions

Change to the $SSN_LABS/Lab2/Exercise1 directory.

$ cd $SSN_LABS/Lab2/Exercise1

Notice that all the following commands have already been added to the script

in the following path solutions/run_mbist_insertion. To run the script properly,

Note make sure you are in the Exercise1 directory then

execute ./solutions/run_mbist_insertion

Invoke Tessent Shell.

$ tessent –shell –logfile logfiles/Lab2_Ex1.log -replace

Set the context to insert DFT into an RTL-level design.

SETUP> set_context dft -rtl -design_id rtl1

For this lab, all the Tessent cell libraries are stored in a single file.

SETUP> read_cell_library \

../../libs/library/standard_cells/tessent/adk.tcelllib

Specify the location of the Tessent Shell Data Base (TSDB) directory.

SETUP> set_tsdb_output_directory ../tsdb_outdir

Lab: Block-level SSN Insertion on processor_core 5

Read in the memory library models. Since the design you are working on is made up of multiple files,

and there are multiple memory models modeled as Tessent core descriptions, you will use

set_design_sources to specify the location of the files. When the netlist is read in and the

design is elaborated, Tessent Shell will use the defined pathnames to search for the required files.

SETUP> set_design_sources -format tcd_memory \

-y ../../libs/library/memories \

-extension tcd_memory

Read in the Verilog memory model to load the design into the tool.

SETUP> read_verilog ../../libs/library/memories/*.v \

-exclude_from_file_dictionary

Now read in the design RTL files from a file list.

SETUP> read_verilog -f rtl_file_list

The final step in loading the design and libraries is to elaborate the design using

set_current_design.

SETUP> set_current_design processor_core

Now that the design is loaded and elaborated, the next step is to specify the requirements for

MemoryBIST.

By specifying the design level, Tessent MemoryBIST will know what type of IJTAG and MemoryBIST

IP to insert. TAP controllers and BISR controllers are inserted at the top, or chip level. In a

hierarchical design, the chip architect defines physical blocks, (modules that will be synthesized) and

sub-blocks (modules that are included as part of the physical blocks). The module you are working on

is a physical block in this exercise.

SETUP> set_design_level physical_block

Specify that you will be inserting memory BIST into this physical block. Specifying -memory_test

on is equivalent to setting the three options -memory_bist, -memory_bisr_chains, and -

memory_bisr_controller to auto, this is a desirable setting.

SETUP> set_dft_specification_requirements -memory_test on

For memory BIST to operate, a clock needs to be supplied. Identify the free-running clock that is a

primary input of this physical block that will be used for memory test.

SETUP> add_clocks 0 dco_clk -period 3.0ns

The next step for specifying requirements is to run DRCs by executing the command

check_design_rules.

SETUP> check_design_rules

Lab: Block-level SSN Insertion on processor_core 6

After the design passes DRCs with no errors reported, the next step is to have Tessent MemoryBIST

generate a DftSpecification. This specification, based on your requirements, will determine what test

circuitry will be added to your design.

ANALYSIS> set spec [create_dft_specification]

As various specifications are created, an optional variable name can be associated with them with the

TCL ‘set’ command as shown above. When you use the report configuration data command you may

specify a specification name or report all configurations.

ANALYSIS> report_config_data $spec

The next step is to create and insert the IP into the design netlist.

ANALYSIS> process_dft_specification

This command also creates the Tessent Shell database (TSDB) if it doesn’t already exist, where all the

information required to implement this block is stored.

Note that the system mode changes to the INSERTION mode after the command completes.

Extract the ICL netlist description for the module processor_core.

INSERTION> extract_icl

Generate the patterns specification using default settings.

SETUP> set spec [create_patterns_specification]

To create the patterns and testbenches, you must process the PatternsSpecification.

SETUP> process_patterns_specification

Specify the location of the simulation library models using

the set_simulation_library_sources command.

SETUP> set_simulation_library_sources \

-v ../../libs/library/standard_cells/verilog/adk.v \

-v ../../libs/library/memories/*.v

Validate the IJTAG and MBIST insertion by running the testbench simulations.

SETUP> run_testbench_simulations

Lab: Block-level SSN Insertion on processor_core 7

There should not be any simulation failures. Notice that the status of the simulations is reported as

they run. If you would like to check the pass/fail results of simulations that have been run previously,

use:

SETUP> check_testbench_simulations -report_status

Exit Tessent Shell.

SETUP> exit

This is the end of Exercise 1.

Lab: Block-level SSN Insertion on processor_core 8

Exercise 2: Second DFT Insertion Pass: Inserting

Block-Level EDT, OCC, and SSN

In this exercise, you will perform the second DFT insertion pass. In this pass you insert the block-level

EDT, OCC, and SSN elements. After the insertion of the SSN and the other logic test elements, you must

simulate the ICLNetwork patterns to verify the correct IJTAG access to all inserted logic test elements,

including the SSN elements. Following a successful simulation of the ICLNetwork patterns, you must

simulate the SSN Continuity patterns to verify that the SSN datapath is correctly integrated into the design.

Step 1: Insert SSH, EDT, and OCC

Similar to EDT and OCC, the tool creates the SSN hardware based on the SSN wrapper defined in the

DftSpecification. For a description of the SSN wrapper, see the “SSN” wrapper description in the Tessent

Shell Reference Manual.

When the tool creates the SSH, EDT, and OCC elements with a single invocation of

the process_dft_specification command, the tool automates the connections between the SSH, EDT, and

OCC instances. Let's follow this procedure:

• Both prefixed and bussed scan input and output pins can be used. For bussed pins, the buses

must be ordered either ascending or descending (not randomly ordered).

• Scan chains must have dedicated input/output pins. This is the default operation for the

insert_test_logic command in Tessent Scan.

Instructions

1. Change to the $SSN_LABS/Lab2/Exercise2 directory.

$ cd $SSN_LABS/Lab2/Exercise2

Notice that all the following commands have already been added to the script

in the following path: solutions/run_ssh_edt_occ_insertion; to run the script

properly, make sure you are in the Exercise2 directory then run ./solutions/

Note run_ssh_edt_occ_insertion

2. Invoke Tessent Shell.

$ tessent -shell -logfile logfiles/Lab2_Ex2.log -replace

3. Set the context to insert DFT into an RTL-level design. Note that the design_id is changed for this

step to rtl2. This file will be used in filenames in the TSDB.

SETUP> set_context dft -rtl -design_id rtl2

Lab: Block-level SSN Insertion on processor_core 9

4. Specify the location of the Tessent Shell Data Base (TSDB) directory.

SETUP> set_tsdb_output_directory ../tsdb_outdir

5. Read the Library by specifying the specific file name.

SETUP> read_cell_library \

../../libs/library/standard_cells/tessent/adk.tcelllib

6. Load design files from the TSDB directory that correspond to the rtl1 design id.

SETUP> read_design processor_core -design_id rtl1 \

-verbose

7. Read in the memory Verilog models to load them into the tool.

SETUP> read_verilog ../../libs/library/memories/*.v \

-exclude_from_file_dictionary

8. The final step in loading the design and libraries is to elaborate the design using

set_current_design.

SETUP> set_current_design processor_core

9. Now add static DFT signals that include global DFT control, logic test control, and scan mode signals,

these DFT signals are typically controlled by a Test Data Register that is part of the IJTAG network.

a. Add ltest_en which is the logic test control signal that is used to enable the logic test mode.

SETUP> add_dft_signals ltest_en

b. Add memory_bypass_en which is the logic test control signal that is used to enable the isolation

around the memories, also it is used to test memories with multi-load ATPG patterns.

SETUP> add_dft_signals memory_bypass_en

c. Add tck_occ_en, which is a global DFT control signal that is used to control the multiplexer used

to inject TCK at the base of the clock trees.

SETUP> add_dft_signals tck_occ_en

d. Add the DFT signals used for the hierarchical DFT implementation.

SETUP> add_dft_signals int_ltest_en \

ext_ltest_en \

int_mode \

ext_mode \

int_edt_mode \

ext_edt_mode

Lab: Block-level SSN Insertion on processor_core 10

10. Report all the DFT signals added in the design.

SETUP> report_dft_signals

Specify the requirements to be checked during the design rule check, here you will specify the logic

test.

SETUP> set_dft_specification_requirements -logic_test on

The next step for specifying requirements is to run DRCs by executing the command

check_design_rules.

SETUP> check_design_rules

After the design passes DRCs with no errors reported, the next step is to create IJTAG host nodes for

the EDT, OCC, and SSN wrappers.

ANALYSIS> set spec [create_dft_specification \

-sri_sib_list {edt occ ssn}]

As various specifications are created a specific name can be associated with them. When you use

the report configuration data command you may specify a specification name or report all

configurations.

ANALYSIS> report_config_data $spec

Run the dofile that contains the wrappers having all the specifications for your specific design

requirements.

ANALYSIS> dofile wrappers.do

Question 1: How many EDT controllers are inserted? What are they?

_______________________________________________________________

The next step is to generate and insert the IP into the design netlist. Then review the specification.

ANALYSIS> process_dft_specification

INSERTION> report_config_data $spec

Extract the ICL netlist description and enable the –create_ijtag_graybox switch to generate

the IJTAG graybox during ICL extraction.

INSERTION> extract_icl -create_ijtag_graybox on

Specify the write_design_import_script command to create a dc_shell design load script

that you can use to load the RTL design into this new file to elaborate and synthesize later.

SETUP> write_design_import_script \

processor_core.dc_design_load_script \

-use_relative_path_to ../Exercise3 –replace

Lab: Block-level SSN Insertion on processor_core 11

Create the ICL Network patterns and the SSN continuity patterns by generating a patterns

specification using default settings.

SETUP> set spec [create_patterns_specification]

SETUP> process_patterns_specification

The command create_patterns_specification creates a patterns specification for the SSN

continuity patterns and the ICL network that includes the IJTAG logic, SSN logic, and the MemoryBIST

logic.

Report the patterns configuration wrappers that are created.

SETUP> report_config_data $spec

Specify the location of the simulation library models using

the set_simulation_library_sources command.

SETUP> set_simulation_library_sources \

-v ../../libs/library/standard_cells/verilog/adk.v \

-v ../../libs/library/memories/*.v

Question 2: What are the two types of patterns created to verify the SSN datapath?

__________________________________________________________________

Run the simulations.

SETUP> run_testbench_simulations

SETUP> check_testbench_simulations -report_status

The run_testbench_simulations command supports the simulation

of the SSN continuity patterns.

Note

Exit Tessent Shell.

ANALYSIS> exit

This is the end of Exercise 2.

Lab: Block-level SSN Insertion on processor_core 12

Exercise 3: Performing Synthesis for Block-Level

In the previous exercise, you used the write_design_import_script command to export a design

load script for use in your synthesis tool.

You will not perform synthesis on the block in this lab, this step is already done for you.

Using any text editor, review the synthesis script:

$ SSN_LABS/Lab2/Exercise2/solutions/processor_core.dc_synth_script

Change to the $SSN_LABS/Lab2/Exercise3 directory.

$ cd $SSN_LABS/Lab2/Exercise3

$ ls -ls

Examine the .timing_options script provided for this step. This script specifies the TCK period and the

set_load_unload_timing_options values.

Using any text editor, review the synthesized design file created for you to be used in subsequent

steps.

$ vi processor_core_synthesized.vg

Close the file when you are done.

This is the end of Exercise 3.

Lab: Block-level SSN Insertion on processor_core 13

Exercise 4: Performing Scan Chain Insertion using

Tessent Scan

Scan chain insertion for wrapped cores includes a task for performing wrapper analysis, which prepares

the functional scannable sequential elements (or “flops”) for potential reuse as wrapper scan cells.

When SSN is present, the tool connects wrapper scan chains to the second smaller EDT controller added

during exercise 2.

More information on the Tessent Shell commands used during this exercise can be found under the

Command Dictionary chapters found in the Tessent Shell Reference Manual.

The commands, with in-line comments, to run the scan insertion step are

also available in an executable dofile within the solutions folder for this

exercise. To run the script properly, make sure you are in the Exercise4

Note directory then run ./solutions/run_scan_insertion

Change to the $SSN_LABS/Lab2/Exercise4 directory.

$ cd $SSN_LABS/Lab2/Exercise4

Invoke Tessent Shell.

$ tessent -shell -logfile logfiles/Lab2_Ex4.log -replace

Set the context for DFT scan insertion.

SETUP> set_context dft -scan

Set the output TSDB directory location.

SETUP> set_tsdb_output_directory ../tsdb_outdir

Read the DFT cell libraries.

SETUP> read_cell_library \

../../libs/library/standard_cells/tessent/adk.tcelllib

Read the synthesized netlist.

SETUP> read_verilog \

../Exercise3/processor_core_synthesized.vg

Lab: Block-level SSN Insertion on processor_core 14

The read_design command is an efficient way to load a design into

Tessent Shell for DFT insertions or pattern generation. The –design_id

option identifies which version of the design to load from the tsdb_outdir.

Using the –no_hdl option restricts the reading to all files in the tsdb_outdir

except the design.

More information about the read_design command and its options are

available in the Command Dictionary in the Tessent Shell Reference

Manual.

Load design files from the TSDB directory that corresponds to the rtl2 design id.

SETUP> read_design processor_core \

-design_identifier rtl2 -no_hdl –verbose

Elaborate the design.

SETUP> set_current_design processor_core

If there are no ATPG models available for memories, use blackboxes.

SETUP> add_black_boxes -modules {SYNC_1RW_8Kx16}

Report all the settings implied to the static DFT signals added.

SETUP> report_static_dft_signal_settings

The pre-registered DFT Signals are by default available for use without

issuing the add_dft_signals command.

More information about the add_dft_signals command and its options

are available in the Command Dictionary in the Tessent Shell Reference

Manual.

Check the design rules.

SETUP> check_design_rules

Report the current set of clocks and confirm that the OCC clock control registers are reported as

scan segments.

ANALYSIS> report_clocks

ANALYSIS> report_scan_segment

Report all the static DFT signals added.

ANALYSIS> report_dft_signals

Lab: Block-level SSN Insertion on processor_core 15

Perform and report the wrapper cell analysis.

ANALYSIS> analyze_wrapper_cells

ANALYSIS> report_wrapper_cells -verbose

Create a scan mode and specify the EDT instance to connect the scan chains to and assign it to its

intended scan mode.

ANALYSIS> set edt_instance [get_instances \

-of_icl_instances [get_icl_instances \

-filter tessent_instrument_type==mentor::edt]]

ANALYSIS> foreach_in_collection edt $edt_instance \

{ if {[regexp {.*int.*} [get_single_name \

$edt] int_edt_instance]} \

{ puts "Found EDT instance $int_edt_instance.\

Will use this instance for internal scan_mode."\

} elseif {[regexp {.*ext.*} [get_single_name \

$edt] ext_edt_instance]} \

{ puts "Found EDT instance $ext_edt_instance.\

Will use this instance for external scan_mode."\

}\

}

ANALYSIS> add_scan_mode int_edt_mode -edt_instances \

$int_edt_instance

ANALYSIS> add_scan_mode ext_edt_mode -edt_instances \

$ext_edt_instance

Analyze the scan chains and review the different scan modes and chains before stitching the chains.

ANALYSIS> analyze_scan_chains

ANALYSIS> report_scan_chains

Insert scan chains and save reports regarding the scan chains and scan cells.

ANALYSIS> insert_test_logic

INSERTION> report_scan_chains

INSERTION> report_scan_cells > scan_cells.list

Lab: Block-level SSN Insertion on processor_core 16

Check the design rules of the scan chains in each mode then create a scan graybox model for

external mode.

INSERTION> set_context patterns -scan

SETUP> add_black_boxes -modules { SYNC_1RW_8Kx16 }

SETUP> foreach_in_collection mode_wrapper \

[get_config_elements \ Core(processor_core)/Scan/Mode \

-part tcd -silent] { \

set mode_name [get_config_value $mode_wrapper -id <0>] \

set mode_type [get_config_value type -in $mode_wrapper] \

import_scan_mode $mode_name \

report_clocks \

check_design_rules \

if {$mode_type eq "external"} { \

report_scan_cells \

analyze_graybox –scan \

write_design -tsdb -graybox -verbose} \

set_system_mode setup}

Create the IJTAG graybox model.

SETUP> set_context patterns -ijtag

SETUP> check_design_rules

ANALYSIS> analyze_graybox -ijtag

ANALYSIS> write_design -tsdb -graybox –verbose

Exit Tessent Shell.

ANALYSIS> exit

This is the end of Exercise 4.

Lab: Block-level SSN Insertion on processor_core 17

Exercise 5: Verifying the ICL-Based Patterns after

Synthesis

The ICL-based verification step verifies the ICL network before the patterns generation step.

You will resimulate the MemoryBIST, ICL verification, and SSN continuity patterns after synthesis to

ensure the ICL network is fully functional and able to be reliably used during ATPG and Scan retargeting

setup.

Step 1: Create Post Synthesis ICL Verification Patterns

Change to the $SSN_LABS/Lab2/Exercise5 directory.

$ cd $SSN_LABS/Lab2/Exercise5

Invoke Tessent Shell and start a logfile.

$ tessent –shell –logfile logfiles/Lab2_Ex5.log –replace

Set the context to patterns to create ICL-based patterns.

SETUP> set_context patterns

Set the output TSDB directory location.

SETUP> set_tsdb_output_directory ../tsdb_outdir

Load design files from the TSDB directory.

SETUP> read_design processor_core \

-design_identifier gate -view interface

Elaborate the design.

SETUP> set_current_design processor_core

Generate patterns to verify the inserted DFT logic.

SETUP> set spec [create_patterns_specification]

SETUP> process_patterns_specification

SETUP> report_config_data $spec

The command create_patterns_specification creates a patterns specification for the SSN

continuity patterns and the ICL network that includes the IJTAG logic, SSN logic, and the MemoryBIST

logic if present.

Lab: Block-level SSN Insertion on processor_core 18

Point to the Verilog model libraries and run the simulation.

SETUP> set_simulation_library_sources \

-v ../../libs/library/standard_cells/verilog/adk.v\

-v ../../libs/library/memories/*.v

SETUP> run_testbench_simulations

SETUP> check_testbench_simulations -report_status

No errors should be reported between simulated and expected patterns.

Exit Tessent Shell.

SETUP> exit

This is the end of Exercise 5.

Lab: Block-level SSN Insertion on processor_core 19

Exercise 6: Generating Block-Level ATPG Patterns

Generating ATPG test patterns for a wrapped core includes a step for generating a graybox model, you

already did this with the scan insertion step.

Run ATPG on the internal mode of the wrapped core. This results in the ATPG patterns that you retarget at

the top-level of the chip.

Step 1: Generate ATPG Patterns

You will generate the ATPG patterns for the stuck-at fault model.

Change to the $SSN_LABS/Lab2/Exercise6 directory.

$ cd $SSN_LABS/Lab2/Exercise6

Invoke Tessent Shell and start a logfile.

$ tessent –shell –logfile logfiles/Lab2_Ex6_stuck.log \

-replace

Set the context to patterns.

SETUP> set_context patterns -scan

Set the output TSDB directory location.

SETUP> set_tsdb_output_directory ../tsdb_outdir

Read the DFT cell libraries.

SETUP> read_cell_library \

../../libs/library/standard_cells/tessent/adk.tcelllib

Load design files from the TSDB directory.

SETUP> read_design processor_core -design_id gate \

-verbose

Elaborate the design.

SETUP> set_current_design processor_core

Specify the current mode using a unique name different than add_scan_mode, then bring in the

desired scan mode configuration.

SETUP> set_current_mode int_edt_mode_stuck \

-type internal

SETUP> import_scan_mode int_edt_mode -fast_capture off

Lab: Block-level SSN Insertion on processor_core 20

Import timing options used during the synthesis step.

SETUP> source ../Exercise3/processor_core.timing_options

Define the tck period and the ijtag retargeting options.

SETUP> set_ijtag_retargeting_options -tck_period \

$processor_core_tck_period

Define the slow clock capture timing.

SETUP> set_capture_timing_options –mode_type internal \

-capture_clock_period 40ns

SETUP> set_core_instance_parameters \

-instrument_type occ -parameter_values \

{capture_window_size 3}

If there are no ATPG models available for memories, use blackboxes.

SETUP> add_black_boxes -modules { SYNC_1RW_8Kx16 }

Check design rules.

SETUP> check_design_rules

Specify the fault model type to stuck-at fault model.

ANALYSIS> set_fault_type stuck

Generate the patterns.

ANALYSIS> create_patterns

ANALYSIS> report_statistics –detail

Question 1: Answer the following:

i. The total relevant test coverage: __________________________

ii. The number of test patterns: _____________________________

Store TCD, flat_model, fault list, and patDB format files in the TSDB directory.

ANALYSIS> write_tsdb_data –replace

Write parallel load testbench.

ANALYSIS> write_patterns \

patterns/processor_core_int_edt_mode_stuck_parallel.v \

-verilog -replace -parameter_list \

{SIM_COMPARE_SUMMARY 1 SIM_KEEP_PATH 1} \

-pattern_set scan

Lab: Block-level SSN Insertion on processor_core 21

Write SSH loopback testbench.

ANALYSIS> write_patterns \

patterns/processor_core_int_edt_mode_stuck_ssh_loop.v \

-verilog -serial -replace -parameter_list \

{SIM_COMPARE_SUMMARY 1 SIM_KEEP_PATH 1} \

-pattern_set ssn_loopback

Write chain and scan patterns.

ANALYSIS> set_chain_test -type nomask

ANALYSIS> write_patterns \

patterns/processor_core_int_edt_mode_stuck_serial_chain.v \

-verilog -serial -replace -end 0 \

-parameter_list {SIM_COMPARE_SUMMARY 1 \

SIM_KEEP_PATH 1} -pattern_set chain

ANALYSIS> write_patterns \

patterns/processor_core_int_edt_mode_stuck_serial_scan.v \

-verilog -serial -replace -end 0 \

-parameter_list {SIM_COMPARE_SUMMARY 1 \

ALL_EXCLUDE_UNUSED 0 SIM_KEEP_PATH 1} \

-pattern_set scan

Exit Tessent Shell.

ANALYSIS> exit

Notice that all the previous commands had already been added to the script in

the following path solutions/run_internal_stuck; to run the script properly make

Note sure you are in the Exercise6 directory then run ./solutions/run_internal_stuck

You will perform the same as the previous step but now you will generate ATPG patterns for the transition

fault model instead of the stuck-at fault.

Generate patterns for the transition fault model, run the run_internal_transition script.

$ ./run_internal_transition

Question 2: Answer the following:

i. The total relevant test coverage: __________________________

ii. The number of test patterns: ______________________________

Lab: Block-level SSN Insertion on processor_core 22

Step 2: Simulate Patterns

In this step, you will simulate the testbench patterns to confirm that the SSN network can successfully

deliver packetized data to the SSH. We do this by first simulating the parallel load patterns, once these are

clean, simulate the serial loopback patterns, followed by 1 serial chain pattern and 1 serial scan pattern.

Review the run_sims script using any text editor, notice that the sequence of patterns to be simulated

is repeated twice, for stuck-at and transition patterns.

Simulate test pattern testbenches.

$ ./run_sims

You should have no errors.

This is the end of Exercise 6.

Lab: Block-level SSN Insertion on processor_core 23

Exercise 7: Block-level SSN Insertion on

gps_baseband (Optional)

In this Exercise, we will go through the necessary steps for inserting SSN into the gps_baseband core

which is instantiated twice in the top-level design.

Figure 2.3: Lab Design

Introduction

In the general SSN Workflow, you perform a bottom-up DFT insertion for each physical block followed by

DFT insertion at the parent level. You continue this bottom-up flow until you have reached the top-level of

the design.

The gps_baseband cores do not contain any memories, so we will skip the first DFT insertion pass.

SSN Block-Level Workflow for the GPS_baseband core:

• DFT Insertion Pass: Inserting block-level EDT, OCC, and SSN

• Synthesis for block-level insertion

• Performing Scan Chain insertion

• Verifying ICL-based verification patterns

• Generating block-level ATPG patterns

Lab: Block-level SSN Insertion on processor_core 24

Step 1: DFT Insertion Pass: Inserting Block-Level EDT, OCC, and SSN

In this DFT insertion pass, you insert the block-level EDT, OCC, and SSN elements. After the insertion of

the SSN and the other logic test elements, you must simulate the ICLNetwork patterns to verify the correct

IJTAG access to all inserted logic test elements, including the SSN elements. Following a successful

simulation of the ICLNetwork patterns, you must simulate the SSN Continuity patterns to verify that the

SSN datapath is correctly integrated into the design.

Insert SSH, EDT, and OCC

Similar to EDT and OCC, the tool creates the SSN hardware based on the SSN wrapper of the

DftSpecification. For a description of the SSN wrapper, see the “SSN” wrapper description in the Tessent

Shell Reference Manual.

When the tool creates the SSH, EDT, and OCC elements at the same time with a single invocation of

the process_dft_specification command, the tool automates the connections between the SSH, EDT, and

OCC instances. Let's follow this procedure:

• Both prefixed and bussed scan input and output pins can be used. For bussed pins, the buses

must be ordered either ascending or descending (not randomly ordered).

• Scan chains must have dedicated input/output pins. This is the default operation for the

insert_test_logic command in Tessent Scan.

Instructions

Go to Exercise7/Step1 directory in Lab2 and study the files used for this step.

$ cd $SSN_LABS/Lab2/Exercise7/Step1

$ ls -ls

Review the run_ssh_edt_occ_insertion dofile. You will use this dofile to insert the SSH, EDT, and

OCC into your design and generate the ICL patterns and SSN continuity patterns. Make sure you

understand all the steps in this dofile, attempt the following questions.

Question 1: How many EDT controllers are inserted? What are they?

________________________________________________________

Question 2: What are the two types of patterns created to verify the SSN datapath?

________________________________________________________

Question 3: What command is used to create the continuity patterns?

________________________________________________________

Lab: Block-level SSN Insertion on processor_core 25

Run the dofile.

$ ./run_ssh_edt_occ_insertion

This should complete without any errors.

Step 2: Performing Synthesis for Block-Level

In the previous step, you used the command write_design_import_script, to create a design

load script of all the RTL to be used with your synthesis tool.

You will not perform synthesis on the block in this lab, this step is already done for you.

Using any text editor, review the synthesis script.

$SSN_LABS/Lab2/Exercise7/solutions/gps_baseband.dc_synth_script

Go to the Step2 directory.

$ cd $SSN_LABS/Lab2/Exercise7/Step2

$ ls -ls

Examine the timing_options script provided for this step. This script specifies the TCK period and the

other set_load_unload_timing_options values.

Using any text editor, review the synthesized design created for you to be used in subsequent steps:

$ vi gps_baseband_synthesized.vg

Close the file when you are done.

Step 3: Performing Scan Chain Insertion using Tessent Scan

The Tessent Scan insertion step in the SSN flow is similar to the scan chain insertion step in the Tessent

Shell Flow for hierarchical designs. When the SSN is present, the tools connect wrapper chains to the

second, smaller EDT controller.

Go to the Step3 directory.

$ cd $SSN_LABS/Lab2/Exercise7/Step3

All needed commands are added to the run_scan_insertion dofile. Using any text editor, review this file and

notice the following:

• Two different scan modes are created: int_edt_mode and ext_edt_mode.

• Each EDT instance is assigned to its intended scan mode.

• The design rule check is performed on each scan mode and the graybox model is created for the

external mode.

Lab: Block-level SSN Insertion on processor_core 26

Run the dofile.

$ ./run_scan_insertion

Step 4: Verifying the ICL-Based Patterns after Synthesis

Resimulating the ICL verification patterns after synthesis ensures the ICL network is fully functional and

able to be reliably used during the ATPG and Scan retargeting setup.

When using SSN, it is important to also reverify the SSN continuity patterns after synthesis before we try to

use it for ATPG and Scan retargeting.

Go to the Step4 directory.

$ cd $SSN_LABS/Lab2/Exercise7/Step4

Review the create_post_synthesis_icl_verification_patterns script using any text editor, notice that the

script creates and verifies the ICL based IJTAG patterns, and creates the SSN ICL-based continuity

patterns.

Run the dofile.

$ ./create_post_synthesis_icl_verification_patterns

Step 5: Generating Block-Level ATPG Patterns

The process for generating ATPG Patterns in the SSN flow is similar to the process used

without SSN.

Go to the Step5 directory.

$ cd $SSN_LABS/Lab2/Exercise7/Step5

Review the run_internal_stuck script and the run_internal_transition script using any text editor,

notice the following:

a. The first script creates stuck-at fault patterns, while the second creates transition fault patterns.

b. Parallel load and SSH loopback patterns are written out.

Run the dofile run_internal_stuck.

$ ./run_internal_stuck

Question 1: Answer the following:

The total relevant test coverage: _________________________

The number of test patterns: ____________________________

Lab: Block-level SSN Insertion on processor_core 27

Run the dofile run_internal_transition.

$ ./run_internal_transition

Question 2: Answer the following:

The total relevant test coverage: __________________________

The number of test patterns: ____________________________

Simulate Patterns

In this step, you will simulate the ATPG patterns to confirm that the SSN network can successfully deliver

packetized data to the SSH. We do this by first simulating the parallel load patterns, once these are clean,

simulate the serial loopback patterns, followed by 1 serial chain pattern and 1 serial scan pattern.

Review the run_sims script using any text editor, notice that the sequence of patterns to be simulated

is repeated twice, for stuck-at and transition patterns.

Run the dofile run_sims.

$ ./run_sims

No errors should be reported between simulated and expected patterns.

This is the end of Exercise7 and Lab2.

Lab: Block-level SSN Insertion on processor_core 28

Lab Answers

Lab 2

Exercise 2

How many EDT controllers are inserted? What are they?

• Two controllers, c1_int and c1_ext.

What are the two types of patterns created to verify the SSN datapath?

• ICL Network Patterns and Continuity Patterns.

Exercise 6

The total relevant test coverage: 97.55%

The number of test patterns: 508

The total relevant test coverage: 93.07%

The number of test patterns: 1238

Exercise 7

Step 1

How many EDT controllers are inserted? What are they?

• Two controllers, c1_int and c1_ext.

What are the two types of patterns created to verify the SSN datapath?

• ICL Network Patterns and Continuity Patterns.

What command is used to create the continuity patterns?

create_patterns_specifications

Step 5

The total relevant test coverage: 98.65%

The number of test patterns: 677

Lab: Block-level SSN Insertion on processor_core 29

The total relevant test coverage: 79.69%

The number of test patterns: 1611

Lab: Block-level SSN Insertion on processor_core 30

NOTES:

Lab: Block-level SSN Insertion on processor_core 31

You might also like

- Tessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics Corporation0% (1)Tessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics Corporation13 pages

- ATPG Simulation Mismatch - Common Problems and Solutions100% (1)ATPG Simulation Mismatch - Common Problems and Solutions6 pages

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeNo ratings yetFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A Time15 pages

- Scan Insertion Lab Observation (K.S.K.S.sarma)100% (3)Scan Insertion Lab Observation (K.S.K.S.sarma)33 pages

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test Case100% (1)A Practical Clock Control Circuit Design & Example Tessent ATPG Test Case22 pages

- Embedded Deterministic Test: by M. Balakrishna50% (2)Embedded Deterministic Test: by M. Balakrishna28 pages

- 1 LOS and LOC in Vlsi Conference-ProceedingNo ratings yet1 LOS and LOC in Vlsi Conference-Proceeding9 pages

- Why Masking Is Needed: Scan Chain Masking in The AcompactorNo ratings yetWhy Masking Is Needed: Scan Chain Masking in The Acompactor6 pages

- Scan Insertion Lab Observations: Vlsiguru DFT Training100% (1)Scan Insertion Lab Observations: Vlsiguru DFT Training3 pages

- DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design100% (1)DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design4 pages

- Simulation Mismatches Can Foul Up Test-Pattern Verification100% (1)Simulation Mismatches Can Foul Up Test-Pattern Verification6 pages

- SAS Programming Guidelines Interview Questions You'll Most Likely Be AskedFrom EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be AskedNo ratings yet

- Internet of Things (Iot) Cybersecurity: Literature Review and Iot Cyber Risk ManagementNo ratings yetInternet of Things (Iot) Cybersecurity: Literature Review and Iot Cyber Risk Management21 pages

- SAP Development Strategy_BTP Partner Forum Bcn_20230316No ratings yetSAP Development Strategy_BTP Partner Forum Bcn_2023031669 pages

- Oracle 11g Business Intelligence Enterprise Edition (OBIEE)No ratings yetOracle 11g Business Intelligence Enterprise Edition (OBIEE)6 pages

- XY-MBZ55A-YC1155-Bluetooth-5-BR-EDR-BLE-module-Datasheet-20211101No ratings yetXY-MBZ55A-YC1155-Bluetooth-5-BR-EDR-BLE-module-Datasheet-2021110127 pages

- FactoryTalk Historian SE Basic Lab (RAcbi) - 8-28-2018-IN05No ratings yetFactoryTalk Historian SE Basic Lab (RAcbi) - 8-28-2018-IN05100 pages

- Unicast Routing Protocols: Rip, Ospf, and BGPNo ratings yetUnicast Routing Protocols: Rip, Ospf, and BGP82 pages

- Class Xii CS Practical List Session 2020No ratings yetClass Xii CS Practical List Session 20203 pages

- Trainee Application Form (Technical Trainee) : Yes NoNo ratings yetTrainee Application Form (Technical Trainee) : Yes No2 pages

- Advance Ethical Hacking Course Contents UpdatedNo ratings yetAdvance Ethical Hacking Course Contents Updated11 pages

- Aaron Nace - 10 Tips For Photoshop Beginners - Reference GuideNo ratings yetAaron Nace - 10 Tips For Photoshop Beginners - Reference Guide12 pages

- Oral - Presentation - RT2018 - NCruz - RNC - Software - ArchitectureNo ratings yetOral - Presentation - RT2018 - NCruz - RNC - Software - Architecture14 pages

- Payment Solutions For Travel Platform: SabreNo ratings yetPayment Solutions For Travel Platform: Sabre2 pages

- Tessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics CorporationTessent ATPG Simulation Mismatch Debug: 2016 Mentor Graphics Corporation

- ATPG Simulation Mismatch - Common Problems and SolutionsATPG Simulation Mismatch - Common Problems and Solutions

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A Time

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseA Practical Clock Control Circuit Design & Example Tessent ATPG Test Case

- Why Masking Is Needed: Scan Chain Masking in The AcompactorWhy Masking Is Needed: Scan Chain Masking in The Acompactor

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingScan Insertion Lab Observations: Vlsiguru DFT Training

- DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System DesignDFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design

- Simulation Mismatches Can Foul Up Test-Pattern VerificationSimulation Mismatches Can Foul Up Test-Pattern Verification

- SAS Programming Guidelines Interview Questions You'll Most Likely Be AskedFrom EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be Asked

- Internet of Things (Iot) Cybersecurity: Literature Review and Iot Cyber Risk ManagementInternet of Things (Iot) Cybersecurity: Literature Review and Iot Cyber Risk Management

- SAP Development Strategy_BTP Partner Forum Bcn_20230316SAP Development Strategy_BTP Partner Forum Bcn_20230316

- Oracle 11g Business Intelligence Enterprise Edition (OBIEE)Oracle 11g Business Intelligence Enterprise Edition (OBIEE)

- XY-MBZ55A-YC1155-Bluetooth-5-BR-EDR-BLE-module-Datasheet-20211101XY-MBZ55A-YC1155-Bluetooth-5-BR-EDR-BLE-module-Datasheet-20211101

- FactoryTalk Historian SE Basic Lab (RAcbi) - 8-28-2018-IN05FactoryTalk Historian SE Basic Lab (RAcbi) - 8-28-2018-IN05

- Trainee Application Form (Technical Trainee) : Yes NoTrainee Application Form (Technical Trainee) : Yes No

- Aaron Nace - 10 Tips For Photoshop Beginners - Reference GuideAaron Nace - 10 Tips For Photoshop Beginners - Reference Guide

- Oral - Presentation - RT2018 - NCruz - RNC - Software - ArchitectureOral - Presentation - RT2018 - NCruz - RNC - Software - Architecture