24bit1 Adc

24bit1 Adc

Uploaded by

Kishore PagarCopyright:

Available Formats

24bit1 Adc

24bit1 Adc

Uploaded by

Kishore PagarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

24bit1 Adc

24bit1 Adc

Uploaded by

Kishore PagarCopyright:

Available Formats

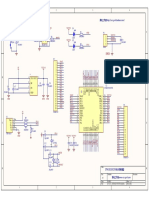

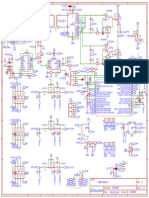

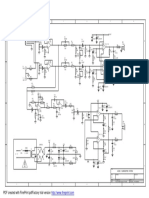

VCC VCC

VCC VCC RP2

CS 2 1 VCC CN3

R1 U1 RP1 CN1 SDI 3

1

560E CS 1 39 D0 2 1 GND SDO 4 P3.0

P10 P00 1 2

SDI 2 38 D1 3 VCC VR1 SCL 5 P3.1

D P11 P01 C3 2 3 D

SDO 3 37 D2 4 CONTR POT1 P3.2

P12 P02 .1UF 3 4

SCL 4 36 D3 5 LCD_RS VCC 10K P3.3

P13 P03 4 S1 5

P1.4 5 35 D4 6 LCD_WR P3.4

P14 P04 5 SW DIP-4 6

P1.5 6 34 D5 7 LCD_EN P3.5

LD1 P15 P05 6 7

P1.6 7 33 D6 8 D0 R3 10K SW1 1 8 P1.4

PWR P16 P06 7 8

P1.7 8 32 D7 9 D1 R4 10K SW2 2 7 P1.5

P17 P07 8 9

D2 R5 10K SW3 3 6 P1.6

9 10

P3.3 13 21 SW1 10K D3 R6 10K SW4 4 5 P1.7

INT1 P20 10 11

P3.2 12 22 SW2 D4

INT0 P21 11 12

23 SW3 D5

P22 12

P3.5 15 24 SW4 D6 IO-PORT

T1 P23 13

P3.4 14 25 SW5 D7

T0 P24 14

C1 26 LCD_EN

P25 15

VCC 31 27 LCD_WR

EA/VP P26 16

28 LCD_RS +5 C4

P27

33pF CR1 19 LCD

18

11.059MHz X1

5

18 U5

X2

74C922 100NJ

C2 RESET 9 10 P3.0

VCC

OSC

C RESET RXD C

11 P3.1 CN2

TXD

S-SDA 17 30 ROW Y1 1 17 SW1

RD ALE/P 1 ROW Y1 DOUT A

33pF S-SCL 16 29 VCC ROW Y3 ROW Y2 2 16 SW2

WR PSEN 2 ROW Y2 DOUT B

U2 COL X1 ROW Y3 3 15 SW3

3 ROW Y3 DOUT C

8051 1 8 COL X2 ROW Y4 4 14 SW4

A0 VCC 4 ROW Y4 DOUT D

2 7 10K R12VCC ROW Y1

A1 WP 5

TP1 3 6 S-SCL ROW Y2 COL X1 11 12 SW5

A2 SCL 6 COL X1 D- AVA

CON1 4 5 S-SDA COL X3 13

GND SDA 7 O/P EN

C5 10K R13 ROW Y4 COL X2 10

8 COL X2

1

U4 VCC 24C64

KB MASK

1 8 VCC KEYBOARD COL X3 8

X1 VCC R10 COL X3

33pF 2 7 VCCC11 7

CR2 X2 SQWOUT COL X4

3 6 S-SCL 10K

VBAT SCL

G

4 5 S-SDA TP4 TP3 +5

33KHz GND SDA

C6 0.1uF S-GND GND

DS1307

6

1

1

VCC C9 CN5 C18

33pF R11 GND 100NJ

4 C19

S-SCL

B BT1 3 1J/63V B

0.1uF S-SDA

3V 2

0E VCC

1

JP2

VCC JUMPER Analog Gnd Digital Gnd I2C-OP

1

2

+12 VCC

R7

U3 47K VCC

CN4 + C14 +

VCC 1 8 C12 C16 C17

VOUT VBAT R8 C10 1 10uF/16V 0.1uF 10uF/16V CAP

2 7

VCC RESET 10uF/25V 2

3 6 47K Q1

GND WDI 3

4 5 BC557

PF1 PF0 4

P3.2 +

MAX690 RESET POWER-IP C13 C15

VCC 10uF/16V 0.1uF

2

1

C7 R9 Title

A A

100nF/BOX JP1 10K -12

CON2 D1

C8 IN4148 Size Number Revision

0.1uF

A4

Date: 18-Mar-2011 Sheet of

File: E:\circuit diagram\OILBDV\24bitADC-VR02.DDB

Drawn By:

You might also like

- Arduino PWM Generator With Duty Cycle Display 1No ratings yetArduino PWM Generator With Duty Cycle Display 11 page

- Atmega328 Based Circuit Diagram of The Project100% (2)Atmega328 Based Circuit Diagram of The Project1 page

- 344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)100% (1)344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)1 page

- schematic_main---flight-computers_2023-06-08-YZ9nbVq3oJTo7q6BNo ratings yetschematic_main---flight-computers_2023-06-08-YZ9nbVq3oJTo7q6B1 page

- GND OUT INH IN +5V0 V - in +3V3: QuantumopticsNo ratings yetGND OUT INH IN +5V0 V - in +3V3: Quantumoptics1 page

- Password Based Circuit Breaker Microcontroller Power and Buzzer Section100% (1)Password Based Circuit Breaker Microcontroller Power and Buzzer Section1 page

- LTC2400 Arduino Voltmeter Module SchematicNo ratings yetLTC2400 Arduino Voltmeter Module Schematic1 page

- Basic - Duino - SCHEMATIC - V1.0.0 - 28-07-2019100% (1)Basic - Duino - SCHEMATIC - V1.0.0 - 28-07-20191 page

- PDF Created With Fineprint Pdffactory Trial Version: A-6332 Subwoofer SystemNo ratings yetPDF Created With Fineprint Pdffactory Trial Version: A-6332 Subwoofer System1 page

- PDF Created With Fineprint Pdffactory Trial Version: ZoudangNo ratings yetPDF Created With Fineprint Pdffactory Trial Version: Zoudang1 page

- (5 - Minutes - Talk) - Komatsu PC1250SP-8 vs. Volvo EC950 Comparison - ENNo ratings yet(5 - Minutes - Talk) - Komatsu PC1250SP-8 vs. Volvo EC950 Comparison - EN3 pages

- Hood River Detailed Sustainable Case StudyNo ratings yetHood River Detailed Sustainable Case Study12 pages

- DYNROT: A Matlab Toolbox For Rotordynamics Analysis: January 1994No ratings yetDYNROT: A Matlab Toolbox For Rotordynamics Analysis: January 199427 pages