STA380BW STMicroelectronics

STA380BW STMicroelectronics

Uploaded by

Rodrigo SousaCopyright:

Available Formats

STA380BW STMicroelectronics

STA380BW STMicroelectronics

Uploaded by

Rodrigo SousaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

STA380BW STMicroelectronics

STA380BW STMicroelectronics

Uploaded by

Rodrigo SousaCopyright:

Available Formats

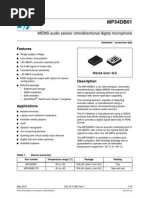

STA380BW

Sound Terminal®

2.1-channel high-efficiency digital audio system

Datasheet - production data

Up to 12 user-programmable biquads with

noise-shaping technology

Direct access to coefficients through I2C

shadowing mechanism

Fixed (88.2 kHz / 96 kHz) internal processing

VQFN48 (7 x 7 mm) sampling rate

Two independent DRCs configurable as a

dual-band anticlipper or independent

Features limiters/compressors (B2DRC)

Digital gain/att +48 dB to -80 dB with

Wide-range supply voltage 0.125 dB/step resolution

– 4.5 V to 26 V (operating range)

Independent (fade-in, fade-out) soft volume

– 30 V (absolute maximum rating) update with programmable rate 48 ~ 1.5 dB/ms

I2C control with selectable device address Bass/treble tones control

Embedded full IC protection Audio presets: 15 crossover filters,

– Manufacturing short-circuit protection (out 5 anticlipping modes, nighttime listening mode

vs. gnd, out vs. vcc, out vs. out)

STSpeakerSafeTM protection circuitry

– Thermal protection

– Pre- and post-processing DC blocking

– Overcurrent protection filters

– Undervoltage protection – Checksum engine for filter coefficients

I2S interface, sampling rate 32 kHz ~ 192 kHz, – PWM fault self-diagnosis

with internal sampling frequency converter for

STCompressorTM dual-band DRC

fixed processing frequency

Three output power stage configurations Table 1. Device summary

– 2.0 mode, L/R full bridges

Order code Package Packing

– 2.1 mode, L/R two half-bridges, subwoofer

full bridge STA380BW VQFN48 Tray

– 2.1 mode, L/R full bridges, PWM output for STA380BWTR VQFN48 Tape and Reel

external subwoofer amplifier

Driving load capabilities

– 2 x 20 W into 8 ternary modulation

– 2 x 9 W into 4 + 1 x 20 W into 8

FFXTM 100 dB dynamic range

Fixed output PWM frequency at any input

sampling frequency

Embedded RMS meter for measuring real-time

loudness

New fully programmable noise-gating function

April 2013 DocID024543 Rev 1 1/162

This is information on a product in full production. www.st.com 162

Contents STA380BW

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2 Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.1 Connection diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.4 Electrical specifications - digital section . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.5 Electrical specifications - power section . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.6 Power on/off sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4 Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.1 Processing data path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.2 Input oversampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.3 STCompressorTM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.3.1 STC block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.2 Band splitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.3 Level meter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.3.4 Mapper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.3.5 Attenuator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.3.6 Dynamic attack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.3.7 Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.3.8 Stereo link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.3.9 Programming of coefficients . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.3.10 Memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5 I2C bus specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1 Communication protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1.1 Data transition or change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2/162 DocID024543 Rev 1

STA380BW Contents

5.1.2 Start condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1.3 Stop condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1.4 Data input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.2 Device addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.3 Write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.3.1 Byte write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.3.2 Multi-byte write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4 Read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4.1 Current address byte read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4.2 Current address multi-byte read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4.3 Random address byte read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4.4 Random address multi-byte read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.4.5 Write mode sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.4.6 Read mode sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6 Register description: New Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.1 CLK register (addr 0x00) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6.2 STATUS register (addr 0x01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6.3 RESET register (addr 0x02) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.4 Soft volume register (addr 0x03) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.5 MVOL register (addr 0x04) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.6 FINEVOL register (addr 0x05) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.7 CH1VOL register (addr 0x06) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.8 CH2VOL register (addr 0x07) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.9 POST scaler register (addr 0x08) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.10 OPER register (addr 0x09) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.11 FUNCT register (addr 0x0A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.11.1 Dual-band DRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.12 Configuration register A (addr 0x11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.12.1 Master clock select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.12.2 Interpolation ratio selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.12.3 Fault-detect recovery bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.13 Configuration register B (addr 0x12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

6.13.1 Serial data interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

6.13.2 Serial data first bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

DocID024543 Rev 1 3/162

Contents STA380BW

6.13.3 Delay serial clock enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.13.4 Channel input mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.14 Configuration register C (addr 0x13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.14.1 FFX compensating pulse size register . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.15 Configuration register D (addr 0x14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.15.1 DSP bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.15.2 Post-scale link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.15.3 Biquad coefficient link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.15.4 Zero-detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.15.5 Submix mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.16 Configuration register E (addr 0x15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.16.1 Noise-shaper bandwidth selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.16.2 AM mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.16.3 PWM speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.16.4 Zero-crossing enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.17 Configuration register F (addr 0x16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.17.1 Invalid input detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.17.2 Binary output mode clock loss detection . . . . . . . . . . . . . . . . . . . . . . . . 64

6.17.3 LRCK double trigger protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.17.4 Power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.17.5 External amplifier power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.18 Volume control registers (addr 0x17 - 0x1B) . . . . . . . . . . . . . . . . . . . . . . 66

6.18.1 Mute/line output configuration register (addr 0x17) . . . . . . . . . . . . . . . . 66

6.18.2 Channel 3 / line output volume (addr 0x1B) . . . . . . . . . . . . . . . . . . . . . 67

6.19 Audio preset registers (0x1D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.19.1 AM interference frequency switching . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.19.2 Bass management crossover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.20 Channel configuration registers (addr 0x1F - 0x21) . . . . . . . . . . . . . . . . . 69

6.20.1 Tone control bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.20.2 EQ bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.20.3 Volume bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.20.4 Binary output enable registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.20.5 Limiter select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.20.6 Output mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.21 Tone control register (addr 0x22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.21.1 Tone control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4/162 DocID024543 Rev 1

STA380BW Contents

6.22 Dynamic control registers (addr 0x23 - 0x26 / addr 0x43 - 0x46) . . . . . . 72

6.22.1 Limiter 1 attack/release rate (L1AR addr 0x23) . . . . . . . . . . . . . . . . . . . 72

6.22.2 Limiter 1 attack/release threshold (L1ATRT addr 0x24) . . . . . . . . . . . . 72

6.22.3 Limiter 2 attack/release rate ( L2AR addr 0x25) . . . . . . . . . . . . . . . . . . 72

6.22.4 Limiter 2 attack/release threshold ( L2 ATRT addr 0x26) . . . . . . . . . . . . 72

6.22.5 Limiter 1 extended attack threshold (addr 0x43) . . . . . . . . . . . . . . . . . . 76

6.22.6 Limiter 1 extended release threshold (addr 0x44) . . . . . . . . . . . . . . . . . 76

6.22.7 Limiter 2 extended attack threshold (addr 0x45) . . . . . . . . . . . . . . . . . . 77

6.22.8 Limiter 2 extended release threshold (addr 0x46) . . . . . . . . . . . . . . . . . 77

6.23 User-defined coefficient control registers (addr 0x27 - 0x37) . . . . . . . . . . 77

6.23.1 Coefficient address register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.23.2 Coefficient b1 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.23.3 Coefficient b1 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.23.4 Coefficient b1 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.23.5 Coefficient b2 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.6 Coefficient b2 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.7 Coefficient b2 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.8 Coefficient a1 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.9 Coefficient a1 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.10 Coefficient a1 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.11 Coefficient a2 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.23.12 Coefficient a2 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.13 Coefficient a2 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.14 Coefficient b0 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.15 Coefficient b0 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.16 Coefficient b0 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.17 Coefficient write/read control register . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.23.18 User-defined EQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.23.19 Pre-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.23.20 Post-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.24 Fault-detect recovery constant registers (addr 0x3C - 0x3D) . . . . . . . . . . 84

6.25 Extended configuration register (addr 0x47) . . . . . . . . . . . . . . . . . . . . . . 84

6.25.1 Extended post-scale range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6.25.2 Extended attack rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6.25.3 Extended biquad selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

6.26 PLL configuration registers (address 0x52; 0x53; 0x54; 0x55;

0x56; 0x57) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

DocID024543 Rev 1 5/162

Contents STA380BW

6.27 Short-circuit protection mode registers SHOK (address 0x58) . . . . . . . . 88

6.28 Extended coefficient range up to -4...4 (address 0x5A) . . . . . . . . . . . . . . 89

6.29 Miscellaneous registers (address 0x5C, 0x5D) . . . . . . . . . . . . . . . . . . . . 90

6.29.1 Rate power-down enable (RPDNEN) bit . . . . . . . . . . . . . . . . . . . . . . . . 90

6.29.2 Bridge immediately off (BRIDGOFF) bit (address 0x4B, bit D5) . . . . . . 90

6.29.3 Channel PWM enable (CPWMEN) bit . . . . . . . . . . . . . . . . . . . . . . . . . . 91

6.29.4 External amplifier hardware pin enabler (LPDP, LPD LPDE) bits . . . . . 91

6.29.5 Power-down delay selector (PNDLSL[2:0]) bits . . . . . . . . . . . . . . . . . . . 91

6.29.6 Short-circuit check enable bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

6.30 Bad PWM detection registers (address 0x5E, 0x5F, 0x60) . . . . . . . . . . . 92

6.31 Enhanced zero-detect mute and input level measurement

(address 0x61-0x65, 0x3F, 0x40, 0x6F) . . . . . . . . . . . . . . . . . . . . . . . . . . 93

6.32 STCompressorTM configuration register (address 0x6B; 0x6C) . . . . . . . . 95

6.33 Coefficient RAM CRC protection (address 0x71-0x7D) . . . . . . . . . . . . . . 96

6.34 MISC4 (address 0x7E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7 Register description: Sound Terminal compatibility . . . . . . . . . . . . . 100

7.1 Configuration register A (addr 0x00) . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.1.1 Master clock select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.1.2 Interpolation ratio select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.1.3 Fault-detect recovery bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.2 Configuration register B (addr 0x01) . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.2.1 Serial data interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.2.2 Serial audio input interface format . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.2.3 Serial data first bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.2.4 Delay serial clock enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.2.5 Channel input mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.3 Configuration register C (addr 0x02) . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.3.1 FFX compensating pulse size register . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.4 Configuration register D (addr 0x03) . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.4.1 DSP bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.4.2 Post-scale link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.3 Biquad coefficient link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.4 Zero-detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.5 Submix mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7.5 Configuration register E (addr 0x04) . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

6/162 DocID024543 Rev 1

STA380BW Contents

7.5.1 Noise-shaper bandwidth selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.5.2 AM mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.5.3 PWM speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.5.4 Zero-crossing enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.5.5 Soft volume update enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.6 Configuration register F (addr 0x05) . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.1 Output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.2 Invalid input detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.6.3 Binary output mode clock loss detection . . . . . . . . . . . . . . . . . . . . . . . 118

7.6.4 LRCK double trigger protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.6.5 IC power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.6.6 External amplifier power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.7 Volume control registers (addr 0x06 - 0x0A) . . . . . . . . . . . . . . . . . . . . . 119

7.7.1 Mute/line output configuration register . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.7.2 Master volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.7.3 Channel 1 volume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.7.4 Channel 2 volume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.7.5 Channel 3 / line output volume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.8 Audio preset registers (addr 0x0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.8.1 Audio preset register (addr 0x0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.8.2 AM interference frequency switching . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.8.3 Bass management crossover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.9 Channel configuration registers (addr 0x0E - 0x10) . . . . . . . . . . . . . . . . 123

7.9.1 Tone control bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

7.9.2 EQ bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7.9.3 Volume bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7.9.4 Binary output enable registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7.9.5 Limiter select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

7.9.6 Output mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

7.10 Tone control register (addr 0x11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

7.10.1 Tone control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

7.11 Dynamic control registers (addr 0x12 - 0x15) . . . . . . . . . . . . . . . . . . . . 126

7.11.1 Limiter 1 attack/release rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7.11.2 Limiter 1 attack/release threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7.11.3 Limiter 2 attack/release rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7.11.4 Limiter 2 attack/release threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

DocID024543 Rev 1 7/162

Contents STA380BW

7.11.5 Limiter 1 extended attack threshold (addr 0x32) . . . . . . . . . . . . . . . . . 130

7.11.6 Limiter 1 extended release threshold (addr 0x33) . . . . . . . . . . . . . . . . 130

7.11.7 Limiter 2 extended attack threshold (addr 0x34 . . . . . . . . . . . . . . . . . ) 131

7.11.8 Limiter 2 extended release threshold (addr 0x35) . . . . . . . . . . . . . . . . 131

7.12 User-defined coefficient control registers (addr 0x16 - 0x26) . . . . . . . . . 131

7.12.1 Coefficient address register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.12.2 Coefficient b1 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.12.3 Coefficient b1 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.12.4 Coefficient b1 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.5 Coefficient b2 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.6 Coefficient b2 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.7 Coefficient b2 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.8 Coefficient a1 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.9 Coefficient a1 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.10 Coefficient a1 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.11 Coefficient a2 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.12.12 Coefficient a2 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.13 Coefficient a2 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.14 Coefficient b0 data register bits 23:16 . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.15 Coefficient b0 data register bits 15:8 . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.16 Coefficient b0 data register bits 7:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.17 Coefficient write/read control register . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.12.18 User-defined EQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.12.19 Pre-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.12.20 Post-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.13 Fault-detect recovery constant registers (addr 0x2B - 0x2C) . . . . . . . . . 138

7.14 Device status register (addr 0x2D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.15 EQ coefficients configuration register (addr 0x31) . . . . . . . . . . . . . . . . . 138

7.16 Extended configuration register (addr 0x36) . . . . . . . . . . . . . . . . . . . . . 139

7.16.1 Dual-band DRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.16.2 Extended post-scale range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.16.3 Extended attack rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.16.4 Extended BIQUAD selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.17 EQ soft volume configuration registers (addr 0x37 - 0x38) . . . . . . . . . . 142

7.18 Extra volume resolution configuration registers (address 0x3F; 0x40) . 143

8/162 DocID024543 Rev 1

STA380BW Contents

7.19 PLL configuration registers (address 0x41; 0x42; 0x43;

0x44; 0x45; 0X46) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

7.20 Short-circuit protection mode registers SHOK (address 0x47) . . . . . . . 146

7.21 Extended coefficient range up to -4...4 (address 0x49, 0x4A) . . . . . . . . 148

7.22 Miscellaneous registers (address 0x4B, 0x4C) . . . . . . . . . . . . . . . . . . . 148

7.22.1 Rate power-down enable (RPDNEN) bit (address 0x4B, bit D7) . . . . . 148

7.22.2 Bridge immediately off (BRIDGOFF) bit (address 0x4B, bit D5) . . . . . 149

7.22.3 Channel PWM enable (CPWMEN) bit (address 0x4B, bit D2) . . . . . . . 149

7.22.4 External amplifier hardware pin enabler (LPDP, LPD LPDE) bits

(address 0x4C, bit D7, D6, D5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.22.5 Power-down delay selector (PNDLSL[2:0]) bits

(address 0x4C, bit D4, D3, D2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

7.22.6 Short-circuit check enable bit (address 0x4C, bit D0) . . . . . . . . . . . . . 150

7.23 Bad PWM detection registers (address 0x4D, 0x4E, 0x4F) . . . . . . . . . . 151

7.24 Enhanced zero-detect mute and input level measurement

(address 0x50-0x54, 0x2E, 0x2F and 0x5E) . . . . . . . . . . . . . . . . . . . . . 152

7.25 STCompressorTM configuration register (address 0x5A; 0x5B) . . . . . . . 154

7.26 Coefficient RAM CRC protection (address 0x60-0x6C) . . . . . . . . . . . . . 155

7.27 MISC3 (address 0x6E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

7.28 MISC4 (address 0x7E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

8 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

8.1 Typical output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

9 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

DocID024543 Rev 1 9/162

List of tables STA380BW

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 4. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 5. Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 6. Electrical specifications - digital section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 7. Electrical specifications - power section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 8. Coefficients extended-range configuration 0x74h. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 9. Compressor ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 10. Conversion example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 11. STC coefficients memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 12. STC band splitter filters memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 13. Default register map table: NEW MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 14. CLK register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 15. STATUS register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 16. RESET register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 17. Soft volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 18. Master volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 19. Fine volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 20. Channel 1 volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 22. Channel 2 volume register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 23. OPER register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 24. OPER configuration selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 25. FUNCT register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 26. Master clock select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 27. Input sampling rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 28. Internal interpolation ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 29. IR bit settings as a function of the input sampling rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 30. Fault-detect recovery bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 31. Serial data first bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 32. Support serial audio input formats for MSB-first (SAIFB = 0) . . . . . . . . . . . . . . . . . . . . . . . 59

Table 33. Supported serial audio input formats for LSB-first (SAIFB = 1) . . . . . . . . . . . . . . . . . . . . . 60

Table 34. Delay serial clock enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 35. Channel input mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 36. FFX compensating pulse size bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 37. Compensating pulse size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 38. DSP bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 39. Post-scale link. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 40. Biquad coefficient link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 41. Zero-detect mute enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 42. Submix mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 43. Noise-shaper bandwidth selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 44. AM mode enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 45. PWM speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 46. Zero-crossing enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 47. Invalid input detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 48. Binary output mode clock loss detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 49. LRCK double trigger protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10/162 DocID024543 Rev 1

STA380BW List of tables

Table 50. IC power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 51. External amplifier power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 52. Line output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 53. Mute configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 54. Channel 3 volume as a function of CH3VOL[7:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 55. AM interference frequency switching bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 56. Audio preset AM switching frequency selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 57. Bass management crossover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 58. Bass management crossover frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 59. Tone control bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 60. EQ bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 61. Volume bypass register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 62. Binary output enable registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 63. Channel limiter mapping as a function of C3LS bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 64. Channel output mapping as a function of C3OM bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 65. Tone control boost/cut as a function of BTC and TTC bits . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 66. Limiter attack rate as a function of LxA bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 67. Limiter release rate as a function of LxR bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 68. Limiter attack threshold as a function of LxAT bits (AC mode) . . . . . . . . . . . . . . . . . . . . . . 75

Table 69. Limiter release threshold as a function of LxRT bits (AC mode). . . . . . . . . . . . . . . . . . . . . 75

Table 70. Limiter attack threshold as a function of LxAT bits (DRC mode) . . . . . . . . . . . . . . . . . . . . 76

Table 71. Limiter release threshold as a function of LxRT bits (DRC mode) . . . . . . . . . . . . . . . . . . . 76

Table 72. RAM block for biquads, mixing, scaling and bass management. . . . . . . . . . . . . . . . . . . . . 83

Table 73. Extended post-scale range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 74. Extended attack rate, limiter 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 75. Extended attack rate, limiter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 76. Extended biquad selector, biquad 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 77. Extended biquad selector, biquad 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 78. Extended biquad selector, biquad 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 79. PLL factors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 80. PLL register 0x54 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 81. PLL register 0x55 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 82. PLL register 0x56 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 83. PLL register 0x57 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 84. Coefficients extended range configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 85. External amplifier enabler configuration bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 86. PNDLSL bits configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 87. Zero-detect threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 89. Manual threshold register 0x3F, 0x40 and 0x6F. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 88. Zero-detect hysteresis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 90. Register STCCFG0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 91. STCCFG0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 92. Register STCCFG1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 93. STCCFG1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 94. Misc register 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 95. I2C registers summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 96. Master clock select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 97. Input sampling rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 98. Internal interpolation ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 99. IR bit settings as a function of the input sampling rate . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 100. Fault-detect recovery bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 101. Serial audio input interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

DocID024543 Rev 1 11/162

List of tables STA380BW

Table 102. Serial data first bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 103. Support serial audio input formats for MSB-first (SAIFB = 0) . . . . . . . . . . . . . . . . . . . . . . 106

Table 104. Supported serial audio input formats for LSB-first (SAIFB = 1) . . . . . . . . . . . . . . . . . . . . 107

Table 105. Delay serial clock enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 106. Channel input mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 107. FFX compensating pulse size bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 108. Compensating pulse size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 109. DSP bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 110. Post-scale link. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 111. Biquad coefficient link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 112. Zero-detect mute enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 113. Submix mode enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 114. Noise-shaper bandwidth selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 115. AM mode enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 116. PWM speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 117. Zero-crossing enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 118. Soft volume update enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 119. Output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 120. Output configuration engine selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 121. Invalid input detect mute enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 122. Binary output mode clock loss detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 123. LRCK double trigger protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 124. IC power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 125. External amplifier power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 126. Line output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 127. Mute configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 128. Master volume offset as a function of MVOL[7:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 129. Channel volume as a function of CxVOL[7:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 130. AM interference frequency switching bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 131. Audio preset AM switching frequency selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 132. Bass management crossover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 133. Bass management crossover frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 134. Tone control bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 135. EQ bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 136. Volume bypass register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 137. Binary output enable registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 138. Channel limiter mapping as a function of CxLS bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 139. Channel output mapping as a function of CxOM bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 140. Tone control boost/cut as a function of BTC and TTC bits . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 141. Limiter attack rate as a function of LxA bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 142. Limiter release rate as a function of LxR bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 143. Limiter attack threshold as a function of LxAT bits (AC mode) . . . . . . . . . . . . . . . . . . . . . 129

Table 144. Limiter release threshold as a function of LxRT bits (AC mode). . . . . . . . . . . . . . . . . . . . 129

Table 145. Limiter attack threshold as a function of LxAT bits (DRC mode) . . . . . . . . . . . . . . . . . . . 130

Table 146. Limiter release threshold as a function of LxRT bits (DRC mode) . . . . . . . . . . . . . . . . . . 130

Table 147. RAM block for biquads, mixing, scaling and bass management. . . . . . . . . . . . . . . . . . . . 137

Table 148. Status register bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 149. Extended post-scale range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 150. Extended attack rate, limiter 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 151. Extended attack rate, limiter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 152. Extended biquad selector, biquad 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 153. Extended biquad selector, biquad 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

12/162 DocID024543 Rev 1

STA380BW List of tables

Table 154. Extended biquad selector, biquad 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 155. Soft volume update enable, increase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 156. Soft volume update enable, decrease . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 157. Volume fine-tuning steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 158. Extra volume resolution enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 159. PLL factors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 160. PLL register 0x43 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 161. PLL register 0x44 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 162. PLL register 0x45 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 163. PLL register 0x46 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 164. Coefficients extended range configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 165. External amplifier enabler configuration bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 166. PNDLSL bits configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 167. Zero-detect threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 169. Manual threshold register 0x2E, 0x2F and 0x5E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 168. Zero-detect hysteresis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 170. STCompressorTM configuration bits1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 171. STCompressorTM configuration bits 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 172. Misc register 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 173. MISC4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 174. VQFN48 (7 x 7 x 0.9 mm) package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 175. Document revision history. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

DocID024543 Rev 1 13/162

List of figures STA380BW

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 2. Pin connections VQFN48 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 3. Test circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 4. Power-on sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 5. Power-off sequence for pop-free turn-off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 6. Processing path, first part . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 7. Processing path, second part: 2.1 output with individually configurable anticlipper/DRCs. 26

Figure 8. Processing path, second part: 2.0 output with B2DRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 9. Processing path, second part: 2.1 output configuration with STCompressorTM . . . . . . . . . 27

Figure 10. STCompressorTM block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 11. Band splitter with 4th order filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 12. STCompressorTM behavior. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 13. STCompressorTM behavior as a limiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 14. Offset effect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 15. Stereo link block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 16. Write mode sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 17. Read mode sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 18. OPER = 00 (default value) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 19. OPER = 11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 20. OPER = 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 21. OPER = 01 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 22. Output mapping scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 23. 2.0 channels (OPER = 00) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 24. 2.1 channels (OPER = 11) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 25. 2.1 channels (OPER = 10) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 26. B2DRC scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 27. Basic limiter and volume flow diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 28. Short-circuit detection timing diagram (no short detected) . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 29. Alternate function for INTLINE pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 30. Coefficients direct access single-write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 31. Coefficients direct access multiple-write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 32. Coefficients direct access single-read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 33. OCFG = 00 (default value) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 34. OCFG = 01 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 35. OCFG = 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 36. OCFG = 11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Figure 37. Output mapping scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Figure 38. 2.0 channels (OCFG = 00) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 39. 2.1 channels (OCFG = 01) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 40. 2.1 channels (OCFG = 10) PWM slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 41. Basic limiter and volume flow diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 42. B2DRC scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Figure 43. Extra resolution volume scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Figure 44. Short-circuit detection timing diagram (no short detected) . . . . . . . . . . . . . . . . . . . . . . . . 147

Figure 45. Alternate function for INTLINE pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 46. Output configuration for stereo BTL mode in filterlight configuration . . . . . . . . . . . . . . . . 158

Figure 47. VQFN48 (7 x 7 x 0.9 mm) package outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

14/162 DocID024543 Rev 1

STA380BW Description

1 Description

The STA380BW is an integrated solution embedding digital audio processing, digital

amplification and FFXTM power output stage. It is part of the Sound Terminal® family and

provides full digital audio streaming from the source to the speaker, offering cost

effectiveness, low power dissipation and sound enrichment.

The STA380BW input section consists of a flexible digital input serial audio interface feeding

the digital processing unit. The serial audio data input interface supports many formats,

including the popular IIS format.

The STA380BW is based on an FFXTM (Fully Flexible Amplification) processor, proprietary

technology from STMicroelectronics. FFXTM is the evolution of the ST ternary technology:

the advanced processor is available for ternary, binary, binary differential and phase shift

PWM modulation. The STA380BW embeds the ternary, binary and binary differential

implementations, a subset of the full capability of the FFXTM processor.

The STA380BW power section consists of four independent half-bridges. These can be

configured via digital control to operate in different modes. A 2.1-channel setup can be

implemented with two half-bridges (L/R) together with a single full-bridge (subwoofer).

Alternatively, the 2.0-channel setup can be done with two full-bridges. When using this

configuration, an external amplifier for the SW channel can also be driven through the PWM

output. The STA380BW is able to deliver 2 x 20 W (ternary) into an 8 load at 18 V or

2 x 9 W (binary) into a 4 load, plus 1 x 20 W (ternary) into an 8 load at 18 V.

The STA380BW digital processing unit includes up to 12 programmable biquads (EQs),

allowing perfect sound equalization and offering advanced noise-shaping techniques.

Moreover, the coefficient range ensures a great variety of filter shapes (low/high-pass,

low/high shelf, peak, notch, band-pass). The equalization engine is fully compatible with the

ST speaker compensation technology embedded into the APWorkbench suite. A state-of-

the-art multi-band DRC, STCompressorTM equalizes the system to provide active speaker

protection with full audio quality preservation against sudden sound peaks. Moreover,

STSpeakerSafeTM technology offers reliable speaker protection under any condition. The

master clock can be from stable BICKI (64xfs, 50% duty cycle) or external XTI.

DocID024543 Rev 1 15/162

Description STA380BW

1.1 Block diagram

Figure 1. Block diagram

STA380BW

16/162 DocID024543 Rev 1

STA380BW Pin connections

2 Pin connections

2.1 Connection diagram

Figure 2. Pin connections VQFN48 (top view)

TEST MODE

GND_DIG2

VDD_DIG2

INT_LINE

PWRDN

RESET

LRCKI

BICKI

SDA

SCL

SDI

SA

48

47

46

45

44

43

42

41

40

39

38

37

VCC_REG 1 36 MCLK

VSS_REG 2 35 AGND_PLL

OUT2B 3 34 VREG_FILT

GND2 4 33 TWARN/FFX4A

VCC2 5 32 EAPD/FFX4B

OUT2A 6 31 FFX3B

OUT1B 7

STA380BW 30 FFX3A

VCC1 8 29 GND_DIG1

GND1 9 28 VDD_DIG1

OUT1A 10 27 GND

VDD_REG 11 26 N.C.

GND_REG 12 25 GND

13

14

15

16

17

18

19

20

21

22

23

24

GND

GND

GND

GND

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

DocID024543 Rev 1 17/162

Pin connections STA380BW

2.2 Pin description

Table 2. Pin list

VQFN 48-pin Name Type Description

1 VCC_REG POWER VCC reg

2 VSS_REG POWER Vss reg, VCC_REG-3.3 V

3 OUT2B OUTPUT Half-bridge 2B output

4 GND2 POWER Half-bridge 2A and 2B ground

5 VCC2 POWER Half-bridge 2A and 2B supply

6 OUT2A OUTPUT Half-bridge 2A output

7 OUT1B OUTPUT Half-bridge 1B output

8 VCC1 POWER Half-bridge 1A and 1B supply

9 GND1 POWER Half-bridge 1A and 1B ground

10 OUT1A OUTPUT Half-bridge 1A output

11 VDD_REG POWER VDD reg 3.3 V

12 GND_REG POWER DC reg ground

13, 14, 15, 18, 19,

N.C. Not connected

23, 24, 26

28 VDDDIG1 POWER I/O ring power supply

29 GNDDIG1 POWER Digital core ground

30 FFX3A OUTPUT Digital PWM line out

31 FFX3B OUTPUT Digital PWM line out

32 EAPD/FFX4B OUTPUT Digital PWM line out

33 TWARN/FFX4A OUTPUT Digital PWM line out

34 VREGFILT POWER Digital VDD from core

35 AGNDPLL POWER PLL analog ground

36 MCLK INPUT PLL input clock

37 BICKI INPUT IIS serial clock

38 LRCKI INPUT IIS left/right clock

39 SDI INPUT IIS serial data input

40 RESET INPUT Reset

Device power-down

41 PWRDN INPUT 0 = power-down

1 = normal operation

42 INTLINE OUTPUT Fault interrupt

43 SDA I/O IIC serial data

44 SCL INPUT IIC serial clock

45 SA INPUT IIC select address (pull-down)

18/162 DocID024543 Rev 1

STA380BW Pin connections

Table 2. Pin list (continued)

VQFN 48-pin Name Type Description

46 TEST_MODE INPUT This pin must be connected to ground (pull-down)

47 GNDDIG2 POWER Digital I/O ground

48 VDDDIG2 POWER Digital core LDO supply

16, 17, 20, 22, 25, 27 GND POWER Ground

Note: To improve thermal dissipation, all the N.C. (no internal connection) pins must be connected

to GND.

DocID024543 Rev 1 19/162

Electrical specifications STA380BW

3 Electrical specifications

3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Min Typ Max Unit

Vcc Power supply voltage (VCCxA, VCCxB) -0.3 31.5 V

VDD_DIG Digital supply voltage -0.3 4 V

Top Operating junction temperature 0 150 °C

Tstg Storage temperature -40 150 °C

Warning: Stresses beyond those listed in Table 3 above may cause

permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any

other conditions beyond those indicated under

“Recommended operating conditions” are not implied.

Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability. In the real

application, power supplies with nominal values rated within

the recommended operating conditions may rise beyond the

maximum operating conditions for a short time when no or

very low current is sunk (amplifier in mute state). In this case

the reliability of the device is guaranteed, provided that the

absolute maximum ratings are not exceeded.

3.2 Thermal data

Table 4. Thermal data

Symbol Parameter Min Typ Max Unit

Rth j-case Thermal resistance junction-case (thermal pad) 1.5 °C/W

Tth-sdj Thermal shutdown junction temperature 150 °C

Tth-w Thermal warning temperature 130 °C

Tth-sdh Thermal shutdown hysteresis 20 °C

20/162 DocID024543 Rev 1

STA380BW Electrical specifications

3.3 Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Min Typ Max Unit

Vcc Power supply voltage (VCCxA, VCCxB) 4.5 26 V

VDD_DIG Digital supply voltage 2.7 3.3 3.6 V

Tamb Ambient temperature 0 70 °C

3.4 Electrical specifications - digital section

The specifications given in this section are valid for the operating conditions:

VDD_DIG = 3.3 V, Tamb = 25 °C.

Table 6. Electrical specifications - digital section

Symbol Parameter Conditions Min Typ Max Unit

Low level input current

Iil Vi = 0 V 0.5 μA

without pull-up/down device

High level input current Vi = VDD_DIG

Iih 0.1 μA

without pull-up/down device = 3.3 V

Vil Low level input voltage 0.8 V

Vih High level input voltage 2.0 V

Vol Low level output voltage Iol = 2 mA 0.15 V

VDD_DIG

Voh High level output voltage Ioh = 2 mA V

-0.15

Rpu Pull-up/down resistance 50 k

DocID024543 Rev 1 21/162

Electrical specifications STA380BW

3.5 Electrical specifications - power section

The specifications given in this section are valid for the operating conditions: VCC = 24 V,

f = 1 kHz, fsw = 384 kHz, Tamb = 25° C and RL = 8 , unless otherwise specified.

Table 7. Electrical specifications - power section

Symbol Parameter Conditions Min Typ Max Unit

Output power BTL Digital limited(1) 20

(1)

Po Output power SE Digital limited 5 W

Output power SE RL = 4 Digital limited(1) 9

RdsON Power Pchannel/Nchannel MOSFET ld = 1.5 A 120 m

gP Power Pchannel RdsON matching ld = 1.5 A 95 %

gN Power Nchannel RdsON matching ld = 1.5 A 95 %

Idss Power Pchannel/Nchannel leakage 10 μA

ILDT Low current dead time (static) Resistive load(2) 8 15 ns

(2)

tr Rise time Resistive load 10 18 ns

tf Fall time Resistive load(2) 10 18 ns

Supply current from Vcc in power-down PWRDN = 0 0.1 1 μA

PCM Input signal = -60 dBfs,

Ivcc

Supply current from Vcc in operation Switching frequency = 384 kHz, 52 60 mA

No LC filters

Ilim Overcurrent limit 4 5 6.5 A

UVL Undervoltage protection 3.5 4.3 V

VOV Overvoltage protection 28.5 V

tmin Output minimum pulse width No load 20 30 60 ns

DR Dynamic range 100 dB

Signal-to-noise ratio, ternary mode A-weighted 100 dB

SNR

Signal-to-noise ratio, binary mode A-weighted 90 dB

FFX stereo mode, Po = 1 W,

THD+N Total harmonic distortion + noise 0.2 %

f = 1 kHz

FFX stereo mode,

<5 kHz, one channel driven at

XTALK Crosstalk 80 dB

1 W and other channel

measured

Peak efficiency, FFX mode Po = 2 x 20 W into 8 90 %

1. The related THD can be defined through appropriate DRC settings (see section: 4.3: STCompressorTM)

2. Refer to Figure 3: Test circuit.

22/162 DocID024543 Rev 1

STA380BW Electrical specifications

Figure 3. Test circuit

DocID024543 Rev 1 23/162

Electrical specifications STA380BW

3.6 Power on/off sequence

Figure 4. Power-on sequence

Note: no specific VCC and

VDD_DIG turn−on sequence

is required

VCC

Don’t care

VDD_DIG

XTI or BICKI Don’t care

HW RESET TR TC

I2C Don’t care CMD0 CMD1 CMD2

HW PWDN

TR = minimum time between XTI master clock stable and Reset removal: 1 ms

TC = minimum time between Reset removal and I2C program, sequence start: 1ms

Note: The definition of a stable clock is when fmax - fmin < 1 MHz.

Section 6.13.1: Serial data interface gives information on setting up the I2S interface.

Figure 5. Power-off sequence for pop-free turn-off

Note: no specific VCC and

VDD_DIG turn−off sequence

is required

VCC

Don’t care

VDD_DIG

XTI or BICKI Don’t care

Soft Mute

Reg. 0x07 Don’t care FE Don’t care

Data 0xFE

Soft EAPD

Reg. 0x05

Bit 7 = 0

Note: The register addresses for Soft Mute and Soft EAPD refer to Sound Terminal compatibility

(see Section 7: Register description: Sound Terminal compatibility on page 100) and are not

the default addresses.

24/162 DocID024543 Rev 1

STA380BW Device overview

4 Device overview

The mentioned hyperlink in this section relates to the default New Map Section 6: Register

description: New Map.

4.1 Processing data path

The whole STA380BW processing chain is composed of two consecutive sections. In the

first one dual-channel processing is implemented (Figure 6) and then each channel is fed

into the post-mixing block allowing to generate either a third channel (typically used in 2.1

output configurations together with crossover filters) or to have the channels processed by

the dual-band DRC block (2.0 output configuration with crossover filters used to define the

cutoff frequency of the two bands).

The first section begins with a 2x oversampling FIR filter allowing 2*Fs audio processing.

Then a selectable high-pass filter removes the DC level (enabled if HFB = 0). The channel 1

and 2 processing chain can include up to 8 filters, depending on the selected configuration

(bits BQL, BQ5, BQ6, BQ7 and XO[3:0]). By default, 4 independent filters per channel are

enabled, plus the pre-configured Bass and Treble controls (BQL=0, BQ5=0, BQ6=0,

BQ7=0).

The STA380BW offers the possibility to share the filter coefficients between the two

processing channels. When this option is set (BQL=1), filters from the 1st to the 4th have

the same coeffcients set. Under these conditions, filters from the 5th to 7th can be used as

custom filters as well (provided the relevant BQx bits are set). Once again filter coefficients

are shared between the two processing channels.

Moreover the common 8th filter, from the subsequent processing section, can be available

on both channels (provided the pre-defined crossover frequencies are not used, XO[3:0]=0,

and the dual-band DRC is not used).

Figure 6. Processing path, first part

Sampling Frequency = 2xFs

X2Over- De-emph Bass Treble

Pre- Hi-Pass Biquad Biquad Biquad Biquad

-sampling

FIR

-scale Filter #1 #2 #3 #4

Or

Biquad #5

Or

Biquad #6

Or

Biquad #7

L

Userd Defined Filters Tone Control

I2S Input

Interface Sampling Frequency = Fs

X2Over- De-emph Bass Treble

Pre- Hi-Pass Biquad Biquad Biquad Biquad

-sampling

FIR

-scale Filter #1 #2 #3 #4

Or

Biquad #5

Or

Biquad #6

Or

Biquad #7

R

Sampling Frequency = 2xFs

Userd Defined Filters Tone Control

DocID024543 Rev 1 25/162

Device overview STA380BW

The second processing stage embeds a mixing block, a biquadratic/crossover filter, a DRC

stage, the volume control, a DC cut filter and a post scaler. Depending on the device

settings, the following configuration and features are available:

2.1 output with individually configurable anticlipper/DRCs (Figure 7): two individually

configurable DRC/anticlippers are available while the eighth biquadratic filter, jointly

with the mixer block, can be used to perform LFE. This configuration and features

ensure the backward compatibility with previous Sound Terminal® products.

Figure 7. Processing path, second part: 2.1 output with individually configurable

anticlipper/DRCs

L C1Mx1 Ch an n el ½

Biq uad #8 An ti-clipper

Ch an n el 1 DC Cut

+ --------------

Hi-p ass XO

Vo lume

/

DRC

Filter

Po st Scale

R C1Mx2 Filter

C2Mx1 Ch an n el ½

Biq uad #8 An ti-clipper

Ch an n el 2 DC Cut

+ --------------

Hi-p ass XO

Vo lume

/

DRC

Filter

Po st Scale

C2Mx2 Filter

C3Mx1 Ch an n el 3

Biq uad #8 An ti-clipper

Ch an n el 3 DC Cut

+ --------------

Lo w-p ass XO

Vo lume

/

DRC

Filter

Po st Scale

C3Mx2 filter

U s er-D efined C ros sov er F requenc y

M ix C oeffic ients D eterm ined by XO Setting

(User Defin ed If

XO =0000)

26/162 DocID024543 Rev 1

STA380BW Device overview

2.0 output with B2DRC (Figure 8): the mixer and the eighth biquadratic filter are used to

divide the channel into two sub-bands, then each sub-band is independently processed

by a DRC block. The two bands are then re-composed and fed to the following

processing blocks. The crossover frequency is user-selectable. This configuration and

features ensure the backward compatibility with the previous Sound Terminal®

products. For further information please refer to Chapter 6.11.1: Dual-band DRC.

Figure 8. Processing path, second part: 2.0 output with B2DRC

Channel 3

DRC 2

Volume

L C1Mx1

B2DRC

- Channel 1 DC Cut

+ Hi-pass XO

filter

+ Volume

DRC 1 + Filter

Post Scale

R C1Mx2

C2Mx1

B2DRC

Channel 2

+ Hi-pass XO

filter - + Volume

DRC 1

C2Mx2

C3Mx1

Channel 3 DC Cut

Volume

DRC 2 + Filter

Post Scale