Memory Locations and Addresses

Memory Locations and Addresses

Uploaded by

rosev15Copyright:

Available Formats

Memory Locations and Addresses

Memory Locations and Addresses

Uploaded by

rosev15Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Memory Locations and Addresses

Memory Locations and Addresses

Uploaded by

rosev15Copyright:

Available Formats

Memory Locations and

Addresses

Memory consists of many millions of

storage elements

One storage element can store one bit

of information

Memory is organized so that a group of

n bits (referred as word ) can be stored

or retrieved

.

.

.

.

.

.

n

bits

b30 b0 b1 b31

Sign bit: b31 = 0 for positive numbers

b31 = 1 for negative numbers

8 bits 8 bits 8 bits 8 bits

ASCII

Character

ASCII

Character

ASCII

Character

ASCII

Character

(a) A signed integer

(b) Four characters

.

.

.

.

.

.

0

1

2^k - 1

k no. of address

bits

24 address bits

generates an

address space of

2^24 (16 M)

locations

2^10 1K (1 Kilo =

1024)

2^20 1M (1 Mega)

2^30 1G (1 Giga)

2^40 1T (1 Tera)

Byte Addressability

a byte is 8 bits

the word length typically ranges from

16 to 64 bits

successive addresses refer to

successive byte locations in the

memory (generally used in computers)

Byte locations have addresses

0,1,2,.....

If the word length is 32 bits, successive

words are located at addresses

0,4,8,...... with each word consisting of

four bytes.

0 1 2 3

4 5 6 7

3 2 1 0

7 6 5 4

2^k-

4

2^k-

3

2^k-

2

2^k-

1

2^k-

1

2^k-

2

2^k-

3

2^k-

4

.

.

.

.

.

.

2^k-4

0

4

0

4

2^k-4

Word

Addres

s

Byte Address Byte Address

(a) Little-endian assignment (b) Big-endian assignment

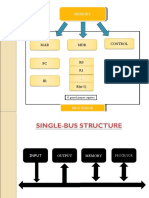

Instructions and Instruction

Sequencing

A computer must have instructions to

perform four types of operations:

Data transfers between the the memory and the

processor registers

Arithmetic and Logical operations on data

Program sequencing and control

I/O transfers

Two notations of instructions

Register transfer notation

Assembly language notation

Register Transfer Notation

R1 [LOC]

The contents of memory location LOC are transferred

into processor register R1

R3 [R1] + [R2]

PLACE [R2]

Assembly Language Notation

Move LOC, R1

Add R1,R2,R3

Move R2, PLACE

Basic Instruction Types

C = A+B -------- HLL statement

C [A] + [B] -------- RTN

assuming this is done in single machine

instruction

Add A,B,C ---------ALN

general instruction of this type has the format

(three address instruction)

Operation Source1, Source2, Destination

Basic Instruction Types

Use of a sequence of simpler instructions (two

address instructions)

Add A,B

Move B, C

in RTN

B [A]+[B]

C [B]

general instruction of this type has the format

Operation Source, Destination

Some machine instructions specify only

one operand.

When the second operand is needed, it

is understood implicitly to be in a

unique location, generally accumulator

(a processor register) is used

they become one address instructions

Add LOC

Load PLACE

Store PLACE

Basic Instruction Types

C= A+B

Load A

Add B

Store C

Basic Instruction Types

Use of processor registers allows faster

accessing and results in shorter

instructions

Load A, Ri or Move A, Ri

Store Ri, LOC or Move Ri,LOC

and

Add LOC, Ri

Basic Instruction Types

C= A+B

Move A,Ri

Add B, Ri

Store Ri, C

Basic Instruction Types

Move A,Ri

Move B,Rj

Add Ri,Rj

Store Rj, C

Transfers that involve the memory are much slower

than transfers within the processor.

A substantial increase in speed is achieved when

processor registers are utilized effectively.

C = A+B -------- HLL statement

C [A] + [B] -------- RTN

Assumptions we make

Compiler allows one memory operand per instruction

Word length is 32 bits and the memory is byte addressable

Single word instruction can include a full memory address

The three instructions are in successive word locations,

starting at location i

Instruction Execution and Straight-Line

Sequencing

Move A,R0

Add B,R0

Move R0,C

.

.

.

.

.

.

.

.

.

Contents Address

i

i+4

i+8

A

B

C

Begin execution

here

3-Instruction

program

segment

Data for the

program

A program for C =[A]+[B]

Execution of the program

To begin execution of the program, the address

of its first instruction (i in this case) is placed into

the PC.

Processor fetches and executes the first

instruction using the information available in PC.

During the execution first instruction, PC is

incremented by 4 to point next instruction.

Instructions are executed one at a time in the

order of increasing addresses. This is called

Straight-Line Sequencing

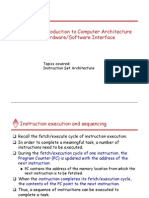

Execution of the program

Executing an instruction is a two-phase procedure

First Phase Instruction Fetch

Instruction is fetched from the memory location whose address

is in the PC

And placed in Instruction Register (IR)

Second Phase Instruction Execute

Instruction is decoded to determine the operations to be

performed.

The specified operations are performed by the processor. This

involves

Fetching operands from memory or from processor registers

Arithmetic and logical operations

Storing results into memory or registers

At some point during this two-phase procedure, the PC

is incremented to point the next instruction to be

exexcuted

Move NUM1,R0

Add NUM2,R0

Add NUM3,R0

Add NUMn,R0

Move R0,SUM

.

.

.

.

.

.

.

.

.

i+4

i+8

i

i+4n-4

i+4n

SUM

NUM2

NUMn

NUM1

Branching

The program sequence is changed form

straight-line sequencing by a branching

instruction

Previous example can be done using LOOP

Loop is repeated as many times as the numbers

to be added

To check whether all numbers added a counter

variable is used and it is imitated with the count

of numbers to be added

Each time the loop executed next number is

added and the count is decremented by 1.

The loop is repeated until the count becomes 0.

to do this a conditional branch instruction is used

Move N,R1

Clear R0

Determine address

of Next number

and add Next

number to R0

Decrement R1

Branch>0 LOOP

Move R0,SUM

.

.

.

n

.

.

.

LOOP

Program

Loop

SUM

N

NUM1

NUM2

NUMn

Condition Codes

Processor keeps track of the

information about the results of

operations for use by subsequent

conditional branch instruction.

Those information bits are called

condition code flags and they are

saved as a group in a register called

condition code register or status

register.

Individual condition code flags are set

to 1 or cleared to 0 depending on the

outcome of the operation

Four commonly used flags are

N (Negative) -Set to 1 if the result is

negative; otherwise cleared to 0

Z (Zero) -Set to 1 if the result is 0;

otherwise cleared to 0

V (Overflow) - Set to 1 if arithmetic

overflow occurs; otherwise cleared to 0

C (Carry) - Set to 1 if a carry results

from the operation; otherwise cleared to 0

Addressing Modes

Addressing means the way to specify

the address of an operand.

The different ways (flexible) of

addressing are called addressing

modes.

The details differ from one computer

to other, but the concepts are the

same.

Name

Assembler Syntax Addressing Function

Immediate #value Operand=value

Register Ri EA=Ri

Absolute(Direct) LOC EA=LOC

Indirect (Ri)

(LOC)

EA=[Ri]

EA=[LOC]

Index X(Ri) EA=[Ri]+X

Base with index (Ri,Rj) EA=[Ri]+[Rj]

Base with index

and offset

X(Ri,Rj) EA=[Ri]+[Rj]+X

Relative X(PC) EA=[PC]+X

Auto increment (Ri)+ EA=[Ri];

Increment Ri;

Auto decrement -(Ri) Decrement Ri;

EA=[Ri]

EA=Effective address Value= a signed number

Variables and Constants

They are simplest data types

In assembly language, a variable is

represented by allocating a register or a

memory location to hold its value

Constants are represented in the

instruction itself

Immediate addressing

The operand is given explicitly in the

instruction

Constants are represented using

Immediate addressing

For example,

Move #200,R0

Add #6, R1

Register Addressing

The operand is the content of a

processor register; the

name(address) of the register is

specified in the instruction

For example,

Add R1,R0

Absolute Addressing (Direct

Addressing)

The operand is in a memory location;

the address of this location is given

explicitly in the instruction

For example,

Move LOC,PLACE

In the following example,

Move LOC,R1

Both register and absolute addressing

mode are used.

Example: A = B+6 --- C statement

In assembly language

Move B, R0

Add #6,R0

Move R0,A

Indirect Addressing

The instruction does not give the operand or its

address explicitly

Information about the memory address of the

operand is given in the instruction

This address is called effective address (EA) of

the operand

Effective address of the operand is the content of

register or memory location whose address is

given in the instruction

EA=[Ri]

EA=[LOC]

For Example,

Add (A), R0

Move (R1),R2

Add (R1),R0

.

.

.

Operand

B

Add (A),R0

.

.

.

B

.

.

.

Operand

Main

memor

y

Register

B

R1

A

B

(b) Through a memory location (a) Through a general-purpose

register

Address Contents

Move N,R1

Move #NUM1,R2

Clear R0

Add (R2),R0

Add #4,R2

Decrement R1

Branch>0 LOOP

Move R0,SUM

Initialization

LOOP

Use of indirect addressing in the program

discussed before

n

.

.

.

SUM

N

NUM1

NUM2

NUMn

Data in memory

The register or the memory location that

contains the address of operand is called

pointer

Indirect Addressing through registers are

used extensively.

But Indirect Addressing through memory

location is seldom used, because it

involves accessing memory twice to get

an operand

Index Addressing

It is useful in dealing with lists and arrays

The Effective Address of the operand is

generated by adding a constant value to the

contents of register

For example,

Add X(Ri), Rj

The EA of first operand is [Ri]+X

Add 20(R1),R2

Operand

.

.

.

1000

.

.

.

Add 1000(R1),R2

Operand

.

.

.

20

.

.

.

1000

1020

1000

1020

20=Offset

R1

R1

(a) Offset is given as a constant

(b) Offset is in the index register

INDEXED

ADDRESSING

20=Offset

n

Student ID

Test 1

Test 2

Test3

Student ID

Test 1

Test 2

Test3

.

.

.

N

LIST

LIST + 4

LIST + 8

LIST + 16

LIST + 12

Student 1

Student 2

A LIST OF STUDENTS MARKS.

Move #LIST,R0

Clear R1

Clear R2

Clear R3

Move N,R4

Add 4(R0),R1

Add 8(R0),R2

Add 12(R0),R3

Add #16,R0

Decrement R4

Branch>0 LOOP

Move R1,SUM1

Move R2,SUM2

Move R3,SUM3

LOOP

INDEXED ADDRESSING USED IN ACCESSING TEST SCORES

IN THE LIST IN THE PREVIOUS FIGURE

Relative Addressing

The Effective Address is determined by the Index

mode using the Program Counter in place of the

general purpose register

For Example,

Branch>0 -16(PC)

Auto increment Addressing

The Effective Address of the operand is the

contents of a register specified in the instruction.

After accessing the operand, the contents of this

register are automatically incremented to point

the next item in the list

For Example,

Add (R1)+, R0

Address Contents

Move N,R1

Move #NUM1,R2

Clear R0

Add (R2)+, R0

Decrement R1

Branch>0 LOOP

Move R0,SUM

Initialization

LOOP

n

.

.

.

SUM

N

NUM1

NUM2

NUMn

Data in memory

Auto decrement Addressing

The contents of a register specified in the

instruction are first automatically decremented

and are then used as the effective address of the

operand

For Example,

Add -(R1), R0

You might also like

- Common Defects in Gas CuttingDocument14 pagesCommon Defects in Gas CuttingASHVIN YADAVNo ratings yet

- CPUDocument50 pagesCPUabhishek sNo ratings yet

- Sample Fall Protection PlanDocument30 pagesSample Fall Protection PlanSoner Kulte100% (1)

- MemoryDocument43 pagesMemoryuma_saiNo ratings yet

- Unit-Iii: Instructions & Instruction SequencingDocument8 pagesUnit-Iii: Instructions & Instruction SequencingSANTOSH4176No ratings yet

- COA Mod2Document51 pagesCOA Mod2Boban MathewsNo ratings yet

- Instructions and Instruction SequencingDocument25 pagesInstructions and Instruction Sequencingsamueljamespeter100% (4)

- CSE 243: Introduction To Computer Architecture and Hardware/Software InterfaceDocument31 pagesCSE 243: Introduction To Computer Architecture and Hardware/Software Interfaceachaparala4499No ratings yet

- MSB LSB: Unit Ii: Machine Instructions and ProgramsDocument17 pagesMSB LSB: Unit Ii: Machine Instructions and ProgramsNaveen A Rao RaoNo ratings yet

- L 5-AddressingModesDocument44 pagesL 5-AddressingModesLekshmiNo ratings yet

- CSA Unit 4Document71 pagesCSA Unit 4amrutapatil7483No ratings yet

- Code GenerationDocument25 pagesCode GenerationlyeabsraNo ratings yet

- Ch2 Lec2 Instruction Sets CharacteristicsDocument46 pagesCh2 Lec2 Instruction Sets CharacteristicsAlazar DInberuNo ratings yet

- Ch2 - Lec2 - Instruction Sets CharacteristicsDocument48 pagesCh2 - Lec2 - Instruction Sets CharacteristicsMagarsaa Qana'iiNo ratings yet

- Addressing Modes Instruction Set ArchitectureDocument15 pagesAddressing Modes Instruction Set ArchitectureSandeep VermaNo ratings yet

- CSE 243: Introduction To Computer Architecture and Hardware/Software InterfaceDocument26 pagesCSE 243: Introduction To Computer Architecture and Hardware/Software Interfaceachaparala4499No ratings yet

- Unit-2 Machine Instructions and Programs (Contd... ) and Basic Processing UnitDocument21 pagesUnit-2 Machine Instructions and Programs (Contd... ) and Basic Processing Unitprathuasharao2017No ratings yet

- CSE 243: Introduction To Computer Architecture and Hardware/Software InterfaceDocument31 pagesCSE 243: Introduction To Computer Architecture and Hardware/Software Interface123456ranoNo ratings yet

- Solved Problems 1Document4 pagesSolved Problems 1kimoNo ratings yet

- CD Unit 5 RVDocument23 pagesCD Unit 5 RVAkashNo ratings yet

- SS-2 MarksDocument47 pagesSS-2 MarkssivayagNo ratings yet

- Ss 1Document78 pagesSs 1lovelykdkingNo ratings yet

- CTCD Unit 4Document25 pagesCTCD Unit 4Ranjit47 HNo ratings yet

- cs2304 System Software 2 Marks and 16 Marks With AnswerDocument18 pagescs2304 System Software 2 Marks and 16 Marks With Answermanojkumar024No ratings yet

- CSE 259 Lecture3Document11 pagesCSE 259 Lecture3robin haqueNo ratings yet

- CAO - Mod1 Mymry, Adress, Adressing ModesDocument47 pagesCAO - Mod1 Mymry, Adress, Adressing ModesvkvNo ratings yet

- Computer OrganisationDocument27 pagesComputer OrganisationAmandeep SharmaNo ratings yet

- Assemblyunit 1Document51 pagesAssemblyunit 1RubyNo ratings yet

- Instruction Formats & Addressing Modes Prof. M P Patel: Topic: Guided byDocument21 pagesInstruction Formats & Addressing Modes Prof. M P Patel: Topic: Guided byHarshit BhayaniNo ratings yet

- System Software 2 Marks and 16 Marks With AnswerDocument23 pagesSystem Software 2 Marks and 16 Marks With AnswerpriyaaramNo ratings yet

- Coa Unit III Part IIDocument23 pagesCoa Unit III Part IIkontham sirisejaNo ratings yet

- System Software2markDocument31 pagesSystem Software2markMohammed HashimNo ratings yet

- Instructions and Instruction SequencingDocument12 pagesInstructions and Instruction SequencingComputer NotesNo ratings yet

- Addressing ModesDocument9 pagesAddressing ModesSouvik MondalNo ratings yet

- (SS) System Software Viva Question and AnswersDocument15 pages(SS) System Software Viva Question and AnswersVenkatesh NaiduNo ratings yet

- 2 MarksDocument17 pages2 MarksGeetha ParthibanNo ratings yet

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsDocument8 pagesCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryNo ratings yet

- DpcoDocument19 pagesDpcos.brainyajayNo ratings yet

- Instructions and Instruction SequencingDocument12 pagesInstructions and Instruction SequencingComputer NotesNo ratings yet

- Chapter 3 LMSDocument37 pagesChapter 3 LMSvexadid644No ratings yet

- Instruction Execution and Straight-Line SequencingDocument5 pagesInstruction Execution and Straight-Line SequencingRavindra RathodNo ratings yet

- Annauniv 5thsem Sytsemsoftware Students CornersDocument21 pagesAnnauniv 5thsem Sytsemsoftware Students CornersstudentscornersNo ratings yet

- Rajalakshmi Engineering College: CS2308 - SS Lab VVQ Unit I-IntroductionDocument17 pagesRajalakshmi Engineering College: CS2308 - SS Lab VVQ Unit I-IntroductionssarvinthNo ratings yet

- Central Processing UnitDocument11 pagesCentral Processing UnitPace InfotechNo ratings yet

- Chapter 8 - Code GenerationDocument22 pagesChapter 8 - Code Generationsindhura2258No ratings yet

- Cs8491 CA QbankDocument128 pagesCs8491 CA QbankSuresh Kanna100% (1)

- General Register OrganizationDocument16 pagesGeneral Register OrganizationGovind UpadhyayNo ratings yet

- 8051 Instruction SetDocument73 pages8051 Instruction SettbijleNo ratings yet

- Code GenerationDocument22 pagesCode GenerationDivyanshu KantolNo ratings yet

- Code GenerationDocument49 pagesCode GenerationCandy AngelNo ratings yet

- Instruction Set Architecture: Logic and Computer Design FundamentalsDocument50 pagesInstruction Set Architecture: Logic and Computer Design FundamentalslogintojalluriNo ratings yet

- Module-6 COMPUTER ARCHITECTUREDocument25 pagesModule-6 COMPUTER ARCHITECTUREpranaykumarghosh41No ratings yet

- 8051 Assembly LanguageDocument39 pages8051 Assembly LanguagemanvithbNo ratings yet

- MODULE-2 - Addressing ModesDocument104 pagesMODULE-2 - Addressing ModestasmiyashaikhNo ratings yet

- C Ompiler Theory: (Intermediate C Ode Generation - Abstract S Yntax + 3 Address C Ode)Document32 pagesC Ompiler Theory: (Intermediate C Ode Generation - Abstract S Yntax + 3 Address C Ode)Saipavanesh GuggilapuNo ratings yet

- Coa Unit1Document99 pagesCoa Unit1Ashish SharmaNo ratings yet

- Ca Lec4Document20 pagesCa Lec4Sana IftikharNo ratings yet

- Addressing ModesDocument20 pagesAddressing ModesAkhil B SkariaNo ratings yet

- Conceptual Programming: Conceptual Programming: Learn Programming the old way!From EverandConceptual Programming: Conceptual Programming: Learn Programming the old way!No ratings yet

- Introduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 AssemblyFrom EverandIntroduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 AssemblyNo ratings yet

- Social IntelligenceDocument1 pageSocial Intelligencerosev15No ratings yet

- Early Cultivation: Neolithic Asia Minor Ancient Greece Levant Mesopotamian Fertile CrescentDocument1 pageEarly Cultivation: Neolithic Asia Minor Ancient Greece Levant Mesopotamian Fertile Crescentrosev15No ratings yet

- OliveDocument1 pageOliverosev15No ratings yet

- CreativityDocument1 pageCreativityrosev15No ratings yet

- Knowledge Representation Commonsense KnowledgeDocument1 pageKnowledge Representation Commonsense Knowledgerosev15No ratings yet

- Planning: Automated Planning and SchedulingDocument1 pagePlanning: Automated Planning and Schedulingrosev15No ratings yet

- Machine Perception Tactile Sensors Computer Vision Speech Recognition Facial Recognition Object RecognitionDocument1 pageMachine Perception Tactile Sensors Computer Vision Speech Recognition Facial Recognition Object Recognitionrosev15No ratings yet

- LongDocument1 pageLongrosev15No ratings yet

- The Breadth of Commonsense KnowledgeDocument1 pageThe Breadth of Commonsense Knowledgerosev15No ratings yet

- Artificial Intelligence (AI) IsDocument1 pageArtificial Intelligence (AI) Isrosev15No ratings yet

- LearningDocument1 pageLearningrosev15No ratings yet

- LTE Advanced 3Gpp: See Also: BelowDocument1 pageLTE Advanced 3Gpp: See Also: Belowrosev15No ratings yet

- Uncertain Probability Economics Combinatorial Explosion: Reasoning, Problem SolvingDocument1 pageUncertain Probability Economics Combinatorial Explosion: Reasoning, Problem Solvingrosev15No ratings yet

- Modes of Operation: Landline Channels Full-Duplex Bandwidth ImtsDocument1 pageModes of Operation: Landline Channels Full-Duplex Bandwidth Imtsrosev15No ratings yet

- IMT-2000 Compliant 4G StandardsDocument1 pageIMT-2000 Compliant 4G Standardsrosev15No ratings yet

- Background: System Spectral Efficiency BitDocument1 pageBackground: System Spectral Efficiency Bitrosev15No ratings yet

- IMT-Advanced Requirements: Itu-R Cellular SystemDocument1 pageIMT-Advanced Requirements: Itu-R Cellular Systemrosev15No ratings yet

- 4G Is The Fourth Generation ofDocument1 page4G Is The Fourth Generation ofrosev15No ratings yet

- Technical Understanding: International Telecommunications Union-Radio Communications SectorDocument1 pageTechnical Understanding: International Telecommunications Union-Radio Communications Sectorrosev15No ratings yet

- T-Mobile International AG Is A German: Telekom)Document1 pageT-Mobile International AG Is A German: Telekom)rosev15No ratings yet

- Derived Unit Electric Potential Electric Potential Difference Electromotive Force Alessandro Volta Voltaic Pile BatteryDocument1 pageDerived Unit Electric Potential Electric Potential Difference Electromotive Force Alessandro Volta Voltaic Pile Batteryrosev15No ratings yet

- Radiotelephone (Or Radiophone) Is A: Communications Radio Audio Radiotelegraphy Telegraph Video Two-Way RadioDocument1 pageRadiotelephone (Or Radiophone) Is A: Communications Radio Audio Radiotelegraphy Telegraph Video Two-Way Radiorosev15No ratings yet

- Voltage, Electric Potential Difference, Electric Pressure or Electric Tension (FormallyDocument1 pageVoltage, Electric Potential Difference, Electric Pressure or Electric Tension (Formallyrosev15No ratings yet

- Cryptography or Cryptology (From: - LogiaDocument1 pageCryptography or Cryptology (From: - Logiarosev15No ratings yet

- UsesDocument1 pageUsesrosev15No ratings yet

- Software Hotspots: WAN Internet Bridging Tethering Android Apple OS X Windows Mobile Linux Atheros Broadcom Intel NicsDocument1 pageSoftware Hotspots: WAN Internet Bridging Tethering Android Apple OS X Windows Mobile Linux Atheros Broadcom Intel Nicsrosev15No ratings yet

- Supplementary Slides For Software Engineering: A Practitioner's Approach, 5/eDocument9 pagesSupplementary Slides For Software Engineering: A Practitioner's Approach, 5/erosev15No ratings yet

- Supplementary Slides For Software Engineering: A Practitioner's Approach, 5/eDocument13 pagesSupplementary Slides For Software Engineering: A Practitioner's Approach, 5/erosev15No ratings yet

- Piton Policarbonato Chorro-Niebla 1.5 Giacomini A7bp Certf. Ul-FmDocument2 pagesPiton Policarbonato Chorro-Niebla 1.5 Giacomini A7bp Certf. Ul-FmEdgar YauriNo ratings yet

- Furniture DetailDocument40 pagesFurniture DetailEdi CahyadiNo ratings yet

- Information Handout3012013Document6 pagesInformation Handout3012013Nikhil MeshramNo ratings yet

- Tutorium Refrigeration SolutionDocument20 pagesTutorium Refrigeration SolutionwanpudinNo ratings yet

- BMW E39 Radio Obc Mid ManualDocument65 pagesBMW E39 Radio Obc Mid ManualNLBananasNo ratings yet

- Pega Ba Flow and Data Modeling: AshockDocument19 pagesPega Ba Flow and Data Modeling: AshockvenkatNo ratings yet

- Naming Convention For Android DevelopmentDocument5 pagesNaming Convention For Android DevelopmentnylhstarNo ratings yet

- 109-23-24 Ambattur QuestionsDocument1 page109-23-24 Ambattur Questionsjohnstruct archNo ratings yet

- Hvac-Mappysil CR 404 - Acoustic InsulationDocument1 pageHvac-Mappysil CR 404 - Acoustic Insulationanwar2masNo ratings yet

- Zhong Chen Slides 1620847925786Document8 pagesZhong Chen Slides 1620847925786Priya ReddyNo ratings yet

- Magnets and Electromagnets (Requires JAVA)Document5 pagesMagnets and Electromagnets (Requires JAVA)Izza Zamora NeriaNo ratings yet

- Model No.: N133Bge Suffix: E31: Product SpecificationDocument38 pagesModel No.: N133Bge Suffix: E31: Product SpecificationkornolNo ratings yet

- F3826CDocument14 pagesF3826CJumongNo ratings yet

- MIS StructureDocument39 pagesMIS StructureAbdullah GubbiNo ratings yet

- ASME 36 (Ss Piping)Document1 pageASME 36 (Ss Piping)Muhammad AhsanNo ratings yet

- Jetstream Europe Brochure EnglishDocument6 pagesJetstream Europe Brochure EnglishFernando ZamoraNo ratings yet

- Cara Menghitung Ukuran Pipa Kapiler RefrigerasiDocument54 pagesCara Menghitung Ukuran Pipa Kapiler RefrigerasiZikko FirmansyahNo ratings yet

- L.6. Pemodelan MatematisDocument23 pagesL.6. Pemodelan MatematisNasikhuddin100% (1)

- Sennheiser Price List 2010Document12 pagesSennheiser Price List 2010Karen IlustrisimoNo ratings yet

- Mos Field Effect Transistor: Data SheetDocument8 pagesMos Field Effect Transistor: Data SheetAdam SchwemleinNo ratings yet

- Mediabox: User'S ManualDocument42 pagesMediabox: User'S ManualMohd Khairul Md DinNo ratings yet

- Interface para Usar El Osciloscopio Como Diagnosticador Por ImágenesDocument5 pagesInterface para Usar El Osciloscopio Como Diagnosticador Por ImágenesWilliams BurgosNo ratings yet

- Acematt Ok 412Document1 pageAcematt Ok 412optimus_1404No ratings yet

- Be Happy and Make Others To Be Happy - Oracle EBS R12 Purchasing, Inventory, Order Management QueriesDocument17 pagesBe Happy and Make Others To Be Happy - Oracle EBS R12 Purchasing, Inventory, Order Management QueriesGanapathiraju SravaniNo ratings yet

- WWW Sanfoundry Com C Program Number Divisible by 5Document5 pagesWWW Sanfoundry Com C Program Number Divisible by 5प्रतीक प्रकाशNo ratings yet

- SpinchillercontrollerDocument59 pagesSpinchillercontrollerIgnacio LopezNo ratings yet

- MESC Description PI04Document4 pagesMESC Description PI04Reastu SaputraNo ratings yet

- PFMEA New FormatDocument63 pagesPFMEA New FormatArshad AnsariNo ratings yet