## Optimization of data transfer on many-core processors, applied to dense linear algebra and stencil computations Minh Quan Ho

### ▶ To cite this version:

Minh Quan Ho. Optimization of data transfer on many-core processors, applied to dense linear algebra and stencil computations. Performance [cs.PF]. Université Grenoble Alpes, 2018. English. NNT: 2018 GREAM042. tel-02426014

### HAL Id: tel-02426014 https://theses.hal.science/tel-02426014

Submitted on 1 Jan 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

### Minh Quan HO

Thèse dirigée par Bernard TOURANCHEAU, Professeur, UGA

préparée au sein du Laboratoire Laboratoire d'Informatique de Grenoble

dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

Optimisation de transfert de données pour les processeurs pluri-coeurs, appliqué à l'algèbre linéaire et aux calculs sur stencils

## Optimization of data transfer on many-core processors, applied to dense linear algebra and stencil computations

Thèse soutenue publiquement le **5 juillet 2018**, devant le jury composé de :

### Monsieur BERNARD TOURANCHEAU

PROFESSEUR, UNIVERSITE GRENOBLE ALPES, Directeur de thèse **Monsieur JOËL FALCOU**

MAITRE DE CONFERENCES, UNIVERSITE PARIS-SUD, Rapporteur

#### Monsieur FRANCISCO DANIEL IGUAL PENA

ASSISTANT PROFESSEUR, UNIV. COMPLUTENSE DE MADRID - ESPAGNE, Rapporteur

#### Monsieur CHRISTIAN OBRECHT

MAITRE DE CONFERENCES, INSA LYON, Examinateur

### Monsieur BENOÎT DUPONT DE DINECHIN

DIRECTEUR DE LA TECHNOLOGIE, KALRAY S.A. - MONTBONNOT-SAINT-MARTIN, Examinateur

#### Monsieur RAPHAËL COUTURIER

PROFESSEUR, UNIVERSITE BOURGOGNE FRANCHE-COMTE, Président

**Disclaimer**: The views and opinions expressed in this document are those of the author and do not necessarily reflect the official policy or position of the Kalray corporate or the University Grenoble Alps, the National Institute of Applied Sciences of Lyon (INSA Lyon) and the University Claude Bernard Lyon 1.

### Abstract

Upcoming Exascale target in High Performance Computing (HPC) and disruptive achievements in artificial intelligence give emergence of alternative non-conventional many-core architectures, with energy efficiency typical of embedded systems, and providing the same software ecosystem as classic HPC platforms. A key enabler of energy-efficient computing on many-core architectures is the exploitation of data locality, specifically the use of scratchpad memories in combination with DMA engines in order to overlap computation and communication. Such software paradigm raises considerable programming challenges to both the vendor and the application developer. In this thesis, we tackle the memory transfer and performance issues, as well as the programming challenges of memory- and compute-intensive HPC applications on the Kalray MPPA many-core architecture.

With the first memory-bound use-case of the lattice Boltzmann method (LBM), we provide generic and fundamental techniques for decomposing three-dimensional iterative stencil problems onto clustered many-core processors fitted with scratchpad memories and DMA engines. The developed DMA-based streaming and overlapping algorithm delivers 33% performance gain over the default cache-based implementation. High-dimensional stencil computation suffers serious I/O bottleneck and limited on-chip memory space. We developed a new in-place LBM propagation algorithm, which reduces by half the memory footprint and yields 1.5 times higher performance-per-byte efficiency than the state-of-the-art out-of-place algorithm.

On the compute-intensive side with dense linear algebra computations, we build a matrix multiplication benchmark based on exploitation of scratchpad memory and efficient asynchronous DMA communication. This program delivers 350 GFLOPS, or 86% of theoretical performance of the MPPA. These techniques are then extended to a DMA module of the BLIS framework, which allows us to instantiate an optimized and portable level-3 BLAS numerical library on any DMA-based architecture, in less than 100 lines of code. We achieve 75% peak performance on the MPPA processor with the matrix multiplication operation (GEMM) from the standard BLAS library, without having to write thousands of lines of laboriously optimized code for the same result.

### Résumé

La prochaine cible de Exascale en calcul haute performance (High Performance Computing - HPC) et des récent accomplissements dans l'intelligence artificielle donnent l'émergence des architectures alternatives non conventionnelles, dont l'efficacité énergétique est typique des systèmes embarqués, tout en fournissant un écosystème de logiciel équivalent aux plateformes HPC classiques. Un facteur clé de performance de ces architectures à plusieurs cœurs est l'exploitation de la localité de données, en particulier l'utilisation de mémoire locale (scratchpad) en combinaison avec des circuits d'accès direct à la mémoire (Direct Memory Access - DMA) afin de chevaucher le calcul et la communication. Un tel paradigme soulève des défis de programmation considérables à la fois au fabricant et au développeur d'application. Dans cette thèse, nous abordons les problèmes de transfert et d'accès aux mémoires hiérarchiques, de performance de calcul, ainsi que les défis de programmation des applications HPC, sur l'architecture pluri-cœurs MPPA de Kalray.

Pour le premier cas d'application lié à la méthode de Boltzmann sur réseau (Lattice Boltzmann method - LBM), nous fournissons des techniques génériques et réponses fondamentales à la question de décomposition d'un domaine stencil itérative tridimensionnelle sur les processeurs clusterisés équipés de mémoires locales et de circuits DMA. Nous proposons un algorithme de streaming et de recouvrement basé sur DMA, délivrant 33% de gain de performance par rapport à l'implémentation basée sur la mémoire cache par défaut. Le calcul de stencil multi-dimensionnel souffre d'un goulot d'étranglement important sur les entrées/sorties de données et d'espace mémoire sur puce limitée. Nous avons développé un nouvel algorithme de propagation LBM sur-place (in-place). Il consiste à travailler sur une seule instance de données, au lieu de deux, réduisant de moitié l'empreinte mémoire et cède une efficacité de performance-par-octet 1.5 fois meilleure par rapport à l'algorithme traditionnel dans l'état de l'art.

Du côté du calcul intensif avec l'algèbre linéaire dense, nous construisons un benchmark de multiplication matricielle, basé sur l'exploitation de la mémoire locale et la communication DMA asynchrone. Ce programme atteint 350 GFLOPS, soit 86% de la performance théorique de MPPA. Ces techniques sont ensuite étendues à un module DMA générique du framework BLIS, ce qui nous permet d'instancier une bibliothèque BLAS3 (Basic Linear Algebra Subprograms) portable et optimisée sur n'importe quelle architecture basée sur DMA, en moins de 100 lignes de code. Nous atteignons une performance maximale de 75% du théorique sur le processeur MPPA avec l'opération de multiplication de matrices (GEMM) de BLAS, sans avoir à écrire des milliers de lignes de code laborieusement optimisé pour le même résultat.

### Acknowledgements

First, I would like to express my respectful thanks to my advisors: Bernard Tourancheau for his experience, patience and methodological research guidance; Christian Obrecht for his expertise in numerical simulation, relevant questions and thorough correction of all my writings; Benoît Dinechin for his deep knowledge, motivation and lightful recommendations.

My special thanks are extended to the reviewers and examiners for their acceptation and their time to study my manuscript and my PhD defense.

I also express my great appreciation to my colleagues at Kalray and LIG: Julien Hascoet, Nicolas Brunie, Julien Lemaire, Romarik Jodin, Jérôme Reybert, Pierre Guironnet de Massas, Clément Leger, Michael Mercier, Van Toan Dao, Baptiste Jonglez, Elodie Morin, Henry-Joseph Audeoud, Pierre Brunisholz, Timothy Claeys and many others for their kindness, interesting discussions, technical support or coffee breaks and cookies during my thesis.

My particular thanks go to members of the SHPC group at the University of Texas at Austin: Field G. Van Zee, Robert A. Van de Geijn, Devangi Parikh, Tyler Michael Smith and Devin Matthews for their friendly contact and valuable discussions.

Some experiments presented in this manuscript would have not been possible without ample access to the PLAFRIM experimental testbed, being developed under the Inria PLAFRIM development action with support from Bordeaux INP, LABRI and IMB and other entities.

I would also like to give special thanks to Jacques Sicard, a grandparent-friendship who helped me a lot in my studies and life, especially during the hard beginning of this thesis.

To my elder brother, our parents and family for their trust and continuous encouragement.

To my daughter Ivy.

And to my wife Linh for your love and givings.

## Contents

| Al  | ostra              | et                                                                | v                          |

|-----|--------------------|-------------------------------------------------------------------|----------------------------|

| Ré  | sum                | 3                                                                 | vi                         |

| Ac  | knov               | vledgements                                                       | vii                        |

| Lis | st of              | Figures                                                           | xiii                       |

| Lis | st of              | Tables                                                            | $\mathbf{x}\mathbf{v}$     |

| Ac  | crony              | ms                                                                | xvii                       |

| In  | tro                | luction                                                           | 1                          |

| 1   | High<br>1.1<br>1.2 | Performance Computing: from Single-core to Many-core Introduction | 5<br>5<br>6<br>9           |

| 2   | 2.1<br>2.2<br>2.3  | ice Boltzmann method (LBM)  Background                            | 12<br>13<br>14<br>14<br>15 |

| 3   | <b>Basi</b> 3.1    | c Linear Algebra Subprograms (BLAS)  Background                   |                            |

Contents CONTENTS

|              | 3.3  | Summ    | ary 2                                                                                                                      | 5 |

|--------------|------|---------|----------------------------------------------------------------------------------------------------------------------------|---|

| 4            | Kal  | •       | assively Parallel Processor Array (MPPA)                                                                                   |   |

|              | 4.1  | Introd  | uction $\dots \dots \dots$ | 8 |

|              |      | 4.1.1   | Company                                                                                                                    | 8 |

|              |      | 4.1.2   | MPPA architecture overview                                                                                                 | 8 |

|              | 4.2  | Progra  | amming models                                                                                                              | 9 |

|              |      | 4.2.1   | Distributed-memory POSIX-C                                                                                                 | 9 |

|              |      | 4.2.2   | Host-based OpenCL acceleration                                                                                             | 0 |

|              | 4.3  | Summ    | ary                                                                                                                        | 1 |

| $\mathbf{C}$ | ont  | ribut   | ions 3                                                                                                                     | 3 |

| 5            | Opt  | timizin | g 3D LBM on Many-core Processors 3                                                                                         | 5 |

|              | 5.1  |         | $uction \dots \dots$ | 6 |

|              | 5.2  |         | d work                                                                                                                     |   |

|              | 5.3  |         | evel 3D asynchronous API                                                                                                   |   |

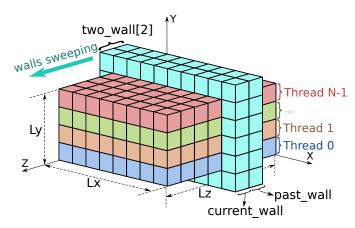

|              | 5.4  |         | ned 3D LBM stencil on clustered many-core processors 4                                                                     |   |

|              |      | 5.4.1   | Global algorithm                                                                                                           |   |

|              |      | 5.4.2   | Subdomain distribution                                                                                                     |   |

|              |      | 5.4.3   | Local subdomain dimensions                                                                                                 |   |

|              |      | 5.4.4   | Local and remote copy-index management                                                                                     |   |

|              | 5.5  |         | s and discussions                                                                                                          |   |

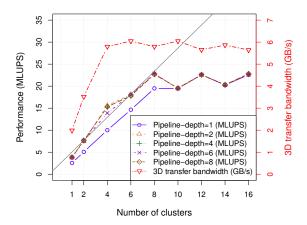

|              | 0.0  | 5.5.1   | Pipelined 3D LBM stencil on MPPA                                                                                           |   |

|              |      | 5.5.1   | Performance extrapolation                                                                                                  |   |

|              | 5.6  |         | sions                                                                                                                      |   |

| 6            | In-r | olace I | BM Propagation Algorithms 55                                                                                               | 3 |

| •            | 6.1  |         | uction                                                                                                                     |   |

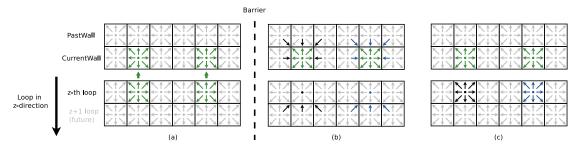

|              | 6.2  |         | vall propagation algorithm                                                                                                 |   |

|              | 0.2  | 6.2.1   |                                                                                                                            |   |

|              |      | 6.2.1   | Advantages and limitations                                                                                                 |   |

|              | 6.3  | -       | -wall propagation algorithm                                                                                                |   |

|              | 6.4  |         | mentations                                                                                                                 |   |

|              | 0.4  | 6.4.1   | OpenMP                                                                                                                     |   |

|              |      | 6.4.1   | _                                                                                                                          |   |

|              | 6 5  |         | OpenCL                                                                                                                     |   |

|              | 6.5  |         |                                                                                                                            |   |

|              |      | 6.5.1   | OpenMP                                                                                                                     |   |

|              | c c  | 6.5.2   | OpenCL                                                                                                                     |   |

|              | 6.6  | Conci   | asions                                                                                                                     | ( |

| 7            |      | _       | Passing Interface (MPI) on Many-core Processors 69                                                                         |   |

|              | 7.1  |         | uction                                                                                                                     |   |

|              | 7.2  |         | d works                                                                                                                    |   |

|              | 7.3  |         | a-MPI design                                                                                                               |   |

|              |      | 7.3.1   | MPI-inter-process Control (MPIC)                                                                                           |   |

|              |      | 7.3.2   | MPI-inter-process Data-Transfer (MPIDT)                                                                                    | 3 |

*Contents* xi

|              | 7.4    | MPPA-MPI implementation                                    | . 75  |

|--------------|--------|------------------------------------------------------------|-------|

|              |        | 7.4.1 MPI_Send - MPI_Recv                                  | . 75  |

|              |        | 7.4.2 MPI_Isend - MPI_Recv                                 | . 76  |

|              |        | 7.4.3 Optimization                                         | . 76  |

|              | 7.5    | MPPA-MPI Throughput modeling                               | . 78  |

|              | 7.6    | Results and Discussion                                     | . 79  |

|              |        | 7.6.1 Inter-CC communication                               | . 80  |

|              |        | 7.6.2 CC-IOS communication                                 | . 80  |

|              |        | 7.6.3 Optimization comparison                              | . 81  |

|              | 7.7    | High Performance Linpack (HPL) on MPPA-256                 | . 82  |

|              | 7.8    | Limitations and conclusions                                | . 83  |

| 8            | Ger    | neral Matrix Multiplication (GEMM) on Many-core Processors | 85    |

|              | 8.1    | Introduction                                               | . 86  |

|              | 8.2    | GEMM in POSIX-C                                            | . 86  |

|              |        | 8.2.1 Algorithm                                            | . 86  |

|              |        | 8.2.2 Assembly-level GEMM micro-kernel                     | . 88  |

|              | 8.3    | GEMM in OpenCL Data-Parallel                               | . 88  |

|              | 8.4    | GEMM in OpenCL POSIX-like (Task-Parallel)                  | . 90  |

|              |        | 8.4.1 Execution and memory mapping                         | . 90  |

|              |        | 8.4.2 Integration of object code or library                | . 91  |

|              | 8.5    | Results                                                    | . 92  |

|              | 8.6    | Conclusions                                                | . 94  |

| 9            | Por    | table and Optimized BLAS Library on Many-core Processors   | 95    |

|              | 9.1    | Introduction                                               | . 96  |

|              | 9.2    | Related work                                               |       |

|              | 9.3    | Portable DMA support for level-3 BLIS                      | . 98  |

|              |        | 9.3.1 Algorithm overview                                   |       |

|              |        | 9.3.2 Memory management                                    | . 99  |

|              |        | 9.3.3 Asynchronous DMA back-end interface                  | . 101 |

|              |        | 9.3.4 Special cases handling                               |       |

|              | 9.4    | Experimental results                                       |       |

|              |        | 9.4.1 Hardware configuration                               |       |

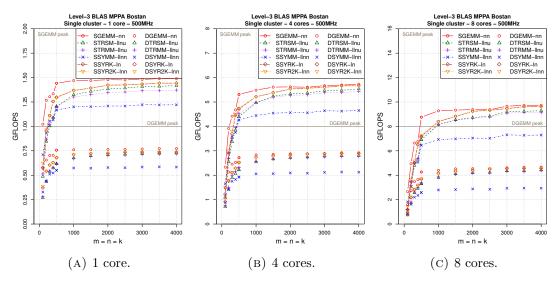

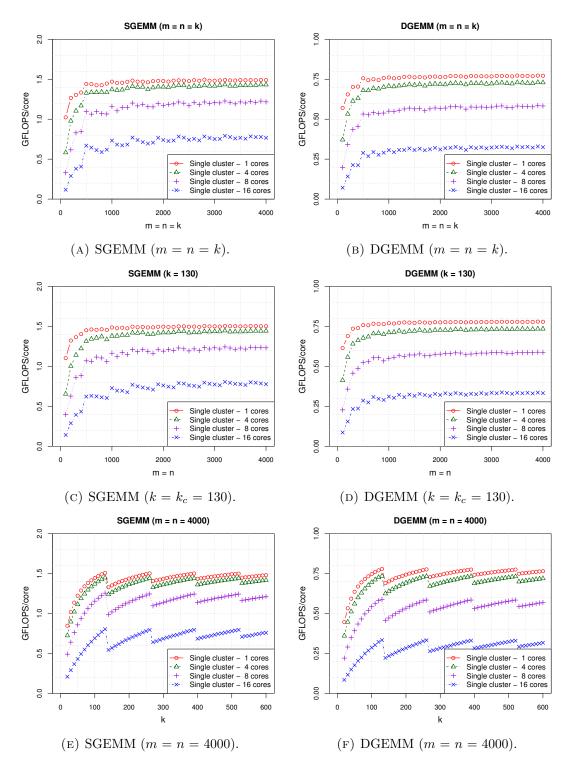

|              |        | 9.4.2 Multi-core level-3 BLAS                              | . 107 |

|              |        | 9.4.3 Multi-core xGEMM in different shapes                 | . 108 |

|              | 9.5    | Conclusions                                                | . 110 |

| C            | onc    | lusions                                                    | 111   |

| $\mathbf{C}$ | 0110   | 14010110                                                   | 111   |

| $\mathbf{A}$ | BL     | IS RDMA backend: reference and MPPA implementation         | 115   |

| B            | ibliog | graphy                                                     | 119   |

## List of Figures

| 1.1        | Moore's law illustration                                                                                                                                                                                                                                                | 4        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | Projected performance of the Top500 list                                                                                                                                                                                                                                | 6        |

| 1.3        | Processor-memory performance gap                                                                                                                                                                                                                                        | 6        |

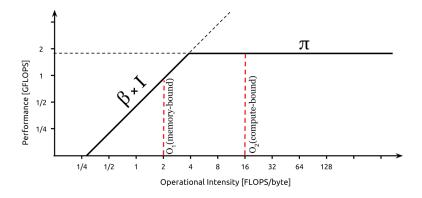

| 1.4        | Arithmetic intensity                                                                                                                                                                                                                                                    | 7        |

| 1.5        | Roofline model                                                                                                                                                                                                                                                          | 8        |

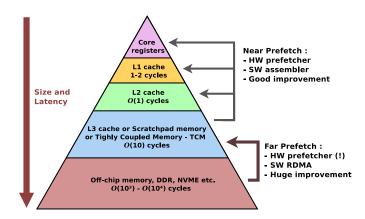

| 1.6        | Different levels and latencies in memory hierarchy                                                                                                                                                                                                                      | 8        |

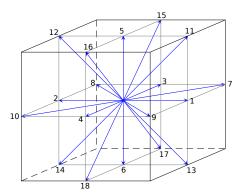

| 2.1        | LBM D3Q19 stencil                                                                                                                                                                                                                                                       | 12       |

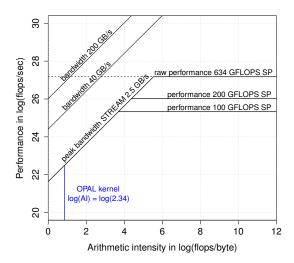

| 2.2        | D3Q19 LBM applied on MPPA2 roofline model                                                                                                                                                                                                                               | 14       |

| 2.3        | Propagation schemes of LBM in the D2Q9 sketch                                                                                                                                                                                                                           | 15       |

| 2.4        |                                                                                                                                                                                                                                                                         | 16       |

| 2.5        | D2Q9 version of AA-pattern                                                                                                                                                                                                                                              | 16       |

| 3.1        | Matrix multiplication                                                                                                                                                                                                                                                   | 21       |

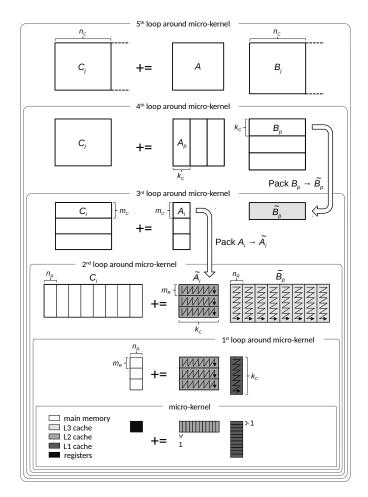

| 3.2        | Cache-based layer design of BLIS                                                                                                                                                                                                                                        | 24       |

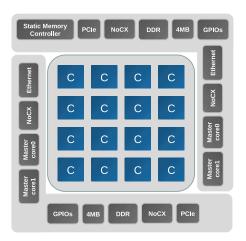

| 4.1        | MPPA-256 processor overview.                                                                                                                                                                                                                                            | 28       |

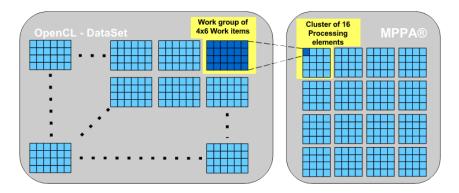

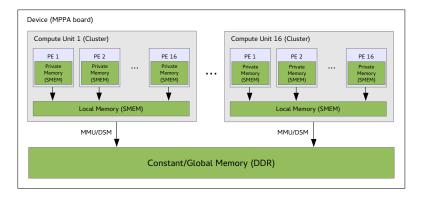

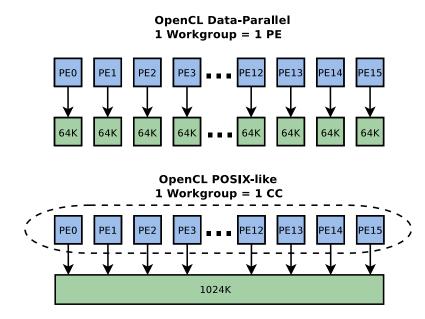

| 4.2        | OpenCL Data-Parallel: execution mapping                                                                                                                                                                                                                                 | 30       |

| 4.3        | OpenCL Data-Parallel: memory mapping                                                                                                                                                                                                                                    | 30       |

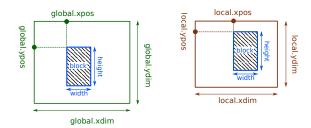

| 5.1        | A part of MPPA Async API for 3D transfer                                                                                                                                                                                                                                |          |

| 5.2        | Illustration of point2d_t datatype for 2D copy                                                                                                                                                                                                                          |          |

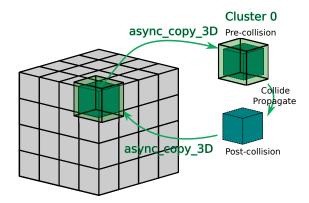

| 5.3        | 3D LBM/stencil decomposition                                                                                                                                                                                                                                            |          |

| 5.4        |                                                                                                                                                                                                                                                                         | 42       |

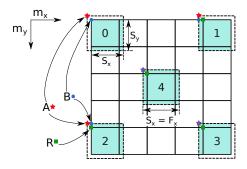

| 5.5        | 3D Row-major subdomain-indexing                                                                                                                                                                                                                                         |          |

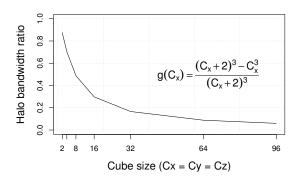

| 5.6        |                                                                                                                                                                                                                                                                         | 44       |

| 5.7        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                   | 46       |

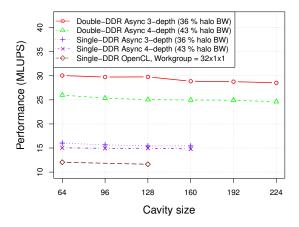

| 5.8        | OPAL_async vs. OPAL OpenCL on MPPA                                                                                                                                                                                                                                      |          |

| 5.9        | Performance extrapolation of OPAL_async                                                                                                                                                                                                                                 | 50       |

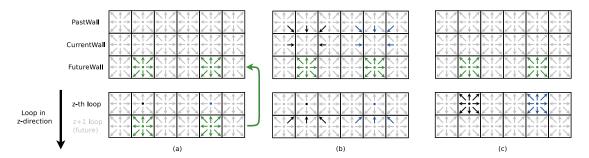

| 6.1        | In-place updates on a grid using $two-wall$ algorithm                                                                                                                                                                                                                   |          |

| 6.2        | Da0a + 6m 11+ 11-1                                                                                                                                                                                                                                                      | 56       |

|            | D2Q9 version of Two-wall in pull scheme                                                                                                                                                                                                                                 |          |

| 6.3        | D2Q9 version of three-wall in pull scheme                                                                                                                                                                                                                               | 59       |

| 6.3<br>6.4 | D2Q9 version of <i>three-wall</i> in pull scheme                                                                                                                                                                                                                        | 59       |

|            | D2Q9 version of three-wall in pull scheme                                                                                                                                                                                                                               | 59<br>60 |

| 6.4<br>6.5 | D2Q9 version of three-wall in pull scheme.  Shared-memory OpenMP pseudo-code of Two-wall and Three-wall in D3Q19.  Heterogeneous memory OpenCL implementation of Two-wall and Three-wall in D3Q19.                                                                      | 59       |

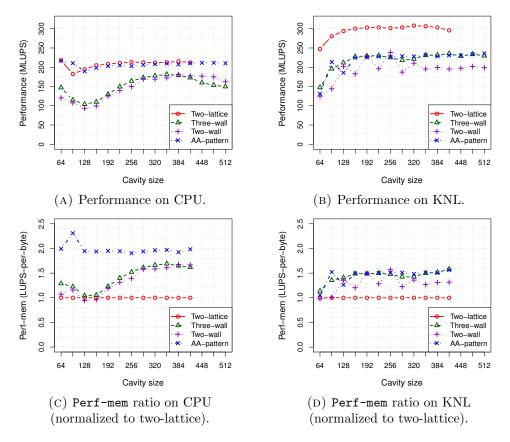

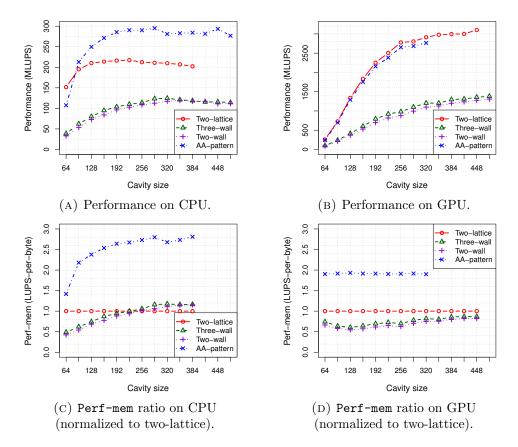

| 6.4        | D2Q9 version of three-wall in pull scheme.  Shared-memory OpenMP pseudo-code of Two-wall and Three-wall in D3Q19.  Heterogeneous memory OpenCL implementation of Two-wall and Three-wall in D3Q19.  Comparison of different propagation algorithms in OpenMP on CPU and | 59<br>60 |

List of Figures LIST OF FIGURES

| 6.7 | Comparison of different propagation algorithms implemented in OpenCL on CPU and GPU |

|-----|-------------------------------------------------------------------------------------|

| 7.1 | Control message structures                                                          |

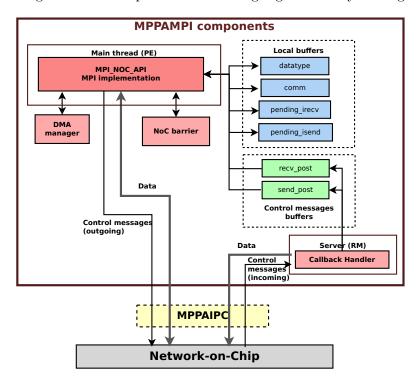

| 7.2 | MPPA-MPI components and interaction with                                            |

|     | Network-on-chip through MPPAIPC                                                     |

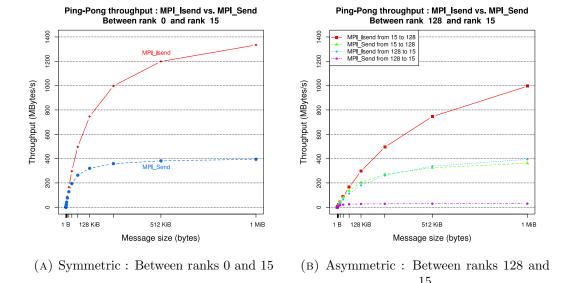

| 7.3 | Ping-pong throughput MPI_Send (PE core) vs. MPI_Isend (DMA) 80                      |

| 7.4 | Optimization approaches comparison                                                  |

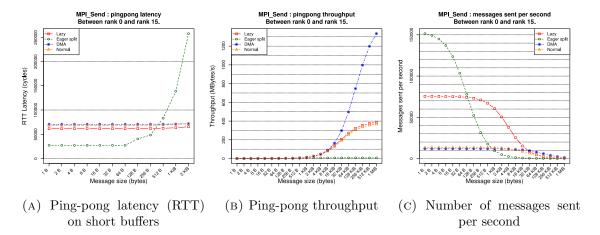

| 7.5 | HPL current performance (a) and extrapolation (b) 82                                |

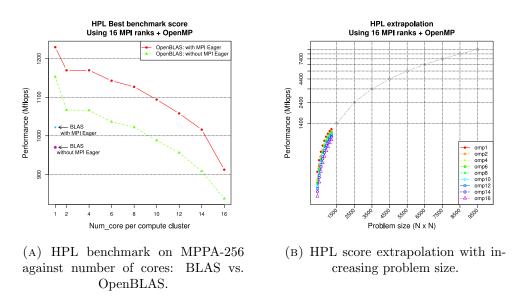

| 8.1 | Streamed-tiled GEMM algorithm                                                       |

| 8.2 | BLIS micro-kernel                                                                   |

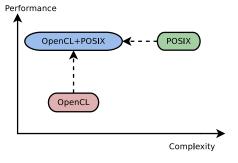

| 8.3 | OpenCL POSIX-like: motivation                                                       |

| 8.4 | OpenCL POSIX-like: execution and memory 91                                          |

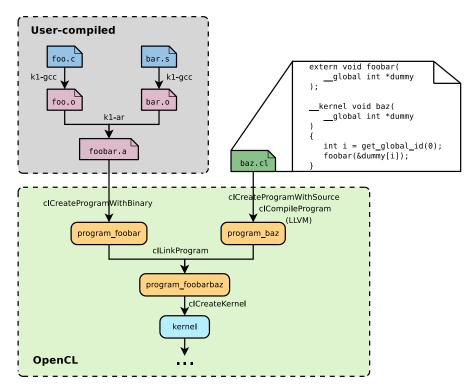

| 8.5 | clLinkProgram()                                                                     |

| 9.1 | Cache-based and DMA-based layer design of BLIS                                      |

| 9.2 | Pseudo-code of BLIS-RDMA through the five layers                                    |

| 9.3 | Illustration of a generic 2D copy                                                   |

| 9.4 | BLIS-RDMA back-end interface                                                        |

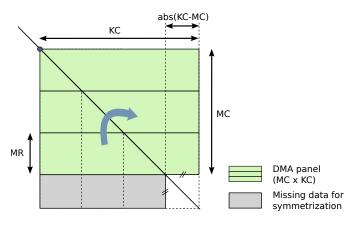

| 9.5 | DMA panel extension requirement of SYMM                                             |

| 9.6 | Performance of multi-threaded level-3 BLAS on MPPA2-256 108                         |

| 9.7 | Scalability of multi-threaded xGEMM in different shapes on MPPA2-256. 109           |

|     |                                                                                     |

## List of Tables

| 5.1 | Copied index offset and halo cutoff of a subdomain                  | 46 |

|-----|---------------------------------------------------------------------|----|

| 6.1 | Estimation of data requirement of two-wall and three-wall algorithm | 58 |

| 6.2 | Compilation flags and OpenMP context on CPU and KNL                 | 62 |

| 6.3 | OpenCL drivers and configuration on CPU and GPU                     | 65 |

| 7.1 | MPI send/receive implementation in MPIDT level                      | 74 |

| 7.2 | Transmission time (cycles)                                          | 80 |

| 8.1 | GEMM-async performance on MPPA2-256                                 | 93 |

| 9.1 | Single-threaded level-3 BLIS-RDMA SMEM footprint calculation 1      | 02 |

| 9.2 | Level-3 BLIS-RDMA configuration on MPPA2-256                        | 06 |

### Acronyms

${\bf BLAS}\;$  Basic Linear Algebra Subprograms.

**BLIS** BLAS-like Library Instantiation Software.

CPU Central Processing Unit.

**DLA** Dense Linear Algebra.

**GEMM** General matrix multiplication.

**GPU** Graphical Processing Unit.

**HPC** High Performance Computing.

**HPL** High Performance Linpack.

KNL Knights Landing.

**LAPACK** Linear Algebra PACKage.

LBM Lattice Boltzmann method.

MPI Message Passing Interface.

MPPA Massively Parallel Processor Array.

**NUMA** Non-uniform Memory Access.

OpenCL Open Computing Language.

OpenMP Open Multi-Processing.

List of Tables Acronyms

Pthreads POSIX threads.

ScaLAPACK Scalable LAPACK.

**VLIW** Very Long Instruction Word.

### Introduction

This manuscript is the fruit of a three-year PhD enduring work on optimizing scientific applications on many-core processors. This thesis is founded by the CIFRE collaboration (French term of Convention Industrielle de Formation par la Recherche – Industrial convention of research-driven training, by the French Ministry of Research and Innovation) between the Kalray corporate and the Grenoble Informatics Laboratory (LIG) from the University of Grenoble Alps (UGA) and Centre for Energy and Thermal Sciences of Lyon (CETHIL) from the National Institute of Applied Sciences of Lyon (INSA Lyon), the National Center for Scientific Research (CNRS) and the University Claude Bernard Lyon 1.

The first four chapters in this manuscript introduce the current High Performance Computing (HPC) situation, the state-of-the-art and objectives of this thesis, and the target many-core platform. Contribution chapters in this manuscript are then presented as two main parts, organized in the thematic order and not in the chronological one. The first part presents approaches in optimizing data transfer and memory footprint of the three-dimensional Lattice Boltzmann method (LBM), which belongs to the memory-bound category of applications. The second part focuses on Dense Linear Algebra (DLA) operations and associated numerical libraries, belonging to the compute-bound class. Experimental results in this document are reported on the Kalray Massively Parallel Processor Array (MPPA) many-core architecture, as well as other latest mainstream computing platforms such as NVIDIA Pascal Graphical Processing Unit (GPU), Intel Xeon Haswell Non-uniform Memory Access (NUMA) Central Processing Unit (CPU) and Intel Xeon Phi Knights Landing (KNL) processor.

Some contribution chapters in this manuscript contain principal materials from published and submitted papers, authored or co-authored by the writer of this manuscript as well. These papers are:

Minh Quan Ho, Bernard Tourancheau, Christian Obrecht, Benoît Dupont de Dinechin, and Jérôme Reybert. MPI communication on MPPA many-core NoC: design,

- modeling and performance issues. In Gerhard R. Joubert, Hugh Leather, Mark Parsons, Frans J. Peters, and Mark Sawyer, editors, *Parallel Computing: On the Road to Exascale, Proceedings of the International Conference on Parallel Computing, ParCo 2015, 1-4 September 2015, Edinburgh, Scotland, UK, volume 27 of Advances in Parallel Computing*, pages 113–122. IOS Press, 2015.

- 2. Julien Hascoët, Benoît Dupont de Dinechin, Pierre Guironnet de Massas, and Minh Quan Ho. Asynchronous one-sided communications and synchronizations for a clustered manycore processor. In Proceedings of the 15th IEEE/ACM Symposium on Embedded Systems for Real-Time Multimedia, ESTImedia 2017, Seoul, Republic of Korea, October 15 - 20, 2017, pages 51-60, 2017.

- 3. Minh Quan Ho, Christian Obrecht, Bernard Tourancheau, Benoit Dupont de Dinechin, and Julien Hascoet. Improving 3D lattice Boltzmann method stencil with asynchronous transfers on many-core processors. In 2017 IEEE 36th International Performance Computing and Communications Conference (IPCCC) (IPCCC 2017), San Diego, USA, December 2017.

- 4. Minh Quan Ho, Christian Obrecht, and Bernard Tourancheau. New parallel inplace update algorithm for better memory usage in 3D lattice Boltzmann algorithm. In submission, 2017.

- 5. Minh Quan Ho, Benoit Dupont de Dinechin, Bernard Tourancheau, and Christian Obrecht. BLIS-RDMA: A portable and high performance level-3 BLAS for DMA-based many-core architectures. In submission, 2017.

### Chapter 1

## High Performance Computing: from Single-core to Many-core

Knowledge has a beginning, but no end.

- Geeta S. Iyengar.

### 1.1 Introduction

Micro-processor architectures have made a considerable evolution since the first days of computer science. Several decades ago, when the processor clock was of the same order as the main memory speed, about hundreds of kilohertz to several megahertz, performance concerns were mostly on the computation cycles, rather than optimizing memory transfers. With advances in semiconductors, the transistor number and computing performance has exponentially increased over the years. Moore's law (Fig. 1.1) is a model of the semiconductor evolution, which depicts the increasing transistor count that doubles approximatively every 24 months for a constant circuit price. This evolution results in a parallel increase in computing power. Despite the limit in transistor size, this law has been nevertheless sustained by processor manufacturers since the last decade, by increasing the clock frequency and integrating more cores into a same silicon die.

FIGURE 1.1: Moore's law illustration at the Heinz Nixdorf Museum.

Credit: Paul Townend.

High Performance Computing (HPC) has become an essential field to guide and to be guided by the moving computing architectures. Nowadays, HPC is almost used in any scientific domain, from molecular dynamics simulation, bio-informatics, medical drug discovery, to computational fluid dynamics (CFD), oil and gas, image and signal processing, ocean simulation and weather forecast, and recently huge explosion in computing workload for astrophysics radio telescopes (Square Kilometer Array – SKA) or deep learning. Nonetheless, performance walls in exploiting parallelism are, were, and will be the main challenge to computer scientists on the road of developing future HPC systems.

### 1.2 Performance walls

### 1.2.1 Frequency-wall

The higher the clock frequency operates, the higher the performance will be. However, there is a physical limit between the clock frequency and the processor design. In synchronous circuits, there exists a maximal frequency, under which the processor still manages to synchronize its components properly with the clock signal and to maintain an operating state. Beyond that frequency, the various distance between the clock source to the working components introduces a micro-dephasing that is in the same order of a single clock rate, results in erroneous synchronization and unstable circuits. That maximal clock frequency is conventionally fixed at 10 GHz. In this case, a single clock rate is roughly the time for the light to travel three centimeters, therefore the maximum possible distance difference on an electronic circuit.

Energy consumption and power dissipation is also an issue. High-frequency working system produces heat and must be accordingly cooled down. Current leakage is proportional to the voltage and increases power consumption. World records in over-clocking end-user computers are often limited at 8 GHz. To reach this level, the system is often cooled down by liquid nitrogen. An alternative to boost performance was, instead, doubling the core count and introducing execution concurrency, which opened the era of multi-core processors.

### 1.2.2 Energy-wall

In the last years, the energy-wall has emerged as the main limiting factor in designing supercomputers. Today, we are in the age of Petascale (10<sup>15</sup> floating-point operations per second) within an energy budget of 20 MW. The first-ranked machine in the Top500 list (list of most powerful supercomputers in the world) delivers currently a power/energy ratio of about 10 GFLOPS/W. To reach Exascale (10<sup>18</sup> floating-point operations per second), predicted to appear in the 2020s (Fig. 1.2), we need a system capable to deliver more than 50 GFLOPS/W, with a global power load of less than 20 MW.

To lower power consumption and to increase flops count, the only solution is to embed a large number of low-frequency cores into a same processor, sometimes up to hundreds of cores on a same die. Such a processor would require disruptive memory and interconnection technologies to feed the core cluster. This arises the question of how to write efficient codes on those architectures, which programming model to design to expose the

FIGURE 1.2: Projected performance of the Top500 list. Source: https://www.top500.org.

massive parallelism, while ensuring ease of coding. It brings into light the challenges of many-core design and programming.

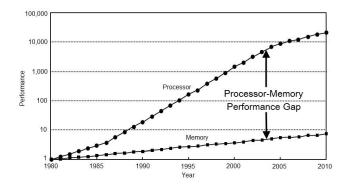

### 1.2.3 Memory-wall

There is an increasing gap between the computing performance and the memory speed. The computing performance slope is much steeper than the memory one. Since the overall performance amounts to the weakest part of the whole system, memory bandwidth turns into a bottleneck for most applications.

FIGURE 1.3: Processor-memory performance gap. Source: Computer Architecture: A Quantitative Approach

- David A. Patterson and John L. Hennessy.

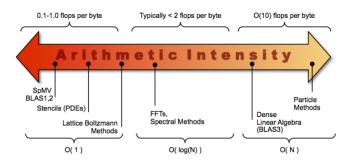

In order to better understand the former issue, we will use the concept of arithmetic intensity and the roofline model [6]. The roofline model provides an easy way to predict performance of an application or more precisely its computation kernel. The concept of arithmetic intensity (I) (ops/byte or flops/byte for floating-point) is defined by the number of arithmetic operations performed on a given quantity of data loaded. Each implementation of a numerical method possesses a proper I related to its computation workload and data access pattern. Fig. 1.4 depicts the range of arithmetic intensity of several well-known computation kernels, such as sparse and dense linear algebra (DLA), lattice Boltzmann method (LBM) and fast Fourier transform (FFT).

FIGURE 1.4: Arithmetic intensity.

Source: https://crd.lbl.gov/departments/computer-science/PAR/research/roofline/.

From the arithmetic intensity, one can assess the attainable performance P of an application on a computing system with a roofline figure (see Fig. 1.5). A roofline figure has an arithmetic intensity x-axis (flops/byte) and a performance y-axis (GFLOPS). Let  $\pi$  the peak theoretical performance of the processor,  $\beta$  the design memory bandwidth. With a given compiler and predefined optimization flags, the application produces a binary code that reaches a performance  $\pi'$ . Running a memory bandwidth benchmark on the system gives a sustained memory bandwidth  $\beta'$  ( $\pi' < \pi$  and  $\beta' < \beta$ ). The real performance P of the computation kernel is equal to  $\min(\pi', \beta' \times I)$ . When  $P = \pi'$ , the kernel is considered compute-bound since its performance does not rely on the memory but on the computing capacity of the processor, the applied compilation options, and the parallelization or vectorization method. This performance is a constant for each configuration variant (horizontal line in the roofline figure, see Fig. 1.5). When  $P = \beta' \times I$ , P follows a sloping line with a slope  $\beta'$ , where comes the name of roofline. In this case, the kernel is considered memory-bound, since its performance relies on the memory bandwidth.

Each processor architecture has its own roof lines, and every computation kernel running on that processor has a performance bounded by those two lines. This performance model, despite being simple to characterize, allows doing a rapid comparison of computation kernels on an architecture (which ones are memory-bound, which ones are

compute-bound), or comparing a specific kernel across multiple architectures (if it is memory-bound, so it should be better to use a higher memory-bandwidth system). Using the roofline model, a developer or an integration engineer can make appropriate choice to use/port their code on a specific platform, to adopt a more aggressive optimization method, or even to make architectural decisions.

FIGURE 1.5: Roofline model.

Source: https://alchetron.com/Roofline-model.

Nevertheless, the roofline model has some weaknesses. First, the performance is assessed only based on the arithmetic intensity. Secondly, data locality and memory latency are not taken into account, yet those are often crucial to the real performance in a high concurrency context. Access pattern of applications impacts the hit or miss ratio in each cache level, thus can result in unpredictable behavior of the underlying memory system (latency, throughput), due to the coherency protocol, invalidation penalties and other side-effects.

FIGURE 1.6: Different levels and latencies in memory hierarchy.

To overcome the memory latency and keep cores busy, computer architectures implement data prefetching. As can be seen in Fig. 1.6, near-core memory levels (caches or scratchpad, of the order of kilobyte and megabyte) can prefetch data either by implicit hardware mechanism or explicit built-in instructions. They were demonstrated to work efficiently on contemporary CPUs. However, when off-chip memories (DDR, NVMe

etc.) come up with supplementary physical media (NoC, PCIe), performing implicit hardware prefetching is much harder and not relevant anymore, as the memory scope is becoming too large (order of giga-byte and tera-byte). Instead, a software approach based on asynchronous RDMA communication libraries, despite requiring additional programming efforts, can improve data locality and deliver satisfactory performance.

### 1.2.4 Software-wall

Exposing parallelism while keeping the programming model simple is a hard question. NUMA CPU processors can be programmed with Open Multi-Processing (OpenMP), POSIX threads (Pthreads), Intel Threading Building Blocks (TBB) or Intel Cilk. With the rise of heterogeneous systems, programming models must evolve as well. The OpenMP 3 for shared and NUMA architecture was revised to OpenMP 4 to support target devices. OpenACC [7], CUDA and Open Computing Language (OpenCL) [8] are also other programming models and APIs for accelerators. Programming language for distributed memory has longly been dominated by Message Passing Interface (MPI) [9] with incremental features leveraging the increasing node count: from two-sided communication in MPI 1 to one-sided communication since MPI 2, non-blocking collective operation since MPI 3 as well as a re-enforced one-sided specification.

Code and performance portability is also an issue due to the hardware diversity. To reduce the programming efforts for non-computer scientists, additional tools and metalanguages were introduced: domain specific languages (DSL) like Halide [10], high-level language and automatic framework (SYCL [11]), data-flow and DAG-based (Directed Acyclic Graph) analysis tools (StarPU [12]). These high-level tools allow users to express their processing kernels and get their code automatically generated, compiled and deployed on multiple computation units.

We believe that future high performance systems will be a combination of various computing platforms. Applications (and their sub-modules), upon their arithmetic intensity range, will be deployed and run on the most suitable platform. Such a system will be highly heterogeneous and non-uniform in terms of performance and memory bandwidth of each sub-platform, where developers sometimes need to hand-tune the code to obtain the best performance, especially on embedded and non-conventional hardware. Programming and running these all-in-one systems raises considerable complexity in design, scheduling, debugging, isolation and security.

Fault tolerance will also be a big concern on large-scale systems to resist against fail-stop failures, due to the fast decline of mean time between failure (MTBF) with the growing system size. Hardware-based fault tolerance mechanisms tend to be vendor-dependent at

a certain degree. Without advances in research, these mechanisms may suffer significant overhead and would be difficult to optimize. Algorithm-Based Fault Tolerance (ABFT), since the last few years, has achieved important results by the research community [13, 14, 15, 16, 17]. However, relevance of following these approaches to the coming Exascale context is still unclear as of today.

### 1.3 Summary

In this chapter, we briefly present the high performance computing (HPC) and its main three performance walls: the frequency-wall, the energy-wall and the memory-wall. We also identify software challenges for the upcoming HPC applications, that we believe to be another obstacle to performance: the software-wall.

In the next chapter, we will introduce the first type of HPC application studied in this thesis: the lattice Boltzmann method, a stencil-based computation, known to be one of the most memory-bound applications.

## Chapter 2

# Lattice Boltzmann method (LBM)

If you can't explain it simply, you don't understand it well enough.

– Albert Einstein.

### 2.1 Background

### 2.1.1 Theory

Inspired from the lattice gas automata theory [18] and first introduced by McNamara and Zanetti [19], the lattice Boltzmann method has become widely used in computational fluid dynamics (CFD) as an alternative to the solving of Navier–Stokes equations. Belonging to the structured grid-based discrete method, the LBM is known for its advantages such as straightforward meshing, ability to model complex geometries, and most of all its inherent parallelism, well-suited to massively parallel computing architectures.

An LBM model is characterized by a stencil type, denoted  $\mathrm{D}d\mathrm{Q}q$ , where d is the number of space dimensions (one, two or three) and q is the number of particle distribution functions (PDFs) [20]. Particle distribution functions describe the interaction between a lattice node and its surrounding neighborhood. More precisely, q relates to the number of neighboring nodes that will be involved into interaction with the lattice node of interest. In most cases, the node itself is taken into account and the number of neighboring nodes equals q-1. The most used stencil types for LBM are D2Q5 and D2Q9 for two-dimensional domains, or D3Q19 and D3Q27 for three-dimensional domains (see Fig. 2.1).

FIGURE 2.1: LBM D3Q19 stencil.

Three-dimensional LBM often operates on D3Q19 or D3Q27 stencils. The LBM spatial domain is represented by a grid of nodes, discretized with a mesh size  $\delta x$ . The simulation duration is discretized in constant time steps  $\delta t$ . The LBM updating rule for each node at each time step is defined by the following equation:

$$|f_i(\mathbf{x} + \delta t \boldsymbol{\xi}_i, t + \delta t)\rangle - |f_i(\mathbf{x}, t)\rangle = \Omega |f_i(\mathbf{x}, t)\rangle$$

(2.1)

in which  $\Omega$  is a pre-defined *collision operator*. The collision operator implements the time evolution of particle distribution functions  $f_i$  ( $i \in \{0,...,q-1\}$ ) of a given node

towards its nearest neighbors with respect to the  $\xi_i$  velocities. For better presentation in LBM codes, Eq. 2.1 is often split into two sub-steps:

$$|f_i^*(\boldsymbol{x}, t + \delta t)\rangle = |f_i(\boldsymbol{x}, t)\rangle + \Omega|f_i(\boldsymbol{x}, t)\rangle$$

(2.2)

$$|f_i(\mathbf{x} + \delta t \boldsymbol{\xi}_i, t + \delta t)\rangle = |f_i^*(\mathbf{x}, t + \delta t)\rangle$$

(2.3)

in which, Eq. 2.2 applies the  $\Omega$  operator to the current state  $|f_i(\boldsymbol{x},t)\rangle$  – a ket vector containing q PDFs of the lattice node. This reduces to local computations (also known as *collision* step), translated into floating-point arithmetic operations. Results of this sub-step are new PDFs of the next time step  $|f_i^*(\boldsymbol{x},t+\delta t)\rangle$ , which temporarily remain within the local node. Eq. 2.3 then streams these PDFs into neighboring nodes (also known as *streaming* step), with the notation of spatial directions  $\boldsymbol{x} + \delta t \boldsymbol{\xi}_i$ . This sub-step is translated into memory load/store instructions.

### 2.1.2 Memory requirement

At each time step, the whole spatial domain must be updated before being able to start the next iteration. This spatio-temporal dependency of the LBM (shared by other stencil numerical schemes) compels developers, for the sake of code simplicity, to allocate two instances of the computational array, one as input of Eq. 2.2 (read-only) and one as output of Eq. 2.3 (write-only). This technique is usually known as two-lattice [21] (see the next section), whose the main drawback is the doubled memory consumption which significantly reduces the maximal reachable spatial resolution. It requires scientists to run their code on more machines with a larger aggregate memory space, thus resulting in larger cost and energy consumption.

From a programming point of view, LBM kernels are easy to implement and well-suited for parallelization on recent multi-/many-core platforms. However, lattice Boltzmann methods are known for their low arithmetic intensity and particularly high memory bandwidth requirement. Taking the example of a basic LBM solver, depending on collision operator, between 200 and 400 floating-point operations are performed on a lattice node per time step. Most D3Q19 LBM implementations require storing all the 19 distribution values for each lattice node. A lattice domain  $L \times L \times L$  contains  $19 \times L^3$  single- or double-precision floating-point numbers. Updating this lattice grid in a single time-step requires  $19 \times 2 \times L^3$  load/store memory operations for less than  $400 \times L^3$  arithmetic operations. Thus, simulating the whole lattice domain through T time-steps will generate a huge amount of data movement of  $19 \times 2 \times L^3 \times T$  floating-point numbers for  $400 \times L^3 \times T$  floating-point operations. Fig. 2.2 illustrates the memory-bound aspect of a D3Q19 LBM model.

FIGURE 2.2: D3Q19 LBM applied on MPPA2 roofline model.

While recent architectures gain computing performance by increasing the clock speed and multiplying the number of cores, evolution of memory systems still cannot fetch enough data to keep cores busy. The dataset cannot always fit in caches and must be stored in the main (even remote) memory with much higher latency. The low arithmetic intensity of stencil kernels like LBM is thus the limit of performance, as well as their poor data-locality which reduces significantly the cache-reuse ratio. Previous studies in [22] and [23] show that LBM implementations are memory-bound and hardly obtain good performance on CPU or Xeon Phi processors. GPU-based accelerators, thanks to their graphics-dedicated high-bandwidth memory, appear to be the most suitable platforms for LBM today.

### 2.2 Propagation algorithms

### 2.2.1 One-step two-lattice (OT)

One-step two-lattice (also known as two-lattice) is the most employed algorithm in LBM implementations on massively parallel architectures. The collision and streaming steps are fused into one compute kernel, either in pull or push scheme (see Fig. 2.3). This kernel loops on all lattice nodes and updates the whole domain at each time step. The two lattice arrays (A and B) which are swapped at the end of each time step, differ from each other by their access type within the compute kernel: one is read-only and one is write-only. Using non-temporal streaming store to perform the write operation in the streaming step is thus a good reason to use this algorithm. But this feature is not widely available on all architectures, due to its hardware cost.

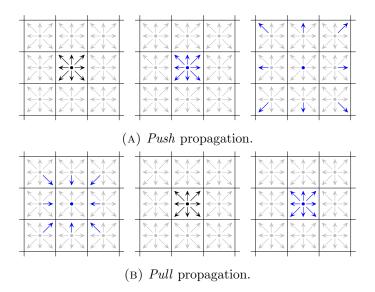

FIGURE 2.3: Propagation schemes of LBM in the D2Q9 sketch.

### 2.2.2 One-step one-lattice (OO)

Different approaches, known as *one-lattice* algorithms, were introduced to reduce the memory footprint by working on only one lattice array and to improve data locality of the LBM. Most of them operate elaborate exchange of PDFs between neighboring lattice nodes in the parallel execution context.

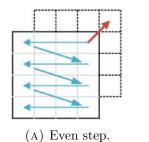

Pohl et al. [24] proposed compressed-grid (also known as shift, see Fig. 2.4) approach to reduce the memory requirement of the two-lattice algorithm. With the same objective, Mattila et al. [25] developed a swap algorithm that requires almost half of memory space compared to the two-lattice algorithm. Comparisons of these algorithms with varying lattice-indexing and data layouts were carried out in [26, 27]. These studies show equivalent computational efficiency of compressed-grid and swap algorithm compared to the two-lattice approach, while consuming less memory. However, these two approaches both require definite iteration order and complex index calculations for shifting the two lattice grids (shift) or swapping distribution values between neighbors (swap). These dependencies make it very hard to implement shift and swap algorithms on highly parallel GPUs and accelerators in offloading mode (CUDA, OpenCL). Today, they are implemented only as sequential CPU code inside a subdomain and are scaled up by using MPI for inter-domain halo exchange [27]. This configuration yields satisfactory weak-scaling but cannot enable strong-scaling, since execution of each shared-memory subdomain cannot be parallelized by either OpenMP or Pthreads.

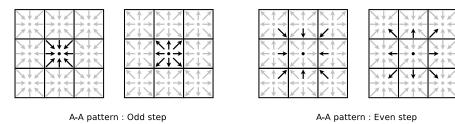

Bailey et al. [28] presented the AA-pattern which overwrites read input PDFs by new collided data via two different kernels (even and odd time steps) (see Fig. 2.5). Geier and Schönherr [29] introduced Esoteric twist (shortened to Esotwist) as an improvement of

Figure 2.4: Compressed-grid (shift) propagation algorithm. Source: Wittmann et al. [27].

AA-pattern, by interacting only with neighboring nodes in positive xyz-direction. These two later algorithms work on one lattice array, are inherently asynchronous and thus are attractive for GPU and similar parallel architectures. However, they are more complex to implement than other algorithms mentioned above. Compressed-grid, AA-pattern and Esotwist need two kernels for even and odd time steps respectively. Esotwist can be implemented with one kernel, but requires imperatively the SoA (structure of arrays) storage layout to swap the Q pointers to their opposite direction after each collision, thus mostly only interesting for GPU architectures.

FIGURE 2.5: D2Q9 version of AA-pattern with two kernels at odd and even time steps. The odd step reads local PDFs in their opposite order, collides and stores back locally in natural order. The even step performs reads of PDFs from neighboring nodes (pull), collides and writes back (push) to the same place on these nodes, with opposite PDFs.

### 2.3 Summary

The lattice Boltzmann method is one of the most memory-bound applications among other iterative stencil-based methods, such as image processing and computer vision. Improving LBM performance lies on optimizing data-locality for better utilization of cache memories, as well as reducing the global memory footprint by inventing new implementation methods.

The fundamental challenge of any *one-lattice* algorithm is that memory accesses (read and write) must be performed carefully on the same lattice buffer to enforce the spatio-temporal dependency between nodes and time steps. More over, implementation often

requires two versions of kernel code, adding more programming effort and reducing the maintainability of the application. On another hand, LBM boundary conditions on new physical models tend to be more and more elaborate. Typical LBM boundary conditions, such as simple bounce-back or interpolated bounce-back [30], imposes specific exchange rules of PDFs between adjacent nodes. Combining these conditions with existing *one-lattice* algorithms raises considerable complexity in implementation and validation, especially for 3D domains.

Other clustered many-core processors, despite a much lower global memory bandwidth with respect to GPUs, embed significant amount of fast local memories [31, 32]. They also provide more predictability in both computing time and data transfer. This enables using explicit and efficient user buffers for elaborate optimizations, such as software prefetching and streaming, based on local memories and asynchronous DMA engines.

### Chapter 3

## Basic Linear Algebra Subprograms (BLAS)

Today, most software exists, not to solve a problem, but to interface with other software.

– I. O. Angell.

## 3.1 Background

#### 3.1.1 Introduction

Since its first release in the 1980s, the Basic Linear Algebra Subprograms (BLAS) [33, 34] has been widely used as the *de facto* foundation of high-level dense linear algebra libraries such as Linear Algebra PACKage (LAPACK) [35] and Scalable LAPACK (ScaLA-PACK) [36], as well as in many inter-disciplinary scientific software. BLAS was designed to provide an unified and portable interface of numerical linear algebra operations on various computer architectures. Along other must-have software tools and libraries, BLAS is the first numerical API to be implemented and optimized on any architecture that targets high-performance computing.

The BLAS API <sup>1</sup> defines three levels of numerical operations: (1) level-1 within or between scalar vectors, (2) level-2 between vector and matrix, and (3) level-3 between matrix and matrix. A typical example of a level-1 operation is the vector-vector addition (AXPY) (equivalent Triad in the STREAM benchmark [37]). The level-2 performs, for instance, vector-matrix multiplication (GEMV), or the well-known solver of linear system of equations  $A \cdot x = b$  (TRSV). For level-3, one should mention the General matrix multiplication (GEMM) operation  $C \leftarrow \alpha \cdot A \cdot B + \beta \cdot C$ , which is used as the core block of many computation-intensive benchmarks and applications. The High Performance Linpack (HPL) benchmark [38, 39] from which the Top500 list is built, as well as many other scientific applications are designed to map on this operation as much as possible to reach the maximal computing capacity of the target platform. In the latest years, GEMM has also become the kingpin of machine learning and deep learning advances.

Nevertheless, implementing and optimizing BLAS (typically level-3) on a given architecture has never been a trivial task. Straightforward implementations seldom deliver satisfying performance without advanced tiling and blocking techniques. To fill up the core pipeline, eliminate stall cycles and reach near-peak performance, developers compulsorily need to understand the low-level functionality of the hardware and write optimal assembly-level kernels. Multiplicity of BLAS parameters and their combinatorial cases yield up to several hundreds of assembly kernels to hand-tune and to maintain; in which to add extensions of instruction set architecture (ISA) and cache size evolution throughout processor generations. Developing and maintaining such an optimal library requires substantial time and expertise, that sometimes can only be afforded by the processor manufacturers or specialized research groups.

http://www.netlib.org/blas/blasqr.pdf

Conventional CPUs are shipped with proprietary libraries that implement BLAS, sparse BLAS routines, and BLAS-like extensions, such as: Intel Math Kernel Library (MKL) [40], AMD Core Math Library (ACML) [41] and IBM Engineering and Scientific Subroutine Library (ESSL) [42]. Open-source options for BLAS-like functionality include the hand-optimized GotoBLAS [43] [44] and its derivative OpenBLAS [45], auto-tuning solution such as Automatically Tuned Linear Algebra Software (ATLAS) [46], and projects that target modern multi-core processors such as Parallel Linear Algebra Software for Multicore Architectures (PLASMA) [47]. The BLAS-like Library Instantiation Software (BLIS) framework [48] is a recent development in the area of open-source and portable BLAS solutions for CPU-based architectures.

Vendors of GPU and other CPU accelerators also develop proprietary BLAS implementations adapted to their heterogeneous computing context: NVIDIA's CuBLAS [49], AMD's clBLAS[50] and rocBLAS [51]. Open-source projects for such architectures include MAGMA [52], clBLAST [53], and KAUST-BLAS [54]. These libraries, written in C-like languages (CUDA, OpenCL), rely on the vendor compiler and runtime API to generate executable code and offload computation onto the device. In order to abstract the hardware complexity and reduce programming effort, scheduling and memory management is hidden as much as possible to the developer and is managed by the deployment runtime and the device driver. Despite facilitating usage by non-expert users, the application portability and performance crucially depends on the vendor's or the open-source community's ability to implement and maintain an optimized BLAS library across multiple architectural generations.

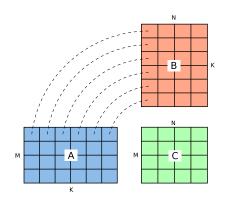

#### 3.1.2 General Matrix Multiplication (GEMM)

#### 3.1.2.1 Basic implementation

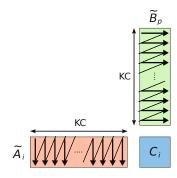

The GEMM operation is the most widely used function in the BLAS API. Fig. 3.1 depicts the GEMM function which performs matrix product between a matrix A of size  $m \times k$  and a matrix B of size  $k \times n$ . This product is then scaled by an  $\alpha$  scalar and is accumulated into a matrix C of size  $m \times n$ , pre-scaled by a  $\beta$  scalar:  $C \leftarrow \alpha \cdot A \cdot B + \beta \cdot C$ .

Let us assume that matrices are square (m = n = k). The basic implementation of GEMM is based on

Figure 3.1: Matrix multiplication.

the following the loop-based approach:

$$C_{i,j} = \alpha \times \left(\sum_{t=0}^{n-1} A_{i,t} \times B_{t,j}\right) + \beta \times C_{i,j} \qquad i, j, t \in [0, n)$$

(3.1)

Eq. 3.1 performs, per each  $C_{i,j}$  element, 2n + 2 floating-point operations (flops),<sup>2</sup> for a data traffic of 2n + 2 words.<sup>3</sup> Commonly, those floating-point operations can be performed within n+1 fused multiply-add (FMA) instructions.<sup>4</sup> This naive implementation has a poor arithmetic intensity. Spatial and temporal locality of data accesses in cache levels are not optimal either.

#### 3.1.2.2 Blocked (Tiled) implementation

Goto et al. [43] revisited GEMM algorithms with multi-layer blocking (or tiling), in which each layer is corresponding to a memory level. For simplicity, let consider a two-layer configuration between a slow memory (DDR) and a fast memory (scratchpad or L1 cache). The matrix C on the slow memory is divided into  $N \times N$  blocks, each block is of size  $b \times b$  ( $N = \frac{n}{b}$ ). The blocksize b is chosen so that the fast memory, whose size is S, can hold at least one block A and one block B ( $S \ge 2b^2$  words), or preferably one block C as well ( $S \ge 3b^2$  words). Let consider that three blocks A, B and C can fit into S, the communication cost between the slow and fast memory, the I/O traffic and arithmetic intensity (AI) of the blocked algorithm are written as follows:

$$I/O \ traffic = N^2b^2 \times N \quad (\text{read every block of A } (N) \text{ times})$$

$$+ N^2b^2 \times N \quad (\text{read every block of B } (N) \text{ times})$$

$$+ 2N^2b^2 \times 1 \quad (\text{read and write every block of C once})$$

$$= 2N^3b^2 + 2N^2b^2 = \frac{2n^3}{b} + 2n^2 = 2n^3\left(\frac{1}{b} + \frac{1}{n}\right)$$

$Complexity = 2n^3$

$$AI = \frac{Complexity}{I/O \ traffic} = \frac{nb}{n+b} = \frac{b}{1+\frac{b}{n}} \approx b \quad (n \gg b)$$

(3.2)

$<sup>^{2}</sup>n + 2$  multiplications and n additions

$<sup>^{3}2</sup>n$  loads for  $A_{i,t}$  and  $B_{t,j}$ , one load and one store for  $C_{i,j}$

<sup>&</sup>lt;sup>4</sup>Included in the IEEE 754-2008 standard and largely available on modern CPU and GPU architectures. The FMA instruction has advantage of significantly reducing the number of CPU cycles and minimizing the accumulated error due to successive rounding steps.

As can be seen from Eq. 3.2, we can improve performance of the blocked algorithm between two successive memory levels by increasing b. Applying recursive tiling on contemporary CPU and GPU architectures is apparently the optimal approach for GEMM. Furthermore, Goto et al. [43] also proposed an additional packing step before inner computations, which consists in reordering A and B data blocks into a pre-defined contiguous layout, in order to maximize cache hit ratio and minimize penalty of Translation Lookaside Buffer (TLB) misses. Through the packing step, the implementation will also be able to handle multiple parameter combinations (transa, transb, uplo, sidea etc.) with only several well-defined inner micro-kernels. This allows implementing BLAS functions without tuning hundreds of assembly kernels, produces well-structured and highly maintainable code, whose a successful example is the BLIS framework.

# 3.2 BLAS-like Library Instantiation Software (BLIS)

BLIS, stands for *BLAS-like Library Instantiation Software* [48], is a sub-project of libflame [55]. The libflame project implements LAPACK-like features and lies closely on BLIS for the BLAS support. Both BLIS and libflame are developed by the Science of High-Performance Computing (SHPC) group at the University of Texas at Austin. They are released under the open-source BSD 3-clause license, facilitating adoption by industry.

During many years, the research community was missing a well-structured, open-source, light-weight, portable and high performance BLAS library. Proprietary implementations are considered as black-boxes and platform-specific. Open-source libraries like ATLAS and OpenBLAS appear too bloated or difficult to port and to optimize on a new architecture. Researchers and vendors need an easy and extensible framework as an experimental tool, not only to implement and tune new linear algebra algorithms, but also to maintain and optimize easily BLAS functions on next-generation architectures. These crucial points have been tackled and successfully solved within the BLIS framework for conventional cache-based CPUs.

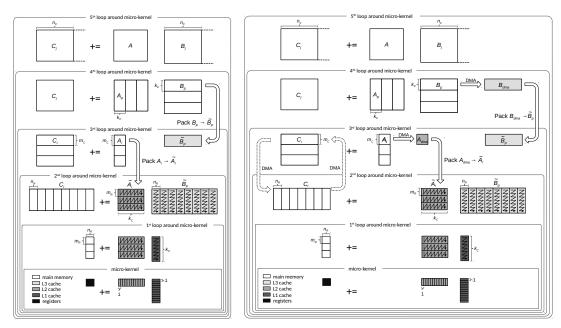

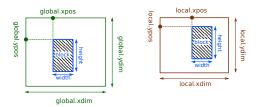

Inspired from GotoBLAS [43], BLIS is designed with fundamental principles in dense linear algebra, including incremental and recursive construction of BLAS operations for code-reusability, data-packing and cache/register blocking for optimal locality, as well as ability to integrate platform-specific assembly code. Fig. 3.2 depicts the global algorithm of the GEMM operation in BLIS. The three matrices A, B and C are partitioned and traversed through five loops around a *micro-kernel*. The micro-kernel performs a

$<sup>^{5}</sup>$ This layout is similar to the row-major GEMM\_TN format: A transposed and B non-transposed.

FIGURE 3.2: Cache-based layer design of BLIS. Courtesy of: Field G. Van Zee and Robert A. Van de Geijn.

rank-k update and constitutes the sixth loop. Other level-3 operations are then built on top of GEMM and this partioning method.

Main advantages of BLIS can be mentioned as follow:

- BLIS introduces a reduced set of micro-kernels (gemm, trsm, gemmtrsm), written in the portable C99 standard by default, as a reference implementation.

- BLIS defines a reduced set of execution parameters (cache sizes, memory alignment, memory allocator), largely used by the internal algorithms, but can differ significantly from one architecture to another.

- BLIS provides a user-defined configuration header which allows arbitrary modification of these execution parameters and easy plug-and-play of ISA-specific micro-kernels to generate a nearly optimized BLAS library on any cache-based architecture, without touching the core functions of BLIS.

This abstract design enables a custom fit on any cache-based system implementing any instruction set with straightforward portability and high-performance. Cache-blocking and packing implementation techniques in BLIS have been proved to be analytically optimal [56] on multi-core and NUMA memory hierarchies, delivering competitive performance to other vendor libraries [57].

## 3.3 Summary

New multi- and many-core architectures keep appearing and are moving fast. On these systems, writing library and software are becoming more and more challenging. Moreover, code-portability sometimes counters performance, due to the hardware diversity. The BLIS framework has emerged as a promising solution for instantiating a light-weight and high-performance BLAS library for *cache-based* architectures.

However, both HPC design strategy and modern embedded and intelligent computing are coming up with more and more power-efficient and non-conventional architectures, on which, writing a BLAS library in pace with the hardware represents a big software challenge. They often do not have a hardware-assisted cache coherency, whereas a software-based cache protocol would suffer significant overhead. Hardware prefetcher, out-of-order execution and advanced branch prediction are commonly discarded to reduce power consumption (and fortunately avoid security vulnerabilities <sup>6</sup>).

On those architectures, computation-intensive parts of code are expected to perform software-managed data-prefetching, by leveraging Direct Memory Access (DMA) engines and operating on scratchpad memories, instead of the traditional cache-based load/store scheme. Support of the asynchronous programming model based on Remote-DMA (RDMA), considered the key enabler of performance on DMA-based architectures, is currently the missing point of any BLAS-like library on these later platforms.

<sup>&</sup>lt;sup>6</sup>https://meltdownattack.com/

# Chapter 4

# Kalray Massively Parallel Processor Array (MPPA)

Any sufficiently advanced technology is indistinguishable from magic. – Arthur C. Clarke.

### 4.1 Introduction

#### 4.1.1 Company

Kalray is a fabless semiconductor company, founded in France in 2008 after a spin-off from the CEA (French Alternative Energies and Atomic Energy Commission). Kalray is specialized and pioneering in developing a new family of many-core processors, namely Massively Parallel Processor Array (MPPA). The MPPA architecture offers unique parallel computing capacity, low latency and low-power consumption. The Very Long Instruction Word (VLIW) core architecture, distributed non-coherent memory system and dual control-plane and data-plane Network-on-chip enable time-predictability necessary to embedded, mixed-critical and real-time systems. The MPPA massively parallel architecture is also suitable for modern and energy-efficient HPC workloads, typically in the area of image processing, computer vision and autonomous vehicles.

#### 4.1.2 MPPA architecture overview

The second generation of Kalray MPPA-256 processor, codenamed Bostan (see Fig. 4.1) embeds 256 VLIW compute cores grouped into 16 compute clusters (CC) and 16 system cores in two unified I/O subsystems (IOS). The sixteen compute clusters are organized in a 4 x 4 grid connected by a 2D torus Network-on-Chip (NoC). The processor delivers peak performance of 634 GFLOPS in single precision and 317 GFLOPS in double precision at a frequency 600 MHz, within a power consumption of 20 W.

FIGURE 4.1: MPPA2-256 processor overview. (Source: Kalray).