本書では、小さなOSをゼロから少しずつ作っていきます。 OSと聞くと腰が引けるかもしれませんが、OS (特にカーネル) の基本機能は案外単純です。巨大なオープンソースソフトウェアとしてよく挙げられるLinuxでさえ、バージョン0.01はたった8413行でした。様々な要求に応えるために次第に肥大化していっただけで、当初は大変素朴な実装になっていました。 本書では素朴なコンテキストスイッチ、ページング、ユーザーモード、コマンドラインシェル、ディスクデバイスドライバ、ファイルの読み書きをC言語で実装します。これだけ様々な機能が詰め込まれているのに、コードは合計でたった1000行未満です。 「1000行なら1日でできそう」と思うかもしれませんが、初学者には少なくとも3日はかかるでしょう。OS自作のハマりポイントは「デバッグ」です。アプリケーション開発とは違うデバッグ手法・能力を習得する必要がありま

絞り込み

-

検索対象

-

ブックマーク数

-

期間

-

セーフサーチ

risc-vの検索結果1 - 40 件 / 199件

-

クレイジーピエロ 著 無から始める自作CPU CPUは作れる!!!!!!!!ご存知でしたか!!!?????? CPU、それは我々が暮らす情報社会の基盤となる魔法の石です。 世に存在する全てのソフトウェア、例えばゲーム、AI、Webサーバ、OS、これらは全てCPUが無ければ動きませんし、今や車や飛行機、家電にも全てCPUが入っている時代です。 そんな誰もがCPUに依存している時代にも関わらず、CPUについて理解を持っている人間は余りにも僅か、というのが現状です。 そんな今こそCPUを作りましょう。 CPUを作り、完全に理解する事で、CPUによって成り立つ技術を学ぶ上での、揺るぎない自信と確証を身につける事が出来るでしょう。 本記事ではCPUという究極のブラックボックスに光を当て、半導体やプログラミングの知識が無の状態から、CPUを作る事を目標としています。 必要な物 本記事の内容の99%はW

-

私が所属する東京大学理学部情報科学科では三年の冬学期に CPU 実験という実験授業が開講されています。本稿ではその簡単な説明をした後、その実験の一環として約一ヶ月ほど取り組んだ「Linux が動作する RISC-V CPU を自作するプロジェクト」で何をしたか、またどのような成果を得たかについて紹介したいと思います。 本稿を読むその前に 弊学科では「XX 年度に教養学部から理学部情報科学科に進学してきた学生」を「XXer」と呼ぶ文化があります。本稿ではこの表現を断りなく用います1。また私は普段 Web が好きでもっぱら Web セキュリティに関することを追いかけているだけのしがない学部 3 年生なので (私についての情報は ここ に大体まとまっています)、こういう低いレイヤのことは未だによく分かっていません。あくまで素人の記事だとご理解いただけると嬉しいです。誤りの指摘や質問があれば、ここ

-

「RISC-V」という言葉が徐々にエンジニア界隈に普及し始め、技術界隈のニュースサイトだけでなく、一般的なニュースを扱うような新聞社の記事でも見かけるようになってきました。例えば以下のような記事です。 www.nikkei.com 半導体エンジニアではない人がこのような記事を書く場合、「設計IP」について正しい知識を持っておかないと、少しおかしなことになってしまいます。しかしこれは記事を書いている記者だけを責めることは出来ません。半導体設計業界はソフトウェア開発業界に比べて小さな業界で、プレーヤの数も少なく、ネット上にあまり情報も出てきません。時事ネタを速攻で記事に起こさないといけない新聞記者が「IPってなんだっけ?」「リスクファイブってなんぞや?」ということをいちいち厳密に調べてられない、ということも理解できます。 そこで、非エンジニア(というか非半導体産業の方)でも理解できるように、R

-

第3回: ローエンドにもRISC-Vが!ダイソーの完全ワイヤレスイヤホンを分解してみよう:ThousanDIYの「ガジェット分解ライフ」:エンジニアライフ

- 224 users

- el.jibun.atmarkit.co.jp

- 暮らし

- 2022/02/01

こんにちは。「100円ショップのガジェット」を中心に電子機器を色々と分解をしているThousanDIYです。 このコラムでは、ガジェットを分解する中での発見や感想をつらつらと書いていきます。 ※タイトルに誤解を生みそうな表現があったので修正しました。(2/2 14:00) Bluetooth接続で左右が独立した「TWS(True Wireless Stereo)イヤホン」、AppleやSonyという大手メーカーから数万円で販売されている高級品というイメージがあったのですが、2021年の春ころから日本国内ではTWSイヤホンの低価格化が一気に進みました。最近ではドラッグストアやコンビニエンスストア、ショッピングセンターにある雑貨店やディスカウントショップでも数千円の製品を普通に見かけるようになりました。 第3回は、そんな「低価格TWSイヤホン」の代表格である、ダイソーの1,100円「完全ワイヤ

-

RISC-Vが面白くなってきたぞ

- 213 users

- zenn.dev/tetsu_koba

- テクノロジー

- 2023/01/06

(雑に書いている戯言であることを最初に断っておきます。あくまで個人の感想です。) 実は私は今までRISC-Vには懐疑的だったのですが、最近の状況を知って考えを改めました。 RISC-Vとは RISC-V(リスク ファイブ)とはオープンソースライセンスで提供されている命令セットアーキテクチャ (ISA)です。 研究にも使うことができるし、実際に多くの半導体メーカーがこの仕様に基づいたCPUを開発、出荷しています。 多くのオープンソースのOSやツールチェインもすでにRISC-Vに対応しています。 私が懐疑的だった理由 RISC-Vはオープンソースであるゆえ、自由に拡張することができます。そのため様々な派製品が登場しています。シンプルな組み込み用のマイクロコントローラからパソコン用、サーバ用、HPC用など広い分野に渡ります。 かつてRISCの考え方にもとづいて開発されたMIPSというCPUがあり

-

現代のコンピューターのほとんどがx86やARMといったクローズドなアーキテクチャを採用する中で、プロセッサ業界に革新をもたらす鍵として注目されているのが、オープンソースの命令セット・RISC-Vです。そんなRISC-Vを搭載し、Linuxの動作にも対応した119ドル(約1万2400円)のコンピューターボード「BeagleV」が発表されました。 BeagleV https://beagleboard.org/static/beagleV/beagleV.html x86やARMはプロセッサのアーキテクチャとして多くのシェアを勝ち取っていますが、利用するためには高額なライセンス料を支払う必要があり、プロセッサ市場への新規事業者の参入障壁となる点などが問題視されてきました。オープンソースのRISC-Vは誰でも無料で利用できるため、普及すれば他業界や研究機関によるプロセッサ開発の垣根を下げ、安価な

-

はじめに 環境の用意 ブートプログラムを作る 動かしてみる コンパイル QEMU上で起動 GDBで制御 最後に おまけ 執筆者 : 高橋 浩和 ※ 「RISC-V OSを作ろう」連載記事一覧はこちら ※ 「RISC-V OS」のコードはgithubにて公開しています。 はじめに RISC-VはMIPSアーキテクチャの流れを汲む正統派?のRISC CPUです。命令セットはシンプルですが、既存のメジャーなCPUのアーキテクチャと大きな違いがあるわけではありません。 Linux上で利用できるRISC-Vツール群も揃ってきたので、それらを使ってRISC-V用の小さなOSを実装してみようと思います。 最初は欲張らずに単純な実装を目指すことにします。 シングルコアのみサポート 64bitモードを使用 マルチタスキングを実現 タイムシェアリングスケジューリングを実装 割り込みネストは無し 保護機能は使わ

-

2020年以降に爆発的に増えているRISC-Vコアの数。ただし、2025年までに600億個というSemico Researchが出した本資料の数字はさすがに無茶な推定だとは思う 米中貿易摩擦の結果、中国の半導体企業がRISC-Vに傾注 2016年後半あたりから、RISC-V FoundationのFoundation Memberは相次いでRISC-Vのコアの開発やRISC-V向けのソフトウェアなどの開発を手がけているが、先にRISC-Vに傾倒し始めたのは中国であった。 中国と米国は2015年頃から不協和音が出ていた。ただオバマ政権時はあまり強硬な手段を取らなかったこともあり、それほど大きな問題にはならなかった。しかし、2017年にトランプ政権に変わり、デカップリング政策を取ったことで急速に関係が悪化する。 BIS(米商務省産業安全保障局)は、特定技術を利用した製品の輸出や移転をする際に認

-

最近x86とArmに続く第3の勢力として、RISC-V(リスクファイブ)の名前を聞くことが多くなった。RISC-Vの場合、x86とArmと異なるのはさまざまなベンダーがさまざまなコアを用意していることで、まだ現状はIPを販売しているレベルの企業の方が多いが、チップの提供を開始しているメーカーも出始めている。 イメージとしては、1980年代末~90年代のx86市場を考えれば良い。インテルとAMD以外にCyrix/IDT/TI/IBM/NexGenなど多数のメーカーが、独自の実装に基づくx86プロセッサーを市場投入していた時代に近い。 もちろんいろいろ異なる点もあるのだが、2010年代前半はプロセッサーといえばx86とArm、それにPowerPC/POWERといった程度がせいぜいだったのに、なぜ2010年代後半から急速にRISC-Vが盛り上がったのか、という一連の流れを数回に分けて説明しよう。

-

PC向けCPUの主流な命令セットアーキテクチャであるx86は、Intel 8086プロセッサに起源を持ち、46年の長きにわたって使われてきました。そんなx86は近い未来に滅んでしまうだろうと、技術系ブログのHackadayが主張しています。 Why X86 Needs To Die | Hackaday https://hackaday.com/2024/03/21/why-x86-needs-to-die/ x86を採用する現代のCPUは、複雑な命令セットコンピューターであるCISC、1クロックサイクルあたり複数の命令を実行可能な「スーパースカラー」、命令を高速化するため順序を変更して実行する「アウト・オブ・オーダー実行」、分岐先の命令を条件が満たされるか不明な状態で実行する「投機的実行」を特徴とする、フォン・ノイマン型アーキテクチャの一部分です。x86はもともとは16bitプロセッサで

-

秋月電子さんに新商品のマイコンが入荷したようです。1個40円の32ビットRISC-Vマイコン CH32V003J4M6 [通販コード:118062]です。あまりの安さとSOP8の可愛さで気になってしまいます。開発環境は公式のものもあるのですが、Arduino IDEもサポートしているようです。今回はお手軽なArduino IDEでセットアップをしてみます。 他にも1個50円のCH32V003F4P6 [通販コード:118061]もあり、こちらはピン数も多く高機能のようですが、まずはSOP8で扱いやすそうなCH32V003J4M6で試してみます。マイコンに書き込むためのツールのWCH-LinkEエミュレータ [通販コード:118065]も販売されていましたのでこちらも購入しました。 マイコンで簡単な回路を作ってみる CH32V003J4M6はSOP8なのでピン間隔も1.27mmと広く表面実装

-

今回は、高専5年次から趣味で学習していたRISC-Vを実装した、簡単なCPU作成をしていこうと思います。 完全に知識ゼロの状態から学び始めたので、間違った解釈をしている部分があるかもしれませんが、その時は優しく指摘していただけると嬉しいです 🙏 また、本ブログはディジタル回路設計とコンピュータアーキテクチャ[RISC-V版]を基に書かれています。初心者でも理解しやすいように丁寧に解説されているので、興味があれば是非買ってみてください! RISC-Vってなんぞ RISC-V公式サイトには以下のように書かれています。 RISC-V is an open standard Instruction Set Architecture (ISA) enabling a new era of processor innovation through open collaboration. (RISC-

-

低レイヤを知りたい人のためのCコンパイラ作成入門 まさに低レイヤのことが分かっておらず、以前から気になっていたこの本。取り掛かってみたところ思いのほかスイスイ進められて、勢いに乗ってセルフホスト(自分が書いたコンパイラで自分自身をコンパイルするところ)までいけたので記念に書いておく。正確には C コンパイラのサブセットです。 GitHub - motemen/mocc 全体的な進め方は、 上記の本の通りに進めていく。 それ以降は自作の 8queen が普通に書けるように機能を強化。 それ以降はセルフホストを目標に進める。 プリプロセッサやリンカは作らず、C からアセンブリまで。 という感じ。自分は手を動かさないと進んでる気がしないので、まずは書いてみつつわからない所があれば調べる、というスタンスでいく。 あと、せっかくなので RISC-V の勉強もしたかったのでこれ向けに書く。なので実行は

-

Java 19が正式リリース。より軽量な仮想スレッド、RISC-Vへの移植など新機能。1年後のJava 21が次のLTS版に

- 115 users

- www.publickey1.jp

- テクノロジー

- 2022/09/21

Java 19が正式リリース。より軽量な仮想スレッド、RISC-Vへの移植など新機能。1年後のJava 21が次のLTS版に Javaの新バージョン「Java 19」正式版がリリースされました。 Java 19 is now available! #Java19 #JDK19 #openjdk Download now: https://t.co/dKovWtNGrs Release notes: https://t.co/EOyaGTLHrl API Javadoc: https://t.co/ViIj9H4JrI Features: https://t.co/XuEExSR7gs Inside Java on JDK 19: https://t.co/q5WGZwxMzb pic.twitter.com/XYYA06ll0m — Java (@java) September 20, 2

-

Googleが「KataOS」を発表した。これはオープンソースの「RISC-V」チップで動作する組み込みシステム向けに、新しいセキュアなOSを模索する初期段階の試みだ。 KataOSは「ほぼ完全にRustで」書かれているという。Rustは「Androidオープンソースプロジェクト」やLinuxカーネルプロジェクトで採用されているプログラミング言語だ。 Googleのオープンソースチームは、「KataOSはほぼ完全にRustで実装されており、Off-by-oneエラー(OBOE)やバッファオーバフローのようなバグのクラス全体を除去することで、ソフトウェアセキュリティの強力な出発点になる」と説明している。同チームは、インテリジェントなアンビエント機械学習(AmbiML)システムの構築を進めている。 プロジェクトのGitHubページでは、KataOSとそれを包含するプロジェクト「Sparrow」

-

GitHub - WerWolv/ImHex: 🔍 A Hex Editor for Reverse Engineers, Programmers and people who value their retinas when working at 3 AM.

- 86 users

- github.com/WerWolv

- テクノロジー

- 2020/12/04

Featureful hex view Byte patching Patch management Infinite Undo/Redo "Copy bytes as..." Bytes Hex string C, C++, C#, Rust, Python, Java & JavaScript array ASCII-Art hex view HTML self-contained div Simple string and hex search Goto from start, end and current cursor position Colorful highlighting Configurable foreground highlighting rules Background highlighting using patterns, find results and b

-

最近ではArm、RISC-Vなど組み込みでも華々しい活躍を見せているRISCプロセッサ。その歴史的経緯を、IT史に詳しい大原雄介さんが解説する。 ARM(現在はArm)の成功は、また別の形で業界に影響を及ぼすことになった。つまり「適当なプロセッサがなければ、自分で作ればいい」というトレンドである。1980年代後半といえば、まだASIC(Application Specific IC:特定用途向けIC)を使うことが多く、国内でもNEC、富士通、日立、東芝、シャープといった大手だけでなく、もっと小さなメーカーもASIC製造に参入していた。 実際、筆者が昔いた会社では、ヤマハに製造を委託することもあった。もっとも、当時のヤマハは規模こそ小さかったものの、97年にIntelに買収された米半導体企業Chips & Technologiesの製品の製造を受諾していたりしていたから、知名度はそれなりにあ

-

コア・オペレーティング・システム・グループでは、ハードウェア、ソフトウェア、アプリケーションを一つのApple体験に統合する、完全に統合されたOSの構築に取り組んでおり、ベクトル・数値計算グループは、iOS、macOS、watchOS、tvOS上で動作するさまざまな組み込みサブシステムの設計、強化、改善を行うことを使命としている。 革新的な「RISC-V」ソリューションと最先端のルーチンを実装しているSWとHWのクロスファンクショナルチームで働ける人材を募集しているそうだ。 この採用情報から、Apple社内ではRISC-Vを統合した何らかの開発が行われていることは明らかで、このアーキテクチャを採用することで、Armのベクターコアのライセンス料を実質的に回避できる。 関連記事 最終回:RISC-Vエコシステムの発展 Arm、NVIDIAとの関係はどうなるのか? RISCの生い立ちから現在まで

-

RISC-Vを取り巻く環境が大きく変化した1週間:「x86、Armに並ぶ存在」とIntelも認める(1/2 ページ) 2022年2月7日の週はRISC-Vエコシステムにとって、非常に重要な1週間だったといえる。一連の発表により、オープンソースの命令セットアーキテクチャ(ISA)の注目度が高まったのだ。以下に詳しく取り上げていきたい。 2022年2月7日の週はRISC-Vエコシステムにとって、非常に重要な1週間だったといえる。一連の発表により、オープンソースの命令セットアーキテクチャ(ISA)の注目度が高まったのだ。以下に詳しく取り上げていきたい。 IntelのRISC-V International加盟 Intelは2022年2月7日(米国時間)、RISC-V Internationalにプレミア(Premier)会員として加盟することを発表した。同社のファウンドリー事業部門「IFS(In

-

RISC-Vの世界的な普及を促進するため、Qualcomm、Infineon、BOSHなど5社がリファレンスアーキテクチャなどを提供する企業を共同設立すると発表

- 66 users

- www.publickey1.jp

- テクノロジー

- 2023/08/08

RISC-Vの世界的な普及を促進するため、Qualcomm、Infineon、BOSHなど5社がリファレンスアーキテクチャなどを提供する企業を共同設立すると発表 米国のQualcomm Technologies、ドイツのInfineon Technologies、ドイツのRobert Bosch、ノルウエーのNordic Semiconductor、オランダのNXP Semiconductorsの5社は、RISC-Vプロセッサの世界的な普及を促進するための企業を共同で設立すると発表しました。 RISC-Vは、RISC-V Internationalの下でオープンかつ無料で使えるプロセッサの命令セットとしてライセンスされています。シンプルな命令セットで電力効率の高いプロセッサを実現可能な点が特徴とされているため、将来的にはArmの競合になるとの見方もあります。 下記はQualcommが発表し

-

Writing a RISC-V Emulator in Rust - Writing a RISC-V Emulator in Rust

- 63 users

- book.rvemu.app

- テクノロジー

- 2020/04/18

NOTE: This project is actively ongoing. Pages are not perfect yet and it possible to change dramatically. Introduction This is the book for writing a 64-bit RISC-V emulator from scratch in Rust. You can run xv6, a simple Unix-like OS, in your emulator once you finish the book. You'll learn the basic computer architecture such as ISA, previleged architecture, exceptions, interrupts, peripheral devi

-

-

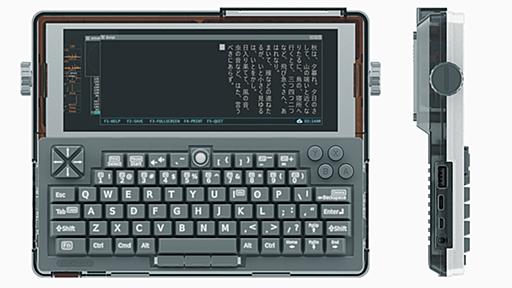

オープンソースのポータブルターミナルキット「DevTerm」に、RISC-Vベースの64ビットCPUコアを搭載した「R-01」モデルが加わった。 Clockworkが販売するDevTermシリーズは、レトロデザインでコンパクトな筐体が特徴のキーボード、ディスプレイ一体型コンピューター。これまでCortex-A53搭載の「A04」を2モデル、Cortex-A72およびCortex-A53搭載の「A06」を2モデル、Raspberry PI CM3+ Lite搭載の「RPI-CM3」を1モデル 発表してきた。これらは特別なツールや知識が無くても簡単に組み立てられ、プログラミングツールとしてだけでなくゲーム機としても利用できる。 R-01はこれまでのモデルと同様、メインボードは95×77mmとコンパクトな「ClockworkPi v3.14」を使う。USBやmicro HDMI、オーディオ端子、

-

RISC-VのCPUにメモリの内容を好き放題にできる脆弱性「GhostWrite」が見つかる、対策するとCPU性能が大幅に低下

- 56 users

- gigazine.net

- テクノロジー

- 2024/08/08

RISC-VのCPUのひとつに、デバイスのメモリを自由に読み取ったり書き換えたりすることができてしまう脆弱(ぜいじゃく)性の「GhostWrite」があることがわかりました。ハードウェアの設計上の問題であるため、修正パッチなどのソフトウェア的な対策を講じることはできず、対処するには性能を大幅に犠牲にしなくてはならないと指摘されています。 GhostWrite https://ghostwriteattack.com/ 今回発見された脆弱性のGhostWriteは、Alibabaの子会社である中国のメーカー・T-Headが開発しているCPUで、現行で最速のRISC-Vチップとされている「T-Head XuanTie C910」の不具合です。 GhostWriteを発見したヘルムホルツ情報セキュリティセンター(CISPA)の研究チームによると、GhostWriteの影響を受ける命令は仮想メモリ

-

Rubyでできる!RISC-Vシミュレータの作りかた 〜 From 4649 To HELLO WORLD 〜 - ESM アジャイル事業部 開発者ブログ

- 56 users

- blog.agile.esm.co.jp

- テクノロジー

- 2022/06/10

HELLO WORLD〜 はじめに こんにちは、永和システムマネジメントの自作CPUおじさん、はたけやまたかし( @htkymtks )です。 今回はRubyを使った小さなRISC-Vシミュレータの作り方をご紹介します(以前もシミュレータの記事を書いたのですが、シミュレータに大幅に手を入れたので、それに対応したHDリマスター版です) リポジトリ (今回ご紹介するシミュレータのリポジトリはこちら) thata / rv32sim https://github.com/thata/rv32sim RISC-Vとは RISC-VはCPUの命令セットアーキテクチャ(ISA)のひとつで、使用料のかからないオープンソースライセンスで提供されていることや、命令セットの美しさから最近注目を集めています。 仕様 RISC-Vの仕様にはワード幅(32ビット、64ビット)や浮動小数点数サポートの有無など、いくつ

-

インテル、オープンな命令セットを推進する「RISC-V 」に最高位メンバーとして加盟。RISC-VベースのFPGAチップも提供開始など、RISC-Vへのコミットを明確に

- 53 users

- www.publickey1.jp

- テクノロジー

- 2022/02/10

インテル、オープンな命令セットを推進する「RISC-V 」に最高位メンバーとして加盟。RISC-VベースのFPGAチップも提供開始など、RISC-Vへのコミットを明確に プロセッサのオープンな命令セットを推進する団体「RISC-V International」は、同団体の最高位メンバーであるプレミアメンバーシップとして米インテルが加盟することを発表しました。 これに伴い、Intel FoundryのバイスプレジデントBob Brennan氏がRISC-VのBoard of Directors(取締役会)および技術的な方向性を決めるテクニカルステアリングコミッティの一員となります。 Intel has been a leader in microprocessor innovation for decades and today’s announcements signal that mas

-

RISC-Vの誕生 既存の命令セットアーキテクチャでは満足できなかった、その理由:RISCの生い立ちからRISC-Vまでの遠い道のり(1/3 ページ) やっと、IBM 801からRISC-Vまで話がたどり着いた。RISC-Vの生い立ちについては以前EETimesで記事を書かせていただいたが、改めて簡単にご紹介を。 昨今の大学の場合、CPUを設計する、というのは割とごく一般的なもの「らしい」(筆者は地方大学の理学部物理学科出身なので、いまいち情報系とか計算機系の研究室のカリキュラムがよく分かっていない)。例えば東京大学理学部の情報科学科では、学部の3年生になるとCPUを作るという課題が与えられるそうだ。ターゲットはFPGAボードであるが、この上で自分の考えたアーキテクチャのCPUをHDL(Hardware Description Language:ハードウェア記述言語)で記述する形で実装し、

-

2021年8月25日紙版発売 2021年8月20日電子版発売 ⻄⼭悠太朗,井⽥健太 著 B5変形判/336ページ 定価3,520円(本体3,200円+税10%) ISBN 978-4-297-12305-5 Gihyo Direct Amazon 楽天ブックス 丸善ジュンク堂書店 ヨドバシ.com 電子版 Gihyo Digital Publishing Amazon Kindle ブックライブ 楽天kobo honto この本の概要 本書では,UCバークレーで開発されたオープンソースの命令セット(ISA)「RISC-V」を用いて,CPUの作り方を解説します。コンピュータアーキテクチャ,ハードウェアに関する知識があまりない方にも理解できるように基礎からわかりやすく学んでいきます。CPUとコンピュータアーキテクチャのしくみを解説したうえで,基本整数命令の実装から,CPUの高速化で活躍するパイ

-

Google、NVIDIA、Qualcomm、インテルらが、RISC-V用オープンソース開発を加速させる組織「RISC-V Software Ecosystem」(RISE)プロジェクトを立ち上げ

- 51 users

- www.publickey1.jp

- テクノロジー

- 2023/06/21

Google、NVIDIA、Qualcomm、インテルらが、RISC-V用オープンソース開発を加速させる組織「RISC-V Software Ecosystem」(RISE)プロジェクトを立ち上げ RISC-V(リスクファイブ)プロセッサ対応のオープンソース開発を加速させる組織「RISC-V Software Ecosystem」(RISE)プロジェクトが、Linux Foundation Europeをホストとし、Google、NVIDIA、Qualcomm、インテルを始めとする13社がボードメンバーとなってスタートしました。 もともとRISC-Vはカリフォルニア大学バークレイ校のコンピュータサイエンス科が開始した、新しいプロセッサ命令セットを開発するためのプロジェクトです。創立メンバーにはRISCプロセッサの基礎を築いた計算機科学者のデイビッド・パターソン博士らがおり、当初は教育に使う

キーボードショートカット一覧

j次のブックマーク

k前のブックマーク

lあとで読む

eコメント一覧を開く

oページを開く