Tema 5. Memorias: Estructura de Computadores

Tema 5. Memorias: Estructura de Computadores

Cargado por

ALONSO_007Copyright:

Formatos disponibles

Tema 5. Memorias: Estructura de Computadores

Tema 5. Memorias: Estructura de Computadores

Cargado por

ALONSO_007Descripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Copyright:

Formatos disponibles

Tema 5. Memorias: Estructura de Computadores

Tema 5. Memorias: Estructura de Computadores

Cargado por

ALONSO_007Copyright:

Formatos disponibles

Tema 5.

Memorias

Estructura de

Computadores

I. T. Informtica de Gestin / Sistemas

Curso 2008-2009

Tema 5:

Transparencia: 2 / 23

Memorias

ndice

Definiciones

Parmetros caractersticos

Jerarqua de memoria

Dispositivos de almacenamiento

Clasificacin

Fundamentos de las memorias

Memoria cach / Memoria virtual

Memoria principal

Mapa de memoria

Organizacin del mapa de memoria

Ejemplo: Microprocesador i80x86

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 3 / 23

Memorias

Definiciones

Memoria: parte del computador que

almacena la informacin: instrucciones

y datos. Es conjunto de posiciones de

memoria

MEMORIA

Direccin: posicin de memoria en la

direcciones

que se almacena una informacin

datos

Punto de memoria: elemento que

seleccin

almacena un bit

lectura

escritura

Palabra: nmero de bits que suele

contener cada posicin de memoria (8,

16, 32 64 bits)

Esquema bsico de memoria

Operaciones bsicas:

Lectura

Escritura

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 4 / 23

Memorias

Parmetros caractersticos (I)

Capacidad: cantidad de informacin que puede almacenar un

dispositivo

Medidas ms usuales:

Kilobyte (KB) = 210 bytes

Megabyte (MB) = 220 bytes

Gigabyte (GB) = 230 bytes

Terabyte (TB) = 240 bytes

Velocidad o tiempo de acceso: tiempo que transcurre desde que

se proporciona la direccin a la memoria y el momento en que el

dato est disponible (lectura) o queda grabado (escritura)

Ciclo de memoria: tiempo que transcurre entre dos accesos

consecutivos a memoria. Es superior al tiempo de acceso (Ej.

DRAM)

Coste por bit: precio por cada bit de informacin

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 5 / 23

Memorias

Parmetros caractersticos (y II)

Comparativa

velocidad/coste

Coste (pts/bit)

Capacidad (bytes)

Comparativa

velocidad/capacidad

1s

10 ms

100 us

1 us

1s

10 ns

10 ms

100 us

1 us

10 ns

Tiempo de acceso

Tiempo de acceso

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 6 / 23

Memorias

Jerarqua de memoria (I)

Consiste en distribuir la informacin de diversos dispositivos de memoria,

de forma que, cerca del procesador se ubique el modelo de memoria

ms rpido y de menor capacidad

El dispositivo ms lento y de mayor capacidad contiene la totalidad del

cdigo y los datos de un programa

El procesador percibe que la velocidad del sistema es aproximadamente

la velocidad del dispositivo ms rpido

Ejemplos:

Jerarqua

Capacidad en octetos Tiempo de acceso

Tipo

Registros

Memoria cache

Memoria principal

Disco duro

CD-ROM

DVD

Cinta

512 bytes

512 Kb

512 Mb

3,5 - 10 Gb

650 Mb

4,7 - 17 Gb

2 ns

2 ns

40 ns.

10 ms

100 ms

ECL

SRAM

SDRAM

Magntico

ptico

ptico

512 Gb - 2 Tb

Minutos

Magntico

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 7 / 23

Memorias

Jerarqua de memoria (y II)

Jerarqua:

Registros CPU

Cache interna

Cache externa

Memoria principal

Dispositivos de

almacenamiento

secundario

CPU

capacidad

tiempo de

acceso

precio

por bit

nivel 1

nivel 2

nivel 3

nivel 4

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

CACHE

MEMORIA PRINCIPAL

DISCOS / CDs / DVDs

UNIDADES DE CINTA

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 8 / 23

Memorias

Memoria cach

Objetivo de la Cach: dar la impresin de que las referencias a

memoria se sirven a una velocidad muy cercana a la del procesador

Diseo de la Cach:

Se debe tener en cuenta la optimizacin de los siguientes

parmetros: probabilidad de acierto, tiempo de acceso efectivo,

retardos debidos a fallos

Est dividida lgicamente en: el directorio y los bloques de datos

estableciendo la correspondencia entre bloques de MP y bloques

de Cach

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 9 / 23

Memorias

Memoria virtual

Objetivo de la memoria virtual:dar la impresin de tener un espacio de

memoria ilimitado

Diseo de la MVirtual:

Es un mecanismo que permite la ejecucin de programas cargados

parcialmente en la memoria principal del computador ofreciendo al

usuario un espacio de memoria principal ilimitado

Combina dos dispositivos de almacenamiento de diferente capacidad,

velocidad y coste: la memoria principal y el disco duro (lo ms

habitual)

Facilita los mecanismos de proteccin de memoria, fundamentales en

multiprogramacin, para que los distintos programas no interfieran

entre s

Separa los conceptos de espacio de direcciones lgicas y espacio de

direcciones fsicas

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 10 / 23

Memorias

Fundamentos de las memorias

Soporte de almacenamiento: almacena los estados de energa 0 1

Dispositivo de lectura (trasductor de lectura):detecta el estado en

el que se encuentra el soporte

Dispositivo de escritura (trasductor de escritura): genera la

energa necesaria para poner el soporte en el estado deseado

Dispositivo de direccionamiento: permite grabar o leer la

informacin en el lugar deseado

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 11 / 23

Memorias

Dispositivos de almacenamiento (I)

Clasificacin

Duracin de la informacin:

Permanente / no voltil

Voltil

Lectura destructiva

Refresco

Modo de acceso:

Aleatorio

Secuencial

Directo

Realizacin de operaciones:

Por palabras

Por bloques

Forma de acceso:

Por direccin

Por contenido

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 12 / 23

Memorias

Dispositivos de almacenamiento (II)

Ejemplos

Ferritas:

Acceso aleatorio (por palabras)

Lectura destructiva

Permiten lectura y escritura

Semiconductores:

Acceso aleatorio (por palabras)

Tipos:

De lectura y escritura

RAM estticas (voltil)

RAM dinmicas

(refresco)

De slo lectura

ROM (permanente)

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 13 / 23

Memorias

Dispositivos de almacenamiento (III)

Ejemplos

Cintas magnticas:

Acceso secuencial (por bloques)

Permanente

Permiten lectura y escritura

Uso: almacenamiento

secundario

Discos:

Acceso directo

(pista/sector/cilindro)

Permanente

Permiten lectura y escritura

Uso: almacenamiento

auxiliar/secundario

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

CD-ROMs, DVDs, HD-DVD, BR:

Acceso secuencial (por

sectores)

Permanente

Slo permiten lectura

Uso: almacenamiento

auxiliar/secundario

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 14 / 23

Memorias

Memoria principal (I)

Clasificacin

RAM (Random Access Memory) - Memoria de acceso aleatorio

SRAM - RAM esttica DRAM - RAM dinmica

SDRAM - Synchronous Dynamic RAM - (RAM sncrona y dinmica)

ROM (Read Only Memory) - Memoria de slo lectura

PROM - Programmable ROM - ROM programable

EPROM - Erasable PROM - PROM que se puede borrar

EEPROM - Electrically EPROM - EPROM elctrica

Flash

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 15 / 23

Memorias

Memoria principal (II)

Mapa de memoria (I)

Mapa de memoria

El mapa de memoria es el espacio direccionable de un computador

El mapa de memoria viene determinado por el tamao de las

direcciones. As, un tamao de direcciones de "m" bits permite

direccionar 2m direcciones

"m" es el ancho del bus de direcciones

Ampliacin del mapa de memoria.

Normalmente no se suele equipar el computador con toda la memoria

0

que es capaz de direccionar

m bits

Memoria

Direccin

m-1

0

Disponible

2k-1

Mapa

usado

Mapa

total

2m-1

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 16 / 23

Memorias

Memoria principal (III)

Mapa de memoria (II)

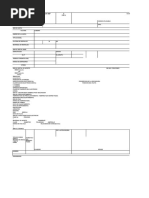

Ampliacin del mapa de memoria en nmero de direcciones

Construir un sistema de memoria de 16Kx8 a partir de mdulos de

8kx8 en un computador con 14 bits de bus de direcciones

1 ver que se puede direccionar. 16k = 214 <= 214 (del bus) con lo que

vemos que se puede direccionar.

2 calcular cuantos mdulos se necesitarn.

16k 8

x = 2 x1 = 2 mdulos de 8kx8

8k 8

Ahora se tiene que reflejar en el mapa de

memoria cuando se accede a un mdulo o a

otro ya que el esquema es el de la figura

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 17 / 23

Memorias

Memoria principal (IV)

Mapa de memoria (III)

3 Calcular el mapa de memoria. Dado que los dos mdulos son de

8Kx8 (8k=213) y tenemos 14 bits en el bus de direcciones se emplear

un bit para distinguir cuando se accede a uno o a otro mdulo

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 18 / 23

Memorias

Memoria principal (V)

Mapa de memoria (IV)

4. Dibujar el esquema de memoria. Solamente se han puesto las

seales del bus de datos, de direcciones y la seal de seleccin del

mdulo CS.

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 19 / 23

Memorias

Memoria principal (VI)

Mapa de memoria (V)

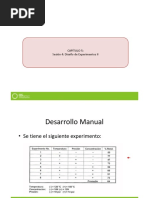

Ampliacin del mapa de memoria en tamao de palabra

Construir un sistema de memoria de 16Kx16 a partir de mdulos de

16kx8 en un computador con 14 bits de bus de direcciones y de 16 bits

en el bus de datos

1 ver que se puede direccionar. 16k = 214 <= 214 (del bus) con lo que

vemos que se puede direccionar. Y el bus de datos tiene el mismo

tamao que la palabra que deseamos leer

2 calcular cuantos mdulos se necesitarn.

16k 16

x = 1x 2 = 2 mdulos de 16kx8

16k 8

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Tema 5:

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Transparencia: 20 / 23

Memorias

Memoria principal (VI)

Mapa de memoria (V)

3 Dibujar el esquema de memoria. Dado que los dos mdulos son de

16Kx8 y queremos almacenar 16 bits se deber acceder a los dos

mdulos a la vez

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

10

Tema 5:

Transparencia: 21 / 23

Memorias

Memoria principal (VII)

Organzacin de la memoria

00000h

MEMORIA PRINCIPAL

RAM

Bus datos

CPU

Puerto 1 Puerto

2

Puerto 3 Puerto 4

Bus datos

Bus direcc.

Bus direcc.

Seales control

Seales control

ROM

Controlador

Perifrico

Controlador

Perifrico

0FFFF0h

0FFFFFh

Controlador

Perifrico

Mapa de memoria en el 8086/88

Memoria multipuerto

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

Tema 5:

Transparencia: 22 / 23

Memorias

Memoria principal (VIII)

Ejemplo del mapa de memoria del i80x86

4096 Mb

Memoria extendida

Memoria alta

(HMA)

Memoria expandida

Pginas lgicas

(EMS)

16 Mb

386/486/Pentium

286

1088 Kb

8086

ROM-BIOS

1024 Kb

Marco de pgina EMS

896 Kb

832 Kb

Memoria de vdeo

768 Kb

640 Kb

Memoria convencional

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

0 Kb

Estructura de Computadores

I. T. I. de Gestin / Sistemas

11

Tema 5:

Transparencia: 23 / 23

Memorias

Bibliografa

Estructura de Computadores (Captulo 6)

Jos M. Angulo

Ed. Paraninfo

Arquitectura de Computadores (Captulo 5)

Jos A. de Frutos y Rafael Rico

Ed. Alcal de Henares

Fundamentos de los Computadores (Captulo 3)

Pedro de Miguel Anasagasti

Ed. Paraninfo

Departamento de Automtica

rea de Arquitectura y Tecnologa de Computadores

Estructura de Computadores

I. T. I. de Gestin / Sistemas

12

También podría gustarte

- Tema3 MemoriasDocumento8 páginasTema3 MemoriasKA CGAún no hay calificaciones

- Ec t5 PDFDocumento12 páginasEc t5 PDFSubsecretario de GobiernoAún no hay calificaciones

- Enunciadosect 5Documento14 páginasEnunciadosect 5Francisco Javier RomeroAún no hay calificaciones

- Memoria Parte 2Documento6 páginasMemoria Parte 2nadia tolabaAún no hay calificaciones

- 4ta Memoria ComputadorDocumento27 páginas4ta Memoria ComputadorChristina BuchananAún no hay calificaciones

- Arquitectura de Computadores-Clase5Documento38 páginasArquitectura de Computadores-Clase5Ing Ana Lidia Barcenas CortésAún no hay calificaciones

- EnsayoDocumento5 páginasEnsayoJavier ChavarreaAún no hay calificaciones

- MemoriaDocumento5 páginasMemoriaMaryi Becerra TorresAún no hay calificaciones

- Solucion de Problemas de MemoriasDocumento36 páginasSolucion de Problemas de MemoriasJose Alexander Estrada López100% (1)

- Investigaciones de Memorias - Arg - 5Documento36 páginasInvestigaciones de Memorias - Arg - 5FrancisAún no hay calificaciones

- iezziTP4-20-9-NOTADocumento42 páginasiezziTP4-20-9-NOTAfontanetAún no hay calificaciones

- Memorias Caracteristica AplicacionesDocumento8 páginasMemorias Caracteristica Aplicaciones12alex66Aún no hay calificaciones

- RamDocumento5 páginasRamPatricio LothbrokAún no hay calificaciones

- Organizacion de La MemoriaDocumento12 páginasOrganizacion de La MemoriaAndres MorenoAún no hay calificaciones

- Tipos de Memoria y Arquitectura de Von Neuman Vs HarvardDocumento10 páginasTipos de Memoria y Arquitectura de Von Neuman Vs Harvardviviam pal,maAún no hay calificaciones

- Semana02 38697Documento26 páginasSemana02 38697Mariela AcostaAún no hay calificaciones

- Memoria InformaticaDocumento5 páginasMemoria InformaticaLorena CabralAún no hay calificaciones

- Trabajo Informatica Preguntas de Repaso IIDocumento5 páginasTrabajo Informatica Preguntas de Repaso IIdayosegb50% (2)

- Las MemoriasDocumento5 páginasLas MemoriasRodrigo Palomino AvilesAún no hay calificaciones

- Unidad 2 MemoriasDocumento5 páginasUnidad 2 MemoriasJosue Misael Haas BacabAún no hay calificaciones

- Guía de Estudio - Extraordinario OCDocumento14 páginasGuía de Estudio - Extraordinario OCjuan perez perezAún no hay calificaciones

- Jerarquía de MemoriasDocumento5 páginasJerarquía de MemoriasArik SamudioAún no hay calificaciones

- Jerarquía de MemoriaDocumento6 páginasJerarquía de MemoriaCarlos Jesus Rivero LopezAún no hay calificaciones

- Presentación de Memorias (Digitales II)Documento16 páginasPresentación de Memorias (Digitales II)Chucho Cast FAún no hay calificaciones

- Tarea de Daniela Alejandra Marin Elias 21-06-22Documento6 páginasTarea de Daniela Alejandra Marin Elias 21-06-22Daniela alejandra Elías mayoAún no hay calificaciones

- Memoria Principal RAM-InterrupcionesDocumento7 páginasMemoria Principal RAM-InterrupcionesCarlos Mtz SerranoAún no hay calificaciones

- Historia - Micro ControladorDocumento12 páginasHistoria - Micro ControladorJhona T IgAún no hay calificaciones

- Patricia Sanz GenísDocumento22 páginasPatricia Sanz Genísrmtico1mjanojanitoAún no hay calificaciones

- UT04-1 MemoriaDocumento41 páginasUT04-1 Memoriatrianc70Aún no hay calificaciones

- Trabajo Practico Nº 3: Conceptos Básicos Sobre Las ComputadorasDocumento6 páginasTrabajo Practico Nº 3: Conceptos Básicos Sobre Las ComputadorascamiyloreAún no hay calificaciones

- Mantenimiento de Sistemas de Informacion 2Documento11 páginasMantenimiento de Sistemas de Informacion 2Miguel PérezAún no hay calificaciones

- Estructura y Funcionamiento de La Memoria ArqpcDocumento21 páginasEstructura y Funcionamiento de La Memoria ArqpcPatricio CordovaAún no hay calificaciones

- La Memoria RamDocumento24 páginasLa Memoria RamCesar L. Inga BuendiaAún no hay calificaciones

- ARQ. CompDocumento32 páginasARQ. CompZoilo juan nkogo bayemeAún no hay calificaciones

- Manual de Hasta 3Documento59 páginasManual de Hasta 3Zoilo juan nkogo bayemeAún no hay calificaciones

- Manual de Clases Arq. ComputacionalDocumento46 páginasManual de Clases Arq. ComputacionalZoilo juan nkogo bayemeAún no hay calificaciones

- Tema 4Documento75 páginasTema 4Miguel Angel Aguilar MoreiraAún no hay calificaciones

- Resolucion Del Examen de ArquitecturaDocumento9 páginasResolucion Del Examen de ArquitecturaJEANCARLO CATARIAún no hay calificaciones

- EQ 1-Actividad Fundamental 3Documento11 páginasEQ 1-Actividad Fundamental 3Angel HuitradoAún no hay calificaciones

- Tema 1 - Arquitectura y Componentes de Un OrdenadorDocumento22 páginasTema 1 - Arquitectura y Componentes de Un OrdenadorNatalia Alejandra Gutiérrez EcheverryAún no hay calificaciones

- Sistemas MicroprocesadosDocumento36 páginasSistemas Microprocesadosacro_09vAún no hay calificaciones

- Ensayo 3Documento11 páginasEnsayo 3Gabriel Feliz JavierAún no hay calificaciones

- Memorias ProgramablesDocumento21 páginasMemorias ProgramablesHermes Alvarez Gavilan100% (1)

- Tema 2 Harware 1 BachilleratoDocumento21 páginasTema 2 Harware 1 Bachilleratocristóbal reina torresAún no hay calificaciones

- capitulo8Documento29 páginascapitulo8Návi OicrutAún no hay calificaciones

- Tarea SofiaDocumento21 páginasTarea Sofiaaimer ruizAún no hay calificaciones

- Practica1 Formato PDFDocumento5 páginasPractica1 Formato PDFMaryCarmenAún no hay calificaciones

- Introducción Lenguaje EnsambladorDocumento120 páginasIntroducción Lenguaje EnsambladorIsidoro GonzalezAún no hay calificaciones

- Tarea 3 Sistemas DigitalesDocumento3 páginasTarea 3 Sistemas DigitalesMartin GomezAún no hay calificaciones

- MemoriaDocumento10 páginasMemoriaJesus ToroAún no hay calificaciones

- Sistema Operativo Informe Final 6Documento12 páginasSistema Operativo Informe Final 6Tania Romero AcuñaAún no hay calificaciones

- Unidad III Microcontroladores Sistemas ProgramablesDocumento7 páginasUnidad III Microcontroladores Sistemas Programablesmarce lopezAún no hay calificaciones

- Tema 9 Arquitectura de Computadoras, Portatiles y ServidoresDocumento88 páginasTema 9 Arquitectura de Computadoras, Portatiles y Servidoresfigueres100% (1)

- Clase 3 U1 Informatica Basica - Docx 1Documento4 páginasClase 3 U1 Informatica Basica - Docx 1nanesc82Aún no hay calificaciones

- Memorias y MicroprocesadoresDocumento25 páginasMemorias y MicroprocesadorestoolioratmAún no hay calificaciones

- Foro 2. Uso y Rendimiento de La MemoriaDocumento2 páginasForo 2. Uso y Rendimiento de La MemoriaJose Mejia MiguelAún no hay calificaciones

- El PrimerDocumento5 páginasEl PrimerDaniel ZavalaAún no hay calificaciones

- Apuntes AulapcDocumento96 páginasApuntes AulapcAmaya Muñoz CastellanosAún no hay calificaciones

- Sistemas Operativos: Implantación de Sistemas Operativos (CFGS ASIR)De EverandSistemas Operativos: Implantación de Sistemas Operativos (CFGS ASIR)Aún no hay calificaciones

- UF1468 - Almacenamiento de la información e introducción a SGBDDe EverandUF1468 - Almacenamiento de la información e introducción a SGBDAún no hay calificaciones

- BlockDocumento2 páginasBlockALONSO_007Aún no hay calificaciones

- BlockDocumento4 páginasBlockALONSO_007Aún no hay calificaciones

- Acta 005 SODocumento23 páginasActa 005 SOALONSO_007Aún no hay calificaciones

- Lab2 FisicaDocumento45 páginasLab2 FisicaALONSO_007Aún no hay calificaciones

- ProblemasDocumento15 páginasProblemasjhordy100% (3)

- Mecanica de Fluidos - Sem 13Documento36 páginasMecanica de Fluidos - Sem 13Vanessa Lizana AncoAún no hay calificaciones

- Permisos de TrabajoDocumento53 páginasPermisos de Trabajojelamadrid100% (3)

- Proyecto No 3 Controlar Un ServomotorDocumento7 páginasProyecto No 3 Controlar Un ServomotorDomingo ArroyoAún no hay calificaciones

- Guía de AlgoritmosDocumento4 páginasGuía de AlgoritmosChristian VelasquezAún no hay calificaciones

- Ejercicios - Regresión y CorrelaciónDocumento12 páginasEjercicios - Regresión y CorrelaciónNicole VallejoAún no hay calificaciones

- Ejercicios Repaso 1er TCPDocumento2 páginasEjercicios Repaso 1er TCPorlando29espinosaAún no hay calificaciones

- Analisis MatricialDocumento37 páginasAnalisis MatricialKelber David Murgas MirandaAún no hay calificaciones

- SoldaduraDocumento2 páginasSoldaduraDeisy Teresa Mejia BarajasAún no hay calificaciones

- Análisis No LinealDocumento24 páginasAnálisis No LinealJHONJAIRO28Aún no hay calificaciones

- Envejecimiento Reologia de AsfaltosDocumento6 páginasEnvejecimiento Reologia de AsfaltosJorge MirandaAún no hay calificaciones

- Comparaciones FilosofíaDocumento4 páginasComparaciones FilosofíasunAún no hay calificaciones

- DINAMICA DE ESTRUCTURAS - PPTX 1Documento54 páginasDINAMICA DE ESTRUCTURAS - PPTX 1Maynor Orestes Torres EspinozaAún no hay calificaciones

- Partes de Una Estación TotalDocumento5 páginasPartes de Una Estación TotalJhonatan ChiicomaAún no hay calificaciones

- Reacciones Exotérmicas y EndotérmicasDocumento11 páginasReacciones Exotérmicas y EndotérmicasMaryury BolañoAún no hay calificaciones

- Silabo de Fisica II Por Competencia 2018-2 ImfDocumento6 páginasSilabo de Fisica II Por Competencia 2018-2 ImfJair Diego Vidaurre QuispeAún no hay calificaciones

- Practica5 - Electronica DigitalDocumento5 páginasPractica5 - Electronica DigitalLopezinAún no hay calificaciones

- Construccion de Una Carta Psicrometrica (Recuperado)Documento5 páginasConstruccion de Una Carta Psicrometrica (Recuperado)Susey Madelit Apaza MamaniAún no hay calificaciones

- Estructura Molecular Unidad 4 Física ModernaDocumento50 páginasEstructura Molecular Unidad 4 Física ModernaNico FernandezAún no hay calificaciones

- Dolphin-Custom Masip AccuriserDocumento3 páginasDolphin-Custom Masip AccuriserLeonardo Manzano GarcíaAún no hay calificaciones

- Cables VDFDocumento4 páginasCables VDFAlex Fernández100% (1)

- MEDIDA DE PH LAB. INSTRUMENTACIÓN IDocumento34 páginasMEDIDA DE PH LAB. INSTRUMENTACIÓN IMELISSA VERONICA TUDELANO OSPINAAún no hay calificaciones

- CQ-QGII-Informe-Titulación Ácido-BaseDocumento3 páginasCQ-QGII-Informe-Titulación Ácido-BaseLesly SanchezAún no hay calificaciones

- Tema 7 AutoescuelaDocumento29 páginasTema 7 AutoescuelaAya el kanfoudAún no hay calificaciones

- BCMV U2 Ea CLMVDocumento5 páginasBCMV U2 Ea CLMVclaudia martinezAún no hay calificaciones

- Ejercicios Resueltos de Calculo Diferencial D4 Ccesa007Documento11 páginasEjercicios Resueltos de Calculo Diferencial D4 Ccesa007Demetrio Ccesa Rayme80% (5)

- Banco de Preguntas - Med Interna IDocumento92 páginasBanco de Preguntas - Med Interna IVictor Euclides Briones MoralesAún no hay calificaciones

- Plotear en NXDocumento7 páginasPlotear en NXTomas LopezAún no hay calificaciones

- Cap 5 Ses 4Documento22 páginasCap 5 Ses 4Diana Davila MarinAún no hay calificaciones

- Itsav InvDocumento12 páginasItsav InvCiber TotyAún no hay calificaciones