Prueba de Sintesis

Prueba de Sintesis

Cargado por

djimenezamoCopyright:

Formatos disponibles

Prueba de Sintesis

Prueba de Sintesis

Cargado por

djimenezamoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Copyright:

Formatos disponibles

Prueba de Sintesis

Prueba de Sintesis

Cargado por

djimenezamoCopyright:

Formatos disponibles

lOMoARcPSD|32574709

Prueba de síntesis

Microelectrónica (Universitat Oberta de Catalunya)

Escanea para abrir en Studocu

Studocu no está patrocinado ni avalado por ningún colegio o universidad.

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Aquesta prova només la poden fer els

estudiants que hagin aprovat l'avaluació

!!!

contínua

Esta prueba solo pueden realizarla los

estudiantes que hayan aprobado la evaluación

continua

Fitxa tècnica de la prova de síntesi / Ficha técnica de la

prueba de síntesis

No és necessari que escriguis el teu nom. Un cop resolta la prova final, només

s’accepten documents en format .doc, .docx (Word) i .pdf. / No es necesario que

escribas tu nombre. Una vez resuelta la prueba final, solo se aceptan documentos

en formato .doc, .docx (Word) y .pdf.

Comprova que el codi i el nom de l'assignatura corresponen a l'assignatura de què

t'has matriculat. / Comprueba que el código y el nombre de la asignatura

corresponden a la asignatura de la que te has matriculado.

Temps total / Tiempo total: 1 hora Valor de cada pregunta: SE

INDICA EN EL ENUNCIADO / S'INDICA A L'ENUNCIAT.

Es pot consultar material durant la prova? / ¿Se puede consultar material durante

la prueba? NO Quins materials estan permesos? / ¿Qué materiales están

permitidos? CAP/NINGUNO

Es pot fer servir calculadora? / ¿Puede utilizarse calculadora? SÍ De quin tipus?

/ ¿De qué tipo? NO PROGRAMABLE

Si hi ha preguntes tipus test, descompten les respostes errònies? / Si hay

preguntas tipo test, ¿descuentan las respuestas erróneas? SÍ Quant? /

¿Cuánto? SE INDICA EN EL ENUNCIADO / S'INDICA A L'ENUNCIAT.

Indicacions específiques per a la realització d'aquesa prova de síntesi/ Indicaciones

específicas para la realización de esta prueba de síntesis:

Pàgina / Página 1 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Pàgina / Página 2 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Enunciats / Enunciados

ENUNCIADO EN CASTELLANO

Actividad 1 (5 puntos)

Responda a las siguientes preguntas tipo test en letra MAYÚSCULA en las casillas que se

muestran a continuación. Cada pregunta tiene un valor de 0.5 puntos y solo una respuesta

es correcta. Las preguntas respondidas incorrectamente tienen una penalización de 0.125

puntos, mientras que las preguntas no respondidas no tienen penalización.

P1 P2 P3 P4 P5

P6 P7 P8 P9 P10

P1. De las siguientes afirmaciones sobre los dispositivos semiconductores y sus principios

de funcionamiento indica cuál de ellas es FALSA.

A. En un transistor de efecto de campo (FET), el flujo de corriente se controla variando el

voltaje en la puerta, lo que altera el ancho del canal por donde pasan los portadores de

carga.

B. En un diodo LED, cuando se aplica un voltaje en la dirección correcta, los electrones y los

agujeros se recombinan en la región de agotamiento, emitiendo luz en el proceso.

C. Un diodo Zener está diseñado para operar en la región de ruptura inversa, manteniendo un

voltaje de salida constante incluso cuando el voltaje de entrada varía significativamente.

D. Un semiconductor tipo N se obtiene al dopar el material semiconductor con átomos que

tienen menos electrones de valencia que el material base.

P2. De las siguientes afirmaciones sobre los elementos y conceptos comunes en circuitos

integrados, indica cuál de ellas es VERDADERA.

A. Un multiplexor es un circuito que compara dos señales de entrada y produce una salida

que indica cuál de las dos es mayor.

B. En un circuito lógico, el uso de puertas XOR es esencial para implementar funciones de

multiplicación binaria.

Pàgina / Página 3 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

C. La memoria ROM (Read-Only Memory) en un sistema integrado permite no solo la lectura,

sino también la escritura de datos, aunque con limitaciones en el número de ciclos de

escritura.

D. Una señal de reloj en un circuito digital sincroniza las operaciones de varios componentes,

asegurando que todos ellos operen en los mismos intervalos de tiempo

P3. De las siguientes afirmaciones sobre los subsistemas típicos en circuitos integrados,

indica cuál de ellas es VERDADERA.

A. La generación de una pareja electrón-hueco en un semiconductor resulta en un aumento

temporal de portadores en la banda de conducción y de valencia.

B. Al duplicar la frecuencia de conmutación de un circuito CMOS respecto a otro similar

(misma tecnología y funcionalidad), se puede asumir que el consumo de energía también

se duplicará.

C. Durante el proceso de conmutación de un inversor CMOS, hay momentos en los que

ambos transistores, NMOS y PMOS, se encuentran operando en la región de saturación.

D. En términos de tiempo de retardo, una puerta OR (tecnología CMOS) con más entradas

tendrá, en el peor caso, un retardo mayor que una puerta OR (tecnología CMOS) con

menos entradas.

P4. De las siguientes afirmaciones sobre los componentes y operaciones de los circuitos

integrados, indica cuál de ellas es FALSA.

A. Un selector es un dispositivo con múltiples entradas y una salida, donde la salida

corresponde al valor de una entrada seleccionada por señales de control.

B. En un circuito restador básico, se puede realizar la operación de resta sin necesidad de

hardware adicional para gestionar el acarreo negativo.

C. La representación en complemento a 1 se utiliza para codificar números negativos en

sistemas digitales invirtiendo todos los bits del número positivo equivalente.

D. Un contador binario en un circuito integrado es un tipo de flip-flop que cambia su estado

con cada pulso de reloj, siguiendo una secuencia binaria predefinida

P5. De las siguientes afirmaciones sobre los transistores MOSFET y puertas CMOS, indica

cuál de ellas es FALSA.

A. Un MOSFET en la zona de saturación mantiene una corriente de drenaje constante a

pesar de aumentos en el voltaje de drenaje.

B. En un diseño de inversor CMOS, el transistor MOSFET de tipo P (pMOS) se utiliza

comúnmente como pull-up.

C. En una puerta AND CMOS, cuando todas las entradas están en alto (un uno lógico), los

transistores nMOS en la parte inferior de la puerta se encuentran en corte.

D. Un transistor MOSFET de agotamiento es normalmente conductivo sin voltaje aplicado

entre la puerta y el sustrato.

P6: Respecto a los ASIC, las FPGA y los dispositivos lógicos programables, indica cuál de

las siguientes afirmaciones es VERDADERA.

Pàgina / Página 4 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

A. Desde la aparición de las FPGAs, siempre se han utilizado lenguajes de descripción de

hardware como el VHDL para realizar el proceso de diseño de funciones lógicas.

B. Las memorias FIFO suelen utilizarse para transferir información de un dominio de reloj a

otro tanto dentro de una FPGA como entre dos FPGAs diferentes.

C. Para capturar una señal digital de entrada asíncrona en una FPGA es recomendable

utilizar un circuito sincronizador simple formado por dos puertas XOR.

D. Todas las respuestas anteriores son FALSAS.

Pàgina / Página 5 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

P7: Respecto a los ASICs, las FPGAs y los dispositivos lógicos programables, indica cuál

de las siguientes afirmaciones es VERDADERA.

A. Las FPGAs basadas en tecnología de programación Flash y RAM son reprogramables. Se

pueden reprogramar directamente con la FPGA montada en la placa, sin necesidad de

desmontar y utilizar un dispositivo especial, y se pueden programar de forma ilimitada.

B. La codificación one-hot permite una mayor frecuencia de funcionamiento de la máquina de

estados, a la vez que reduce el área ocupada en la FPGA.

C. La metodología de producción de ASICs basada en la matriz de puertas permite reducir los

costes de fabricación y el tiempo desde que se termina el diseño hasta que se obtiene el

chip fabricado.

D. Todas las respuestas anteriores son FALSAS.

P8: Respecto al diseño microelectrónico, indique cuál de las siguientes afirmaciones es

VERDADERA.

A. La descripción VHDL es más compleja cuando el dispositivo sobre el que va a

implementarse el diseño es un ASIC y no una FPGA.

B. El proceso de diseño full custom está totalmente automatizado por herramientas CAD que

hacen su síntesis a partir de una descripción HDL.

C. Cuando se programa una FPGA, lo que se hace es programar interconexiones entre los

distintos bloques y elementos lógicos que la conforman.

D. Todas las respuestas son ciertas.

P9: Dado el siguiente fragmento de código VHDL, indica cuál de las siguientes afirmaciones

describe mejor la funcionalidad del mismo.

A. Es una máquina de Moore con 3 estados y reset asíncrono.

B. Es un contador de 2 bits con señal de habilitación y reset asíncrono.

C. Es una máquina de Moore con 3 estados y reset síncrono.

D. Es una máquina de Mealy con 3 estados y reset asíncrono.

Pàgina / Página 6 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Pàgina / Página 7 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Pàgina / Página 8 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

P10: Dado el diagrama de estados de la siguiente figura, indica cuál de las siguientes

afirmaciones describe mejor la funcionalidad del mismo.

A. Es un detector de la secuencia "11011" basado en una máquina Mealy.

B. Es un detector de la secuencia "10011" basado en una máquina Mealy.

C. Es un detector de la secuencia "10011" basado en una máquina Moore.

D. Todas las anteriores son falsas.

Pàgina / Página 9 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Ejercicio 1 (2.5 puntos)

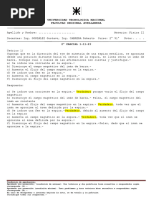

En la siguiente figura mostramos un diagrama de bloques de un circuito basado en biestables D y

multiplexores. Analiza en detalle su funcionamiento, y razona qué funciones proporciona y con qué

objetivo.

Figura 1. Circuito del Ejercicio 1.

Pàgina / Página 10 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Ejercicio 2 (2.5 puntos)

El objetivo de este ejercicio consiste en el diseño de una máquina de estados (de tipo Mealy) para

un detector de secuencia con solapamiento. La máquina de estados tiene una señal de salida,

denominada “detected”, que debe activarse a nivel ‘1’ cuando en la señal de entrada “data_in” se

ha recibido la secuencia de bits 1010. Cada bit dura un ciclo de reloj y entra en el circuito en un

flanco de subida de la señal de clock (“clk”).

Se pide lo siguiente:

1. Diseñar el diagrama de estados de la máquina.

2. Completar el código VHDL de la máquina de estados a partir del siguiente bloque de

código.

Pàgina / Página 11 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Figura 2. Código VHDL del ejercicio 2.

ENUNCIAT EN CATALÀ

Activitat 1 (5 punts)

Respon les següents preguntes tipus test amb lletra MAJÚSCULA a les caselles que es

mostren a continuació. Cada pregunta té un valor de 0,5 punts i només una resposta és

correcta. Les preguntes respostes incorrectament tenen una penalització de 0.125 punts

mentre que les preguntes no respostes no tenen penalització.

P1 P2 P3 P4 P5

Pàgina / Página 12 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

P6 P7 P8 P9 P10

P1. De les afirmacions següents sobre els dispositius semiconductors i els seus principis

de funcionament indica quina és FALSA.

A. En un transistor d'efecte de camp (FET), el flux de corrent es controla variant el voltatge a

la porta, cosa que altera l'amplada del canal per on passen els portadors de càrrega.

B. En un díode LED, quan s'aplica un voltatge a la direcció correcta, els electrons i els forats

es recombinen a la regió d'esgotament, emetent llum en el procés.

C. Un díode Zener està dissenyat per operar a la regió de ruptura inversa, mantenint un

voltatge de sortida constant fins i tot quan el voltatge d'entrada varia significativament.

D. Un semiconductor tipus N s'obté en dopar el material semiconductor amb àtoms que tenen

menys electrons de valència que el material base.

P2. De les afirmacions següents sobre els elements i conceptes comuns en circuits

integrats, indica quina és VERDADERA.

A. Un multiplexor és un circuit que compara dos senyals d'entrada i produeix una sortida que

indica quin dels dos és més gran.

B. En un circuit lògic, l'ús de portes XOR és essencial per implementar funcions de

multiplicació binària.

C. La memòria ROM (Read-Only Memory) en un sistema integrat permet no només la lectura,

sinó també l'escriptura de dades, encara que amb limitacions al nombre de cicles

d'escriptura.

D. Un senyal de rellotge en un circuit digital sincronitza les operacions de diversos

components, assegurant que tots ells operin en els mateixos intervals de temps

P3. De les afirmacions següents sobre els subsistemes típics en circuits integrats, indica

quina és VERDADERA.

A. La generació d'una parella electró-buit en un semiconductor resulta en un augment

temporal de portadors a la banda de conducció i de valència.

B. En duplicar la freqüència de commutació d'un circuit CMOS respecte a un altre de similar

(mateixa tecnologia i funcionalitat), es pot assumir que el consum d'energia també es

duplicarà.

Pàgina / Página 13 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

C. Durant el procés de commutació d'un inversor CMOS, hi ha moments en què tots dos

transistors, NMOS i PMOS, es troben operant a la regió de saturació.

D. En termes de temps de retard, una porta OR (tecnologia CMOS) amb més entrades tindrà,

en el pitjor cas, un retard més gran que una porta OR (tecnologia CMOS) amb menys

entrades.

P4. De les afirmacions següents sobre els components i les operacions dels circuits

integrats, indica quina és FALSA.

A. Un selector és un dispositiu amb múltiples entrades i una sortida, on la sortida correspon al

valor d'una entrada seleccionada per senyals de control.

B. En un circuit restador bàsic, es pot fer l'operació de resta sense necessitat de maquinari

addicional per gestionar el ròssec negatiu.

C. La representació en complement a 1 s'utilitza per codificar nombres negatius en sistemes

digitals invertint tots els bits del nombre positiu equivalent.

D. Un comptador binari en un circuit integrat és un tipus de flip-flop que canvia el seu estat

amb cada pols de rellotge, seguint una seqüència binària predefinida

P5. De les afirmacions següents sobre els transistors MOSFET i portes CMOS, indica quina

és FALSA.

A. Un MOSFET a la zona de saturació manté un corrent de drenatge constant malgrat

augments en el voltatge de drenatge.

B. En un disseny d'inversor CMOS, el transistor MOSFET de tipus P (pMOS) s'utilitza

comunament com a pull-up.

C. En una porta AND CMOS, quan totes les entrades estan enlaire (un u lògic), els transistors

nMOS a la part inferior de la porta es troben en tall.

D. Un transistor MOSFET d'esgotament normalment és conductiu sense voltatge aplicat entre

la porta i el substrat.

P6: Pel que fa als ASIC, les FPGA i els dispositius lògics programables, indica quina de les

afirmacions següents és VERDADERA.

A. Des de l'aparició de les FPGAs, sempre s'han utilitzat llenguatges de descripció de

maquinari com el VHDL per fer el procés de disseny de funcions lògiques.

B. Les memòries FIFO se solen utilitzar per transferir informació d'un domini de rellotge a un

altre tant dins d'una FPGA com entre dues FPGA diferents.

C. Per capturar un senyal digital d'entrada asíncrona a una FPGA és recomanable utilitzar un

circuit sincronitzador simple format per dues portes XOR.

D. Totes les respostes anteriors són FALSES.

P7: Pel que fa als ASICs, les FPGAs i els dispositius lògics programables, indica quina de

les afirmacions següents és VERDADERA.

Pàgina / Página 14 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

A. Les FPGAs basades en tecnologia de programació Flash i RAM són reprogramables. Es

poden reprogramar directament amb la FPGA muntada a la placa, sense necessitat de

desmuntar i utilitzar un dispositiu especial, i es poden programar de manera il·limitada.

B. La codificació one-hot permet una major freqüència de funcionament de la màquina

d'estats, alhora que redueix l'àrea ocupada a la FPGA.

C. La metodologia de producció d'ASIC basada en la matriu de portes permet reduir els

costos de fabricació i el temps des que s'acaba el disseny fins que s'obté el xip fabricat.

D. Totes les respostes anteriors són FALSES.

P8: Pel que fa al disseny microelectrònic, indiqueu quina de les afirmacions següents és

VERDADERA.

A. La descripció VHDL és més complexa quan el dispositiu sobre el qual s'implementarà el

disseny és un ASIC i no una FPGA.

B. El procés de disseny full custom està totalment automatitzat per eines CAD que en fan la

síntesi a partir d'una descripció HDL.

C. Quan es programa una FPGA, el que es fa és programar interconnexions entre els

diferents blocs i elements lògics que la conformen.

D. Totes les respostes són certes.

P9: Donat el següent fragment de codi VHDL, indica quina de les afirmacions següents

descriu millor la seva funcionalitat.

A. És una màquina de Moore amb 3 estats i reset asíncron.

B. És un comptador de 2 bits amb senyal d'habilitació i reset asíncron.

C. És una màquina de Moore amb 3 estats i reset síncron.

D. És una màquina de Mealy amb 3 estats i reset asíncron.

Pàgina / Página 15 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Pàgina / Página 16 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

P10: Donat el diagrama d'estats de la figura següent, indica quina de les afirmacions

següents en descriu millor la funcionalitat.

A. És un detector de la seqüència "11011" basat en una màquina Mealy.

B. És un detector de la seqüència "10011" basat en una màquina Mealy.

C. És un detector de la seqüència "10011" basat en una màquina Moore.

D. Totes les anteriors són falses.

Pàgina / Página 17 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Exercici 1 (2.5 punts)

A la figura següent mostrem un diagrama de blocs d'un circuit basat en biestables D i multiplexors.

Analitza detalladament el seu funcionament, i raona quines funcions proporciona i amb quin

objectiu.

Figura 1. Circuit de l'exercici 1.

Pàgina / Página 18 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Exercici 2 (2.5 punts)

L'objectiu d'aquest exercici consisteix en el disseny d'una màquina d'estats (de tipus Mealy) per a

un detector de seqüència amb solapament. La màquina d'estats té un senyal de sortida, anomenat

“detected”, que s'ha d'activar a nivell '1' quan al senyal d'entrada “data_in” s'ha rebut la seqüència

de bits 1010. Cada bit dura un cicle de rellotge i entra al circuit en un flanc de pujada del senyal de

clock (“clk”).

Es demana el següent:

1. Dissenyeu el diagrama d'estats de la màquina.

2. Completar el codi VHDL de la màquina d'estats a partir del bloc de codi següent.

Figura 2. Codi VHDL de l'exercici 2.

Pàgina / Página 19 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

lOMoARcPSD|32574709

Prova de síntesi / Prueba de síntesis

2023/24-1

Hora

Assignatura Codi Data inici

Asignatura Código Fecha Hora

inicio

Microelectrònica

M1.607 24/1/2024 10:30

Microelectrónica

Pàgina / Página 20 de 20

Descargado por Diego JA (djimenezamo84@gmail.com)

También podría gustarte

- Examen Final Transito PachecoDocumento12 páginasExamen Final Transito PachecoJuan Carlos Hernandez moralesAún no hay calificaciones

- Medición de Resistividad Mediante PlacasDocumento5 páginasMedición de Resistividad Mediante PlacasHerby Beiter Jiménez Peredo100% (2)

- SR PS 19012022Documento8 páginasSR PS 19012022pabloAún no hay calificaciones

- TF6095834 - PV IotDocumento2 páginasTF6095834 - PV IotHarry PotterAún no hay calificaciones

- TF 6077971Documento2 páginasTF 6077971Harry PotterAún no hay calificaciones

- SR PS 09012022Documento6 páginasSR PS 09012022pabloAún no hay calificaciones

- SDR PS 20210120Documento4 páginasSDR PS 20210120pabloAún no hay calificaciones

- TF 6254194Documento2 páginasTF 6254194Harry PotterAún no hay calificaciones

- EX Canales de Distribución. Ene 2022. UOCDocumento10 páginasEX Canales de Distribución. Ene 2022. UOCIngrid SanchezAún no hay calificaciones

- TF 5507801Documento3 páginasTF 5507801Harry PotterAún no hay calificaciones

- Guía de Prácticas 03-SignedDocumento2 páginasGuía de Prácticas 03-SignedCarolina AmandaAún no hay calificaciones

- TF6081230Documento3 páginasTF6081230Génessis Alejandra Chávez RoblesAún no hay calificaciones

- Parcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1)Documento25 páginasParcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1)Lizandro Carvajal RamosAún no hay calificaciones

- FundamentosProgramacion17622junio SolucionadoDocumento6 páginasFundamentosProgramacion17622junio SolucionadoHarry PotterAún no hay calificaciones

- Ingenieria ElectronicaDocumento2 páginasIngenieria ElectronicaAir SalvaAún no hay calificaciones

- Laboratorio #3 PDFDocumento2 páginasLaboratorio #3 PDFIsse HyodoAún no hay calificaciones

- TF 6077364Documento7 páginasTF 6077364Ismael YCAún no hay calificaciones

- Ex 1Documento5 páginasEx 1pabloAún no hay calificaciones

- Parcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1)Documento23 páginasParcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1)mari rojasAún no hay calificaciones

- Guía de Prácticas 08-SignedDocumento2 páginasGuía de Prácticas 08-SignedKevin DavidAún no hay calificaciones

- Laboratorio #3Documento2 páginasLaboratorio #3Isse HyodoAún no hay calificaciones

- TF 5553360Documento3 páginasTF 5553360Harry PotterAún no hay calificaciones

- TF 5893721Documento7 páginasTF 5893721Harry PotterAún no hay calificaciones

- PS - ExpresionOralyEscrita - 2021 22-02Documento2 páginasPS - ExpresionOralyEscrita - 2021 22-02retratos porencargoAún no hay calificaciones

- Informe 6Documento10 páginasInforme 6Cristhofer Stefano Perez PorcelAún no hay calificaciones

- Formatos, Casquino Ramos, Lelis (1) (2) - TaggedDocumento8 páginasFormatos, Casquino Ramos, Lelis (1) (2) - TaggedAquiles JHAún no hay calificaciones

- EVALUACIÓN DE ENTRADA - Revisión de Intentos - DistanciaDocumento5 páginasEVALUACIÓN DE ENTRADA - Revisión de Intentos - DistanciaJESUS CARLOS CHILE LETONAAún no hay calificaciones

- TF5505006 - 1 2Documento5 páginasTF5505006 - 1 2Harry PotterAún no hay calificaciones

- TF5505006 1Documento5 páginasTF5505006 1Harry PotterAún no hay calificaciones

- TF5926094 1Documento2 páginasTF5926094 1Harry PotterAún no hay calificaciones

- SD Hoja Guia 1 2024BDocumento2 páginasSD Hoja Guia 1 2024Boscarsg265Aún no hay calificaciones

- TF6074655 1Documento2 páginasTF6074655 1Harry PotterAún no hay calificaciones

- Prueba de Síntesis 2022/23-1: Esta Prueba Sólo La Pueden Realizar Los Estudiantes Que Han Aprobado La Evaluación ContinuaDocumento7 páginasPrueba de Síntesis 2022/23-1: Esta Prueba Sólo La Pueden Realizar Los Estudiantes Que Han Aprobado La Evaluación ContinuaPedro RodríguezAún no hay calificaciones

- Orden de Trabajo ElectricidadDocumento2 páginasOrden de Trabajo Electricidadbg3388310Aún no hay calificaciones

- Lab 4 Circuitos MsiDocumento3 páginasLab 4 Circuitos MsiZaleznik Dionicia López MéndezAún no hay calificaciones

- PRacti6 - Codificador y DecodificadorDocumento7 páginasPRacti6 - Codificador y DecodificadorEvelin SatuquingaAún no hay calificaciones

- TF5926090 - 1 3Documento3 páginasTF5926090 - 1 3Harry PotterAún no hay calificaciones

- Prueba N°2 2023Documento3 páginasPrueba N°2 2023ric.valenzuelaAún no hay calificaciones

- TP3 Tel2 2024Documento15 páginasTP3 Tel2 2024Carlos IparraguirreAún no hay calificaciones

- TR Diagnostico y Reparacion de Sistemas Electricos y Electronicos en Vehiculos LivianosDocumento9 páginasTR Diagnostico y Reparacion de Sistemas Electricos y Electronicos en Vehiculos LivianosJeison Aldair Nuñez PinedaAún no hay calificaciones

- 0359 Electrónica Aplicada 2324Documento8 páginas0359 Electrónica Aplicada 2324LuisMi GilAún no hay calificaciones

- TF 5551711Documento2 páginasTF 5551711Harry PotterAún no hay calificaciones

- Copia de Parcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1) PDFDocumento13 páginasCopia de Parcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORES - (GRUPO1) PDFJuan PerezAún no hay calificaciones

- TF55517241 2Documento2 páginasTF55517241 2Harry PotterAún no hay calificaciones

- Diseño de Un Multímetro Digital Basado en El Procesador DSPIC33FDocumento47 páginasDiseño de Un Multímetro Digital Basado en El Procesador DSPIC33FJosue Marcelo ChavarriaAún no hay calificaciones

- Wuolah Free 20191715161101201ES 1Documento5 páginasWuolah Free 20191715161101201ES 1ce0906Aún no hay calificaciones

- Evaluación T1 RedesDocumento8 páginasEvaluación T1 RedesAlonso MendozaAún no hay calificaciones

- Universidad Mariano Gálvez de Guatemala: Facultad de Ingeniería en Sistemas de Información y Ciencias de La ComputaciónDocumento2 páginasUniversidad Mariano Gálvez de Guatemala: Facultad de Ingeniería en Sistemas de Información y Ciencias de La ComputaciónDavid HernandezAún no hay calificaciones

- TF 6095385Documento3 páginasTF 6095385Harry PotterAún no hay calificaciones

- Glab S04 Pbenites 2024 01Documento24 páginasGlab S04 Pbenites 2024 01misael.cordovaAún no hay calificaciones

- ProyectoDocumento3 páginasProyectolaura sofia dazaAún no hay calificaciones

- CAF2 - Laboratorio 1 - 7902Documento6 páginasCAF2 - Laboratorio 1 - 7902Nicolas Av100% (1)

- Examen Parcial UnfvDocumento9 páginasExamen Parcial UnfvJohn Marin GuerreroAún no hay calificaciones

- Guia Convertidor Trifasico Ac - DCDocumento3 páginasGuia Convertidor Trifasico Ac - DCJunior CithoAún no hay calificaciones

- Micros PracticasDocumento45 páginasMicros PracticasEdison FernandezAún no hay calificaciones

- Cardex SimpleDocumento1 páginaCardex SimpleRené MedelAún no hay calificaciones

- Examen Automatizacion Sistemas de Percepcion II Parcial I 2020 Erik David CorralesDocumento3 páginasExamen Automatizacion Sistemas de Percepcion II Parcial I 2020 Erik David CorralesErik CorralesAún no hay calificaciones

- PS Inglés II - 20 Enero 2024Documento3 páginasPS Inglés II - 20 Enero 2024correcaminosbipbip123Aún no hay calificaciones

- Q2 - Silabo Micro 2023Documento9 páginasQ2 - Silabo Micro 2023Adolfo Portillo FigueroaAún no hay calificaciones

- Lab04 - Teclado MatricialDocumento12 páginasLab04 - Teclado Matricialjose valdesAún no hay calificaciones

- Sistemas de medición electrónica: Generalidades y algo másDe EverandSistemas de medición electrónica: Generalidades y algo másAún no hay calificaciones

- Normal Español Une en 60794Documento3 páginasNormal Español Une en 60794Juan Alberto Amaya HurtadoAún no hay calificaciones

- Trabajo de Investigación 1Documento43 páginasTrabajo de Investigación 1Juan Pablo Pineda0% (1)

- Estudio de Protecciones Electricas - SubEstacion 630kVADocumento2 páginasEstudio de Protecciones Electricas - SubEstacion 630kVAElMar Sebaña EnMi PatioAún no hay calificaciones

- Dossier Electricidad Muestra 9pagsDocumento9 páginasDossier Electricidad Muestra 9pagsAna ESeAún no hay calificaciones

- Manual CircutorDocumento70 páginasManual CircutorRaizen FactorAún no hay calificaciones

- Des in Frae Structur ADocumento198 páginasDes in Frae Structur AMichelle HigginsAún no hay calificaciones

- Contactos Normales Planta BajaDocumento1 páginaContactos Normales Planta BajaAlexis OrtizAún no hay calificaciones

- Informe 6 Laboratorio Fisicoquimica IiDocumento5 páginasInforme 6 Laboratorio Fisicoquimica Ii8monsalve9Aún no hay calificaciones

- Análisis de Respuesta en Frecuencia en TransformadoresDocumento14 páginasAnálisis de Respuesta en Frecuencia en TransformadoresGerardo SánchezAún no hay calificaciones

- Proyecto 2 Grupo 4Documento5 páginasProyecto 2 Grupo 4Thaily IsabelAún no hay calificaciones

- Informe Motro Trifasico AsincronoDocumento15 páginasInforme Motro Trifasico AsincronovidalAún no hay calificaciones

- Manual Curso Particulas Megneticas Nivel I y II 2022Documento122 páginasManual Curso Particulas Megneticas Nivel I y II 2022Itzel Balderas Duran100% (1)

- Nuevo Documento de Microsoft WordDocumento9 páginasNuevo Documento de Microsoft WordALA_ASLA7071Aún no hay calificaciones

- Informe #2 Ensayo en Carga Del TransformadorDocumento7 páginasInforme #2 Ensayo en Carga Del TransformadorLuis Manuel RodriguezAún no hay calificaciones

- Prospeccion Geofisica de YacimientosDocumento8 páginasProspeccion Geofisica de YacimientosCristopferE100% (1)

- Proyecto PANELES SOLARES PARA JAYANCADocumento30 páginasProyecto PANELES SOLARES PARA JAYANCARicardo Cancino0% (1)

- Informe de Robot Seguidor de LineasDocumento6 páginasInforme de Robot Seguidor de LineasDavoAlejandroAún no hay calificaciones

- Ud2 Instalac Electricas InterioresDocumento52 páginasUd2 Instalac Electricas InterioresJorge LodeiroAún no hay calificaciones

- Tipos de Subestaciones EléctricasDocumento16 páginasTipos de Subestaciones EléctricasDanielAún no hay calificaciones

- 211002-07 Rev 0 Diseño Sismico Desconectadores 245 KVDocumento7 páginas211002-07 Rev 0 Diseño Sismico Desconectadores 245 KVMatiasAún no hay calificaciones

- Informe Previo 4-L2Documento5 páginasInforme Previo 4-L2ROD STEVEN CARRASCO BENAVENTEAún no hay calificaciones

- Matriz Ficha Tecnica 150HP 6 PulsosDocumento3 páginasMatriz Ficha Tecnica 150HP 6 PulsosOswaldo HernandezAún no hay calificaciones

- Potencia y Energia PDFDocumento4 páginasPotencia y Energia PDFSaul Obando ZapataAún no hay calificaciones

- Copia de CONSOLIDADO CONTROL MENSUAL DE MANTENIMIENTO 2018Documento65 páginasCopia de CONSOLIDADO CONTROL MENSUAL DE MANTENIMIENTO 2018Alexander EspitiaAún no hay calificaciones

- 2° Parcial Resuelto para Los Alumnos (1-11-23)Documento10 páginas2° Parcial Resuelto para Los Alumnos (1-11-23)Matias Nicolas RodriguezAún no hay calificaciones

- ElectromagnetismoDocumento4 páginasElectromagnetismoRoly Marin CalvoAún no hay calificaciones

- Miller SoldadorDocumento56 páginasMiller Soldadorjapele100% (1)

- Ejercicios Fuerza de LorentzDocumento2 páginasEjercicios Fuerza de LorentzCarlos AntonioAún no hay calificaciones

- Segundo Examen Parcial - Revisión Del IntentoDocumento3 páginasSegundo Examen Parcial - Revisión Del IntentoYEHIMY CAMBAS PRESENTEAún no hay calificaciones