US011360740B1

( 12 ) Kent

United

States Patent

et al .

( 54 ) SINGLE - STAGE HARDWARE SORTING

BLOCKS AND ASSOCIATED MULTIWAY

MERGE SORTING NETWORKS

( 71 ) Applicant: UNM Rainforest Innovations ,

Albuquerque, NM (US )

( 72 ) Inventors: Robert Bernard Kent , Albuquerque,

NM (US ) ; Marios Stephanou

( 10) Patent No .: US 11,360,740 B1

(45 ) Date of Patent :

Jun . 14 , 2022

(52 ) U.S. CI.

G06F 7/16 ( 2013.01 ) ; G06F 77026

(2013.01 ) ; G06F 7/5443 ( 2013.01 )

( 58 ) Field of Classification Search

CPC

G06F 7/16 ; G06F 7/026

See application file for complete search history.

???

U.S. PATENT DOCUMENTS

Pattichis , Albuquerque, NM (US )

Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154 ( b ) by 0 days.

( * ) Notice:

A *

A

B2 *

B1 *

4/1984 Coleman

12/1986 Nelson

10/2007 Adas

12/2019 Ferger

5/2008 Mohamed

G06F 7/026

382/218

G06F 7/22

HO4L 49/30

* cited by examiner

Primary Examiner Chuong D Ngo

Related U.S. Application Data

( 60 ) Provisional application No. 62 / 984,880 , filed on Mar.

4 , 2020 .

G06F 7/16

G06F 7/02

GO6F 7/544

4,441,165

4,628,483

7,281,009

10,523,596

2008/0104374 Al

( 21 ) Appl . No .: 17/190,843

Mar. 3 , 2021

(22) Filed :

( 51 ) Int . Cl .

References Cited

( 56 )

( 2006.01 )

( 2006.01)

( 2006.01 )

(74 ) Attorney, Agent, or Firm — Valauskas Corder LLC

( 57 )

ABSTRACT

A system and methods for designing single -stage hardware

sorting blocks , and further using the single - stage hardware

sorting blocks to reduce the number of stages in multistage

sorting processes , or to define multiway merge sorting

networks.

15 Claims , 40 Drawing Sheets

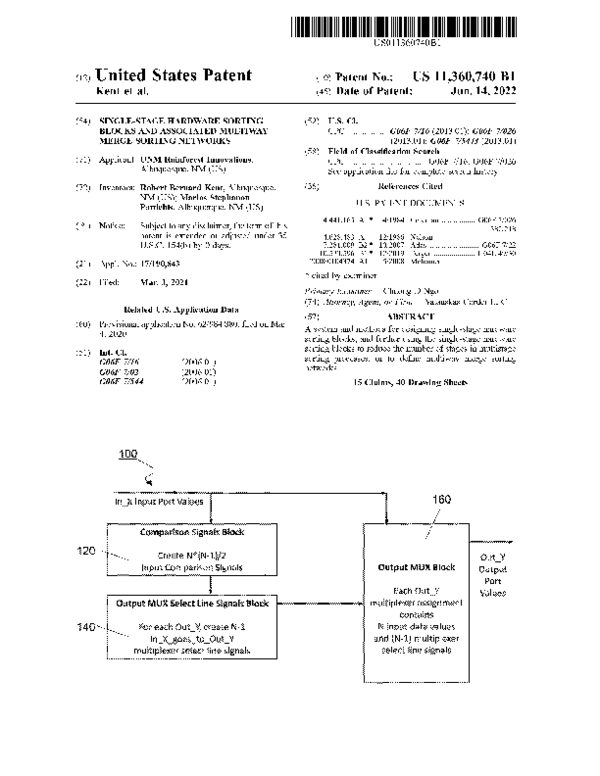

100

In X input Port Values

160

Comparison Signals Block

120

Create N * { N - 1 }/ 2

input comparison Signals

Output MUX Block

Output MUX Select Line Signals Block

Each Out Y

multiplexer assignment

T

140

For each Qut Y, create N - 1

in X goesto Out Y

multiplexer select line signals

contains

Ninput data values

and ( N - 1 ) multiplexer

select line signals

OutY

Output

Port

Values

�U.S. Patent

Jun . 14 , 2022

Sheet 1 of 40

US 11,360,740 B1

nax

Comparison Block :

One 2 - value

Comparison

Out o

ge 10

Output MUX Block :

2-10-1 per-bit

Multiplexers

PRIOR ART

FIG . 1

100

160

in X input fort Values

Comparison Signals Block

120

Create N {N - 1 }/ 2

Input Comparison Signals

140

Output MUX Block

Output

Each Out y

Values

Output MUX Select Line Signals Block

multiplexer assignment

For each Out Y, create N - 1

in X goesto Out Y

multiplexer select line signals

N input data values

contains

and { N - 1} multiplexer

select line signals

FIG . 2

Port

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 2 of 40

module sort 9 values 8 bits

# ( parameter MAX BIT_INDEX

M

w

}

(

input

input

input

input

input

input

input

input

( MAX BIT INDEX

( MAX BITINDEX

( MAX_BIT_INDEX

( MAX_BIT_INDEX

( MAX_BIT_INDEX

( MAX BIT INDEX

( MAX BIT INDEX

[ MAX_BIT_INDEX

:

:

:

:

:

:

:

=

0

0

0

0

0

@

0

:

:

:

:

:

:

:

0)

0)

0)

0)

0)

01

0)

input ( MAX BIT INDEX :=

the max value

output

output

output

output

output

output

output

(

(

(

(

(

(

(

MAX BITINDEX

MAX BIT INDEX

MAX BIT_INDEX

MAX_BIT_INDEX

MAX_BIT_INDEX

MAX BIT INDEX

MAX_BIT_INDEX

output ( MAX_BIT_INDEX

output ( MAX BIT INDEX

the min value

FIG . 3

)

)

)

)

)

1

)

1

In

In

In

In

In

In

In

In

8

7

6

5

4

2

1

1 In 0

Out

Out_7

Out 6

Out

Out4

Out 3

Out 2 ,

: 01 Out

: 01 Out o

�U.S. Patent

200

Jun . 14 , 2022

Sheet 3 of 40

US 11,360,740 B1

Start

WWW

Applying to input ports a list of N

unsorted data input values

202

Using a comparison operator to

generate result signals

204

Enforcing an order

206

Providing a set of output

multiplexers

208

Assigning, in parallel, each N data

input value to an output port

210

Outputting to output ports a sorted

list of values

212

Stop

FIG . 4

�U.S. Patent

Jun . 14 , 2022

Sheet 4 of 40

9

// The comparison signals ; " ge " for " >

1 / 36 comparisons for 9 - sorter

wire ge_8_7 ( In 8 > * In 7 ) ;

wire

ge_8.5

wire

ge 83 ( In 8

ge8 2 = ( In8

ge_81 ( In 8

( In8

wire

Wire

wire

wire

( In 8 ** In 5 )

W

M

WY

?==

**

>=

>

)

In 3

In2

In 1

In 0

WY

13

) ;

) ;

) ;

)

1128 comparisons for & Sorter

wire

wire

wire

wire

wire

11 21

wire

wire

Wire

wire

wire

ge 7 6

W

( In 7 > In 6 ) ;

M

sete

ge_73 ( In 7

ge 7 2 * ( In 7

ge 7 1 = ( In 7

ge 7 8 = ( In 7

comparisons for

ge_6 5 = ( In 6

ge_6 4 = ( In 6

ge 6_3 = ( In6

ge 6_2 ( In 6

ge 61 ( In 6

tetek

)

>

>

>=

In 3 ) ;

In 2 ) ;

In 1 ) ;

In ) ;

>

>

>*

>*

In 5

In 4

In3

In 2

In 1

topp

)

)

)

)

)

;

;

;

;

1/15 comparisons for : 6 - sorter

Wire

wire

wire

Wire

wire

ge_53

( In 5

In

w

AN

// 10 comparisons for 5 - sorter

Wire ge_43 * ( In 4 * In 3

wire de 4.2 * ( In 4 * In 2

Wire

wire ge 40 * ( In 4 * In

16 comparisons for 4- sorter

Wire ge3

( In 3 * In 2

wire ge 37 * ( In 3 » In 1

w

M

Wire

) ;

ge 30

( In 3

In

) ;

) ;

)

)

)

)

3 comparisons for 3 - sorter

What mere

ge_2 1 ( In 2 » In 1 )

ge_2_0 = ( In_2 > = In )

1 comparison

Sorten

Wire

ge 10 * ( In 1 > In

A

::

FIG . 5

US 11,360,740 B1

greater than or equal "

�U.S. Patent

Jun . 14 , 2022

assign Out2

( In 8 goes

( In 7 goes

( In6goes

( Ingoes

w

Sheet 5 of 40

to Out 2 ? In 8 :

to out.2 . In :

w

w

w

to Out2 ? In6 :

to out 2 In 5 :

( In 4goes to Out 2. In

In 3.goes_to_out_2 In

( In 2 goes to Out 2 ? In

In goes_to_out_2 In

1

w

US 11,360,740 B1

WY

4

3

2

2

:

:

:

: In_ ) ) ) ) ) ) ) ) ;

FIG . 6

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 6 of 40

Start

300

w

Creating for each N data input all

2N -1 possible product terms

302

Select product term

303

Is data input

on left side of operator

AND signal state is non

YES

inverted ?

304

NO

Assign a "win

308

YES

is data input

on right side of operator

AND signal state is

inverted ?

306

NO

Is this the last

comparison signal state

in the product term ?

309

YES

Sum the " wins "

310

Adding to SOP equation

312

Stop

Determine output port assignment

314

FIG . 7

NO

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 7 of 40

In_Succes_to_out_5 * xy S & product terms

wire

988..Sealine

?

?

?

66.8.5

?

68

ges

88

The

&&

ge 5..5

BB

&&

ga ... S &&

88

ge5 88

ses

ges

origem

seis Sock …………

&&

8

Big

age 85 8 %

ge 85 &

{

28 get 5

Be

* Le

4

se 5 && ges3

5 4 ods generalde

&

88

( !

ges

g

5 88

? : ? ?.75

&

88

$

ge 7

&&

????

B3 && ! ge2 Suite

?? }

ges

S3 && se 5.2 SS ! Be S.2. S & ge

}

265:58

$ & 5.

&& 26.5.2 LE

ge

88

g

26 5 3

}

I go 50 )

&&

se 5.2 ben

86 ge4

&&&&& ges S & ge 54

&& be

&& gens && ! B. && SS3 &&

8 & ge_7_5 88ge 5.5 : S & g 48 gen ?

} geo &&

}

2 Set 825,2 Led

geS3 && get &&

:1

}

SS.SS PRES

geri Segers 4

ge

a ! ?????

se 5.2

ge65 : Se

& Q 6.5 S &

88

ge * &&

ge4

de 7 && gens && ! Se

se

ge 7.5 88 ge5884 &

SS

ge4 82

ge7 88

ge

Se..9..2 Broase

&

get to see the

80 65 od

tewme els

& SE

&&&&& geboren &&

se 5.2

845 88 gege

)

X2

seu &&

{

!

Be ... Sirge

Seele

&& { ge75 &&

Sige

(

ses So

se & 5 8882558&

ge55 &&

8.35 88

{

??

& !

ge: 7.5 && SE 6.5 Si

g

& t ge5 So home

88

?

se 5.2 Set

gens Bosses &&

get 3 && ! se S..2

FIG . 8

??

gemeente

se 5.2

se$ }

.

iii

�U.S. Patent

Jun . 14 , 2022

module sort.values & bits

#sorameter

{

US 11,360,740 B1

Sheet 8 of 40

MAX 817INDEX

input ( MAX BIT_INDEX : 1 in

1:17

input ( MAX_BIT_INDEX ; 01 190

input ( MAX_BIT_INDEX :

At the sax value

output ( MAX BIT INDEX ; 8 1 Out

output ( MAX_BIT_INDEX ; 61 : Out..

output ( MAX BIT INDEX : 0 ) Out

the min value

The comparison signals

// 3 comparisons for 3 - sorter

wire

In

Wire

*

// 1 comparison for 2 - sorter

Wire

wyn

YAWAVAWAW

MYA

1 / Insoes to out $ 34 ] tiplexer select line signals

niyaya

VANYAYA

In goes to out ?

(

wire

In

?

Wire

In_2.goestowout .

goes to Out

ge 28 )

YAXXXVWAWA

Imastoout..2

In 1 goes to Out :

(

In 190esto out

vanyAYVA

1 / The output port multiplexer assigndents

assign Out 2

( In 2 goes to out2 :? In 2 :

{ Imagta Out2 1 IM1 Ima } } ;

assign Out

( In 2 goes to out1

( In 1 goes to out1

assign Out

( In 2 goes to Out

19

( Ilmoes to out

endmodule // sort_values.bits

FIG . 9

?

? In 2 :

:? In

Ins ) :

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 9 of 40

400

410

440

in X input fort Values

2 Logic Blocks in Series

Comparison Signals Block

Create N * { N - 1 }/ 2

Input Comparison Signals

420A

1 2 - sorter Equivalent

Propagation Delay

Output MUX Block

1 * MUX Select Line Signals Block 3 Logic Blocks iri Series

In X goes to Out Y

1.5 2 -sorter Equivalent

In Xa OR Xb goes to OutY

Propagation Delay

One Multiplexer per

Output Value Bit

My

24 MUX Select Line Signals Block

In_X_goes_to_Out_Y signals

420B - OR equation combinations of

Output

Number of Multiplexers

* N * Bits Per Value

4 Logic Blocks in Series

2 2 -sorter Equivalent

Propagation Delay

FIG . 10

sortex

dow

ROW Data

7.

B Sun

7

house

The

10

$

9

19

General Hardware Sorterembodiment

Data $ ssputs (and Outputs sss a full list Sorter)

2 Comparisons

3

goes to Out y Select inputs for Output Mix

Data inputs * In_X_es_to_Out y Select Inputs

1

3

goes to Outy Product Ferm

4

10

1

3

3 Osta inputs * Comparisons

6 Comparisons in in

2

10

2

5

*

15

2.3

23

28

28

35

3

2

7

9

3

24

23

7

HardwareSorterEmbodimentVtifixingDesign Block WithfourorEight& -BaputLUIS

finput LUTs per

goes to Out Product Terrss.

& Lagie Black Stages in Series

Sorter Propagation Delay { 2- sorter Equivalent)

3

1

2

2

3

18 inputs Per Qutput Bit Multiplexer

3

som

FIG . 11

i

?

W

?

3

3

sa

on

4

&

$

1.5 1.5 2.5 2.5 2

2

©

13 LUTS Pes Output Bit Mux ( 3* Effectively May Be a

3

2

3.

9

12

12 13

28

2

2

2

3*

�U.S. Patent

Futy Sorter: V10 - V

Slice blocks in Series

2 - sorter Propagation Delay

Jun . 14 , 2022

Sheet 10 of 40

everything

Go

Sasorter 6 - sorter 7 - sorter

3

2 -sorter -sortes

1.5

738

2 - sorter LUT Kesources

1.8

3

6.8

2 -pax

2-72x

4-1732x

S - max

Slice blocks in series

i

ju

7

3

Physh LUTS

12

Z - sorter Propagation Delay

2 - sorter LUT Resources

9 sorter

3

2

PhyscialLUTS

N - Max Fitter: N -

US 11,360,740 B1

?

2

2

13,6

67 %

24.4

9-192x

-ax

3

1.5

72

83

3.6

4,15

S

2.5

The 5 -median filter has the same propagation delay and hardware resource usage as the 9 -max filter,

AULUT resource usage numbers assume that the data values are 8- bit unsigned nunbers .

FIG . 12

210

20.5

�U.S. Patent

Jun . 14 , 2022

Sheet 11 of 40

Amor AMOWA nagore. Men onartun sousmanganmengonsumo de consomma

US 11,360,740 B1

wanaweAMWAMWAMoserMowania

// * vsorter general hardware design equation has

/

inputs i won't fit in aninput LUT

1 / combine thres In * In ** In ** signals into two In 3 OR In 2 * IN 3 OR IN 1 * Sigmals

assign Out 2

YANVAWW

( Insoes

( In 2gbes

( Ingoes

YAWA

// General Hardware

* goes Out 2

XX I

In 2 In

I www.nuoma

to Dutz ? In

:

to Out

In : LR_3 }

WWWWWWA

Desige

14-60 - I LUT Multiplexer Design

* goes to out2

IN OR IN2

to Qutz In

In 3

2

// periods ,

2

2

i

In

IVAVA KVALVAVNA

$ , replace as in the 3bove truth tables

XXYYYAA .

di Code implementation for the 4 - to - 1 multiplexers using 2 X Select links

wire

18

InLORINS.o.out.2

)

}

{

}

{

wire

In 3OR IN1 goesto out 2

{

{

{

{

wire

get

( 4:01 MEX selects out 2

In 3 OR IN 2 goes to out 2 IROR In

goes to Out 2 } ;

Aweyit MVVVKYVYVAXY

assign but *

{ mux selects out 2 ** 7 ' 5:13

( muxSelects Out2 * 7'610

mumSelects_out.2 ** ' 83

In 3 :

IM.2 :

In

Ins ) :

FIG . 13

ge

}

;

�U.S. Patent

Jun . 14 , 2022

Sheet 12 of 40

US 11,360,740 B1

1 / 5 - Sorter general hardware design Out equation has 9 inputs ,

5 data inputs and 4 x select line inputs

Commented out beloni .

11 Requires 2 LUTS , plus their connor MUX , for each output bit multiplexer

Vis

AVNAYAYAYAYN

11 assign Out 2

(

(

(

(

In4 goes to out.2 ? In 4 :

IngoestomOut.2 IBM :

In 2goes to out.2 ? In 2 :

Ingoes to Out 2 In 1 :

w

w

M

M

Ha MardeMarieMarathikitehadeMateriadeMareDorothea ...

1 LUT assignment , uto - 1 multiplexer , as in a musorter

Mara MariaMyMany MAMMA MAMAYAN...

wire ( MAX_BIT_INDEX : ® 1 LUT_8_Out 2 datafrom In 2 ORL_OR_

( 192.goes to Out 2 ? In 2 :

( Ingoes to Out

IB

M

: In

)

1 / LUTA assignment ; 2 - to - 1 multiplexer , 2 $ in @ 2 - sorter

FU VYA

wire ( MAX_BIT_INDEX :

( In

) LUTA Out 2 datafrom In11 4 OR3

goes to Out 2 ? : In

: IB3 }

1 MUXF7AB assignment ; 2 - to - 1 bit multiplexers , Inputs are LUTA and LUT outputs

genvar bit index

Eenerate

for ( bit index

B

bit index ** MAX BIT INDEX

bit index

bit index

) begin

MUXF7 suxF7 A & _out_2_1nst

bitindex 1 )

LE

.IO ( LUT_8_out data from IR_OR_2_OR_Or bit index 1 ) ,

Y

2 - bit date output

- bit data

input

bit data input

11 ( LUTA Out 2 data from In 4 OR 31

bit index 1 ) ,

SC

IR_4_OR__goes to out 2

) ) : / ? - bit select input

w

end

endgenerate

FIG . 14

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 13 of 40

// 5- sorter In OK speso Out product teras have 7 separate comparison signals

Can't Fit N single fan input LUI

// Use % wis plus their COBRON XX3X to create 7 - ingat EUT

IR_4_08__Des_to_out_2

*

(

BE4.3 && ! De42 && ! Se

..

1 &&

ws

??

de

There are non a total of 6 separate comparison signals in the BUT prwuct terns

y Common signal se

repoved will become the 2 - to - It Rhix select Signal

NYUN

Wir

LUTSELIN 4 DR .

??

DR . to Dut.

42 Be

Be

wire

CM

See

LUTE42.8 190Kbvesto

18042

SI ES

AyWynwy WANNAMYwNNAVA

112-10-3 multiplexer to finally create In 4 OR_goes to Out2 signal

wwwwww????

VAN

VV

XXXF7 PRIXF7 4 Outlast

hit data output

..206 LUTEIN 4 , OR 90 to Quta } , 32- vit data Input

3. LUTA BEROR 3 goes to Dutch )

13- it dats inut

) Hill bit select input

FIG . 15

3.1

PS Ige

�U.S. Patent

Jun . 14 , 2022

Sheet 14 of 40

9

US 11,360,740 B1

Each of these select line signals is created in the *** MUX Select Lines Blocks

They are all " OR * functions of several In x goes to out y signals

The signals for all associated sorters propagate through 4 logic blocks

NyhONNENNUNNIvanarnarnyaNINGATUNKUNNANVARena tuntunTVANGUNANNARASVATUrena

} 6 - sorter 2-10-2 Select line signal for MUXF7 in Output MUX Block

VANN

In 5 OR 4 OR

Wire

ces to out2

M

( In _ $ _ goes_to_out_2 11 In_4_goes_to_out_2 11 In__goes_to_out_2 ) ;

by MyHouse

whereas

1 / 7 - sortege 2 - - 1 Select line signal for MUXF7 In Output MUX Block

In 6 OR_5_OR_4_goes_to_out_2

wire

M

( Ingoes_to_out_2 || In 5 goes to out_2 11 In 4 goes to out2 ) ;

w

M

Wweet

MENYAWA

** A

ATUA

// 8 - sorter 7-10-3 Select line signal for MUXF7 in Output MUX Block

Viv

In / OR

wire

OR

OR 4goes to out2

M

11 In 6 goes to out_2 11

In 5 goes to out2 11 In 4 goes to out 2

AY

Matomas

/19- sorter 2 - to - 1 Select line signal for MUXF7 in Output MUX BLOCK

InS_OR_4_OR goes to out2

( In_s_goes_to_out_2 I| 193_4_goes to out 2 11 In_3_goes_to_out_2 )

w

VAAJA

// 9 -sorten Zut0-4 Select line signal for MUXF # In Output MUX Block

wire

In 8. OR 7 OR_6 goes to out_2

( In_8_goes to out_2 |

A

In 7 goes to out2 11 In 6 goes to out 2 )

FIG . 16

�U.S. Patent

WIM

Jun . 14 , 2022

US 11,360,740 B1

Sheet 15 of 40

LYAIRS.koes twout

Se1

• ?

•

?

..

de

28

??

-

??

??????? ???

se , Bus

LUygosto Ove.Rets 1.87 %

wire

??????? &

SAS

de5% 8

de 52 &&

Hege 5.2 B &

se ..

de

...

.

LU

.

{

U

.

I?

ge toosterfe751 de3 R8

?????

& !

{ ges deage

cet

?

??? .

ce 5

R8

ge

ge53 S &

ge 52. &&

Ww

de 50

.

. ! ???

sele

SE548 80

M I ??

se 53 BS

&&

53 S | te

LIT_O_ 19roes to out Agers are

wine

. ??? .

?

????? ! | Be538

A SE gemeen Best ?????

???? ..

3 ME A ????? ???

BE

??

!

Se 5

beste

ge5 .

*

{

RES

?e

&

ME

de

do Sul

?

KE | ge

1. I BE0

Be3 &&

{

• ?????

&

I gestos

??

ge5

am

Bologna

ge

ge5 && get

de Somme && Bell

ge_52 RE ! de 52

| ge

wife

teren

get &&

| ?????

e

| Bess &

gens

&

te

&S

SE

ce

&&

Re... 1

???

&&

ge3 &&

FIG . 17

getme lees

&

ge 59

F ...

)

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 16 of 40

WWWA

1 / 2 - to - 1 mux TWO LUTS with ge _ $ _ $

Il behavioral equivalent :

2 ; ge_7_5 is the mux select line

Www

MUX AB In 5 to Out5 ge851

( ges ? LUTAIn5goes to Out5ge5 Inge751

: LUTBIn5goes to outgesige ? ..50 ) ;

ht

ht

Me

wire

MUX_AB_In _ $ _ to_out_5_be_8_5_S

wers

MUXF7 muxF7In to Outwee 8 minst

(

OP

MUX_AB_In_5_to_out_5_ge_8_5_1

),

.IO ( LUT B In 5 goes to Out 5 ge 85 1 ge 750 ) ,

M

.11 ( LUTAIN 5 goes to Out 5 mge851ge7 . ) ,

M

ge7.5

. (

//111 - bit data output

11- bit data

1 - bit data

input

input

) ) ; // 1 - bit select input

WAV

1 / 2-10-1 MUX

ge_75 is the mux select Line

TWO LUTS with ge_8_5

NAVIY UNAONYVANNYNN

wire

MUXCOIn Sto Out 5mge850 ;

MUXF7 muxf7 In

(

to Out 5 de 850 inst

output

MUX - COIN.Qoutube

IO ( LUT_D_In_5_goes to outsge_5_cute

) , //1.bit data input

« I1 ( LUT In 5 goes to out s ge5be751 ) 11- bit data input

ge 75

Dit - bit select input

SC

V

1 / 2 - to - 1 mux

wire

combine the outputs of the 2 muxes above

using ge 85 as the mux select line

In 5 to Out 5 ;

MUXF8 muxF8_In_5_to_out_5 inst

(

)

.00 In 5 to outs

.IO ( MUX CDIn to Out 5uge850 ) ,

I1 ( MUX_AB_In_5_to_out_5_ge_8_51 ) ,

50

ge_85

11- bit data output

// Inbit data input

111 - bit data

input

) ) ; // 1 -bit select input

FIG . 18

C

�U.S. Patent

Jun . 14 , 2022

morethan the onetothe tow Matutessasi tantointhewomen and the

US 11,360,740 B1

Sheet 17 of 40

AYWAXAAWYrity VAT

// * Sorter Out 2 Output Multiplexer LUTS : Behavioral Code

* A

wire

WAYAW

MAX_BIT_INDEX < 0

In 2 goes to out_

{( In goes to out.22

LUT_B_out_2from1n 2 OR 2ORE

In2

In 1 In ) ) ;

0 1 LUT A out 2_fron In 5 OR 4 OR_3

In 53

M

( MAX_BIT_INDEX

( n goes to Out

wire

Were

( IN_4_goes to out 2

wire

WA

In 4

W

| MAX 817 INDEX ;

LUTC Out 2 from In_8_OR_7_OR_6

}

( Ingoes to Out 2 ?

( In

goes to out 2. In7

w

I swear to thesite with thesame strutturation

surturatura

19- Sorter Out

In 6

)

BENANNTMuantum OVOAREwanguNatvaSVARENAVA

Output Sit MUXF * s

Structural code in a generate block

MUX ABOut_2

MUX CD Out2

MAX_BIT INDEX :

wire

In )

Benvar bit index

generate

for ( bituindex

bit index < = MAX BIT INDEX

YA

bit_index

bit index * I.

;

}

MUXF7 HUXF7AB Outminst

?

bit index

06 MUXF7AB Out 2 (

output

),

bit data iaput

104 LUT & Out 2 from In 2 OR_1_OROC bit index 1 )

* 116 LUTA out__from_In _ $ _ OR_4_OR_31 bit_index 1 ) .

2 - it data Input

In_S_OR_4_OR_3_goes to 013 * 2 ) ) ; // 1 - bit select input

{

UIXF * * uxf7 CD Out Inst

bit data output

.O ( MUXF7 CD Out 2

bit index 1 ) ,

)

18 ( 1'60

1 bit data

input

11 ( WTC Out 2 from In 8 OR 7 OR 6 ( bit Index )

?

?

M

V

.

+

Bli Xbit select input

- S { vbi

MUXF8 muxf8_out_2inst

?

101

Out 21 bit Index ) ) ,

MUXF7_AB_out_26 bit index ) ) ,

MUXF7 CD Out 21 bit index 1x

.58 In8 OR 7 OR 6 goes to Out 2

end 11 for ( bit index =

endgenerate

FIG . 19

11- bit data outout

// 1 - b1t fata

bit data

input

input

!! Lbit select input

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 18 of 40

WNA

X ! The behavioral code for these & LUT equations seeds No sodifiuition

???

?

VUNA

AMNVIVAVAA

wire ( MAX_BIT_INDEX : BLUT AQUtember 20111

wire ( MAX 811 INDEXILUT 80ut22e21e_22110

In 2 : ?

wire [ NAX_BIT INDEX : 91 LUT out 2e 3.2ge 2 se $ 101.

ge

Y

182

In 3 : In B ):)

In * ; IRB } }

wire ( MAX SIT, INDEX :

LUT QUtge0198

Ini ( 1 gemini

Wir ( MAX.81YWINOEX :

LUTE_QUt2be2ce20_011

wire ( MAX_BIT_INDEX :BLUTOUTER

ge

IN

mbele 2010

Ini

2BIN 2 :

)

wire ( MAX KIT INDEX ON LUT 0 Out our

otele 12.601

wire [ MAX HIT INDEX

*

0

LUT QUE

1.

BOB

UNAM

1 ! The behavioral code below needs to be replsced with separató wire declarations ,

3 generate block , and structural instantiations of MUXF7 / 8 / 9 primitives

My www.marathon

wire I MAX KIT INDEX + @ MUXF7 48 Outugemeen 31

(

18 ? LUT QUthege.222.6112 WY_2_006_22_1110 ) ;

wire

MAXSIY INDEX :

MUXF7Cooutware

2.8

{ eenB ? LUTE DutmaBehandelmed

IAX - UT . Outween these menee

100 )

wir ( MAX 817. INDEX ;

MUXFY.EE Out22ge 2202

C de 10 LUTOst.

Zwembe

911 : { U10e220_018 )

wire ( NAX_BIT INDEX 10 MUXF7GH_OUE2_32_2_00

ge1

LUT &Oute

12.61 : LUTH0012.ge 3.2.2.133.686

Waar was

wir. ( MAX & IT_INOEX :

MUXF & _ABCD_QUt22

bet ? MUXF7.AB Outube

23.11 : MUXF7.COout Zeemee ? 19 )

wire ( MAX_BIT_INDEX : 0 MUXF8EFGH_outer 20

6 se

MUXFT.ET QUtemile

BB : XOXF75_outube 60 ) ;

assign Out

M

? be

? AUX $ & ABCDsteem

MUXF8EFOHLOUBE

FIG . 20

�U.S. Patent

?????

Jun . 14 , 2022

?? ??

?????

US 11,360,740 B1

Sheet 19 of 40

?? ? ?? ?? ?? ?

???

???? ??

SV pseudocode ; Frog Bevious examples , one skilled in the 3rt can implcrent

“ wiren seclarations as needest

" assign statements as needed

a generate block as needed

muxe * structural instantiations as needed

????? ?? ?? ?? ??? ?

1 / 4X

?????

???? ?????? ?????

// Investo.Out.my ana

* signals always have a hit width of 1

19 10.2mg04.20_03- ( 13.2

// in Lugoes to our m3 (

w

(

# These bit output multiplexer signals 311 wave a bit width of ( MAX BIT INDEX

LUT0U _3_ge_3__

LUT Out

* { { ge

, se 2

B } ** *** 11 ? IN

)

; ( ge

IM 2 : IN 3 )

{ ge_32 I AYA_Out sugo.03.23 : LUT. 8.01.3.3.3.28 )

????? ??? ?? ?? ???? ?? ??????? ?? ?? ?? ???? ???????? ?????????

11 : 38F7A3.09.03

???? ?? ?????? ?? ?? ?

1 ! The wak In moesto_Out signals and states can be put into the following diagram:

s / for readability

// www

BT state is shown as an * tote

VAM

& B

88

M

A

2ID

2

1 / ????

-Bir

?? ??

// InX.gies.com.out ... and gen signais always have a bit width of

VAUVA

M

// In tagoes to_out wax t

17 is Daroes towtw (

// These bit output multiplexer signals 311 have a bit width of ( xAX_BIT_IKOEX * * }

LUNA_Out3.25138 )

LUT80Uere

{

32

21,

20

2008 ? 63 : {

2288

E.

In : The ) ) .

IN 2 : IB

(

? In

AUTUBoutube.3.3. LTA ...

Mt

20 )

FIG.21

An

Ins;

* UXF7A8 Okt

�U.S. Patent

! ????

5V pseudocode

Jun . 14 , 2022

US 11,360,740 B1

Sheet 20 of 40

?????? ?

???? ???

from previous examples , one skilled in the art can implerent

" wire ” declarations as needed

" assign statements as needed

generate block as needed

MIX * STIC ??? ? ? antiations as needes

1 / ???? ????????? ?? ???? ?? ????????????? ???? ???? ??? ? ?

1/ 5

?????? ?

?????? ?? ???

// wwwww ~~~~~

// Far reatsbaitys a ' a ' state is $ rown as an " E " state in the Following table

// ge__3 will be the MUXFB select line signal

// Set will be the select line signal for the two UXKZS

??

4444 335 22

*

?? ?

?

11

a

LUT_A_QUt__ee_22_11

( ge_26 ge48 ) **** 612

IN 4 : { ge 2

LUT B_out 4.04.3.08.2.1.18 %

1 go.2,48 ) ~ 26 7 10.4 1.10

In 2 : 10 )

10.10.0 ) )

MVUMA

LUT_ Outube_01 (

2. ge

** 2.611

AUTO_out 4. ga 4.3.8.2.3.00 % { { ga 31 go.38 )

IN

: ( 80

20071R 3 : { e.

In

: IRO )

Int : 100 ) ) ;

UXFT_AS_Quttages sui. * ( 22 ATALONE 48.3.21 147 BLO.3.2.1.15 )

UKFY.CO. Outw4.ne4.3.8

.

( de 22 ? LUTC_Out_40_4_1_2_01 ; LUK0 Out_se_2467 ) ;

winyim

MUXF & _ABCD_Out 4

* (

43

NIKEY_AB_0xt_4.age_4_31

MUXF8 ABCD OUT

FIG.22

�U.S. Patent

US 11.360,740 B1

Sheet 21 of 40

Jun . 14 , 2022

<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<

SY Scade ;

“ ? ” ? “ ?? 5

, ?? ? ratest ? ? ?? ? ? ,

<<<<<<

{ { AAAAAAAAAAA

B- $99x

?? ???? ? ?

????AAAAAAAAAAAAAA

<<<<<

AVAVA

?? ? ? ? ?? ? ?? ??

:

? ? ? ?

? ?

?

? ?? ?? &

??

23:33

????

4

??

82

??

,

YVAUVAVAVAVAUVAUVAVAWTVA

? , ??? ? , ??

?

?

? ? ? SA

.

? ? ???? ?

& x

11 In_5_goes_to_out_7

_7.g ? ? _ ?? _it ?

?”

? ? X ? res 2

?? ,?? .2 .? O S , ..

?

? _?? _3ge5

Ret_ ?

wmowarewmunowmowmowma

53???

?? ??? ? X_ ???

? ?? ? ???

select line For MUXF7

select line for MOXFS

tva

??3.7 IT &

5.7.8

AB Out

ABCO QUE

VAIV AV VMVVM

// Output

MUX Blocks signals with bit width

AppMyA

( MAX BIT INDEX

)

? ht?

_ ???

?

?? ?? 2 ° ? ? ? 383 ;

Kiez ? E_RE ... xxz' ? ? ? ? _3 :

3 ? ? ? ecs_f7_8 ? ‘ :: ? ; ? 8

LUT A out7

( ? 5.xo?S. Cruit_ ??3:41 :

w

?

? ABSAY . ?

?

{

RAVES & St_7387

STER

{

MUXF7 CD Out7

" Xv8xt . AT :

? :

) ;

I 8.7} ;

. ;

???? Y_C_ ? ?

VXKANA

{

7 VR_5_0& x.g :

SRF7.ht

FIG . 23

? XF8_AP #ext_ ?

: ??7A8_out ) ;

�U.S. Patent

350

Jun . 14 , 2022

Sheet 22 of 40

US 11,360,740 B1

Start

Providing hardware N - sorter

352

Removing unused output and

related logic

354

Creating a single stage hardware N

to M filter

356

Stop

FIG . 24

�U.S. Patent

Row

7

6

5

3

2

1

Jun . 14 , 2022

Sheet 23 of 40

3

2

1

32

28

:24

31

27

23

12

15

11

30

26

22

18

7

3

29

25

21

13

quran

US 11,360,740 B1

qis the sequence number

Nrows 8

No Ncols * Nrowse = 32

Top row (NrowEp )

Bottom rowo

Left column ( Ncols - 1 )

Right column = 0

FIG . 25

Symbol

Dention

Equation ( 1 ) Parameter Definitions

The total number of value to be porta in the All UCMS Network

The number of sorted lists to be irierged in each UCMS merge sequence

The number of columns in a UCMS rectangle

The sumier of rows in the sequence 0 2-0 irray 3 Nruso Neols

Each column of the Sequence 0 2 - D anlay is sorted by an Nrows sorter

Pina 1 1 : The muniber of the merge sort sequences in the network

SCPJURCE fissi is the last sequence in thesouting network

Rectangle Definitions, q > 1 See t'te figureimmediately ahove

The number of values in a Sequence q rectangle

Na

Nrowse

The sumber of rows it a Sequence iz rect3ngle:

Num rectanglesa

The number of rectangles in Sequence a

Time and Resource Units for Sorter and Network Normalization

3-surter Equivalent Ime Propagation delay of one 2- sorter, or of a stage with only 2 - sorters

2 -sorter Equivalent kse Resources used for a 2 - sorter in i purticular hartware type

Unified Column Merge Sort, this sorting network systein

FIG . 26

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 24 of 40

The original list of 32 unsorted values for the 4 -column UCMS example is

22. 2.8 38 25 33 33

17 16 31.923 39 24 27

22% 24. 2. 25 27 25 25 26

Sequence 0 : Unsorted List of 32 into 16 Sorted Pairs

8

3rd

moramo

11 30 2

*****

18 29

1

3

6

23 24

3

5

1

2

722

13 14

25 15 28 6

6

4

8

Paired But Not Yet Sorted

16 15 14 13 12 11 10

1

9

8

1

2

3

1

13 22 25 172&

9

31 10 16

5

8

20 24 3

Paired And Sorted

Sequence 0. Stage 1 : Unsorted List of 32 Broken into 16 Pairs ; Pairs Then Sorted

FIG . 27

Sequence : Four 2 ROWS * 4 Columns Rectangles

Merge Sort Stage flow is from top to bottom in Each rectangle Column

NIC : Row /Col Deltas Between Successive Diag Salsations

3

1

ROW

3

18-30 532

2

3

12. 19 -

0

0

Row

23

1

3

27 ppi $ * 13 * 22.

24. 3*** 14

0

Row

3

25mph 1730 * 3

Row

3

3

Sequence 1, Stage 1 : Build Four 2x4 Rectangles and Sort Al Rows

ROW

RON

i

5

1

1

+

3 2

ž

231932

3

20 16 10 1

29 31 2.

***

i

3 2

27 32 33

a

28 : 25:17

0

0

26 21 15 6

How

3

3

0

28 262135

Sequence 1 , Stage 2 : 1/1 Row /Column Oiagonal Sort

Row

1

0

2

i

ROW

32 31 29 11.

2

3

How

2

1

1

19

1

0

3

2

1

3

25. 178

0

22 13

Sequence 1, Stase 3 : 1/2 ROW / Column Ojagora Sort

RO

3

1

8

32

3

2

Row

3

1

1

2

3

2

i

2.7 34 22

Row

23

2

1

2

21. 258

Sequence 1 , Stage 4 : 1/3 R / C Diagonal Sort ; NG " Intkowi Sart Since Threre Are No Interni ROWS

3

1

2

$

31 30 29

S

2

Row

3

3

2 2

28 26:25 21

2

1

0

1.2.

1.

13 : 3

4

3

Sequence 1 Complete : Each of the four 2x4 Rectangles is Now Sorted

FIG . 28

:

3.7 25

6

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 25 of 40

X Columns

Sequence 2 Merge Sort Final Rectangle . S ROWS **

Stage flow is left to Rigist: Starting in Top Rectangle: R13W

2

7

?

0

Row

3

2

5

31/25/24/20

30/25/2219

6

31 29

18 717 / 13 12

15/31/1077

3

38

35

29 721/16/14

9787574

2

3

?

something

32 30por27 : 23

32 28 27 23

2

1

1

7

2

heretoget

7

3

3

3

1

How

7

3 2 3 0

32 31 29 26

S

27 21 21. 19

23 20.12 1.4

3

2

3

0

30 28 25.2 %

..

38 362312

6

www

2

Stage 1 : Son All ROWS

Stage 2 : 2/1 R / C Diagonal Sort Stage 3 : 1/1 A / C Diagonal Son Stage # : 12 0 3gons Sort

Kow

?

ROM

3

32 31

3

7

2926. 27.24

6

5

3

3

w

...

32 31 30 29

R / C : Row /Col Oeitas Between Successive Diag Selections

24 23 22 21

20 19 18 17

Stage 5 : The Last Stage in Sequence

Includes UCMS 1/{ Ncols- 1 ) R / C Diagonal Sort

28 27 26 25

2

2

5

3 2

a

3

3

2

1

Stage S : 13 Diagrirtkow Sort $ 49.2 Done : Sorted Order

Also , includes " intkowo Sort

For uven Ncols values > 2. Iritrow Sort in Last Stage

{aturnal values of a row are sorted, frosn 1 to { Ncols- 21

FIG . 29

Anternal rows are sorted from 1 to NOWS - 2 }

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 26 of 40

The original list of 9 unsorted values for the 3-column standard UCMS example is

4 6 9 2 7 1 8 5 3

Sequence 0 : Unsorted List of 9 ; 3 Lists of Length 3

ROW

ROW

?

2

1

7

11

5

3

2

1

9

***

6

WA

2

Lists of 3/3/3 Built But Not Yet Sorted

5

pther3omotion

1

Lists of 3/3/3 Built And Sorted

Sequence 1 : Final Single Rectangle With 3 Rows x 3 Columns

Stage Flow is left to Right , Starting in Top Rectangle Row

R / C : Row/Col Deltas Between Successive Diag Selections

2

1

2

2

2

1

1

..

awa

7

6

2

2

9

I

8

Stage 2 : 1/1 R / C Diag Sort

Row

0

2

1

0

1

2

Stage 3 : 1/2 R / C Diagonal Sort

3

2

??

Stage 1 : Build 3x3 Rectangle : Sort All ROWS

1

ww

2

3

6

S

4

3

2

1

tuk1

Final Sorted List of 9 Values

FIG . 30

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 27 of 40

The original list of 8 unsorted values for the 2- column standard UCMS example is

4 627 3 1 5 8

Sequence 0 : Unsorted List of 8 Into 4 Sorted Pairs

Paired And Sorted

Paired But Not Yet Sorted

8

Row

C

2

5

19 11 1

1

1

7

B

6

8

8

2

tout

Sequence 0 Stage 1 : Unsorted List of 8 Broken into 4 Pairs ; Each pair Sorted

Sequence 1. Two Z Rows x 2 Columns Rectangles

Merge Sort Stage Flow is from Top to bottom in Each Rectangle Column

Sequence 1 : 2x2 Rectangle 0

Sequence 1 : 2x2 Rectangle I

ROW

1

o

Raw

1

0

1

how

0

I

// 6,4 swapped

2 m

// No change : 3,1

Sequence 1 , Stage 1 : Two 2x2 Rectangles Created ; Rows Sorted

?

Row

0

// No change : 4,3

1

11 8,5 swapped

11 7,2 swapped

0

1

// 7,5 swapped

@

Sequence 1 , Stage 2 : Two 2x2 Rectangles: 1/1 Row Column Diagonal Sort

Sequence 2 : Final 4 Rows x 2 Columns Rectangle

Stage Flow is left to Right , Starting in Tao Rectangle Row

R / C : Row / Col Deltas Between Successive Diag Selections

Raw

3

1

1 / 8,6 swapped

47 117, $ swapped

3

5 1/5, 3 swapped

Row

&

3

2

>

1

@

1

G // No change : 6,5

1 No change : 4,2

entrega l} 7 , 1 swapped

Sequence 2 , Stage 1 4x2 Rectangle ; Sort Rows Sequence 2 , Stage 2 : 2/1 R / C Diagonal Sort

Row

3

.

1

I

8

0

-

2

// 7,6 swapped

Row

3

2

// 5,4 swapped

I No change : 3,2

Sequence 2 , Stage 3 : 1/1 R / C Diagonal Sort

1

7

mw

junih

0

2

Final 2.Column Sorted List of 8 Values

FIG . 31

�U.S. Patent

Jun . 14 , 2022

Sequence Number of

Number aq

Sorters

0

Nrow so

US 11,360,740 B1

Sheet 28 of 40

Nrowsq in

Sequence a

Number of

Rectangles

Num recanglesa

Nfonul

91

Nfina !

NrowseNcols

Nrowse

Nrow50 * Ncolsa

FIG . 32

450

Streaming Results

Data Qut

Dat Out

I

?

Control Streaming

Datos

460

Streaming interface to Host Comite :

Sorted Datannit

List Length - Napo?

Urisorted Data in

480A

UCMS Sorting Network Top Level / Data Transfer Wiring

470

Sequence 0 : 1 Stage

Sequence 1. Nools Stages

Final Sequence has I Rectangle : Morfirin Nools * Nrowsfiro!

Number of Stages

- Acols + CEILINGI logg{ ASOWSER !! Hcols ) }

if Final Sequence is not Sequence

FIG . 33

480B

490

�U.S. Patent

US 11,360,740 B1

Sheet 29 of 40

Jun . 14 , 2022

Vools , the number of lists to be more and columis in the rectangles .

1 Vrons , we mumber of rows in the Sequence 2-0 array ,

!! Njinné , the number of values in the input wnsorted list and output sorted list,

sapsar: The

the last serience swier ; ( fierad .

list of None suosien valses

Output: The 3 -d list of Mana starteri values

s Transfer input - list of Nancé unsorted values to Sequence 02 -Harony :

1/ Seovec 2-8 array kas Arown, rows and anal / Nrows ) columns

2 In Sequexe soxt auk solurn of the as array with as Vrows series ;

The siminun velve in each column goes to row $ ; the maximum goes to row ( Nronisp : 1 ) .

1 / Nox selam Saquence merge sort .

3 Set sequence yamahl

* Wrows = : Krows :

s Vum rectangless Ninas/ ( ww ; * Munis ) .

* sepseat / process each wea sort sexquence

Use 2-4 array from Sequence ( - ) to create a recangles rectangles in Sequenca:

**

1 ! Each group of Vous columns in Sequence (0 - 1 ) array produ one rectangle

Process the reciznglés tough the stages ofSexe Q :

Transfer sorted data for the Sagenes en rectangles to the Sequence output 2mmy :

11 TM sorted we values in each rectangle become a column in the output array.

it 92

the di sotsp the nextstano

Q

Nrow traw . * Veuils ;

Num reconglese Num_recanglesq- 3 /Nols ;

end

is until 3 * Ons

17 The output array from Sexuance si fisuri has sinus roks and 1 colum .

36 Transfer the single onlum of Sequence gjinal output data to the inal - list of fina sorted values ;

FIG . 34

UCMS Standard Sequence 2 Stages With Column Delta and Intkows Specifications

Cousin Delta

5

3

2

Aš dows At Rows Ad Rowi AB Rows 8}} Rows

3

Nous

A

Noots - 5

Neais 4

Nous

drols

Inthous

8

Nicols

ROWS AB ROWS A Rows servering 18štiat Row Sort

2013 Howcal Diag

Rowico Dias

? ??

Howycol Dias

V2

282

1/3

1/5

1/6

V3

24

? ?

HuwCol Disg

Rowicol Bag

How /col Días

Row / cobias

Intdows

? ??

Howy w Bias

?

Fina Row sont

The last 2 (Ncols - 1 } rows both refer to the last stage in anymerge sort Sequence et , with a

FIG , 35

�U.S. Patent

Jun . 14 , 2022

Num . Max

Sort Sort

Row

3

3

thW

81

MC Diagonal Stage

16 831 4.1 21

he

Sequence Mrows Columns Rectangles Stagesa Desta , Cols Rows 32

0

US 11,360,740 B1

Sheet 30 of 40

3

2

AWAN3

3

.

?

w

tu

S

:?

YA

16

16.

20

22

3

18

FIG . 36

The original list of 8 unsorted values for the 3 - column non - standard UCMS example is

4 6 2 7 3 1 5 8

Sequence o : Unsorted List of 8 ; 1 List of Length 2¡2 Lists of Length 3

2

2

1

2

A

1

7

S

2

word

mm

3

2

a

7

5

8

6

1

Lists of 2/3/3 Built But Not Yet Sorted

Lists of 2/3/3 Built And Sorted

Sequence 1 : Merge Sort of Final Rectangle

Stage Flow is left to Right , Starting in Top Rectangle Row

R / C : Row / Col Deltas Between Successive Diag Selections

2

Row

ROW

1

0

5

2

1

2

2

1

3

0

Stage 1 : Build 3x3 Rectangle : Sort All Rows

2

ROW

2

3

2

Stage 2:11 Diagonal Sort

2

1

2

7

3

an

1

2

1

0

1

Stage 3 : 1/2 R / C DiagonalSort

w

6

3

3

8

7

2

3

Final Sorted List of 8 Values

FIG . 37

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 31 of 40

sodule 1685 network Hals N final. 32 Miss Bits .

values in lists

input (781 input ansertendist che dimensimial ( 31 : 0 1

Output (

output some list

* bits

wire ( 7 $ 1 #sartelists

dimansional { 31 : 91

for secure

wire to sorted distribencz

X

wire ( 7 : 8

sorted lists

wire 17:01 sorted lists with

% CWS

16 coixis

1:15:01

{ : 1:01 { 15 ; 0

from secience

( 72

from sequence

[ 32

sequence encols 4.4 Final 32 Nike S105

3

8

3380HS

[ : 3 : 13

1 colu

32

]

SpieNic.instance

&

)

ir data for sequence of ansörteist 2 timenet

}

out data from: seguence of sorted listrom serience

Spisnice I int *

sequence 3 Ncols 4 x final 32 NER its&

in tata kr Sekilence 3 (

sorted Lists

from sequence

out data from_sequence2

sostenlists

from sequencement

samedli** . 21mm sequence

spiritistait

sequence 2 kcals

final 32 Num dits8

In data for sequence 2 (

501960sts

from soovesico

out data from seguonok

;

*

}

3

one 11155_index

203VBI

generate

for { One 1355

one 21st

Selist

1 / 83for the

to the 2

Index

index >

one

3st Index 1

index

norted Input list

Input array used in Sequence 33

py there are 2 r $ 65 9 14 colcAM

in the Secrience

array

assign unsortex lists 2 For Sequence I

list index 16 ( osie : list_index. % 15

issukcesorted List one dimensionall one 1st Index ) ;

14 trasfertso sisgis so Ihad prasis the last sequence - output, array

to the 3.- Sorted output list

ASSES sutsutsorted_list_one dimensional ( one listindex

sorted lists2.requenc . {

15kmine 1 { }

end

endgenerata

dadurch

FIG . 38

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 32 of 40

module sequence_oNcols 4 N final 32 Num Bits &

tjeje

hi

8 bits

2 BW'S

input ( 7 : 0 ) in data_for_sequence_

( 1101 ( 15 : 81 ?

output ( 7 : 0 ) out data from sequence @ 11:01 | 15:01

col2013 index

genver

generate

1 Instantiate the 16 2n sorters

for ( Column Index

Column index

column_index

15

colum Index - 1

sont z values 8 bits

(

Y

begin

sequence o sort 2

In 1 ( in data forsequence

Int ( in data for sequence

8x value

( 11

1 )

Out out data from sequence ( 1

Out ( out data from sequence

1

A

M

nin value

endgenerate

andaarule

FIG . 39

column index 1 ) ,

column index 1 ) ,

>

column_index ) )

column index ) )

1

�U.S. Patent

Jun 14 , 2022

US 11,360,740 B1

Sheet 33 of 40

R8yg3 $$$$$$$$$$$$$$$

43zh _ { { ……

& & xts

??? tp *

{{

* **}

???

833814

***

{ $o $

RK? # # 3 # # # # # # # # 3

{ " st_333 { * * * } { } } } }

&

f

888*

, ?????_ { ????? ?

Generste

for ( rectangle Index

?? ?

%f

wire

xxxe

Wg

{ { :*}

{+ : 1

( 7:01

{ } ;#}

+ : #3

X

{ fews

$$

{ { :} } { } }

* ?????? { : # # # # 2

diagtdata 11

(

( 3

???????????? { { : # { $ ;

?

30 ? { { ; # } { } ;

$

Stay

4 ; } < 3g_sex++ } & ? gs

* ? "C33gessex

? xt

#}

#

#?

#}

a

}

:

:

;

}

{

?? p ? £ ata

}

tt Sq ?:???? , # ?* , fry Set -

seq_2_row_sort_instance

{ $$$tage

( qYg % 81

{ " S ** { ata } . $$$$$$?ata { $$$

?? $

???? 3 ,

6 ?? , ??.?ds stage w?} Jow sex3 1 > text{} ? ets

seq_dial,22 instance

sele

stage

{ , … { { { sta{ $$$$ *** ?? t } } ????? :

ata { ? &

(

? 3

seguancay stage diagonal stage with row delta

3 ??

???sta?? *

$

??????? *** ????

{ , ? ags_? atafosts

{

} } .???

ts { ? g

SexNCK I , stage A , last stage in sequence diagonal stage with R/ C

??????ag_33_ {sta?

Seg_ ???????

{ » 33 & _433{ d À

¥ ts } } 14384 3 3 dkdata 413 4

$ { {

? ata } }

& 1

3xas } }

* *

?? das } }

3/3 3./(KCOLS-1 )

3 ??t data } } ;

{}

???????? ??? ?? ??? ? ?? ka

3

{ 3 } { CB_Xxx

;

?? K } & ;

??

??????

* * ??? > > ? . * ; }ssss8X

<

»• } {3 }

split off 4 Colsons from sequence Input data to rectangle ros_sort_11_486x rray

? sig? ? 5

? ka { fr ????? } { { { ? K

In data for sequence

CW_index 1 Col index + ( rectangleIndex * XCOLS ) } ;

XXoay the final sorted data from this rectangle into & single column of the output data

? $$$ { {? 3 day' ??????????? { { ???????? *

& } } { { ? } { " Eag{ { { X 3

? a { { A ?at { {

{ x { { $ kxx ex } }

3

essed IX END OF " for rowindex

ex? {

??? {

?

* 3* { [

??- ' Kur { ' ?????

k ??? .

3

??? RK, * * ;

*

????????? '

?????x3

FIG , 48

�U.S. Patent

Jun 14 , 2022

US 11,360,740 B1

Sheet 34 of 40

#xatu ? ? quit_K??.1_4katW A8

%

& its

(

?? $

{ {RAY { { } } &

??? t &_fast2 {

? utput { ? : ? } ???? $ # @YC & 2 { } } } } { } : 8 3

p3 "????? "

Rectangle_index , colindex , row insiex j

generate

0 ; rectangle index

for { rectangleindex

3 { ft .& # xxx++ } … .

8 bits

wif & } 7 : 3 ft Sorts ?? : { * * * }

Kir { ? : } f ? KSp ???? ts { ? * * }

{ re {

& 3?????ta { } : # }

e { } } } } ? 3330 * 4 ta { } # }

. ” { } } } } ????? { {???t? { } :

?.? { + 1 8 3 ?????ts { * * }

{ { start with sequence 2 , stage 1. row sort

$$$?ste ????

{ . % $$ *

{

{

{

{

*

#

# ( 133

3

3

$

3

3

#

:

:

;

:

:

#

#

{

#

8

#

1

}

}

}

}

}

#

}

}

}

;

SAMSKRs13

{ fo $ +k ???? } } , ** $

??? { f

{ $²q? nce 2 , Stage 2 , ???????? stge w?t f? ? 33 * 1 , cg3

?

3?*3

$ ??? aÁXX3state

????? xst

pagate

????24_ Gu ? ata { ?? A

{ ,????33_3_data{

$

sequence 2x stage 3 , diagonál stage with row delta

, coluniss delta

2

exastage

$

{ ??? ?8

??: ? a } }

? k_e?? } }

???E_1_3_{ 3 { ???

ats { ?????? ??? }

>

??????? { ?????

a } };

/ ? sequence 2 , stage ay diagonal stage wi03 A delta = mw coll delta

$

ia2k3st333Cg

???????????????

{ ?????

?? { ixGf4a

?

; } - ??????

SWX_ { ?????? } }

} gitte * stage … , 1st stage 2 ???€xact : ????? $ ?????

• 1 t { { NKH53 )

$ ².81stHg

aist?RE

??.

;

{ + 44838xta { 41444fa3 } ??

+

gu ? ad { ????? } }

1 } xap sequence input and output okta

fe {

X } &d

for now index

{ } $ ? t of $

S

j.col.index > # # ( 4Xxxsex** } best

; fjsex x * ; " ?????idgX •• }

??}}s from ????? ??? ??? # # #ectangle raspx_???

assign robsort .Indata ( Bow Index } [ col_index )

K

in data for seigence_2 ( * _index 1 Col Index + ( rectangle index * XOLS )

17 wap the sorted data from this rectangle into a single coluan of the output data

assign out data from Stuence 2

Index * HQOLS > CO3 isdex

tangle_index )

{ { _ ? ???????? tg { " d ? ex } { { {}} { } }

7

end 17 ENS OF " for ( row_index

? d f} $

?* ** p { ?????????

-

end 11 END OF **For ( rectangle index

{ ???"

S

Á

???? g X

FIG , 41

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 35 of 40

module seq_1_row_sort_stage

8 bits

2 rows

4 columns

input [ 7:01 row sort in data

output [ 7:01 Tow_sort_out_data ( 1 : 0 ] [ 3:01

YYY

) ;

row index

11 Instantiate the 2 4- sorters for this rectangle

genvar

generate

for ( row index

rok index

row index

sort 4 values 8 bits

30

In 36

. In 26

. In 16

.In(

w

M

row index

Out (

Out 20

Out 10

.Out_o (

x

$

3

begin

row sort_4 sorter

row.sort in data

row_sort_in data

row_sort_in_data

rowsort in data

1 / max value

?

mys

row sort out data

row sort out data

row sort out data

row_sort_out data

www

1 / min value

end

endgenerate

endmodule

FIG . 42

(

(

(

(

row index

row_index

row_index

row index

]

]

])

]

1

(

(

(

row

row

row

row

1 ( 3 )

1 1 2)

1 1 ]

] [ 0]

M

index

index

index

index

[ 33 kia)n adt

rpetdan***orte[ltanlnget

[ 1

[ 0]

3

)

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 36 of 40

module seg 2 diag.2.1 stage

(

port List

8 - bit values

input 17:01 dia

output (

4 columns

in data

1 diag 2 1 out data [70 ] [30 ]

// The passthrough assignments

Vyaviy

NYWAWNAWOWAVNAVAT

assign diag2 bout datal

diag 2 1 indata (

offet

?teret

Peter

tete

vy

// The sorter block instantiations

sort.4.values 8 bits

(

Sorter From row 1 column 3

„ In3 ( diag.2.1 in data 1

71 (

.In ( diag

310

„ In_2 (( dian 21 in data 1

.In

in data !

(( diag.21 in data 1

max value

Out ( diag2 out

Out 2 ( diag 2.1 out

.Out ( diag22 out

Out o ( diag_2_3_out

Y

data (

data

data /

data 1

endmodule

FIG . 43

510

>

21 ) ;

31 )

21 )

31 )

3

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 37 of 40

ALGORITHM 2 : Czestion of Module: Cxte for a Rectangle Diagonal Stage:

laput: Nrox . Nools, tirea number of rows and columns in the rectangle

Input: Kox Delta , the amber of rows howmen successive sorter location selections

Isput: O Delta , the winter of columns between successiva sortar location selections

Output: The Systein Verlog Module Code for Sorters and Passthroughs

: Initialize all locations of rectangle array Used in Sorier to 0. 1o . false ;

2. Initialize string variable: module code ; row limit Vrows - Berta Delta w . ) ;

> for colctart - Vcois - downto Ca Dalia by - doreste all diagonal axters

if al start < Vcois . Ca Deita thesi.

row Jimit Rok Delaws;

end

for row.saari - O tu row limit to

Initialize location list to empty : locations in fil

next rOWY start ;123.co col start ,

:

while (next ION < Nrows) and (next 10 do 1xt row .Wtcol still in the rectangle ?

fututions in list locations in U15

3

next ruie ext_sOW Ruw uitu ; next 60 next 60 !mCol della ;

if ( excations in list then found at least 2 locations to sort

Initialize sorter text for {{ocations in lignorier ;

foreach location in luxation list do i Preserve on to max order

Wild fixation as next highest input 3ad sutput posts text of sortir ext ;

13

€ 30

3

2

end

Sex ilseduin Sorterfination to lietne ;

end

23. Re ?

as if EVEN Vcois ) and ( Nools

fox

and ( Col Delta

This is the latRow Sort section ,

Noods - 1

= 1 to Vrows - 2 do

Initialize sorterex for ( Voals wer :

for cox xm 1 to Neois - 2 do

arve min to inax iritas

erid

Add locatim ruw hum.cu ! bum as next highest input and cxUtput ports text of sorter text :

Set Used_in_arter location to 1. 10. true ;

finaliu sorter text and add it to module code :

» forcach location in Used In Sorter do X Create passé routs

* 1 tften

*

( Vrous > 2 ) that

Ostate passthrough text for lixection and add it tomule code

* Finalize module code and write it to stage module $ V ale ;

FIG , 44

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 38 of 40

The original list of 9 unsorted values for the 3 - column standard UCMS example is

4 6 9 2 7 1 8 5 3

Sequence o: Unsorted List of 9 ; 3 Lists of Length 3

3

Row

2

Row

Seura

2

mm

1

0

Baterie

1

3

0

ww

4

2

1

7

6

Song

1

Lists of 3/3/3 Built But Not Yet Sorted

Lists of 3/3/3 Built And Sorted

Sequence 1 : Find the Median of the Final Single Rectangle With 3 Rows x 3 Columns

Stage flow is left to right , Starting in Top Rectangle Row

R/ C: Row /Col Deltas Between Successive Diag Selections

ROW

2

2

..

11

I

87

7. Min of Max's

Median of Medians

www 1

Max of Min's

Stage 1 : Build 3x3 Rectangle: Sort All Rows

Row

2

1

0

2

I

5

Final Median of g Values

FIG . 45

2

1

7

..

malo

Stage 2 : 1/1 R / C Median of 3

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 39 of 40

The original list of 25 unsorted values for the 5 - column UCMS example is

18 10 22 14 6 12 25

19 13

17 16 24

23

22

11 15 5 20

Sequence o : Unsorted List of 25 ; 5 Lists of Length 5

2

.

3

2

422

418

410

12 25

4

23

1

17

2

111

1

414

G

13

9

1

41621 4242

15

2

3

*

-

2

.

)

23

4

3

5

2

3

27

21

24

20

model

un

le

font

2

5 lists of 5 Built And Sorted

5 Lists of 5 Built But Not Yet Sorted

Sequence 1 : Find the Median of the Final Single Rectangle With 5 Rows X 5 Columns

Stage Flow is left to Right, Starting in Top Rectangle Row

R / C : Row / Col Deltas Between Successive Diag Selections

4

2

1

22.

24

1

20

A

3

17

2

tom

og

2

1

1

0

10

5

0

Min 1 of < ; Median of5 ; Max 1 of 4

Mid 3 085 ; Max 3 085 ; Max 2 of 5

2

2

Stage 2 : R/ C1 / 1 Diagonal

Stage 1 : Build 5x5 Rectangle: Sort Rows

From Top Row: Min2 of 5 ; Min 3 of 5 ;

3

20

***

3

HOW

I

4

w

3

3

2

3

2

1

2

1

.

13

--}

Stage 3 : R / C 1/2 Diagonal: Median of 3

Median of 25 has been determined

FIG . 46

0

�U.S. Patent

Jun . 14 , 2022

US 11,360,740 B1

Sheet 40 of 40

The original list of 25 unsorted values for the S- column UCMS example is

18 19 22 14 6 12 25 8 19 13

17 16 24 9 23 2 21

13 11 15 5 20

Sequence 0: Unsorted List of 25 ; 5 Lists of Length 5

How

4

3

2

N

Jamah

1

3

2

12 25

8

4

um

23

13

9

2

7

1

1

15

5

3

2

25

22

1I

w

16 24

2

3

Row

1

?

20

5 Lists of 5 Built But Not Yet Sorted

5 Lists of 5 Buit And Sorted : Max Row

Sequence 1 : Find the Max of the Row of Max's

Stage Flow is left to Night, Starting in Top Rectangle Row

2

4

2

25

22

2

I

24 20

3

2

2

1

1

.

Stage 1 : Sort the Max Row

Vax of 25 has been determined

FIG . 47

I

0

�1

US 11,360,740 B1

2

SINGLE -STAGE HARDWARE SORTING

BLOCKS AND ASSOCIATED MULTIWAY

MERGE SORTING NETWORKS

CROSS - REFERENCE TO RELATED

APPLICATIONS

5

determine a max or min value until it has performed a full

list sort. Both algorithms use merge sorts of 2 sorted lists ,

and the only single - stage hardware sorters that are used in

these sorting networks are 2 - sorters.

For merging two large, sorted lists , John von Neumann's

Merge Sort is typically used . However, the basic algorithm

is very slow , as only the max or min of 2 values is selected

in each clock cycle . Because of this, merge sequences from

O - EMS sorting networks are often used to increase the

This application claims the benefit of U.S. Provisional

Application No. 62 / 984,880 , filed on Mar. 4 , 2020 , all of

10 number of output values in each clock cycle .

which are incorporated by reference .

Rank order filters may be used to select an element from

FIELD OF THE INVENTION

an ordered output list . Rank order filters do not produce a

full list of sorted values from an unsorted list . Rather, they

The invention relates generally to sorting lists of values in produce only a partial list of the sorted values , and often

hardware. More specifically, the invention relates to single- 15 there is only one filtered value that is output. Typical rank

stage sorting blocks and associated multiway merge sorting order filters produce the max , median, and / or min values

networks.

from an unsorted input list . Multiway merge sorting net

works may be used as rank order filters, for example, to sort

BACKGROUND OF THE INVENTION

Hardware sorting systems use single - stage 2 -sorters, or

processes. These single - stage hardware blocks have 2 input

values , a block which compares those 2 input values , and the

comparison result signal is used as the output multiplexer

(MUX ) select line, or control input signal, for the block's

output ports. A 2 -max filter only presents the maximum

(max ) of the 2 inputs, a 2 - min filter presents the minimum

(min) of the 2 inputs. A 2 - sorter presents both the max and

min sorted outputs. A schematic of a 2 - sorter, with both

2 -max and 2 - min output ports, is shown in FIG . 1. A

hardware 2 - sorter may be made into a 2 -max or 2 -min rank

order filter by removing the output multiplexer logic for the

output port not used , but there is no propagation delay

improvement for such a rank order hardware block . Propagation delay is the time required for an input signal to

propagate to an output along the slowest path in a singlestage or network sorting block .

Single -stage hardware N - sorters directly sort more than 2

values at a time when N = 3 . Certain 3 - sorters, for example

those for a 3 -way merge sort process , create their sorters

from 3 serial stages of 2 - sorters . Therefore , these 3 - sorters

are very slow, taking 3 times longer than a single 2 - sorter. A

sorting network using these 3 - sorters becomes a two level

network of 2 - sorter networks. A sorting network consists of

a network of small single - stage hardware sorters and filters,

connected in such a way as to sort lists larger than what can

be sorted by a single - stage sorter or filter. The small N - sorters and N - filters used in traditional sorting networks are

2 - sorters and 2 -max and 2 - min filters.

An advantage to N - sorters when N23 include that fewer

hardware resources may be used for a single - stage hardware

sorter versus a multi -stage network of 2 -sorters .

Single stage hardware 2 -sorters may be connected to

operate in parallel in each stage of the sorting process . This

is considered a sorting network with a purpose to sort

unsorted input values in a fast and efficient manner , and to

output the full sorted list of those same values . When a

sorting network only uses 2 - sorters, even small lists with

more than 2 values must be sorted with a sorting network .

Single stage sorting blocks are used in various sorting

algorithms, such as Odd- Even Merge Sort (O - EMS ) and

Bitonic Merge Sort. Both algorithms take the same amount

of time to sort a list of values , but Bitonic Merge Sort uses

more hardware resources in its networks than O - EMS .

O - EMS can also be used to build fast max or min sorting

network rank order filters, but Bitonic Merge Sort does not

network median rank order filters or to sort network max and

20 min rank order filters.

What is needed is an improved system and methods for

designing single -stage hardware sorting blocks , and further

using the single - stage hardware sorting blocks to reduce the

number of stages in multistage sorting processes, or to define

comparators , and 2 -max and 2 -min filters in their sort

25 multiway merge sorting networks. The invention satisfies

this need .

SUMMARY OF THE INVENTION

30

The invention is directed to a general methodology for the

systematic design of single - stage hardware N - sorter with

N23 . All of the hardware sorters produced in accordance

with this and the following hardware N - sorter embodiments

produce a “ stable sort ” . That is , any duplicated values in the

35 input list are distributed to the output ports in the same

relative order found in the input list . This may be important,

for example, when the values to be sorted are keys in

key /value pairs .

The single - stage sorting blocks comprise a set of at least

40 3 input values , contained in one or more lists . There is one

list of sorted output values , containing the input values , now

in sorted order. A full sorter presents all sorted output values ,

and aa filter presents a subset of the full sorted list . The output

ports are defined using output multiplexers, one port mul

45 tiplexer per each output value bit .

At least three 2 - input comparisons are implemented in

parallel. The comparison result signals may be used directly

as select lines for the output multiplexers, or they may be

combined in various ways in order to define the output

50 multiplexer (MUX ) select lines , or control input signals . The

multiplexer select line operations inside the output bit mul

tiplexers are all performed in parallel.

The systematic design of single - stage hardware N - sorters

according to the invention is appropriate for any type of

55 hardware in which a design can be implemented using a

Hardware Description Language (HDL ) , such as a Field

Programmable Gate Array (FPGA ). It is contemplated that

the invention may be implemented in any known HDL

language, for example, System Verilog ( SV) . It is further

60 contemplated that the invention may be implemented in C

( including C ++ ) language.

The invention is also directed to single - stage rank order

N - filters , which present as outputs M only a subset of the N

sorted inputs, with M < N . N - filters also work on a list of

65 totally unordered input values . Some of these N - filters, such

as hardware median filters , simply output values from the

full sorted output list , without any change in the design for

�3

US 11,360,740 B1

4

the specific values that are output. However, single -stage

FIG . 20 illustrates bit multiplexer behavioral code .

hardware N -max and N -min filters are often specially

FIG . 21 illustrates pseudocode for 4 - min and 4 -max

designed in order to improve the speed of the filters, versus single stage hardware filters.

FIG . 22 illustrates pseudocode for 5 -max single stage

the speed of the associated full N - sorter.

The invention is also directed to single - stage N - sorters 5 hardware filters .

used to enable fast multiway merge sorting networks. A

FIG . 23 illustrates pseudocode for 8 -max single stage

multiway merge sorting network includes one or more hardware filters .

merge sequences, in which 3 or more sorted lists are merged

FIG . 24 illustrates aa flow chart for creating N -to - M filter

into a single sorted output list . After the final merge from a general hardware N -sorter.

sequence, all of the unsorted inputs are presented in a full 10 FIG . 25 is a table of UCMS 4 - column sorted order.

FIG . 26 is aa table of UCMS notations and abbreviations.

sorted output list of those unsorted input values .

The invention is also directed to the design of rank order

FIG . 27 is a UCMS sorting network example for

sorting network filters, where only a subset of the sorted Sequence 0 : 4 -column , Nfinal = 32.

output values are produced and provided as filter outputs .

FIG . 28 is a UCMS sorting network example for

These rank order sorting network filters have reduced 15 Sequence 1 : 4 - column, Nfinal = 32 .

resource usage , versus the corresponding network that outFIG . 29 is a UCMS sorting network example for

puts all of the sorted input values . In some cases , such as Sequence 2 : 4 - column , Nfinal = 32 .

max and min sorting network filters , the filter speed is much

FIG . 30 is a UCMS sorting network example for sequence

faster than the corresponding network which outputs all of flow : 3 - column, Nfinal = 9, Ncols =3 .

the sorted input values . Max and min multiway merge 20 FIG . 31 is a UCMS sorting network example for sequence

sorting network filters , where 3 or more max /min values are flow : 2 -column, Nfinal = 8, Ncols =2 .

merged in each stage , are also shown to be much faster than

FIG . 32 is aa table of a combined equation.

prior art max - and - or -min sorting network filters using 2 -way

FIG . 33 illustrates aa block diagram of a top level UCMS

merge sort, which are restricted to only using 2 -max and network .

25

FIG . 34 is an algorithm for the top level UCMS network .

2 -min single - stage hardware filters.

The invention and its attributes and advantages will be

FIG . 35 is a table of UCMS Sequence 1 stages .

further understood and appreciated with reference to the

FIG . 36 is aa table of various parameters and stage order:

detailed description below of presently contemplated Nfinal = 243 , Ncols =3 .

embodiments , taken in conjunction with the accompanying

FIG . 37 is a non - standard sequence flow : Nfinal = 8 ,

drawings.

30 Ncols =3 .

FIG . 38 is code for 4 - column UCMS example: Nfinal = 32,

DESCRIPTION OF DRAWINGS

Ncols =4 .

FIG . 39 is code for 4 -column UCMS example , Sequence

The preferred embodiments of the invention will be 0 : Nfinal = 32, Ncols =4 .

described in conjunction with the appended drawings pro- 35 FIG . 40 is code for 4 - column UCMS example, Sequence

vided to illustrate and not to limit the invention .

1 : Nfinal= 32, Ncols =4 .

FIG . 1 is a block diagram illustrating a prior art 2 - sorter.

FIG . 41 is code for 4 -column UCMS example, Sequence

FIG . 2 is aa block diagram illustrating a general hardware 2 : Nfinal= 32, Ncols =4 .

N - sorter.

FIG . 42 is code for 4 - column UCMS example row sort,

FIG . 3 illustrates code for a port list creation .

40 Sequence 1 : Nfinal = 32 , Ncols = 4 .

FIG . 4 is a flow chart directed to the design steps of a

FIG . 43 is code for passthrough and 4 -Sorter instantiation

general hardware N - sorter.

from 4 - column example Stage : R / C = 2 / 1 .

FIG . 5 illustrates code for comparison signals.

FIG . 44 is an algorithm used to create module code for a

FIG . 6 illustrates code for output port assignments.

diagonal stage.

FIG . 7 is a flow chart directed to the design steps for 45 FIG . 45 is a median of 3x3 window using UCMS

building multiplexer select line signals .

sequence flow : Nfinal= 9, Ncols = 3 .

FIG . 8 illustrates code for product terms.

FIG . 46 is a median of 5x5 window using UCMS

FIG . 9 illustrates 3 - sorter code created using the general sequence flow : Nfinal = 25, Ncols = 5 .

hardware design embodiments according to the invention .

FIG . 47 is a max of a 5x5 window using UCMS sequence