Labsheet1 ec303 student

•

0 likes•457 views

1. The document describes experiments conducted using Altera Quartus II software to design and simulate combinational logic circuits. 2. In Experiment 1, a 2-input AND gate was designed and its output waveform was simulated with inputs of different time periods. 3. Experiment 2 involved designing a more complex combinational logic circuit and simulating its output waveform.

Report

Share

Related slideshows

Report

Share

Download to read offline

More Related Content

What's hot

Develop Embedded Software Module-Session 3

This presentation is part of training session delivered during Train The Trainer (TOT) program on Embedded Software Engineer job role supported by ESSCI.

Cadancesimulation

This document describes the design and implementation of a 32-bit ALU using Cadence tools. Verilog code was written for the 32-bit ALU and its 8-bit components. NCVerilog was used to verify the code had no errors. Encounter was used to generate schematics, perform analysis, and implement the design. Virtuoso extracted the layout from the design file. The 32-bit ALU was successfully simulated and the design met timing constraints.

00454

This document is an exam for an Electronics and Communication Engineering degree. It contains 15 multiple choice and written response questions covering various topics in computer-aided design for very-large-scale integration including: data structures and algorithms, complexity classes, simulated annealing, compaction applications, multi-level logic synthesis, channel routing, floor planning problems, event queues, binary decision diagrams, minimal spanning trees, Dijkstra's shortest path algorithm, incremental spanning tree computation, Liao-Wong compaction and Bellman-Ford algorithms, Kernighan-Lin partitioning, positive co-factors of reduced ordered binary decision diagrams, gate-level modeling and simulation, and force-directed scheduling. Students have 3 hours to complete the exam which

VLSI Final Design Project

16-bit ALU(Arithmetic Logic Unit) using 130nm process. Software tools that were used are Cadence, HSpice, Design Vision, Siliconsmart, Waveview, Encounter and Primetime

Isorc18 keynote

This document summarizes a keynote presentation on timing analysis and testing. It discusses several topics:

- Timing analysis techniques including worst-case execution time analysis, detailed architectural modeling, and the Chronos timing analysis tool.

- Cache analysis including identifying thrashing scenarios, instrumenting assertions, and using symbolic execution to generate tests that expose cache performance issues.

- Applications to multi-core timing analysis, analyzing cache side channels, and generating tests or attack scenarios rather than just worst-case execution bounds.

The document advocates leveraging advances in constraint solving and symbolic execution to develop additional timing analysis applications beyond traditional worst-case execution time analysis.

Net practicals lab mannual

This document contains a practical report on C# .NET submitted by Rahul Singh to Abhishek Kr Pathak at Uttaranchal Institute of Management. It includes 30 programs covering concepts like data types, string handling, classes, inheritance, exceptions, threads, delegates and windows forms. The programs demonstrate basic to advanced .NET concepts through examples.

Symbexecsearch

Keynote in KLEE workshop on Symbolic Execution 2018

Systematic greybox fuzzing inspired by ideas from symbolic execution, work at NUS

Covers new usage of symbolic execution in automated program repair, work at NUS

Algorithms Lecture 1: Introduction to Algorithms

We will discuss the following: Algorithms, Time Complexity & Space Complexity, Algorithm vs Pseudo code, Some Algorithm Types, Programming Languages, Python, Anaconda.

Relational Operators in C

The document discusses algorithms and flowcharts for conditional and iterative problems. It provides examples and solutions for writing algorithms and flowcharts to determine voter eligibility based on age, print all natural numbers from 1 to N, and find the biggest of two or three numbers. It also includes practice problems for students to write algorithms and flowcharts to solve problems related to discounts based on order quantity and calculating the sum of two numbers using functions. The document aims to help students understand how to design algorithms and flowcharts for conditional and iterative problems.

Doctoral Consortium@RuleML2015: Genetic Programming for Design Grammar Rule I...

The knowledge engineering effort associated with defining grammar systems can become a barrier for the practical use of such systems. Existing grammar and rule induction algorithms offer rather limited support for discovering context-sensitive graph grammar rules as required by some applications in the domain of engineering design. For this task the present work proposes a rule induction method grounded on Genetic Programming. Specializations regarding the representation and evaluation of rule candidates are discussed. Results from preliminary experiments with a prototype implementation demonstrate the feasibility

of the suggested approach.

Automated Test Suite Generation for Time-Continuous Simulink Models

This document summarizes an approach for automated test suite generation for Simulink models with time-continuous behaviors. It discusses two main challenges with existing Simulink testing techniques: incompatibility with the underlying SAT/SMT-based techniques which cannot handle features like time-continuous blocks, and low fault revealing ability when test oracles are manual. The proposed approach uses search-based test generation driven by output diversity and failure patterns to generate test cases that are more likely to reveal faults. An evaluation compares the fault detection capability of the approach to Simulink Design Verifier and finds that the proposed output diversity technique outperforms it. The approach is implemented in a tool called SimCoTest.

ScaRR

ScaRR is a system that provides scalable runtime remote attestation to verify dynamic properties of complex systems. It uses offline analysis to generate measurements of expected execution paths that are verified online. ScaRR models programs as graphs of execution checkpoints and actions to handle complex control flows. It provides efficient verification by checking consistency between reported execution paths and pre-computed expected paths stored in a hashmap. An evaluation shows ScaRR can verify programs faster and with lower network overhead than previous work, while providing security against various attacks.

Algorithms Lecture 3: Analysis of Algorithms II

We will discuss the following: Maximum Pairwise Product, Fibonacci, Greatest Common Divisors, Naive algorithm is too slow. The Efficient algorithm is much better. Finding the correct algorithm requires knowing something interesting about the problem

Csphtp1 06

The document outlines a chapter on methods in C#. It discusses key concepts like defining methods, passing arguments by value vs reference, and using built-in classes like Math. It provides examples of methods that square integers, find the maximum of 3 numbers, and demonstrate passing by reference and out parameters.

Code quailty metrics demystified

from DevMotion Meetup on 2016-03-14

In our everyday work as developers, we are confronted with various software metrics. What do these numbers mean, how are they calculated? Do these metrics enable us to make better software?

In this talk we investigate the use of software metrics in general and also take a detailed look at several frequently used code quality metrics.

We will learn about the meaning and usefulness of metrics such as lines of code, cyclomatic complexity, duplication, package entanglement and unit test coverage.

Survey on Software Defect Prediction

This document provides an overview of software defect prediction approaches from the 1970s to the present. It discusses early approaches using simple metrics like lines of code and complexity metrics. It then covers the development of prediction models using machine learning techniques like regression and classification. More recent topics discussed include just-in-time prediction models, practical applications in industry, using historical metrics from software repositories, addressing noise in data, and the feasibility of cross-project prediction. The document outlines challenges and opportunities for future work in the field of software defect prediction.

What's hot (16)

Doctoral Consortium@RuleML2015: Genetic Programming for Design Grammar Rule I...

Doctoral Consortium@RuleML2015: Genetic Programming for Design Grammar Rule I...

Automated Test Suite Generation for Time-Continuous Simulink Models

Automated Test Suite Generation for Time-Continuous Simulink Models

Similar to Labsheet1 ec303 student

Micrcontroller iv sem lab manual

This document provides information about a lab manual for a Microcontrollers course. It includes:

1) An index listing 12 experiments covering assembly programming of 8051 microcontrollers and interfacing programs, along with MSP430 programming.

2) Syllabus details for the course outlining topics like data transfer, arithmetic, logic instructions, counters and interfacing modules.

3) Instructions for students on lab protocols and expectations.

4) Table of contents organizing the experiments and programs by topic and page numbers.

5) An introduction section describing 8051 architecture features and Keil μVision tools for programming.

Altera up1

This document provides a user's guide for implementing digital logic designs on Altera's UP 1 Educational Board using their MAX+plus II CAD software. It introduces a 4-bit binary counter design example to demonstrate the design process. The steps covered include entering the design schematically, performing functional simulation, synthesizing the design for the FPGA, and downloading the design onto the UP 1 board. The guide is organized into chapters that cover general information about the UP 1 board and MAX+plus II tools, the binary counter example, and combining schematic and hardware description language approaches.

cscript_controller.pdf

The document is a tutorial that introduces the C-Script block in PLECS, which allows implementing custom controllers and components using C code. It discusses how the C-Script block interfaces with the simulation engine via function calls, its parameters including sample time settings, and provides exercises to implement a mathematical function and digital PI controllers with and without calculation delays.

resumelrs_jan_2017

This document provides a summary of Laird Snowden's experience and qualifications. It includes contact information, a performance summary, and lists membership in professional organizations. The bulk of the document describes Snowden's extensive experience in semiconductor testing and new product introduction, including bringing fabrication facilities online, developing automated test equipment, improving yield, and reducing test time. It highlights experience at companies including Bell Labs, AT&T, TriQuint, and Silicon Labs.

final report

This document provides an overview of automation and SCADA systems. It discusses what automation is, defines industrial automation, and describes the main components of an automated system, including programmable logic controllers and SCADA. It also discusses the benefits of SCADA systems and their functions, including data acquisition, network communication, and data presentation. The document contains profiles of leading SCADA companies and provides details on installing SCADA software and developing applications in InTouch SCADA.

EC6612 VLSI Design Lab Manual

1. The document describes the syllabus for the VLSI Design Laboratory course for the academic year 2017-2018 at Erode Sengunthar Engineering College.

2. The syllabus includes experiments involving HDL-based design and simulation of basic components like counters and adders using FPGA tools. It also includes layout design and simulation of basic CMOS gates using CAD tools.

3. The listed experiments will be carried out in two cycles. Cycle 1 involves the implementation of components like adders, multipliers and counters on FPGA. Cycle 2 involves the design and simulation of CMOS gates using EDA tools and their layout using other CAD tools.

Dsp lab manual 15 11-2016

This document provides information about a digital signal processing laboratory manual, including:

- An index listing 12 experiments covering topics like DSP chip architecture, linear and circular convolution, FIR and IIR filter design, FFT implementation, frequency response analysis, and power spectral density computation.

- General instructions for successfully completing experiments within the 3-hour laboratory period and guidance for laboratory reports.

- Procedures for working with MATLAB and Code Composer Studio software to execute experiments and programs on a DSP processor.

- An introduction to digital signal processors and an overview of the architecture of the TMS320C67xx DSP chip used, including its CPU, memory, peripherals, and advanced parallel processing capabilities

LOW COST SCADA SYSTEM FOR EDUCATION

A prototype based on SCADA system was developed as a result of the final project of the discipline entitled Applied Microcontrollers to Control and Automation Engineering. This course has project based learning (PBL) methodology. he prototype has a drive unit and a computer program. This evice was developed using a PIC18F4550 microcontroller and various electronic components: resistors, capacitors, LEDs, among others. The computer program was developed using programming language C Sharp (C #) in Visual Studio development environment. The interface between the program and the device is performed via USB communication. This prototype is now used in the discipline mentioned in order to teach practical lessons about embedded systems projects, USB communication, data acquisition and supervisory systems. As all stages of the project were presented to the students in a very detailed way and its development was performed on a real application, the students showed a lot of interest about this tool during the last school year.

ContentsTeam Work Schedule3Team Task Assignment3Project .docx

Contents

Team Work Schedule 3

Team Task Assignment 3

Project Plan 4

Step 1: Define the Problem 4

Step 2: Create a Plan 4

Step 3: Execute 4

Step 4: Check Work 6

Step 5: Learn and Generalize 6

House of Quality (HOQ) for Theia’s Smart Glasses 7

Step 1: Define the Problem 7

Step 2: Create a Plan 7

Step 3: Execute 8

Step 4: Check Work 14

Step 5: Learn and Generalize 14

Aggregate Project Plan 15

Step 1: Define the Problem 15

Step 2: Create a Plan 15

Step 3: Execute 16

Step 4: Check Work 22

Step 5: Learn and Generalize 22

I was able to use the APP skills from the midterm and apply it to our actual project. We learned that project #2 yields the highest EMV so that will be the industry we will be focusing on. 22

Theia’s Conceptual Design Process 23

Step 1: Define the Problem 23

Step 2: Create a Plan 23

Step 3: Execute 24

Concept 1 27

Concept 2 28

Concept 3 29

Concept 4 30

Concept 5 31

Concept 6 32

Step 4: Check Work 34

Step 5: Learn and Generalize 34

Phase Ⅱ Reportca 36

Step 1: Define the Problem 36

Step 2: Create a Plan 36

Step 3: Execute 36

Project Planning 36

House of Quality 37

Aggregate Project Plan 37

Reverse Engineering (includes FAST analysis + diagram) 38

Conceptual Design 38

Step 4: Check Work 38

Step 5: Learn and Generalize 39

Team Work Schedule

Date

Task

10/24

Homework assigned, touch bases with team to decide weekend plans.

10/25

Read handout and HOQ example. Everyone assigned to do individual research about AR Glasses.

10/26

Read handout and HOQ example. Everyone assigned to do individual research about AR Glasses.

10/27

Meet at a cafe downtown, due to the power outage. Meeting time is 1 hour.

10/28

Everyone working remotely. Also everyone is working on Phase I/II at the moment. HOQ problem is postponed for a while as we are working on Phase I/II.

10/29

Meet at TBD. Meeting time is 1 hour.

10/30

Revise our work.

10/31

Final revisions. Turn in homework.

Team Task Assignment

Task

Phase 1 - Missing Info + Tech Strategy

Phase 1 - Missing Functional Maps

Project Planning

House of Quality for Product

Aggregate Project Plan

Reverse Engineering

Conceptual Design

Phase II ReportProject PlanStep 1: Define the Problem

We need to clearly determine the tasks required of this project and develop a systematic plan of action to tackle these tasks.Step 2: Create a Plan

Framework for Project Planning:

1. Clearly state the intent of the Project

2. Determine the Design/Development sub-tasks and activities Comment by Christopher Chiang: Develop OS

Develop Display technology

Develop glasses framework

Audio Output

Develop Bluetooth compatibility

Battery development

Charge development

Environment sensing capability

3. Create a design/development activity matrix

4. Create a schedule for each subtask using a GANTT Chart

5. Identify the Critical Path for the Project

6. Assign Clear Roles and Responsibilities & track progressStep 3: Execute

1. Clearly state the intent of the Project

a. Develop smart glasses wearable technology prototype within a 1 year timesp.

Filter designandanalysisusingmicrowaveoffice

This document provides supplementary information for a module that introduces RF/microwave filter design using the CAD tool Microwave Office (MWO). It describes the specific steps shown in setting up a low-pass filter project in MWO and provides instructions for a band-pass filter design project. It also includes step-by-step instructions for obtaining a student version of MWO.

File 1 proteus tutorial for digital circuit design

This document provides instructions for using Proteus software to simulate and design digital circuits. It discusses:

1) The objectives of learning to use Proteus software to simulate designed digital circuits and understand how to apply digital logic equations to hardware designs.

2) How to use tools in Proteus like parts browsing, power supplies, input generators, and logic state components.

3) How to simulate circuits by placing components, wiring them, and using logic probes or waveform displays to view output measurements.

4) Some example assignments involving creating circuits from logic equations and comparing/reducing equations, and plotting input-output relationships.

process control instrumentation lab and labview report

this is process control and instrumentation lab report and simulations were implemented using the matlab simulink and labview

UDP Report

This document summarizes the development of a distributed simulation toolbox for MATLAB/Simulink. The toolbox allows for real-time communication between systems using UDP. It was developed in two phases: first, test applications in C++, then S-functions for MATLAB. The C++ applications demonstrated singlecast, multicast, and broadcast transmissions of data arrays. The S-functions translate this functionality into Simulink blocks for UDP send and receive with parameters for port, IP, and data type.

Engineering C-programing module1 ppt (18CPS13/23)

The document provides information about a C programming course, including:

1) An introduction to computer hardware and software concepts such as computer generations, types, bits, bytes, CPU, memory, ports, input/output devices and networks.

2) An overview of the C programming language including the basic structure of a C program, executing a program, and data types.

3) Examples of C programs to calculate the area and perimeter of shapes like circles and rectangles as well as examples demonstrating constants, variables, and data types in C.

Be cps-18 cps13or23-module1

The document provides information about a C programming course, including:

1) An introduction to computer hardware and software concepts like computer generations, types, bits, bytes, CPU, memory, ports, input/output devices and networks.

2) An overview of the C programming language including the basic structure of a C program, executing a program, and data types like constants, variables, integers, floats etc.

3) Examples of C programs to calculate the area and perimeter of shapes like circles and rectangles, along with the basic components of a C program like preprocessor directives, main function, declaration and executable parts.

COCOMO MODEL

The document discusses several popular effort estimation methodologies including function points and COCOMO. It provides examples of using function points and COCOMO I to estimate effort and schedule for a simple POWER function project estimated to be 100 lines of code. Estimates using different approaches were: 5 person days and 3 calendar days from personal experience, 7.9 person days and 7.9 calendar days from function points, and 6.7 person days and 1.5 calendar months from COCOMO I. The document notes challenges with estimation models and many professionals rely on their own experience and company data.

18CSL48.pdf

This document provides details for the course plan of a Microcontroller and Embedded Systems lab. It includes 13 experiments related to assembly language programming and interfacing for ARM microcontrollers. The document outlines the laboratory information, objectives, experiments, assessment details, and mapping to program outcomes. The 13 listed experiments cover topics such as binary addition, finding sums and factorials, array operations, sorting, interrupts, UART communication, motor control, analog to digital conversion, and keyboard interfacing.

GE3171-PROBLEM SOLVING AND PYTHON PROGRAMMING LABORATORY

GE3171-PROBLEM SOLVING AND PYTHON PROGRAMMING LABORATORYANJALAI AMMAL MAHALINGAM ENGINEERING COLLEGE

The document provides a lab manual for the course GE3171 - Problem Solving and Python Programming Laboratory. It includes the course objectives, list of experiments, syllabus, and programs for various experiments involving Python programming concepts like lists, tuples, conditionals, loops, functions etc. The experiments cover problems on real-life applications such as electricity billing, library management, vehicle components, building materials etc. The document demonstrates how to write Python programs to solve such problems and validate the output.IRJET- A Testbed for Real Time Water Level Control System

The document describes the design and development of a testbed for real-time water level control system. The testbed is intended to provide engineering students a platform to test process control algorithms before implementation. It uses an algorithmic state machine approach where the state transition table is converted to a ROM structure. The hardware components include a microcontroller, ADC, timer and driver circuits. The design calculations and subsystem design are also outlined. The conclusions state that the low-cost testbed will enable practical learning of process control and help improve engineering education.

Costing ass4

This document discusses using use case points (UCP) to estimate software development effort. UCP involves classifying use cases and actors based on complexity, then calculating unadjusted use case and actor weights. Technical and environmental factors are also assessed. These variables are used in an equation to determine the adjusted use case points and estimated effort in hours or weeks. The document presents this method and tools to automate it. It also compares UCP to function points and shares results from applying UCP in three industry projects, finding the estimates were close to expert assessments.

Similar to Labsheet1 ec303 student (20)

ContentsTeam Work Schedule3Team Task Assignment3Project .docx

ContentsTeam Work Schedule3Team Task Assignment3Project .docx

File 1 proteus tutorial for digital circuit design

File 1 proteus tutorial for digital circuit design

process control instrumentation lab and labview report

process control instrumentation lab and labview report

GE3171-PROBLEM SOLVING AND PYTHON PROGRAMMING LABORATORY

GE3171-PROBLEM SOLVING AND PYTHON PROGRAMMING LABORATORY

IRJET- A Testbed for Real Time Water Level Control System

IRJET- A Testbed for Real Time Water Level Control System

Recently uploaded

FINAL MATATAG LANGUAGE CG 2023 Grade 1.pdf

MATATAG K TO 10 CURRICULUM OF THE K TO 12 PROGRAM

LANGUAGE GRADE 1

How to Add Collaborators to a Project in Odoo 17

Effective project management in Odoo 17 hinges on collaboration. By adding collaborators, we can assign tasks, share information, and keep everyone on the same page.

Tale of a Scholar and a Boatman ~ A Story with Life Lessons (Eng. & Chi.).pptx

A PowerPoint Presentation of a meaningful story that teaches important Life Lessons /Virtues /Moral values.

The texts are in English and Chinese.

For the Video with audio narration and explanation in English, please check out the Link:

https://www.youtube.com/watch?v=GH71Ds2WzU8

BANG E BHARAT QSN SET by Amra Quiz Pagoler Dol

BANG E BHARAT Quiz at Silchar Quiz Fest by Amra Quiz Pagoler Dol

Celebrating 25th Year SATURDAY, 27th JULY, 2024

Dear Sakthi Thiru Dr. G. B. Senthil Kumar,

It is with great honor and respect that we extend this formal invitation to you. As a distinguished leader whose presence commands admiration and reverence, we cordially invite you to join us in celebrating the 25th anniversary of our graduation from Adhiparasakthi Engineering College on 27th July, 2024. we would be honored to have you by our side as we reflect on the achievements and memories of the past 25 years.

Types of Diode and its working principle.pptx

A diode is a two-terminal polarized electronic component which mainly conducts current in one direction and blocks in other direction.

Its resistance in one direction is low (ideally zero) and high (ideally infinite) resistance in the other direction.

How to Configure Extra Steps During Checkout in Odoo 17 Website App

Odoo websites allow us to add an extra step during the checkout process to collect additional information from customers. This can be useful for gathering details that aren't necessarily covered by standard shipping and billing addresses.

principles of auditing types of audit ppt

this slide share explains about types of audit,internal audit,external audt,

How to Set Start Category in Odoo 17 POS

When Opening a session of a Point of Sale (POS) we can set the default product view. We can give which category we need to view first. This feature will help to improve the efficiency and it also saves time for the cashier. This slide will show how to set the start category in Odoo 17 POS.

sdintegrating21stcenturyskillsinclassroom-basedassessment-240715032004-e59ed7...

sdintegrating21stcenturyskillsinclassroom-basedassessment-240715032004-e59ed7...ABELARDOBALDOVEAZUEL

TopiLecture Notes Unit5 chapter 15 PL/SQL Programming

Description:

Welcome to the comprehensive guide on Relational Database Management System (RDBMS) concepts, tailored for final year B.Sc. Computer Science students affiliated with Alagappa University. This document covers fundamental principles and advanced topics in RDBMS, offering a structured approach to understanding databases in the context of modern computing. PDF content is prepared from the text book Learn Oracle 8I by JOSE A RAMALHO.

Key Topics Covered:

Main Topic : PL/SQL

Sub-Topic :

Structure of PL/SQL Block, Declaration Section, Variable, Constant, Execution Section, Exception, How PL/SQL works, Control Structures, If then Command,

Loop Command, Loop with IF, Loop with When, For Loop Command, While Command, Integrating SQL in PL/SQL program.

Target Audience:

Final year B.Sc. Computer Science students at Alagappa University seeking a solid foundation in RDBMS principles for academic and practical applications.

URL for previous slides

Unit V

Chapter 15

Unit IV

Chapter 14 Synonym : https://www.slideshare.net/slideshow/lecture_notes_unit4_chapter14_synonyms-pdf/270327685

Chapter 13 Users, Privileges : https://www.slideshare.net/slideshow/lecture-notes-unit4-chapter13-users-roles-and-privileges/270304806

Chapter 12 View : https://www.slideshare.net/slideshow/rdbms-lecture-notes-unit4-chapter12-view/270199683

Chapter 11 Sequence: https://www.slideshare.net/slideshow/sequnces-lecture_notes_unit4_chapter11_sequence/270134792

chapter 8,9 and 10 : https://www.slideshare.net/slideshow/lecture_notes_unit4_chapter_8_9_10_rdbms-for-the-students-affiliated-by-alagappa-university/270123800

About the Author:

Dr. S. Murugan is Associate Professor at Alagappa Government Arts College, Karaikudi. With 23 years of teaching experience in the field of Computer Science, Dr. S. Murugan has a passion for simplifying complex concepts in database management.

Disclaimer:

This document is intended for educational purposes only. The content presented here reflects the author’s understanding in the field of RDBMS as of 2024.

Plato and Aristotle's Views on Poetry by V.Jesinthal Mary

PPT on Plato and Aristotle's Views on Poetry prepared by Mrs.V.Jesinthal Mary, Dept of English and Foreign Languages(EFL),SRMIST Science and Humanities ,Ramapuram,Chennai-600089

Understanding Clergy Payroll : QuickBooks

Learn how to understand the best practices for determining, paying, and reporting clergy payroll and expenses.

Recently uploaded (20)

Tale of a Scholar and a Boatman ~ A Story with Life Lessons (Eng. & Chi.).pptx

Tale of a Scholar and a Boatman ~ A Story with Life Lessons (Eng. & Chi.).pptx

SD_Creating Excellent and Powerful Learning Facilitation.pptx

SD_Creating Excellent and Powerful Learning Facilitation.pptx

How to Configure Extra Steps During Checkout in Odoo 17 Website App

How to Configure Extra Steps During Checkout in Odoo 17 Website App

sdintegrating21stcenturyskillsinclassroom-basedassessment-240715032004-e59ed7...

sdintegrating21stcenturyskillsinclassroom-basedassessment-240715032004-e59ed7...

Plato and Aristotle's Views on Poetry by V.Jesinthal Mary

Plato and Aristotle's Views on Poetry by V.Jesinthal Mary

Labsheet1 ec303 student

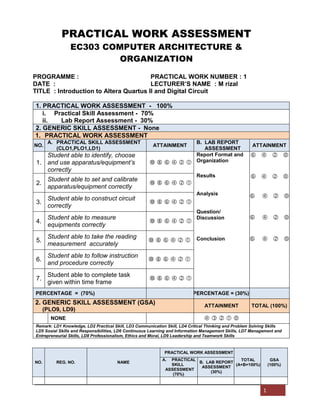

- 1. 1 PRACTICAL WORK ASSESSMENT EC303 COMPUTER ARCHITECTURE & ORGANIZATION PROGRAMME : PRACTICAL WORK NUMBER : 1 DATE : LECTURER’S NAME : M rizal TITLE : Introduction to Altera Quartus II and Digital Circuit 1. PRACTICAL WORK ASSESSMENT - 100% i. Practical Skill Assessment - 70% ii. Lab Report Assessment - 30% 2. GENERIC SKILL ASSESSMENT - None 1. PRACTICAL WORK ASSESSMENT NO. A. PRACTICAL SKILL ASSESSMENT (CLO1,PLO1,LD1) ATTAINMENT B. LAB REPORT ASSESSMENT ATTAINMENT 1. Student able to identify, choose and use apparatus/equipment’s correctly Report Format and Organization Results Analysis Question/ Discussion Conclusion 2. Student able to set and calibrate apparatus/equipment correctly 3. Student able to construct circuit correctly 4. Student able to measure equipments correctly 5. Student able to take the reading measurement accurately 6. Student able to follow instruction and procedure correctly 7. Student able to complete task given within time frame PERCENTAGE = (70%) PERCENTAGE = (30%) 2. GENERIC SKILL ASSESSMENT (GSA) (PLO9, LD9) ATTAINMENT TOTAL (100%) NONE Remark: LD1 Knowledge, LD2 Practical Skill, LD3 Communication Skill, LD4 Critical Thinking and Problem Solving Skills LD5 Sosial Skills and Responsibilities, LD6 Continuous Learning and Information Management Skills, LD7 Management and Entrepreneurial Skills, LD8 Professionalism, Ethics and Moral, LD9 Leadership and Teamwork Skills NO. REG. NO. NAME PRACTICAL WORK ASSESSMENT TOTAL (A+B=100%) GSA (100%) A. PRACTICAL SKILL ASSESSMENT (70%) B. LAB REPORT ASSESSMENT (30%)

- 2. 2 PRACTICAL/LAB SHEET EC303 COMPUTER ARCHITECTURE & ORGANIZATION. PRACTICAL LABORATORY NUMBER : 1 TITLE : INTRODUCTION TO ALTERA QUARTUS II AND DIGITAL CIRCUIT LEARNING OUTCOME : 1. Construct arithmetic logic operation and interfacing circuit into the digital circuit using logic gates and flip-flop (P4). APPARATUS / EQUIPMENT : 1. Personal computer (Pentium III (866 MHz or faster)) 2. Altera Quartus II,Version 8 INTRODUCTION / THEORY : The Altera Quartus II design software provides a complete, multiplatform design environment that easily adapts to your specific design needs. It is a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes solutions for all phases of FPGA and CPLD design (Figure 1). In addition, the Quartus II software allows user to use the Quartus II graphical user interface and command-line interface for each phase of the design flow. User can use one of these interfaces for the entire flow, or different options at different phases. ACTION NAME & DESIGNATION SIGNATURE DATE Prepared by: Approved by:

- 3. 3 Figure 1: Quartus II design flow. WORKING PROCEDURES : Experiment 1.1 : Draw a 2 input AND gate , and show the simulation 1. Run the Altera Quartus II program and create a new project. 2. Create a directory and name of the project as test1. 3. Choose the right device. 4. Make a new schematic file by clicking File > New > Block diagram/Schematic file 5. Draw the AND gate by insert the symbol. Select the symbol tool. 6. Add a symbol by type the name of component. (and2 = 2 input for AND gate; input = input ; output=output) Figure 2: And gate. VCC pin_name INPUT VCC pin_name2 INPUT pin_name3OUTPUT AND2 inst

- 4. 4 7. Rename the input of the AND gate with A and B, and the output as C. Save all the project.(step 1 until 7 is for drawing a circuit) 8. Compile the project by clicking a compilation button. 9. Click on the test1.bdf window and click Processing > Analyze Current File 10. Click Start Analysis & Synthesis button. (step 8 until 10 is for compilation,analysis and synthesis the circuit) 11. Insert a title and get a RTL viewer by click Tool>Netlist Viewers >RTL Viewer 12. Create a new file of waveform file. Click File> New > Vector Waveform File 13. Right click on the waveform1.vwf window and click insert > insert node or bus > Insert node or bus. 14. Click Node Finder > List. Select all the nodes found. Figure 3: Node finder 15. Setup the value of clock for input A and B by clicking the overwrite clock icon. Click the waveform, then click on the overwrite clock icon. For A, the time period is set to 10ns with 50% duty cycle. For B, time period is change to 20ns.

- 5. 5 Figure 4 : Clock setting. 16. Save all the project. 17. Click processing > simulator tool. Select simulation mode to functional. Click Generate Functional Simulation Netlist. Click start. 18. Click open on the simulator tool window to see the simulation input file. 19. Click report on the simulator too; window to see simulation report. 20. Discuss all the result. Experiment 1.2 : Combinational Logic Circuit With the same steps, draw the combinational logic circuit by using Altera Quartus II, and show the simulation waveform with the period value of A =10ns, B=20ns and C=40 ns with 50% duty cycle. Figure 5: Combinational logic circuit.

- 6. 6 RESULTS : Experiment 1.1 Result Schematic circuit (print screen) RTL Viewer (Print screen) Output Waveform (Sketch) and truth table A B C 0 0 0 1 1 0 1 1 Output Waveform (print screen)

- 7. 7 RESULTS : Experiment 1.2 Result Schematic circuit (print screen) RTL Viewer (Print screen) Output Waveform (Sketch) and truth table A B C J 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

- 8. 8 Result Output Waveform (print screen) ANALYSIS : 1. Altera Quartus ii application and logic circuit. 2. Boolean equation 3. Related output data and theory

- 9. 9 QUESTION / DISCUSSIONS : 1. What the effect to the output waveform if the duty cycle below 50 percent, 50 percent and over 50 percent? CONCLUSION :