Real-time Control Systems - é»åé»å 系統èæ¶çè¨è¨å¯¦é©å®¤ - åç« ...

Real-time Control Systems - é»åé»å 系統èæ¶çè¨è¨å¯¦é©å®¤ - åç« ...

Real-time Control Systems - é»åé»å 系統èæ¶çè¨è¨å¯¦é©å®¤ - åç« ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

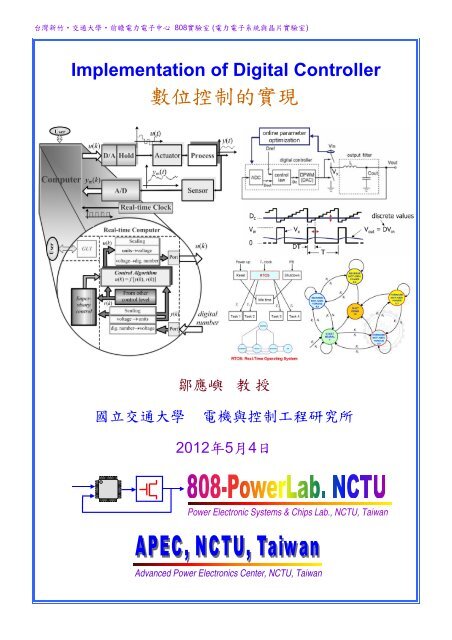

台 灣 新 竹 ‧ 交 通 大 學 ‧ 前 瞻 電 力 電 子 中 心 808 實 驗 室 ( 電 力 電 子 系 統 與 晶 片 實 驗 室 )<br />

Implementation of Digital <strong>Control</strong>ler<br />

數 位 控 制 的 實 現<br />

鄒 應 嶼<br />

教 授<br />

國 立 交 通 大 學<br />

電 機 與 控 制 工 程 研 究 所<br />

2012 年 5 月 4 日<br />

Power Electronic <strong>Systems</strong> & Chips Lab., NCTU, Taiwan<br />

Advanced Power Electronics Center, NCTU, Taiwan

<strong>Real</strong>-<strong>time</strong> <strong>Control</strong> <strong>Systems</strong>: A Tutorial<br />

A. Gambier<br />

Automation Laboratory, B6 23-29, EG. Bauteil C<br />

University of Mannheim, 68131 Mannheim, Germany<br />

gambier@ti.uni-mannheim.de<br />

Abstract<br />

The literature about real-<strong>time</strong> systems presents digital<br />

control or computer controlled systems as one of its most<br />

important practical application field. However, it is very<br />

difficult to find in these textbooks real-<strong>time</strong> control aspects.<br />

It seems to be more natural that these applications should<br />

be treated as part of digital control courses. In spite of<br />

that, control system literature rarely includes extensively<br />

the real-<strong>time</strong> subject and it does normally not pay attention<br />

to real-<strong>time</strong> aspects beyond algorithms and choice of sampling<br />

<strong>time</strong>s. The aim of this paper is to highlight important<br />

issues about real-<strong>time</strong> systems that should be taken into<br />

account at the moment to implement digital control.<br />

1 Introduction<br />

The implementation of digital control systems and real-<strong>time</strong><br />

systems belong together and they should be connected<br />

more or less later in the control engineering curricula.<br />

However, it is difficult to find this connection in the<br />

standard textbooks, where the real-<strong>time</strong> implementation is<br />

almost always ignored. For example, a very good introduction<br />

into computer controlled systems can be found in [1],<br />

but no orientation to the real-<strong>time</strong> software is given there.<br />

Mechanisation of control algorithms are given e.g. in [9].<br />

In [8], hardware and software for digital control systems<br />

are described shortly. On the other hand, in [3] the real<strong>time</strong><br />

system design is treated from the optic of control<br />

engineering without to consider implementation aspects.<br />

In general, real-<strong>time</strong> issues are gradually becoming “transparent”<br />

to the control engineering student. This transparency<br />

has been considerably increased in the last years with the<br />

advent of software tools like Matlab/Simulink ([24]) with<br />

its RTW (<strong>Real</strong> Time Workshop), the RTWT (<strong>Real</strong> Time<br />

Windows Target) and products from other companies like<br />

WinCon from Quanser ([25]) and ECP Executive from ECP<br />

<strong>Systems</strong> ([26]). They certainly do the implementation of<br />

real-<strong>time</strong> experiments easier and save much <strong>time</strong>, but on<br />

the other hand they put more distance regarding to the reallife<br />

problems, which can emerge during the real-<strong>time</strong> implementation<br />

of control systems. Hence, control concepts<br />

become today easier to be exemplified, but control engineering<br />

students can lose the real dimension about designing<br />

real-<strong>time</strong> control systems, particularly when they have to<br />

deal with <strong>time</strong>-critical applications.<br />

This paper attempts to give an introduction to the implementation<br />

of real-<strong>time</strong> control systems, where characteristics<br />

of real-<strong>time</strong> systems and digital control issues are taking together<br />

into account.<br />

The outline of the paper is as follow. Digital control aspects<br />

are introduced in Section 2. Definitions and characteristics<br />

of real-<strong>time</strong> systems are described in Section 3. Here, some<br />

common mistakes and misconceptions by developing real<strong>time</strong><br />

control software are also discussed. Section 4 treats the<br />

implementation of real-<strong>time</strong> controllers and Section 5 summarizes<br />

some important specifications for the implementation<br />

of real-<strong>time</strong> control systems as well as some well-known<br />

commercial products. Finally, conclusions are drawn in<br />

Section 6.<br />

2 Computer controlled systems<br />

The introduction of digital computers in the control loop<br />

has allowed developing more flexible control systems<br />

including higher-level functions and advanced algorithms.<br />

Furthermore, most current complex control systems could<br />

not be implemented without the application of digital hardware.<br />

However, the simple sequence sensing–control–actuation<br />

for the classical feedback control becomes more complex<br />

as well. Nowadays, this sequence can be supplemented<br />

as follow: sensing–data acquisition–control law<br />

calculation–actuation–data base update. Figure 1 shows<br />

an overview of such control systems.<br />

User<br />

Computer<br />

User<br />

Supervisory<br />

control<br />

u(k)<br />

D/A Hold<br />

y m (k)<br />

GUI<br />

<strong>Real</strong>-<strong>time</strong> Computer<br />

u(k)<br />

r(k)<br />

A/D<br />

Scaling<br />

unitsvoltage<br />

voltagedig. number<br />

<strong>Control</strong> Algorithm<br />

u(k) = f [y(k), r(k)]<br />

From other<br />

control level<br />

Scaling<br />

voltage units<br />

dig. numbervoltage<br />

u(t)<br />

Actuator<br />

y m (t)<br />

<strong>Real</strong>-<strong>time</strong> Clock<br />

Port<br />

y(k)<br />

Port<br />

Process<br />

Sensor<br />

u(k)<br />

digital<br />

number<br />

Figure 1. Overview of a computer controlled system<br />

y(t)

Thus, the control system now contains not only wired components<br />

but also algorithms, which must be programmed,<br />

i.e. software is now included in the control loop. This<br />

leads to new aspects to take into account by designing<br />

control systems:<br />

1.Errors due to A/D and D/A conversion as well as due<br />

to limited length word calculations. This subject is<br />

well treated in the literature (see for example [ 9]).<br />

2. Software developing is prone to errors. Thus, a new<br />

concept has to be introduced to consider this aspect, the<br />

verification, i.e. a mechanism to test if the software is<br />

doing exactly what it is expected. Here it is necessary<br />

to remark that in general a high percent of errors in<br />

digital control systems are caused by programming<br />

mistakes. Hence, digital control projects need not<br />

only control engineers but also engineers with skills in<br />

software engineering and computer programming.<br />

3. Standard textbooks on digital control systems normally<br />

assume that sampling is uniform, periodic and synchronous.<br />

This leads to a case of “zero-<strong>time</strong>-execution” for<br />

the control law. However, that is not realistic since the<br />

control algorithm also consumes some <strong>time</strong> producing a<br />

control or feedback delay (control or feedback latency),<br />

i.e. a delay between a sampling instant and the instant<br />

at which a control-signal value is applied to the actuator.<br />

If the controller design is based on a model and the<br />

delay is constant and known, it could be helpful to use a<br />

tool for the description of the inter-sample behaviour<br />

(e.g. modified z-transform) in order to obtain a discrete<strong>time</strong><br />

model more approximated to the real case.<br />

4.The computational <strong>time</strong> of control algorithms can<br />

change from one sampling instant to other (e.g. hybrid<br />

controller with controller switching mechanism, event<br />

based controllers, adaptive controllers with on-line<br />

parameter update, etc.). This variation in the delay is<br />

called control jitter (according to the IEEE, jitter is “the<br />

<strong>time</strong>-related abrupt, spurious variation in the duration<br />

of any specified related interval”). Moreover, value<br />

calculation for the control signal is usually carried out<br />

using multitasking (Subsection 3.2) defining a set of<br />

control tasks with respective priorities. Thus, a task can<br />

be pre-empted by higher priority tasks. In general, it<br />

can be said that the control system is also affected by<br />

several kind of jitter depending on context: sampling<br />

jitter, control latency jitter, input jitter, output jitter, etc.<br />

Finally, real-<strong>time</strong> issues are often ignored in the implementation<br />

of digital control systems. This is in part a consequence<br />

of erroneous definitions and false interpretations.<br />

Popular misconceptions from the control engineering<br />

community about real-<strong>time</strong> systems are for example:<br />

The computer was connected to the plant by mean of<br />

A/D and D/A converters in order to obtain the real<strong>time</strong><br />

system. Analog plants should be connected to the<br />

computer through A/D and D/A converters. This link<br />

with the “real world” does not lead to a real-<strong>time</strong><br />

system. On the other hand, it is possible to find real<strong>time</strong><br />

systems in complete digital contexts.<br />

Our plant is so slow that real <strong>time</strong> is actually no<br />

problem. A slow control system, which does not need<br />

a fast computer, can require critical <strong>time</strong> constraints.<br />

It is also possible that a control system does no need<br />

any hard real-<strong>time</strong> requirements but it is not necessarily<br />

a consequence of the slow plant.<br />

It is not meaningful to talk about guarantying real-<strong>time</strong><br />

performance. It is true that occasionally <strong>time</strong> constraints<br />

can be relaxed without introducing additional problems<br />

in the control loop. This particularly applies to nice designed<br />

laboratory experiments. However, this actually<br />

depends on the application, and the <strong>time</strong> criticality<br />

should be proved for each individual case. On the other<br />

hand, real-<strong>time</strong> performance cannot be 100% guaranteed<br />

while hardware and software failures cannot be avoided<br />

at all.<br />

We do not care about real <strong>time</strong> in our digital control<br />

system and even though it works. This statement is<br />

similar to the previous one. The problem here is that<br />

you are not able to know when your system can fail.<br />

<strong>Real</strong>-<strong>time</strong> programming is assembly coding, priority<br />

interrupt programming and device driver writing. It<br />

is true that some code is still writing in assembler.<br />

However, high programming languages like C, Ada<br />

95, Modula 2 and <strong>Real</strong>-<strong>time</strong> Java are normally used<br />

to develop real-<strong>time</strong> software. Device driver programming<br />

is necessary for real-<strong>time</strong> as well as non-real<strong>time</strong><br />

systems but they should be provided by the operating<br />

system or by the device manufacturer. Interrupt<br />

programming should be in principle avoided as much<br />

as possible. This point is treated in Subsection 3.5.<br />

In the next Sections, an overview about real-<strong>time</strong> systems<br />

and control systems will be given in order to clarify real-<strong>time</strong><br />

programming and its most important application.<br />

3 <strong>Real</strong>-<strong>time</strong> systems: a short introduction<br />

<strong>Real</strong>-<strong>time</strong> computing is a vast field and therefore, a complete<br />

discussion about that is outside the scope of this paper.<br />

Therefore, only the most relevant aspects will be treated here.<br />

3.1 Definitions and general aspects<br />

It is possible to find in the literature several definitions for<br />

real-<strong>time</strong> systems. Here, a definition that does not contradict<br />

the definition given in the IEEE POSIX Standard (Portable<br />

Operation System Interface for Computer Environments)<br />

will be assumed<br />

A real-<strong>time</strong> system is one in which the correctness of a<br />

result not only depends on the logical correctness of<br />

the calculation but also upon the <strong>time</strong> at which the<br />

result is made available.<br />

This definition emphasizes the notion that <strong>time</strong> is one of<br />

the most important entities of the system, and there are<br />

timing constraints associated with systems tasks. Such<br />

tasks have normally to control or react to events that take<br />

places in the outside world, which are happening in “real<br />

<strong>time</strong>”. Thus, a real-<strong>time</strong> task must be able to keep up with<br />

external events, with which it is concerned.

It should be noted here that real-<strong>time</strong> computing is not<br />

equivalent to fast computing. Fast computing aims at getting<br />

the results as quickly as possible, while real-<strong>time</strong> computing<br />

aims at getting the results at a prescribed point of <strong>time</strong> within<br />

defined <strong>time</strong> tolerances. Thus, a deadline (for this point of<br />

<strong>time</strong>) can be associated with the task that has to satisfy this<br />

timing constraint specifying either its start or completion <strong>time</strong>.<br />

If the task has to meet the deadline, because otherwise it<br />

will cause fatal errors or undesirable consequences, the<br />

task is called hard real-<strong>time</strong> task. On the contrary, if the<br />

meeting of the deadline is desirable but not mandatory, the<br />

task is said to be a soft real-<strong>time</strong> task. By extension, one<br />

speaks about hard/soft <strong>time</strong>-constraints as well as hard/soft<br />

deadlines.<br />

3.2 <strong>Real</strong>-<strong>time</strong> operating systems (RTOS)<br />

In order to implement multitasking real-<strong>time</strong> systems, two<br />

approaches can be used: The first one consists in programming<br />

by using concurrent real-<strong>time</strong> languages and the<br />

second one is to use a sequential language and a real-<strong>time</strong><br />

operating system ([4]). There has been a long debate about<br />

advantages and drawback of both approaches, which will not<br />

be treated here. However, a very important point is that<br />

real-<strong>time</strong> systems and real-<strong>time</strong> operating systems are not<br />

equivalent concepts: A RTOS provides facilities, like<br />

multitasking (i.e. concurrency or potential parallelism),<br />

scheduling, intertask communication mechanism, etc., for<br />

implementing real-<strong>time</strong> systems.<br />

Old operating systems are characterised by the fact that each<br />

task is a simple program running in its own memory space.<br />

In the last years, there has been a tendency to provide facilities<br />

for creating several tasks within the same program to<br />

have faster task switch, unrestricted access to shared memory<br />

and to simplify the communication and synchronization.<br />

Such tasks are commonly called threads. The most<br />

important disadvantage of using threads consists in that the<br />

memory is not protected between threads of the same<br />

program. Figure 2 illustrates the difference between<br />

multitasking and multithread systems.<br />

M ultitasking<br />

M ultitasking<br />

One Thread<br />

M ultithread<br />

Task 1 Task n Task 1<br />

Task n<br />

Program 1 Program n Program 1 Program n<br />

Figure 2. Multitasking and multithreading concepts<br />

Together with parallelism, determinism is another important<br />

property of RTOS. A RTOS is predictable if the <strong>time</strong><br />

necessary to acknowledge a request of an external event is<br />

know in advance. The end point of this predictability<br />

scale is called determinism, in sense that this <strong>time</strong> is<br />

exactly known in advance. This concept should not be<br />

confused with responsiveness, which is the <strong>time</strong> (after the<br />

acknowledgement) elapsed till the request is attended.<br />

Determinism and responsiveness make up the response <strong>time</strong><br />

to external events. This is also called system latency.<br />

Modern RTOS include in general the following features:<br />

fast switch context, small size, preemptive scheduling based<br />

on priorities, multitasking and multithreading, intertask communication<br />

and synchronisation mechanisms (semaphores,<br />

signals, events, shared memory, etc.), real-<strong>time</strong> <strong>time</strong>rs, etc.<br />

However, RTOS are similar to standard operating systems<br />

from a structural point of view, since functional components<br />

as interrupt handler, task manager, memory manager, I/O<br />

subsystem and intertask communication are proper of both<br />

kind of operating systems.<br />

3.3 <strong>Real</strong>-<strong>time</strong> scheduling<br />

The distinctive part of a RTOS is the task manager. It is<br />

composed by the Dispatcher and the Scheduler. The Dispatcher<br />

carries out the context switch, i.e. the parameter<br />

saving for the outgoing task and the parameter loading for<br />

the incoming task, and the CPU handing over to the task<br />

that is becoming active.<br />

The Scheduler has the function of selecting the task, which<br />

will obtain the processor as next. This choice is given by<br />

means of algorithms and this is the point where RTOS and<br />

non-RTOS are mostly distinguished. <strong>Real</strong>-<strong>time</strong> systems need<br />

special algorithms to schedule a set of tasks. This is a very<br />

active area of research in computer science and many<br />

algorithms have been proposed. In this paper, only the<br />

most important uniprocessor scheduling algorithms for real<strong>time</strong><br />

requirements will be presented. Fig. 3 presents an<br />

overview about some well-known scheduling algorithms<br />

(for details see e.g. [17], [12]).<br />

Scheduling algorithms can be grouped in two classes: static<br />

and dynamic algorithms. A static scheduling requires that<br />

the complete information about the scheduling problem<br />

(number of tasks, deadlines, priorities, periods, etc.) is<br />

known a priori. Thus, the scheduling problem is solved<br />

before the schedule is executed. Such scheduler is also<br />

called clairvoyant. If at run <strong>time</strong> the feasibility can be<br />

determined and changes in the configuration may be carried<br />

out, then the scheduling is said to be dynamic.<br />

Static schedules must always be planed off-line. Dynamic<br />

schedules can be planed either off-line if the complete<br />

scheduling problem is known a priori but with an on-line<br />

implementation, i.e. the configuration is changed at run<br />

<strong>time</strong>, or on-line if the future is unknown or ignored. Advantage<br />

of off-line scheduling is its determinism and the disadvantage<br />

its inflexibility. On the contrary, an on-line<br />

scheduling is very flexible but poor in determinism. Moreover,<br />

an on-line scheduling does not perform well if the<br />

system is overloaded. However, on-line scheduling is clearly<br />

the only option in a system whole future workload is<br />

unpredictable.<br />

The guarantee that all deadlines are met can be taken as<br />

measure of the effectiveness of a real-<strong>time</strong> scheduling algorithm.<br />

If any deadline is not met, the system is said to be<br />

overloaded. Liu and Layland ([13]) showed that the total<br />

processor utilization for a set of n tasks given by<br />

n C<br />

U i<br />

(1)<br />

min( D , )<br />

i 1 i T<br />

i<br />

can be used as schedulability test. C is the execution <strong>time</strong>,<br />

D the deadline and T the task period. If the task is<br />

aperiodic or the deadline is smaller than the period, then<br />

the deadline is used in the equation. Figure 3 presents a<br />

classification for the most well-known dynamic scheduling<br />

algorithms for uniprocessor systems. In the following, the

most popular algorithms for scheduling tasks with real-<strong>time</strong><br />

requirements will be shortly presented.<br />

Static Scheduling<br />

Scheduling Policies<br />

With Priorities<br />

Dynamic Priorities<br />

Dynamic Scheduling<br />

Without Priorities<br />

Preemptive Non-preemptive Preemptive<br />

Static Priorities<br />

Nonpreemptive<br />

Preemptive<br />

Nonpreemptive<br />

SJF FPS mit Deadline mit Deadline SRT HRRN RR FCFS<br />

<strong>Real</strong>-Time Scheduling<br />

FPS: Fixed-Priority<br />

RMS DMS EDF LLF MUF<br />

FCFS: First Come First served RMS: Rate Monotonic<br />

RR: Round Robin<br />

DMS: Deadline Monot. Scheduling<br />

<strong>Real</strong>-Time Scheduling<br />

FC-EDF<br />

EDF: Earliest Deadline<br />

SJF: Shortest Job First<br />

LLF: Least Laxity First<br />

SRT: Shortest Remaining Time MUF: Maximum Urgency<br />

HRRN: Highest Response Ratio Next FC-EDF: Feedback EDF<br />

Figure 3. Classification of uniprocessor scheduling<br />

algorithms<br />

Fixed-Priority Scheduling (FPS). In this approach, each<br />

task has a fixed static priority which is computed pre-run<br />

<strong>time</strong>. The runnable tasks are executed in the order determined<br />

by their priorities. If all tasks are periodic, a simple<br />

priority assignment can be done according to the statement:<br />

the shorter the period, the higher the priority. This approach<br />

is known as Rate Monotonic Scheduling (RMS) and it was<br />

proposed in [13]. The schedulability analysis for this algorithm<br />

presumes that all tasks are pre-emptive, periodic with<br />

deadlines equal to the period and independent (i.e. no task<br />

precedence between tasks exists). In this case the total<br />

utilization has an upper bound given by<br />

1/ n<br />

U n(2 1)<br />

This bound converges to 0.693 for n , to 0.88 when<br />

the periods are uniform and to 1,00 only when the periods<br />

are harmonics of the smallest period. Under the conditions<br />

given above, it can be showed that the algorithm is<br />

optimal among fixed priority policies (i.e. given a set of<br />

tasks, RMS always produces a feasible schedule for this set,<br />

if any other algorithm can do that). This approach is easy to<br />

be implemented and if there are schedulability problems,<br />

the first task to fail is the task with the longest period, i.e.<br />

if the system becomes overloaded, deadlines are missed predictably.<br />

The most important drawbacks are its low utilization<br />

(under 70%), the fixed priorities, which can lead to<br />

starvation and deadlocks, and the fact that all deadlines<br />

should be equal to the periods.<br />

In order to get out of the last problem, the Deadline Monotonic<br />

Scheduling (DMS) was proposed in [11]. They generalized<br />

the RMS allowing deadlines less than periods,<br />

where the fixed priority of a task is inversely proportional<br />

to its deadline.<br />

(2)<br />

Deadline-based Dynamic Scheduling. There are some dynamic<br />

scheduling algorithms which are based on assigning<br />

priorities according to their deadline. The simplest algorithm<br />

in this class is the Earliest Deadline First algorithm (EDF),<br />

where the task with the earliest (shortest) deadline has the<br />

highest priority. Thus, the resulting priorities are naturally<br />

dynamic. This algorithm can be used for both dynamic and<br />

static scheduling. However, absolute deadline are normally<br />

computed at run <strong>time</strong> and hence the algorithm is presented<br />

as dynamic. This algorithm was also proposed in [ 13] .<br />

They also showed that if all task are periodic and preemptive,<br />

then the algorithm is optimal and its utilization is U 1.<br />

A disadvantage of this algorithm is that the execution <strong>time</strong> is<br />

not taken into account in the priority assignment.<br />

Another algorithm that is also optimal for scheduling preemtive<br />

tasks on one-processor system is the Maximum Laxity<br />

First (MLF) algorithm ([6], also called Least Slack-<strong>time</strong><br />

First, (LSF) or Least Laxity First (LLF) algorithm). At any<br />

<strong>time</strong>, the laxity (or slack) of a task with deadline is equal to<br />

Laxity deadline remaining execution <strong>time</strong> . (3)<br />

The MLF algorithm assigns priorities based on their laxities:<br />

the smaller the laxity, the higher the priority. This algorithm<br />

requires the knowledge of the current execution <strong>time</strong>, and<br />

then laxity is essentially a measure of the flexibility available<br />

for scheduling a task. Thus, MLF takes into consideration the<br />

execution <strong>time</strong> of a task, and this is it advantage in front of<br />

EDF. On the other hand, the execution <strong>time</strong> is normally not<br />

known until the task complete and therefore estimation is<br />

necessary. Because this estimation is used to schedule the<br />

set of task, the resulting schedule can be incorrect. This is<br />

its most serious disadvantage.<br />

The MLF algorithm also has a schedulable bound of 100%<br />

for all task sets. A problem with EDF as well as MLF is<br />

that there is no way to predict which tasks will fail in<br />

transient overboard situations. This has led to another algorithm<br />

called Maximum Urgency First (MUF) algorithm<br />

([19]), where an explicit description of urgency is assigned<br />

to each task. This urgency is defined as a combination of<br />

two fixed priorities, and a dynamic priority, which is<br />

inversely proportional to the task laxity. One of the fixed<br />

priorities, called task criticality has precedence over the<br />

dynamic priority. The other fixed priority, called user<br />

priority, has lower precedence than the dynamic priority.<br />

The criticality helps on-line algorithms to distinguish more<br />

important from less important tasks. Finally, it is necessary<br />

to remark that all mentioned dynamic algorithms do not<br />

remain optimal if pre-emption is not allowed or the system<br />

has multiple processors.<br />

If sporadic or aperiodic tasks must be scheduled, two algorithms<br />

can be used: the Deferrable Server Algorithm (DSA)<br />

and the Sporadic Server Algorithm (SSA). However, only<br />

SSA conforms to the RMS schedulability analysis.<br />

3.4 Intertask Communication and Synchronisation<br />

The intertask communication can be carried out as for<br />

non-RTOS by using mailbox, pipes and shared memory.<br />

Synchronization is very important in real-<strong>time</strong> systems for<br />

two reasons: (i) tasks may experience unpredictable delays<br />

due to blocking on shared resources to which they require<br />

exclusive access (e.g. A/D and D/A converters), and (ii) some<br />

tasks should be executed depending on results of other tasks.<br />

It can be shown that the addition of mutexes in real-<strong>time</strong> programs<br />

makes the general scheduling problem a non-predictable<br />

one ([14]). To solve this problem with an EDF algorithm<br />

kernelized monitor protocol can be used and priority<br />

ceiling protocol if the scheduling algorithm is RMS.<br />

3.5 Common programming mistakes<br />

By programming real-<strong>time</strong> system, many typical mistakes<br />

are often founded ([ 18] ). Some of them are:

Large or many if-then-else and/or case statements.<br />

These statements introduce in the code many different<br />

paths with varying length so that the code will also have<br />

different execution <strong>time</strong>. This becomes more significantly<br />

when the path is very long. Variable functions,<br />

state machines, lookup tables should be used instead the<br />

mentioned statements.<br />

Delays implemented as empty/dummy loops. This leads<br />

to inaccurately delays depending on the hardware.<br />

RTOS timing mechanisms should be used here for<br />

implementing exactly <strong>time</strong> delays.<br />

Indiscriminate use of Interrupts. Interrupts affect seriously<br />

the real-<strong>time</strong> predictability: They cannot be<br />

scheduled, and they have always very high priorities.<br />

Programs based on interrupt are very difficult to debug<br />

and to analyse. Moreover, they operate in kernel<br />

context.<br />

There is a very popular myth, which says that interrupts<br />

save CPU <strong>time</strong> and they guarantee the execution start of<br />

a task. This can be true in small and simple microprocessor<br />

based systems. However, it is not the case for<br />

complex real-<strong>time</strong> system, where non-preemptive periodic<br />

tasks can provide similar latency with better predictability<br />

and CPU utilization.<br />

Periodic polling threads should be used if it is possible.<br />

Interrupt services routines should be programmed in<br />

such a form that its only function is to signal an<br />

aperiodic server.<br />

Configuration information fixed using #define or similar<br />

statements. Programmers frequently use #define statements<br />

in their code to specify register addresses, limits<br />

for arrays, and configuration constants. Although this<br />

practice is common, it is undesirable because it prevents<br />

on-the-fly software patches for emergency situations,<br />

and it increases the difficulty of reusing the software in<br />

other applications. Changes in the configuration require<br />

that the entire application has to be recompiled.<br />

Implementation based on a big single loop. One big<br />

loop leads to the fact that the complete software executes<br />

to the same rate. In order to assign different and<br />

proper rates concurrent techniques for pre-emptive<br />

RTOS should be used.<br />

Use of message passing as primary intertask communication<br />

mechanism. Message passing reduces real-<strong>time</strong><br />

schedulability bound and it produces significant overhead<br />

leading to many aperiodic servers instead of periodic<br />

tasks. Moreover, deadlocks can appear in closed<br />

loops systems. Shared memory and proper synchronization<br />

mechanisms to prevent deadlocks and priority<br />

inversion should be used.<br />

To think that problems can be fixed magically. Programming<br />

errors, which become seldom visible in the<br />

debugging phase, can appear exactly at the <strong>time</strong> when<br />

the application is running and it is not possible to<br />

correct the mistake. It is necessary to find all mistake<br />

causes before the software is released.<br />

Do not analyse memory during the design. The amount<br />

of memory in most real-<strong>time</strong> systems is limited. Frequently,<br />

programmers have no idea about how much<br />

memory a certain program or data structure uses. Moreover,<br />

they are normally wrong by an order of magnitude.<br />

A memory analysis is quite simple with most of<br />

today’s development environments.<br />

Design without execution-<strong>time</strong> measurement. It is very<br />

common to assume that the program is short enough<br />

and the available <strong>time</strong> is sufficient. However, measuring<br />

of execution <strong>time</strong> should be part of the standard testing<br />

in order to avoid surprises. Hence, the system should<br />

be designed so that the code is measurable all <strong>time</strong>.<br />

4 Computer implementation of control systems<br />

Building a real-<strong>time</strong> control system requires two stages in<br />

general: controller design and digital implementation. At<br />

controller design stage, normally a control performance<br />

index is defined (because optimal control is normally<br />

preferred to specify control performance requirements) and<br />

a controller is designed which optimise this index while<br />

maintaining stability and rejecting disturbances. SISOcontrollers<br />

in an imput/output approach, e.g. PID (Proportional<br />

Integral Derivative), GMV (Generalized Minimum<br />

Variance) GPC (Generalized Predictive <strong>Control</strong>ler), pole<br />

placement, etc., can be represented by the general equation<br />

1 1 1<br />

Pq ( ) uk ( ) Tq ( ) rk ( ) Qq ( ) yk ( )<br />

where P, T, and Q are polynomials, u is the control signal,<br />

r the reference signal and y the plant output. (Notice that<br />

for the PID controller T(q -1 ) = Q(q -1 )). State Space controller<br />

with observer are given in general by<br />

(1)<br />

u( k) K r( k) K x ˆ( k)<br />

(2)<br />

o<br />

r<br />

xˆ( k1) [ AK C] xˆ( k) [ BK D] u( k) K o y(<br />

k)<br />

where K o is the observer gain. The controller is executed<br />

cyclically according to the sampling <strong>time</strong>, whose value is<br />

assumed to be correctly chosen, i.e. satisfying not only the<br />

condition given by the Shannon’s sampling theorem but<br />

also achieving the desired performance (the control design is<br />

normally based on a <strong>time</strong>-discrete model which also depend<br />

on the sampling <strong>time</strong>). In order to satisfy the “zero-execution<br />

<strong>time</strong>” requirement, it is desired that the new value for the<br />

control signal be delivered as soon as possible.<br />

At implementation stage, multiple control tasks should be<br />

scheduled to run on microprocessors or microcontrollers.<br />

All tasks should be scheduled with limited available computing<br />

resources. The chosen sampling <strong>time</strong> should take into<br />

account the limited computation <strong>time</strong> provided by the hardware.<br />

Thus, the computation <strong>time</strong> delay (control latency) <br />

is always in conflict with the sampling <strong>time</strong> T o . Depending<br />

on the magnitude of relative to T o this conflict can be<br />

classified into either a delay (0 < < T o ) or loss (T o )<br />

problem. Since the control latency is usually affected by<br />

control jitter, delay and loss can occur alternately in the<br />

same system at different <strong>time</strong>s. The loss of the control<br />

signal u(k) is equivalent, to the case when the controller<br />

computer fails to update its output during any one sampling<br />

interval and u(k-1) is applied again. Because this could<br />

occur randomly at any <strong>time</strong>, the failure to deliver a control<br />

o<br />

x<br />

(3)

signal can be treated as a correlated random disturbance<br />

u(k) at the input of the plant.<br />

The interaction between control performance and task scheduling<br />

has been investigated in [16]. Research results led to<br />

the conclusion that separated design produces suboptimal<br />

performance. Hence, the digital control system design has to<br />

be revisited in order to introduce considerations about<br />

real-<strong>time</strong> computing. In [10] and [16], the task attribute<br />

assignment with respect to control performance was focused<br />

on task period selection for a single task model of the controller<br />

like the example shown in Figure 4 (Matlab syntaxes is<br />

used for simplicity).<br />

Set_Event_Variable()<br />

(wait function)<br />

set highest priority;<br />

y = read_ADC(Ch#1);<br />

ys = signal_conditioning_scaling(y);<br />

r = signal_generator(Parameters);<br />

e = [(w-ys) e(2:length(e)];<br />

u = u + q’ * e;<br />

write_DAC(Ch#1, u);<br />

Scheduler<br />

Figure 4. <strong>Control</strong>ler implemented with one real-<strong>time</strong> periodic<br />

task<br />

Here, in order for delivering the control signal u(k) as soon<br />

as possible one-step-ahead predictive controller can be used<br />

in the form<br />

uk ( 1) f[ rk ( 1), rk ( ), , rk ( n), uk ( ), ,<br />

(4)<br />

uk ( m), yk ˆ( 1), yk ( ), , yk ( n)]<br />

where r(k+1) is assumed to be known and yk ˆ( 1)<br />

is<br />

calculated by a simple linear predictor given by<br />

yk ˆ( 1) yk ( ) yk ( ) yk ( 1)<br />

<br />

( k1) k k( k1)<br />

yk ˆ( 1) 2 yk ( ) yk ( 1)<br />

Hence, the control task started first delivering u(k) (which<br />

was calculated at <strong>time</strong> k-1), after this the remaining operations<br />

are carried out, i.e. read y(k) from A/D converter,<br />

calculating yk ˆ( 1)<br />

and then u(k+1). The disadvantage of<br />

this approach is that the control signal is calculated based on<br />

a prediction. This prediction can be however improved by<br />

using a model of the plant but in this case, more execution<br />

<strong>time</strong> is necessary.<br />

A second approach was proposed by [ 5]. This is based on<br />

the implementation of two periodic real-<strong>time</strong> tasks. The<br />

first one calculates the control signal directly after reading<br />

and conditioning y(k) and the second one updates the states<br />

after the control signal value was delivered. For the I/O<br />

representation, eq. (1) can be implemented by using a<br />

realization in the form of a ladder structure given by<br />

xr( k1) A 0xr( k) Br<br />

0 rk<br />

() <br />

<br />

<br />

xy( k1) y( k) <br />

<br />

0 A x 0 B<br />

<br />

yk ()<br />

<br />

y<br />

<br />

(5)<br />

R<br />

(6)<br />

(7)<br />

uk ( ) <br />

C<br />

r( )<br />

r<br />

( )<br />

r<br />

C<br />

k d r k<br />

y <br />

x 0 <br />

<br />

y( k) <br />

<br />

d <br />

y<br />

y( k)<br />

<br />

<br />

x<br />

<br />

0<br />

<br />

where the matrices A, B y , B r , C y , C r , d y and d u are obtained<br />

from some realization of<br />

1<br />

1<br />

T( z )<br />

ur( z) r( z)<br />

and Qz ( )<br />

u<br />

1<br />

y( z) yz ( )<br />

1<br />

Pz ( )<br />

Pz ( )<br />

and contains the controller parameters. Figure 5 illustrates a<br />

possible implementation of this idea.<br />

Task 1 (with maximum priority)<br />

Scheduler<br />

Set_Event_Variable(1)<br />

(wait function)<br />

y = read_ADC(Ch#x);<br />

ys = signal_conditioning_scaling(y);<br />

r = signal_generator(Parameters);<br />

ry = [r; ys];<br />

u = [Cr –Cy]* xu + [dr 0;0 dy] * ry;<br />

write_DAC(Ch#x, u);<br />

Reset_Event_Variable(2);<br />

Sampling <strong>time</strong> T<br />

Task 1<br />

Shared Memory<br />

Deadline Task 1<br />

Task 2<br />

Task 2<br />

Set_Event_Variable(2)<br />

(wait function)<br />

xu= Au * xu + Bu * ry;<br />

(8)<br />

Deadline<br />

Task 2<br />

Figure 5. I/O <strong>Control</strong>ler implemented with two real-<strong>time</strong><br />

tasks<br />

Space-state controllers naturally fit this task model (Figure<br />

6). All these approaches are based on optimal control design.<br />

In [15], the control performance is specified by rise <strong>time</strong>,<br />

maximum overshoot, settling <strong>time</strong> and steady state error. The<br />

task scheduling was carried out by a heuristic approach.<br />

Task 1 (with maximum priority)<br />

Scheduler<br />

Set_Event_Variable(1)<br />

(wait function)<br />

r = signal_generator(Parameters);<br />

u = Kr * r - Kx * x;<br />

write_DAC(Ch#x, u);<br />

eset_Event_Variable(2);<br />

Shared Memory<br />

u, r, x, y, Ab, Bb, Kr, Kx<br />

etc.<br />

Deadline<br />

Task 2<br />

Sampling <strong>time</strong> T<br />

Task 1<br />

Deadline Task 1<br />

Task 2<br />

Task 2<br />

Set_Event_Variable(2)<br />

(wait function)<br />

y = read_ADC(Ch#x);<br />

ys = signal_conditioning_scaling(y);<br />

x = Ab * x + Bb * [u’ y’]’;<br />

Figure 6. <strong>Real</strong>-<strong>time</strong> implementation of a state-space<br />

controller<br />

A supervisor can be implemented as an independent task.<br />

A possible scheme is shown in Figure 7.<br />

4.1 Some common mistakes in the implementation of<br />

real-<strong>time</strong> control systems<br />

In the laboratory, it can be frequently observed that control<br />

engineering students commit some of following mistakes:<br />

Overlook the anti-aliasing filter. Anti-aliasing filter is<br />

necessary to bind the highest signal frequency in order to<br />

determine correctly the sampling <strong>time</strong>. The filter can be<br />

dispensed with if the highest frequency of the signal is<br />

known and the sampler can be set accordingly.<br />

Implement the anti-aliasing filter in software (as digital<br />

filter) after the sampling. This is a typical error committed<br />

by students. Because the filter is used to avoid

Task 1 (with maximum Priority)<br />

Scheduler<br />

Set_Event_Variable(1)<br />

Sampling Time (control)<br />

(wait function)<br />

y = read_ADC(Ch#x);<br />

ys = signal_conditioning_scaling(y);<br />

r = signal_generator(Parameters);<br />

ry = [r; ys];<br />

u = [Cr –Cy]* xu + [dr 0;0 dy] * ry;<br />

write_DAC(Ch#x, u);<br />

Reset_Event_Variable(2);<br />

Scheduler Task 3<br />

Set_Event_Variable(2)<br />

(wait function)<br />

Supervision();<br />

Deadline<br />

Task 1 Task 1<br />

Task 2<br />

Shared Memory<br />

Deadline<br />

Task 2<br />

Sampling Time (supervision)<br />

Task 3<br />

Blocked by Task 1 Deadline<br />

Task 3<br />

Task 2<br />

Set_Event_Variable(2)<br />

(wait function)<br />

xu = A * xu + Br * ry;<br />

Figure 7. <strong>Real</strong>-<strong>time</strong> implementation of a state-space<br />

controller<br />

aliasing at the sampling stage, the filter must be situated<br />

before the sampling and it has to be analogue.<br />

Overlook the signal scaling. <strong>Control</strong>lers are normally<br />

designed by using a model that is parameterized according<br />

to physical or normalized units. Thus, sampled signal<br />

have also to be converted to the corresponding units,<br />

before they can be used for the control signal calculation.<br />

Unnecessary implementation of continuous-<strong>time</strong> controllers.<br />

Students frequently design a continuous-<strong>time</strong><br />

controller in Simulink and then they transfer the algorithm<br />

to real-<strong>time</strong> target system using the <strong>Real</strong> Time<br />

Workshop. The consequence is that the controller is<br />

implemented using a fixed-step solver for differential<br />

equations (normally fourth-order Runge-Kutta) with a<br />

sampling <strong>time</strong> equal to the integration step. Thus, the real<strong>time</strong><br />

task suffers an unnecessary overload. If it is possible,<br />

discrete-<strong>time</strong> controllers should be implemented.<br />

Here it is important to remark that some<strong>time</strong>s discrete<strong>time</strong><br />

control systems perform poorer than continuous<strong>time</strong><br />

ones and increasing the sampling rate does not<br />

always lead to a performance improvement. Moreover,<br />

some problems are caused by the properties of sampling<br />

zeros of pulse transfer functions at high sampling<br />

rates. In these cases, continuous-<strong>time</strong> control should be<br />

applied and the above advice could be incorrect. This<br />

clarifies the sense of the expression “if it is possible”.<br />

5 <strong>Real</strong>-<strong>time</strong> platform<br />

Nowadays it is very difficult to choose a software/hardware<br />

configuration for real-<strong>time</strong> experiments because there are<br />

many manufacturers that offer a variety of well designed<br />

systems. Thus, it is necessary to be careful at the moment<br />

to define the specifications for such systems.<br />

Today it is very common to use two computers in a host/<br />

target configuration to implement real-<strong>time</strong> control systems.<br />

The host is a computer without real-<strong>time</strong> requirements, in<br />

which the develop environment, data visualization and<br />

control panel in the form of a Graphic User Interface (GUI)<br />

reside. The real-<strong>time</strong> system run on the target, which can be<br />

a second computer or an embedded systems based on a<br />

board with a DSP (Digital Signal Processor), a PowerPc or a<br />

Pentium family processor.<br />

This separation is not necessary for small systems, since<br />

hard real-<strong>time</strong> PC operating systems such QNX ([7]),<br />

LynxOS and RT-Linux have solved the problem of deterministic<br />

response of real-<strong>time</strong> tasks, which coexist together<br />

with non-real-<strong>time</strong> tasks on the same computer. However, if<br />

the project has some spread then the host/target architecture<br />

brings more flexibility, order and computational power. An<br />

additional advantage is that the real-<strong>time</strong> system will continue<br />

working still in the case that the host crashes, increasing<br />

the reliability of the system. Requirements for a real<strong>time</strong><br />

system could be:<br />

Preemptive Multitasking for hard real-<strong>time</strong> requirements.<br />

Multitasking and multithreading are necessary if<br />

e.g. there are many independent control loops. It is also<br />

necessary to implement supervisory control as well as<br />

adaptive control.<br />

Laboratory plants do not usually need hard real-<strong>time</strong> response<br />

to obtain an acceptable performance for a simple<br />

control loop. However, this property becomes essential if<br />

the project includes research in the area of hybrid<br />

dependable systems or the algorithms should be tested<br />

for <strong>time</strong>-critical applications.<br />

POSIX compliance. Posix (Portable Operating System<br />

Interface) is an IEEE standard for operating systems.<br />

Norms 1003.1b, 1003.1d, 1003.1j specify requirements<br />

and compatibilities for real-<strong>time</strong> systems. Posix compliant<br />

software is easy to be ported.<br />

Support for real-<strong>time</strong> scheduling. Several algorithms are<br />

available for this task, e.g. RMS, EDF, MLF and MUF.<br />

Small latency such that sampling <strong>time</strong>s in the area of 1<br />

ms should be possible for several control loops.<br />

Integration with Labview. Labview is a graphical programming<br />

environment from National Instrument Inc.<br />

that combines development with a powerful programming<br />

language allowing 2-D and 3-D data presentation<br />

and visualization.<br />

The use of Matlab/Simulink/RTW should not be the<br />

exclusive tool to implement real-<strong>time</strong> software but an<br />

additional facility. Therefore, a real-<strong>time</strong> operating<br />

system with a develop environment to write software<br />

is also needed.<br />

The above stated requirements are very hart if the acquisition<br />

of ready-to-use products is wanted. For example,<br />

although EDF, MLF and MUF are well-known scheduling<br />

algorithms for real-<strong>time</strong> requisites, they are hardly to find in<br />

commercial real-<strong>time</strong> operating systems. MLF and MUF are<br />

not implemented at all and EDF can be found in JBed ([20])<br />

and RT-Linux ([2]). However, JBed is not Posix compliant,<br />

the integration with Matlab/Simulink and LabView is not<br />

available and only few CPUs and interface cards are supported.<br />

RT-Linux (or RTAI) could be a good choice if<br />

software drivers are available for the corresponding acquisition<br />

boards and the developers have enough experience<br />

installing RT-Linux because this activity is very cumbersome.<br />

A limited interface with Matlab/Simulink/RTW and<br />

Labview is available.<br />

The first software specification (multitasking/multithreading)<br />

excludes products like RTWT ([24]), WinCom ([25]) and

eal-<strong>time</strong> systems based on DSP board, since they are very<br />

limited in this aspect. Most WindowsNT-based real-<strong>time</strong> systems<br />

are inadequate for system with hard deadlines and<br />

products like InTime (from RadiSys Co.) and Hyperkernel<br />

(from Nematron Co.) do not support Matlab/Simulink and<br />

Labview. The same is valid for LynxOS ([21]).<br />

6 Conclusions<br />

In this contribution, an introduction to real-<strong>time</strong> digital<br />

control from an educational point of view has been given.<br />

Some well-known misconceptions coming from the control<br />

system community were clarified and common mistakes<br />

in the programming and in the real-<strong>time</strong> control implementtation<br />

have been highlighted. The relevance of the real<strong>time</strong><br />

implementation of the control system, particularly in<br />

case of <strong>time</strong>-critical application, can also be taken from<br />

the paper.<br />

Finally, the problem to find an adequate commercial real<strong>time</strong><br />

operating system was pointed out by summarizing the<br />

experience collected in this field.<br />

References<br />

[1] Åström, K. and B. Wittenmark. Computer <strong>Control</strong>led<br />

<strong>Systems</strong>. Prentice Hall International, 1997.<br />

[2] Barabanov, M., (1997). A Linux-based <strong>Real</strong>-Time<br />

Operating System. M.S. Thesis at New Mexico<br />

Institute of Mining and Technology.<br />

[3] Bennet, S. <strong>Real</strong>-<strong>time</strong> Computer <strong>Control</strong> an Introduction.<br />

Prentice Hall International, 1994.<br />

[4] Burns, A. and A. Wellings. <strong>Real</strong>-<strong>time</strong> <strong>Systems</strong> and Programming<br />

Languages. Addison Wesley, 2001.<br />

[5] Cervin, A. Improved Scheduling of <strong>Control</strong> Tasks, Proc.<br />

11th Euromicro conference on real-<strong>time</strong> systems,<br />

1999.<br />

[6] Dertouzos, M. L. and A. K. Mok. Multiprocessor<br />

on_line scheduling of hard_real_<strong>time</strong> tasks. IEEE<br />

Transactions on Software Engineering, Vol. 15, no.<br />

12, 1497-1506, 1989.<br />

[7] Hildebrand, D., (1992). An architectural overview of<br />

QNX. In USENIX Workshop on Micro-Kernels and<br />

Other Kernel Architectures, pp. 113-126, Seattle,<br />

WA, April 1992. USENIX.<br />

[8] Houpis, C. H. and G. B. Lamot. Digital <strong>Control</strong><br />

<strong>Systems</strong>. McGraw-Hill, 1992.<br />

[9] Katz, P. Digital <strong>Control</strong> using Microprocessors.<br />

Prentice Hall International, 1981.<br />

[10] Kim, B. K. Task Scheduling with Feedback Latency<br />

for <strong>Real</strong>-Time <strong>Control</strong> <strong>Systems</strong>. Proc. IEEE 5th Int.<br />

Conf. on <strong>Real</strong> Time Computing <strong>Systems</strong> and<br />

Applications, 37-41, 1998.<br />

[11] Leung, J.-T. and J. Whitehead. On the complexity of<br />

fixed priority scheduling of periodic real-<strong>time</strong> tasks.<br />

Performance Evaluation, 2 (4), 237–250, December<br />

1982.<br />

[12] Liu, J. W. S. <strong>Real</strong>-<strong>time</strong> <strong>Systems</strong>. Prentice Hall, 2000.<br />

[13] Liu, C. L., and J. W. Layland. Scheduling Algorithms<br />

for Multiprogramming in a Hard <strong>Real</strong> Time Environment.<br />

Journal of the Association for Computing<br />

Machinery, Vol. 20, no. 1, pp. 44-61, 1973.<br />

[14] Mok, A. K. Fundamental Design Problems of Distributed<br />

<strong>Systems</strong> for the Hard <strong>Real</strong> Time Environment.<br />

PhD thesis. M.I.T., 1983.<br />

[15] Ryu M., S. Hong, M. Saksena. Streamlining <strong>Real</strong>-<br />

Time <strong>Control</strong>ler Design: From Performance Specifications<br />

to End-to-end Timing Constraints. Proc.<br />

IEEE 3rd <strong>Real</strong> Time Technology and Application<br />

Symposium, p. 1-99, 1997.<br />

[16] Seto D., J. P. Lheoczk y, L. Sha, and K. G. Shin. On<br />

Task Schedulability in <strong>Real</strong>-Time <strong>Control</strong> <strong>Systems</strong>.<br />

Proc. 17th <strong>Real</strong>-Time <strong>Systems</strong> Symposium, 13-21,<br />

1996.<br />

[17] Stallings, W. Operating <strong>Systems</strong>. Prentice Hall, 2001.<br />

[18] Stewart D. B. 30 Pitfalls for <strong>Real</strong>-Time Software Developers.<br />

Embedded <strong>Systems</strong> Programming. Parts 1<br />

and 2, vol. 12, no. 11, 32-41; no. 12, 74-86, 1999.<br />

[19] Stewart D. B. and P. K. Khosla. <strong>Real</strong>-Time Scheduling<br />

of Dynamically Reconfigurable <strong>Systems</strong>. Proc.<br />

IEEE International Conference on <strong>Systems</strong> Engineering,<br />

Dayton Ohio, 139-142, 1991.<br />

[20] Tryggvesson J., T. Mattsson and H. Heeb, (1999).<br />

JBED: Java for <strong>Real</strong>-Time <strong>Systems</strong>. Dr. Dobb's<br />

Journal, 1999.<br />

[21] Wind River <strong>Systems</strong>, Inc., 1010 Atlantic Avenue, Alameda,<br />

CA 94501-1147, USA. VxWorks Programmer’s<br />

Guide, 1993.<br />

[22] Wittenmark B., J. Nilsson, M. Törngren. Timing Problems<br />

in <strong>Real</strong>-Time <strong>Control</strong> <strong>Systems</strong>. Proc. of American<br />

<strong>Control</strong> Conference, 1995.<br />

[23] RTLinux. The <strong>Real</strong><strong>time</strong> Linux, www.rtlinux.org.<br />

[24] The MathWorks, 3 Apple Hill Drive, Natick, MA<br />

01760- 2098, www.mathworks.com<br />

[25] Quanser Consulting, 102 George Street, Hamilton,<br />

Ontario, Canada L8P 1E2, www.quanser.com<br />

[26] ECP Educational <strong>Control</strong> Products. 5725 Ostin Avenue<br />

Woodland Hills, CA 91367 USA, www.ecpsys.com

chapter sixteen<br />

Implementation of Digital <strong>Control</strong><br />

Using Digital Signal Processors<br />

The control based on programmable digital devices such as programmable<br />

logic devices (PLDs), microprocessors/controllers (henceforth,<br />

µ-controllers), and digital signal processors (DSPs) is used widely for<br />

numerous applications ranging from home appliances to industry products.<br />

DSPs are adopted for system controllers due to their fast operation<br />

speed through dedicated arithmetic units with multipliers and<br />

fast analog-to-digital converters and digital-to-analog converters. Their<br />

fast operation is thought to be suitable enough for replacing the existing<br />

analog controllers. Of course, there are still intrinsic limitations in a<br />

digital controller’s bandwidth, compared to the classical analog controllers.<br />

In many applications, however, system designers can select either<br />

appropriate µ-controllers or DSPs with enough performance. In addition,<br />

programmable controllers provide the flexibility of easily implementing<br />

unexpected conditions.<br />

In general, in order to properly utilize DSPs as well as µ-controllers,<br />

designers should take a series of steps toward gathering the physical<br />

information about the chosen processor, software development environment,<br />

and interface between the processor and external circuits. The next<br />

step is to move on to actual implementation of the system. This chapter is<br />

intended to explain and provide helpful guidelines for implementation<br />

of a system controller based on programmable digital processors specifically<br />

with DSPs. For the convenience of explaining and understanding,<br />

a controller for a non-inverting buck-boost DC/DC converter [1]–[16] is<br />

presented. Some parts of the source codes and physical waveforms are<br />

provided.<br />

16.1 Introduction to Implementation of<br />

Digital <strong>Control</strong> Based on DSPs<br />

As the first stride toward the implementation of controllers using DSPs,<br />

the basic concepts of DSP in a hardware and software point of view, specification<br />

of the desired system, description of control flow based on the<br />

functional requirements, selection of proper µ-controllers or DSPs, and<br />

detail datasheets and manuals are explained.<br />

© 2009 Taylor & Francis Group, LLC<br />

273

274 Integrated Power Electronic Converters and Digital <strong>Control</strong><br />

16.1.1 Basic Concepts of DSPs from Hardware<br />

and Software Points of View<br />

DSP has two meanings based on hardware and software points of view.<br />

In terms of hardware, literally, a digital signal processor is a kind of<br />

µ-processor.<br />

DSPs manufactured by various semiconductor companies are presented<br />

in Table 16.1. The examples of DSP chips supplied by manufacturers<br />

are shown in Figure 16.1. The chips have leads to exchange digital or<br />

analog signals with external circuits. The chips are soldered on printed<br />

circuit boards (PCBs). Once DSP chips are powered, they begin to execute<br />

© 2009 Taylor & Francis Group, LLC<br />

Table 16.1 DSP Hardware Manufacturers<br />

Manufacturer<br />

Advanced Devices, Inc.<br />

Advanced RISC Machines<br />

Analog Devices<br />

AverLogic Technologies, Inc.<br />

DSP Group<br />

Freescale Semiconductor, Inc.<br />

Hyperstone<br />

IDT<br />

Infineon Technologies<br />

Intersil<br />

Intrinsity, Inc.<br />

Logic Devices<br />

LSI<br />

MicroChip<br />

NXP<br />

STMicroelectronics<br />

Texas Instruments, Inc.<br />

VeriSilicon<br />

Vitesse Semiconductor Corporation<br />

Zilog<br />

Remarks<br />

16/32 bit/floating point<br />

(ARM) CPU core vendor<br />

16/32 bit DSP–SHARC<br />

32-bit embedded processors–<br />

uP/68000–uCRISC/DSP combo ICs<br />

RISC/DSP combo ICs<br />

Packet classification processors<br />

8/16 bit CMOS uP<br />

DSP devices<br />

dsPIC 16-bit RISC digital signal<br />

controllers<br />

TI320Cxx DSP processors-high speed<br />

CMOS signal processing/all-digital<br />

down/up-converters, digital filters,<br />

high-speed QAM modem chip sets<br />

DSP coprocessor, VoIP<br />

DSP-based T3/E3 transceiver<br />

16-bit multi-purpose DSP<br />

manufacturer<br />

Source: Davis, L. 2008. DSP processor vendors. http://www.interfacebus.com/Digital_<br />

Signal_Processor_Manufacturers.html.

Chapter sixteen: Implementation of Digital <strong>Control</strong> 275<br />

(a) TMS320F243PGE<br />

(b) TMS320F2812PGFA<br />

Figure 16.1 DSP chip (manufactured by Texas Instruments) examples.<br />

the codes programmed by the designers in phase with the clock signals<br />

from crystal oscillators or resonators.<br />

From a software perspective, digital signal processing is said to be<br />

DSP, which means a series of procedures composed of algorithms and<br />

software codes. In other words, DSP is about how to obtain the system<br />

desired analog/digital output signals from the analog/digital input signals.<br />

The procedures of DSP can be summarized as<br />

© 2009 Taylor & Francis Group, LLC

276 Integrated Power Electronic Converters and Digital <strong>Control</strong><br />

1. Capturing analog/digital input signals (sample and hold) from hardware<br />

pins through external interface circuits<br />

2. Acquiring the digital data from the sampled signal through an analog-to-digital<br />

converter (ADC)<br />

3. Carrying out operations and calculations with the converted data<br />

and making digital results—either integer, fixed point, or floating<br />

point calculations<br />

4. Converting the digital results into the system desired analog signals<br />

through digital-to-analog converters (DACs) or digital output ports<br />

Figure 16.2 presents overall flows of program execution procedures<br />

after the DSP chip is powered. Figure 16.3 shows a diagram explaining<br />

digital signal processing including the DSP chip and the mounted DSP<br />

user program.<br />

16.1.2 Specifications of Desired System<br />

The non-inverting buck-boost DC/DC converter is used as an implementation<br />

example. The first step is to specify the functional requirements.<br />

Clarifying the specifications is the most important job for designers.<br />

Power on<br />

Boot code<br />

performed<br />

Initializing<br />

interrupt service<br />

vectors<br />

Initializing internal<br />

H/W architectures<br />

of the DSP chip<br />

Initializing the<br />

parameters of<br />

user program<br />

Interrupt Service Routines<br />

(ISRs)<br />

ISR1<br />

(Communication)<br />

ISR2<br />

(Timer/counter)<br />

ISR3<br />

(ADC)<br />

ISR4<br />

(External signals)<br />

ISRn<br />

(Other sources)<br />

User program<br />

running<br />

Data memory<br />

(Parameters/variables stored)<br />

Figure 16.2 General flow of source codes execution on DSP chips.<br />

© 2009 Taylor & Francis Group, LLC

Chapter sixteen: Implementation of Digital <strong>Control</strong> 277<br />

Periodic (<strong>time</strong>r) interrupt request<br />

every control period (in ms, us, …)<br />

Digital inputs<br />

Analog inputs<br />

Sample and<br />

hold<br />

ADC<br />

n-bit internal data<br />

memory<br />

S/W<br />

filter<br />

Input pins<br />

n-bit data memory<br />

(variables)<br />

Operations and<br />

calculations<br />

according to user<br />

procedures<br />

DAC<br />

Analog outputs<br />

Digital outputs<br />

<strong>Control</strong> parameters<br />

(data memory)<br />

Output pins<br />

Figure 16.3 Overall flow of digital signal processing.<br />

Through specifications, designers can break the project into sub-projects<br />

and assign individual jobs to team members. This helps integrate and<br />

evaluate the individual jobs.<br />

16.1.2.1 Functional Requirements of Noninverting<br />

Buck-Boost Converter<br />

The electrical specifications of a non-inverting buck-boost converter are<br />

provided in Table 16.2. The overall system block diagram is presented in<br />

Figure 16.4, where the error amplifier and PWM generator are achieved<br />

by digital components such as DSP chip and user program and PLDs.<br />

Basically, the non-inverting buck-boost converter can have three operating<br />

modes: buck, boost, and buck-boost. The buck-boost mode is lossy<br />

compared to the other modes.<br />

16.1.2.2 Modeling and State Block Diagram of Converter<br />

The electrical specifications are the same as the parameters presented in<br />

Table 16.2 and Figure 16.4. The second step is to build the state block diagram<br />

of the converter by deriving the system model. Figure 16.5 presents<br />

the equivalent circuits of the operating modes in each switching period.<br />

The buck operation and boost operation modes do not appear at the same<br />

control period. To model the non-inverting buck-boost converter, state<br />

space averaging technique [18] is introduced as follows.<br />

For small signal modeling [18],<br />

© 2009 Taylor & Francis Group, LLC

278 Integrated Power Electronic Converters and Digital <strong>Control</strong><br />

Table 16.2 Electrical Specification of Non-inverting Buck-Boost Converter<br />

Input voltage<br />

V in = 4.2 V ~ 2.5 V<br />

Output voltage<br />

V o = 3.3 V<br />

Inductor<br />

L = 100 uH<br />

Output capacitor<br />

C = 330 uF<br />

Load<br />

R = 4.7 Ω<br />

Switching frequency<br />

f s = 100 kHz<br />

Minimum effective duty cycle D min_eff = 6.265%<br />

Maximum effective duty cycle D max_eff = 98.67%<br />

iL = IL + % i L , vo = Vo+ % v o , vin = Vin + % v in ,<br />

%<br />

v in ⊕0<br />

d = D + d<br />

%<br />

= d ʺ1 , d = D + d<br />

%<br />

= d −1≥<br />

0<br />

buck buck buck ctrl<br />

boost boost boost ctrl<br />

dbuckboost = Dbuckboost + d<br />

% buckboost<br />

(16.1)<br />

For buck operation, the transfer functions and DC gains are<br />

diL<br />

1<br />

= (<br />

dt L d buck v in − v o )<br />

(16.2)<br />

dvo<br />

1<br />

dt C i o<br />

= ( L − )<br />

vR<br />

(16.3)<br />

1<br />

v%<br />

s LC V in<br />

o()<br />

d%<br />

buck() s<br />

= 2 1<br />

s +<br />

RC s 1<br />

+<br />

LC<br />

(small signal model)<br />

(16.4)<br />

v%<br />

o()<br />

0<br />

= Vin<br />

(small signal DC-gain)<br />

d%<br />

buck()<br />

0<br />

(16.5)<br />

© 2009 Taylor & Francis Group, LLC

Chapter sixteen: Implementation of Digital <strong>Control</strong> 279<br />

i in<br />

Buck<br />

switch<br />

L<br />

i L<br />

D 2<br />

i o<br />

+<br />

Q 1<br />

Q 2<br />

v o<br />

v in<br />

+<br />

–<br />

D 1<br />

Boost<br />

switch<br />

C<br />

Load<br />

R<br />

–<br />

V ref<br />

v o<br />

Error<br />

amplifier<br />

G 1 G 2<br />

v ctrl PWM<br />

generator<br />

(a) The Converter<br />

v ctrl<br />

0<br />

T s<br />

v buck_ctrl = v ctrl<br />

v H<br />

v mod<br />

v boost_ctrl = v ctrl -v mod<br />

v L<br />

G 1<br />

Buck Boost<br />

G 2<br />

0<br />

Time (s)<br />

(b) PWM Modulation Strategy (8)<br />

Figure 16.4 Non-inverting buck-boost converter. (a) Converter, (b) PWM modulation<br />

strategy [8].<br />

1<br />

V s LC V in D buck<br />

o()=<br />

2 1<br />

s +<br />

RC s 1<br />

+<br />

LC<br />

(large signalmodel),<br />

(16.6)<br />

© 2009 Taylor & Francis Group, LLC

280 Integrated Power Electronic Converters and Digital <strong>Control</strong><br />

L<br />

i in Q1<br />

D 2<br />

i L<br />

Buck<br />

i c<br />

switch<br />

+<br />

Boost<br />

v in – D 1 switch<br />

Q 2<br />

C<br />

i o<br />

+<br />

v o<br />

Load<br />

L<br />

i<br />

D in Q1<br />

2<br />

i L<br />

Buck<br />

i c<br />

switch<br />

+<br />

Boost<br />

v in – D 1 switch Q 2<br />

C<br />

i o<br />

+<br />

v o<br />

Load<br />

–<br />

(a) Buck Operation<br />

–<br />

L<br />

i in Q 1<br />

i<br />

Buck L<br />

D 2<br />

i c<br />

switch<br />

+<br />

Boost<br />

v in – D 1 switch Q 2<br />

C<br />

i o<br />

+<br />

v o<br />

Load<br />

L<br />

i in Q1<br />

D 2<br />

Buck i L<br />

i c<br />

switch<br />

+ Boost<br />

v in – D 1<br />

Q<br />

switch 2<br />

C<br />

i o<br />

+<br />

v o<br />

Load<br />

–<br />

(b) Boost Operation<br />

–<br />

Figure 16.5 Equivalent circuits of operating modes.<br />

Vo()<br />

0 = VinDbuck<br />

(large signal DC-gain) (16.7)<br />

For the boost operation, the transfer functions and DC gains are<br />

diL<br />

1<br />

= [<br />

dt L v in −( 1−<br />

d boost) v o]<br />

(16.8)<br />

dv<br />

dt<br />

o<br />

1 vo<br />

= [( 1 −dboost<br />

) iL<br />

− ]<br />

C<br />

R<br />

(16.9)<br />

'<br />

Dboost<br />

v s LC V ILs<br />

%<br />

o −<br />

o()<br />

=<br />

C<br />

d<br />

%<br />

' 2<br />

boost () s<br />

s<br />

RC s D<br />

+ +<br />

LC<br />

2 1 boost<br />

v%<br />

o()<br />

0 Vo<br />

Vo<br />

= = (smallsignalDC-gain)<br />

d%<br />

'<br />

boost () 0 D 1 − Dboost<br />

boost<br />

(16.10)<br />

(16.11)<br />

© 2009 Taylor & Francis Group, LLC

Chapter sixteen: Implementation of Digital <strong>Control</strong> 281<br />

1<br />

V s LC V in( 1−<br />

D boost )<br />

o()<br />

=<br />

1<br />

s<br />

RC s 1<br />

+ + ( 1 − Dboost<br />

)<br />

LC<br />

2 2<br />

(large signal model)<br />

(16.12)<br />

V<br />

o<br />

Vin<br />

() 0 = (large signal DC-gain)<br />

1 − D<br />

boost<br />

(16.13)<br />

The DC gain (steady-state characteristic) of the non-inverting buckboost<br />

converter based on equations (16.1) to (16.13) is plotted in Figure 16.6.<br />

In particular, the fact that the steady-state characteristic is continuous in<br />

the neighborhood of d ctrl = 1 helps designers construct a single controller<br />

for the converter with two different operating modes. Even in small signal<br />

DC gain in equations (16.5) and (16.11), continuity can be found when D boost<br />

= D ctrl – 1 = 0.<br />

Figure 16.7 shows the state block diagram constructed based on the<br />

state space averaged differential equations (16.2) to (16.9). The converter<br />

output voltage can be adjusted by two parameters d buck and d boost . The<br />

construction of the state block diagram provides intuitive information<br />

about input (feedback) and output signals from the controller. As seen in<br />

Figure 16.7, the controller uses v o and v o_ref as a feedback and the desired<br />

output voltage as input signals, respectively. These two signals are processed<br />

according to the user procedures as presented in Figure 16.3. The<br />

output signals d buck and d boost are given in the form of digital pulse stream,<br />

which has a fixed frequency and variable pulse width.<br />

V o<br />

1.0<br />

3<br />

2<br />

Boost region<br />

d boost = d ctrl – 1 > = 0<br />

V o = 2V in<br />

1<br />

V o = V in<br />

Buck region<br />

d buck = duty ctrl<br />

0<br />

0.0 0.2 0.4 0.6 0.8 1.2 1.4 1.6<br />

Duty d ctrl<br />

Figure 16.6 DC gain of large signal model.<br />

© 2009 Taylor & Francis Group, LLC

282 Integrated Power Electronic Converters and Digital <strong>Control</strong><br />

v in<br />

Converter<br />

d buck<br />

+<br />

1/s 1/L<br />

i L (1–d boost )<br />

+<br />

v L –(1 – d boost )<br />

+<br />

+<br />

i c<br />

1/s<br />

1/C<br />

v o<br />

–1/R<br />

d buck<br />

v o_ref<br />

System<br />

controller (DSP)<br />

d boost<br />

v o<br />

Figure 16.7 State block diagram of system.<br />

16.1.3 <strong>Control</strong> Flow Based on State Block Diagram<br />

The controller of the system ranges from the traditional PID to the modern<br />

techniques such as sliding mode control and adaptive control [19].<br />

The state block diagram provides helpful information in selecting the<br />

preferred technique. As an example, a PI controller is introduced in this<br />

section.<br />

Figure 16.8 presents the control flow of a classical PI control with antiwindup<br />

and the analog implementation of PWM modulation based on<br />

Figure 16.4. In the PWM modulator, d boost must be less than one to prevent<br />

the inductor current i L from being extremely high in boost operation<br />

mode. In other words, v ctrl is always lower than 2v mod as seen in Figure 16.8.<br />